О

VI

4 00 VJ

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации.

Цель изобретения - расширение функ- 5 циональных возможностей путем обеспечения возможности самоконтроля цифроаналогового преобразователя в процессе преобразования реального аналогового сигнала.10

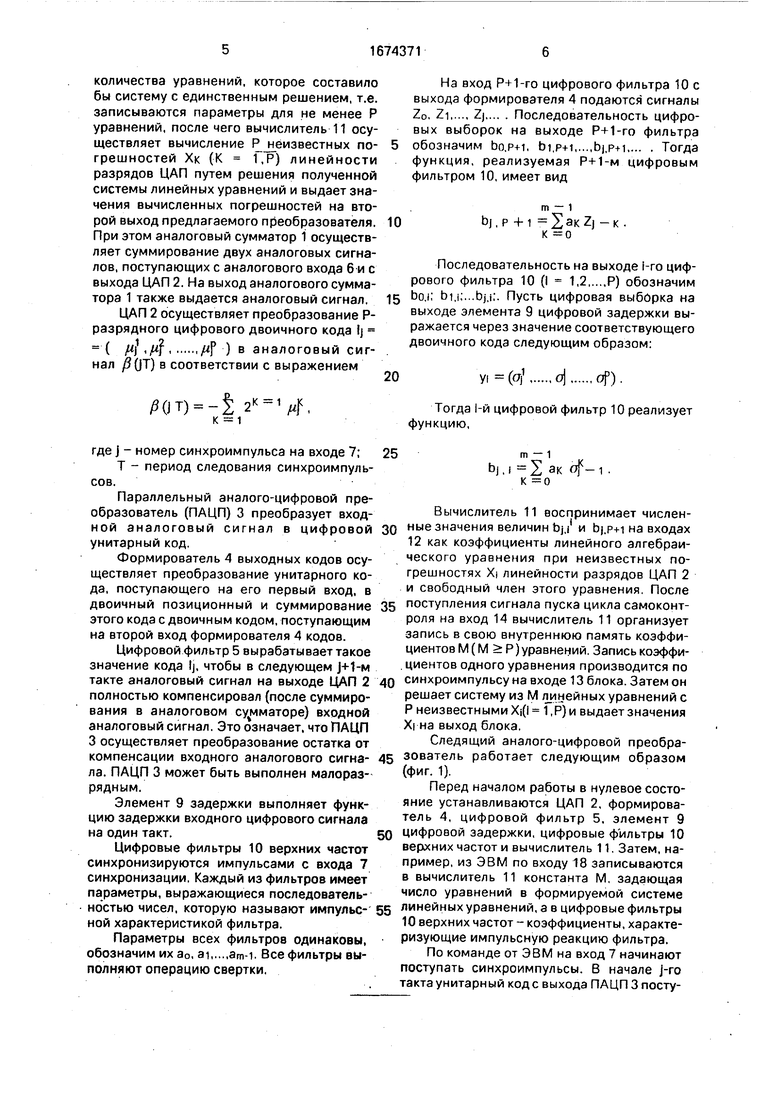

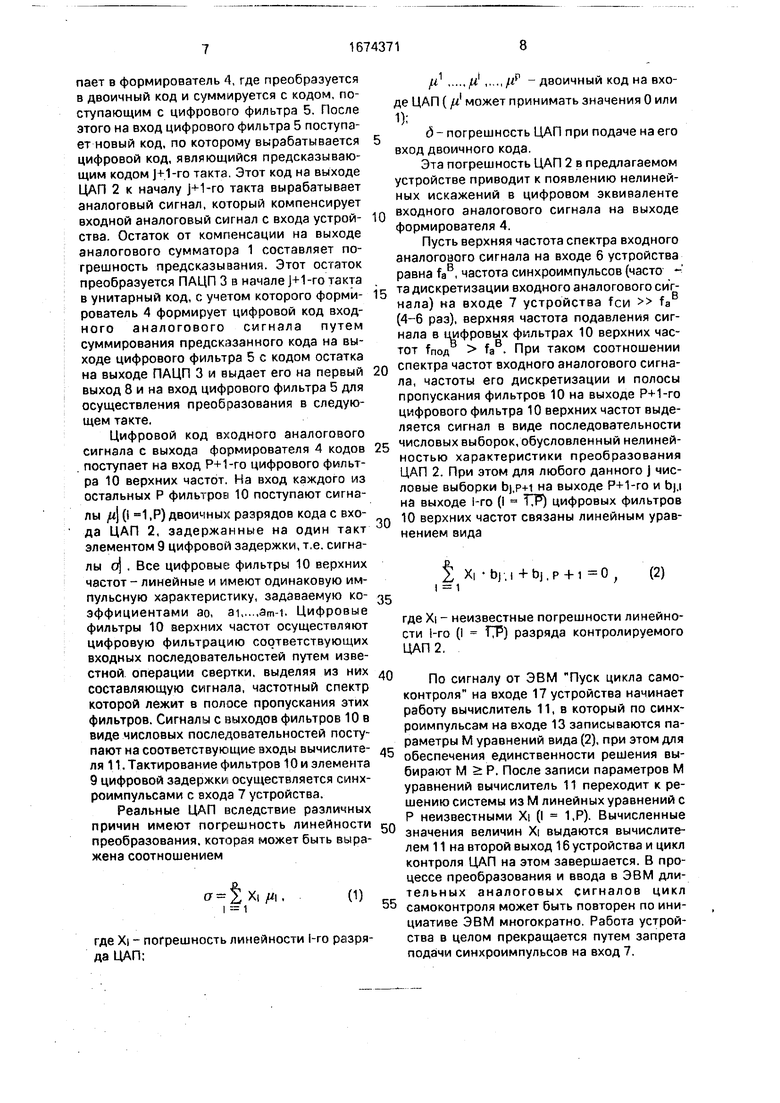

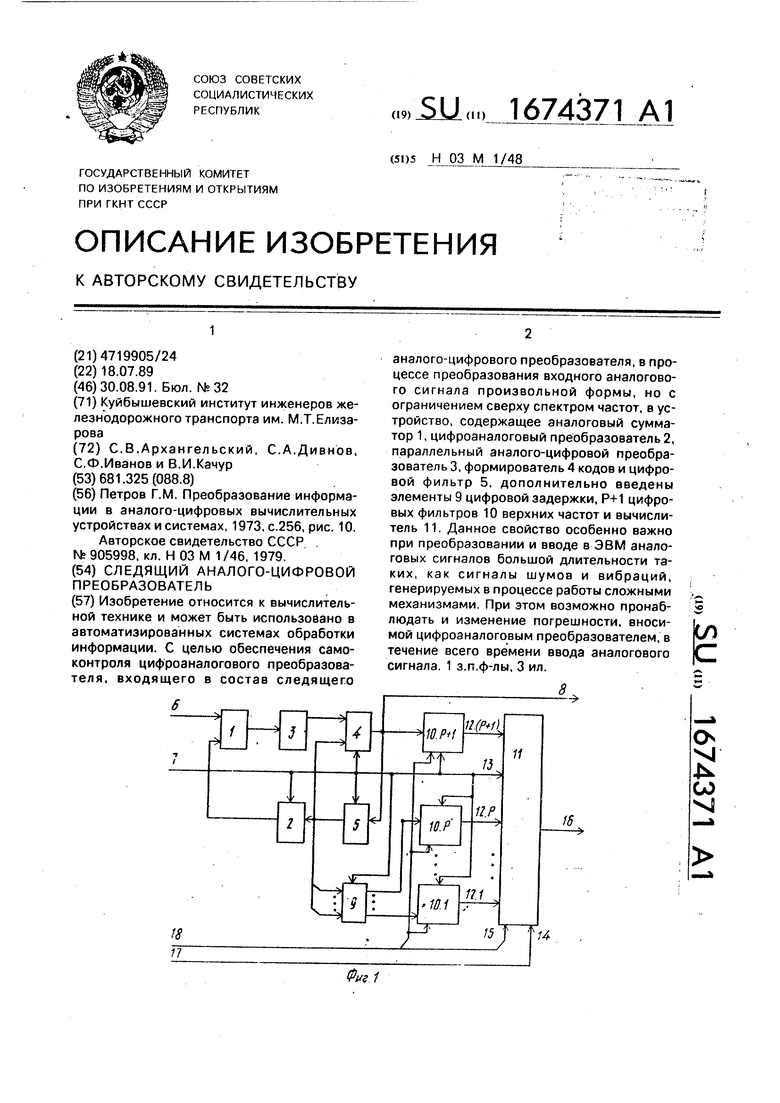

На фиг. 1 приведена функциональная схема предлагаемого преобразователя; на фиг. 2 - функциональная схема вычислителя; на фиг. 3 - алгоритм работы блока управления вычислителя.15

Следящий аналого-цифровой преобразователь содержит аналоговый сумматор 1, цифроаналоговый преобразователь 2, параллельный аналого-цифровой преобразователь 3, формирователь 4 выходных кодов, 20 цифровой фильтр 5. аналоговый вход 6 и вход 7 синхронизации, первый выход 8. элемент 9 цифровой задержки. Р+1 цифровых фильтров 10 верхних частот, вычислитель 11 с информационными 12, синхронизирую- 25 щим 13, первым 14 и вторым 15 управляющими входами, второй выход 16 и первый 17 и второй 18 входы.

Вычислитель 11 включает Р+1 блоков 19 памяти, два мультиплексора 20 и 21, умно- 30 житель 22, накапливающий сумматор 23, блок 24 решения системы линейных уравнений, три регистра 25-27, три блока 28-30 сравнения, три счетчика 31-33 и блок 34 управления.35

В аналого-цифровых преобразователях (АЦП) применяются цифроаналоговые преобразователи (ЦАП), построенные на основе резисторных сеток с взвешенными резисто- 40 рами и сеток типа R-2R. Структурно такие ЦАП эквивалентны блоку взвешенного суммирования (БВС) на Р входов с весовыми коэффициентами, в идеальном случае пропорциональными величине 2(l - 0.1....P-1), 45 где Р - разрядность ЦАП. В реальных ЦАП вследствие технологических разбросов при изготовлении, а также старения, изменения температуры и т.п., разрядные весовые ко- эффициенты эквивалентного данному ЦАП 50 БВС отличаются от величины 2 т.е. имеют погрешность. На практике можно считать, что эта погрешность существует только при открытом состоянии ключа соответствующего разряда ЦАП и равна нулю при закры- 55 том ключе. Данные погрешности приводят к нелинейности характеристики преобразования ЦАП такого вида (ее производная имеет разрывы). Погрешность линейности ЦАП при подаче на его вход определенного

двоичного кода может быть найдена по формуле

7 Ј Хко ,

К 1

где Хк - погрешность линейности К-го разряда ЦАП;

а -двоичный код на входе ЦАП (о может принимать значение 0 или

)

На аналоговый вход предлагаемого преобразователя поступает сигнал с ограниченным спектром частот. Частота выборок при аналого-цифровом преобразовании должна быть не менее удвоенной верхней частоты частотного диапазона входного аналогового сигнала,

В предлагаемом преобразователе аналого-цифровое преобразование входного сигнала производится с частотой выборок (задается частотой следования импульсов на синхровходе преобразователя) значительной большей (2-4 раза) минимально достаточной частоты. Пусть верхняя частота спектра входного аналогового сигнала равна faB и верхняя частота подавления сигнала в фильтре верхних частот тПодВ fe . Если при аналого-цифровом преобразовании входного аналогового сигнала в предлагаемом преобразователе нелинейные искажения отсутствуют (т.е. ЦАП идеально линеен), то при подаче выборок такого преобразованного сигнала с выхода формирователя выходных кодов на вход цифрового фильтра верхних частот с указанной выше характеристикой на выходе последнего сигнал в идеальном случае будет равен нулю для любого момента времени.

Погрешности линейности разрядов контролируемого ЦАП приводят к появлению нелинейных искажений (погрешности линейности) в выходном сигнале формирователя выходных кодов. На выходе Р+1-го цифрового фильтра верхних частот выделяется сигнал высокочастотной составляющей погрешности линейности аналого-цифрового преобразования, обусловленной погрешностью линейности разрядов ЦАП. При этом в каждом такте сигналы на выходе Р+1-го и К-го (К - 1, Р) цифровых фильтров верхних частот соотносятся как свободный член и коэффициенты линейного уравнения при неизвестных погрешностях Хк линейности К-го разряда контролируемого ЦАП. Следовательно, каждой выборке соответствует одно линейное уравнение.

По сигналу, например, из ЭВМ в вычислитель 11 записываются параметры такого

количества уравнений, которое составило бы систему с единственным решением, т.е. записываются параметры для не менее Р уравнений, после чего вычислитель 11 осуществляет вычисление Р еизвестных погрешностей Х« (К 1,Р) линейности разрядов ЦАП путем решения полученной системы линейных уравнений и выдает значения вычисленных погрешностей на второй выход предлагаемого преобразователя. При этом аналоговый сумматор 1 осуществляет суммирование двух аналоговых сигналов, поступающих с аналогового входа бис выхода ЦАП 2. На выход аналогового сумматора 1 также выдается аналоговый сигнал.

ЦАП 2 осуществляет преобразование Р- разрядного цифрового двоичного кода Ij

( , ) в аналоговый сигнал /(JT) в соответствии с выражением

) -Ј .

к 1

где j - номер синхроимпульса на входе 7;

Т - период следования синхроимпульсов.

Параллельный аналого-цифровой преобразователь (ПАЦП) 3 преобразует входной аналоговый сигнал в цифровой унитарный код.

Формирователь 4 выходных кодов осуществляет преобразование унитарного кода, поступающего на его первый вход, в двоичный позиционный и суммирование этого кода с двоичным кодом, поступающим на второй вход формирователя 4 кодов.

Цифровой фильтр 5 вырабатывает такое значение кода Ij, чтобы в следующем j+1-м такте аналоговый сигнал на выходе ЦАП 2 полностью компенсировал (после суммирования в аналоговом сумматоре) входной аналоговый сигнал. Это означает, что ПАЦП 3 осуществляет преобразование остатка от компенсации входного аналогового сигнала. ПАЦП 3 может быть выполнен малоразрядным.

Элемент 9 задержки выполняет функцию задержки входного цифрового сигнала на один такт.

Цифровые фильтры 10 верхних частот синхронизируются импульсами с входа 7 синхронизации. Каждый из фильтров имеет параметры, выражающиеся последовательностью чисел, которую называют импульсной характеристикой фильтра.

Параметры всех фильтров одинаковы, обозначим их Эо. aiam-i. Все фильтры ВЫПОЛНЯЮТ операцию свертки.

На вход Р-M-ro цифрового фильтра 10 с выхода формирователя 4 подаются сигналы Zo. ZiZj Последовательность цифровых выборок на выходе P+1-ro фильтра

обозначим bo.p+1, bi.p+ib|,p+i Тогда

функция, реализуемая Р+1-м цифровым фильтром 10, имеет вид

10

m - 1

bj. р + 1 Zj - к к о

Последовательность на выходе i-ro цифрового фильтра 10 (I 1,2Р) обозначим

15 bo.i; bi,i;...bj.i:. Пусть цифровая выборка на выходе элемента 9 цифровой задержки выражается через значение соответствующего двоичного кода следующим образом:

20yi(aj1ojof).

Тогда i-й цифровой фильтр 10 реализует функцию,

25т-1

bj.i 2, ак (1)- 1 . к о

Вычислитель 11 воспринимает численные значения величин bj.i и Ь|.р+1 на входах 12 как коэффициенты линейного алгебраического уравнения при неизвестных погрешностях Xi линейности разрядов ЦАП 2 и свободный член этого уравнения. После

поступления сигнала пуска цикла самоконтроля на вход 14 вычислитель 11 организует запись в свою внутреннюю память коэффициентов М(М Р)уравнений. Запись коэффициентов одного уравнения производится по

синхроимпульсу на входе 13 блока. Затем он решает систему из М линейных уравнений с Р неизвестными Xi(i 1,Р)и выдает значения Xi на выход блока.

Следящий аналого-цифровой преобразователь работает следующим образом (фиг. 1).

Перед началом работы в нулевое состояние устанавливаются ЦАП 2, формирователь 4, цифровой фильтр 5, элемент 9

цифровой задержки, цифровые фильтры 10 верхних частот и вычислитель 11. Затем, например, из ЭВМ по входу 18 записываются в вычислитель 11 константа М. задающая число уравнений в формируемой системе

линейных уравнений, а в цифровые фильтры 10 верхних частот - коэффициенты, характеризующие импульсную реакцию фильтра.

По команде от ЭВМ на вход 7 начинают поступать синхроимпульсы. В начале j-ro такта унитарный коде выхода ПАЦП 3 поступает в формирователь 4, где преобразуется в двоичный код и суммируется с кодом, поступающим с цифрового фильтра 5. После этого на вход цифрового фильтра 5 поступает новый код, по которому вырабатывается цифровой код, являющийся предсказывающим кодом J+1-ro такта. Этот код на выходе ЦАП 2 к началу j+1-го такта вырабатывает аналоговый сигнал, который компенсирует входной аналоговый сигнал с входа устройства. Остаток от компенсации на выходе аналогового сумматора 1 составляет погрешность предсказывания. Этот остаток преобразуется ПАЦП 3 в начале j+1-ro такта в унитарный код, с учетом которого формирователь 4 формирует цифровой код входного аналогового сигнала путем суммирования предсказанного кода на выходе цифрового фильтра 5 с кодом остатка на выходе ПАЦП 3 и выдает его на первый выход 8 и на вход цифрового фильтра 5 для осуществления преобразования в следующем такте.

Цифровой код входного аналогового сигнала с выхода формирователя 4 кодов поступает на вход Р+1-го цифрового фильтра 10 верхних частот. На вход каждого из остальных Р фильтров 10 поступают сигналы ум| (I -1,Р) двоичных разрядов кода с входа ЦАП 2, задержанные на один такт элементом 9 цифровой задержки, т.е. сигналы о) . Все цифровые фильтры 10 верхних частот - линейные и имеют одинаковую импульсную характеристику, задаваемую коэффициентами ао, ai,...,am-i. Цифровые фильтры 10 верхних частот осуществляют цифровую фильтрацию соответствующих входных последовательностей путем известной операции свертки, выделяя из них составляющую сигнала, частотный спектр которой лежит в полосе пропускания этих фильтров. Сигналы с выходов фильтров 10 в виде числовых последовательностей поступают на соответствующие входы вычислителя 11. Тактирование фильтров 10 и элемента 9 цифровой задержки осуществляется синхроимпульсами с входа 7 устройства.

Реальные ЦАП вследствие различных причин имеют погрешность линейности преобразования, которая может быть выражена соотношением

a L Xi i 1

где Xi - погрешность линейности 1-го разряда ЦАП;

/i ft ,. .,др - двоичный код на входе ЦАП (// может принимать значения 0 или

1):

д- погрешность ЦАП при подаче на его

вход двоичного кода.

Эта погрешность ЦАП 2 в предлагаемом устройстве приводит к появлению нелинейных искажений в цифровом эквиваленте

входного аналогового сигнала на выходе формирователя 4.

Пусть верхняя частота спектра входного аналогового сигнала на входе 6 устройства равна faB, частота синхроимпульсов (часто та дискретизации входного аналогового сигнала) на входе 7 устройства fen faB (4-6 раз), верхняя частота подавления сигнала в цифровых фильтрах 10 верхних частот тпод faB. При таком соотношении

спектра частот входного аналогового сигнала, частоты его дискретизации и полосы пропускания фильтров 10 на выходе P+1-ro цифрового фильтра 10 верхних частот выделяется сигнал в виде последовательности

числовых выборок, обусловленный нелинейностью характеристики преобразования ЦАП 2. При этом для любого данного J числовые выборки Ь),р+1на выходе Р+1-го и bj.i на выходе i-ro (I Т,Р) цифровых фильтров

10 верхних частот связаны линейным уравнением вида

35

Ј Х| bj. i + bj. Р + i 0 , (2)

i i

где Xi - неизвестные погрешности линейности 1-го (I ГР) разряда контролируемого ЦАП 2.

40По сигналу от ЭВМ Пуск цикла самоконтроля на входе 17 устройства начинает работу вычислитель 11, в который по синхроимпульсам на входе 13 записываются параметры М уравнений вида (2), при этом для

4$ обеспечения единственности решения выбирают М Р, После записи параметров М уравнений вычислитель 11 переходит к решению системы из М линейных уравнений с Р неизвестными Xi (i 1,P). Вычисленные

50 значения величин Xi выдаются вычислителем 11 на второй выход 16 устройства и цикл контроля ЦАП на этом завершается. В процессе преобразования и ввода в ЭВМ длительных аналоговых сигналов цикл

55 самоконтроля может быть повторен по инициативе ЭВМ многократно. Работа устройства в целом прекращается путем запрета подачи синхроимпульсов на вход 7.

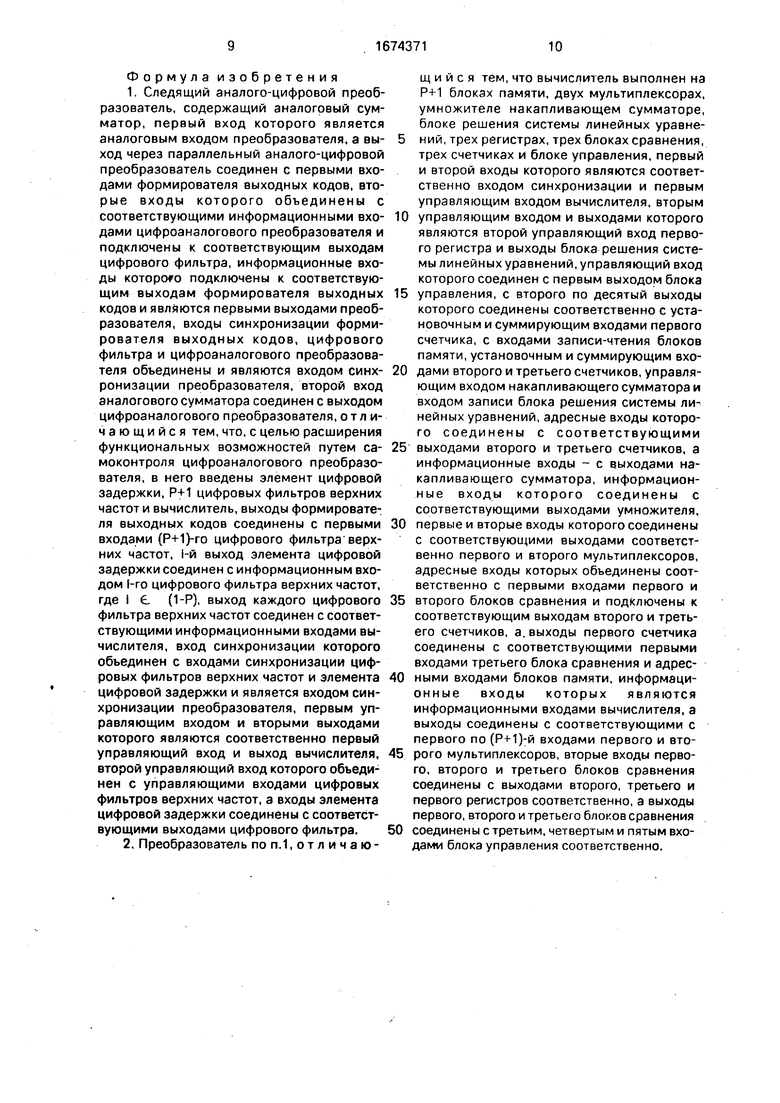

Формула изобретения

1.Следящий аналого-цифровой преобразователь, содержащий аналоговый сумматор, первый вход которого является аналоговым входом преобразователя, а выход через параллельный аналого-цифровой преобразователь соединен с первыми входами формирователя выходных кодов, вторые входы которого объединены с соответствующими информационными входами цифроаналогового преобразователя и подключены к соответствующим выходам цифрового фильтра, информационные входы которого подключены к соответствующим выходам формирователя выходных кодов и являются первыми выходами преобразователя, входы синхронизации формирователя выходных кодов, цифрового фильтра и цифроаналогового преобразователя объединены и являются входом синхронизации преобразователя, второй вход аналогового сумматора соединен с выходом цифроаналогового преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей путем самоконтроля цифроаналогового преобразователя, в него введены элемент цифровой задержки, Р-М цифровых фильтров верхних частот и вычислитель, выходы формирователя выходных кодов соединены с первыми входами (Р+1)-го цифрового фильтра верхних частот, 1-й выход элемента цифровой задержки соединен с информационным входом 1-го цифрового фильтра верхних частот, где I (L (1-Р). выход каждого цифрового фильтра верхних частот соединен с соответствующими информационными входами вычислителя, вход синхронизации которого объединен с входами синхронизации цифровых фильтров верхних частот и элемента цифровой задержки и является входом синхронизации преобразователя, первым управляющим входом и вторыми выходами которого являются соответственно первый управляющий вход и выход вычислителя, второй управляющий вход которого объединен с управляющими входами цифровых фильтров верхних частот, а входы элемента цифровой задержки соединены с соответствующими выходами цифрового фильтра.

2.Преобразователь по п.1,отличающий с я тем, что вычислитель выполнен на Р+1 блоках памяти, двух мультиплексорах, умножителе накапливающем сумматоре, блоке решения системы линейных уравне- 5 ний, трех регистрах, трех блоках сравнения, трех счетчиках и блоке управления, первый и второй входы которого являются соответственно входом синхронизации и первым управляющим входом вычислителя, вторым 0 управляющим входом и выходами которого являются второй управляющий вход первого регистра и выходы блока решения системы линейных уравнений, управляющий вход которого соединен с первым выходом блока

5 управления, с второго по десятый выходы которого соединены соответственно с установочным и суммирующим входами первого счетчика, с входами записи-чтения блоков памяти, установочным и суммирующим вхо0 дами второго и третьего счетчиков, управляющим входом накапливающего сумматора и входом записи блока решения системы линейных уравнений, адресные входы которого соединены с соответствующими

5 выходами второго и третьего счетчиков, а информационные входы - с выходами накапливающего сумматора, информационные входы которого соединены с соответствующими выходами умножителя.

0 первые и вторые входы которого соединены с соответствующими выходами соответственно первого и второго мультиплексоров, адресные входы которых объединены соответственно с первыми входами первого и

5 второго блоков сравнения и подключены к соответствующим выходам второго и третьего счетчиков, а. выходы первого счетчика соединены с соответствующими первыми входами третьего блока сравнения и адрес0 ными входами блоков памяти, информационные входы которых являются информационными входами вычислителя, а выходы соединены с соответствующими с первого по (Р-М)-й входами первого и вто5 рого мультиплексоров, вторые входы первого, второго и третьего блоков сравнения соединены с выходами второго, третьего и первого регистров соответственно, а выходы первого, второго и третьего блоков сравнения

0 соединены с третьим, четвертым и пятым входами блока управления соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| ПОЛИГАРМОНИЧЕСКИЙ ПРЕДСКАЗЫВАЮЩИЙ ФИЛЬТР | 1993 |

|

RU2046359C1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2013 |

|

RU2541856C2 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1979 |

|

SU1840108A1 |

| Преобразователь "Угол-Код" индукционного датчика угла | 2016 |

|

RU2649033C1 |

| Измеритель сдвига фаз | 1986 |

|

SU1366966A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312737A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации. С целью обеспечения самоконтроля цифроаналогового преобразователя, входящего в состав следящего аналого-цифрового преобразователя, в процессе преобразования входного аналогового сигнала произвольной формы, но с ограничением сверху спектром частот, в устройство, содержащее аналоговый сумматор 1, цифроаналоговый преобразователь 2, параллельный аналого-цифровой преобразователь 3, формирователь 4 кодов, цифровой фильтр 5, дополнительно введены элементы 9 цифровой задержки, P + 1 цифровых фильтров 10 верхних частот и вычислитель 11. Данное свойство особенно важно при преобразовании и вводе в ЭВМ аналоговых сигналов большой длительности, таких как сигналы шумов и вибраций, генерируемых в процессе работы сложными механизмами. При этом предоставляется возможность пронаблюдать и изменение погрешности, вносимой цифро-аналоговым преобразователем, в течение всего времени ввода аналогового сигнала. 1 з.п. ф-лы, 3 ил.

Ъ Мф

ty sP I

| Петров Г.М | |||

| Преобразование информации в аналого-цифровых вычислительных устройствах и системах, 1973, с.256, рис | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU905998A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-30—Публикация

1989-07-18—Подача