Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано для автоматической компенсации погрешности измерительного канала с периодической обработкой и выдачей измеряемого сигнала.

Цель изобретения - повышение точности измерения.

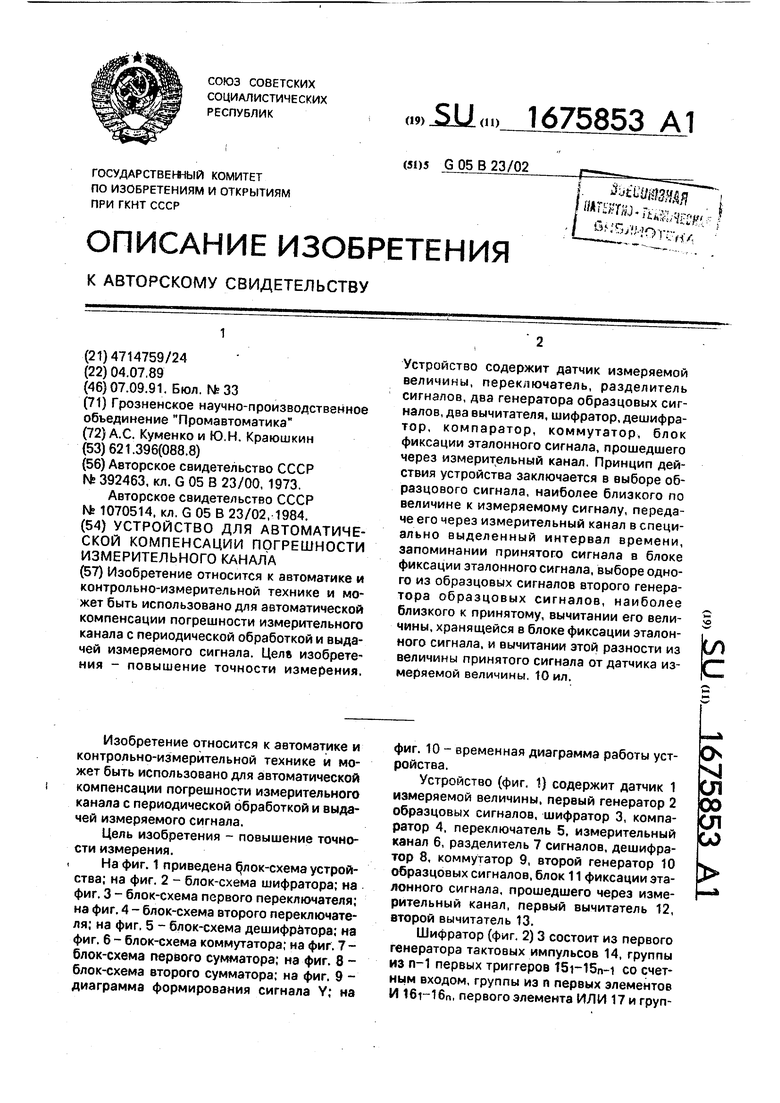

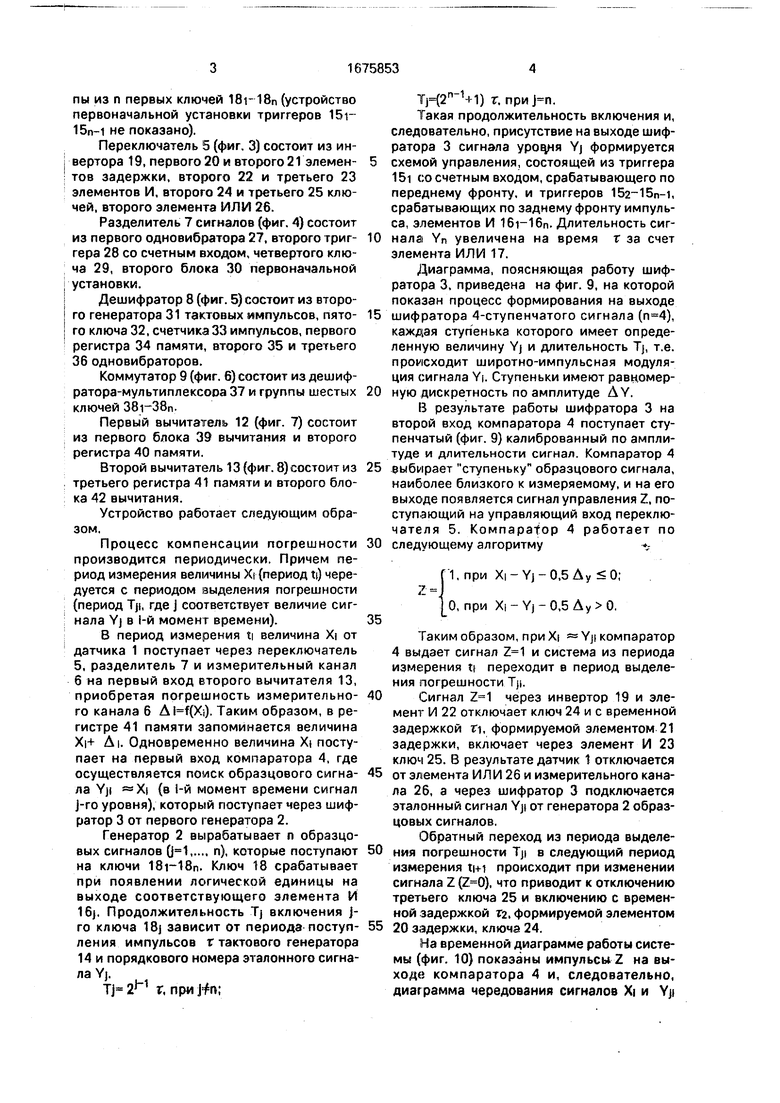

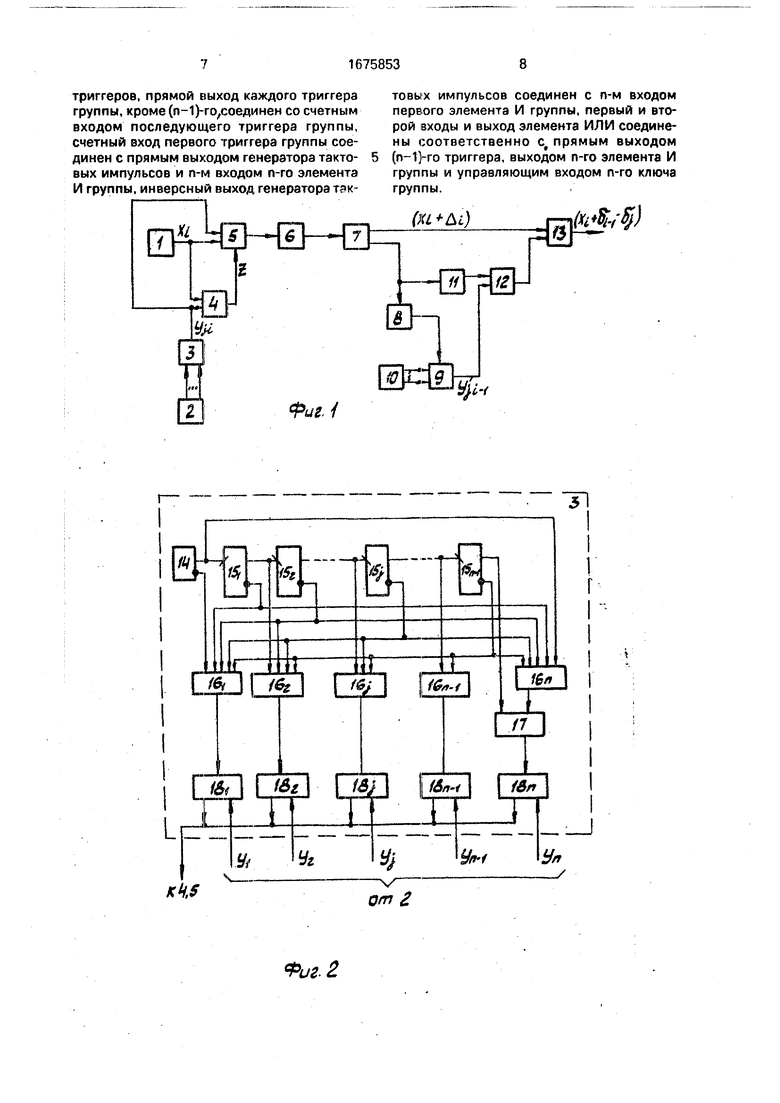

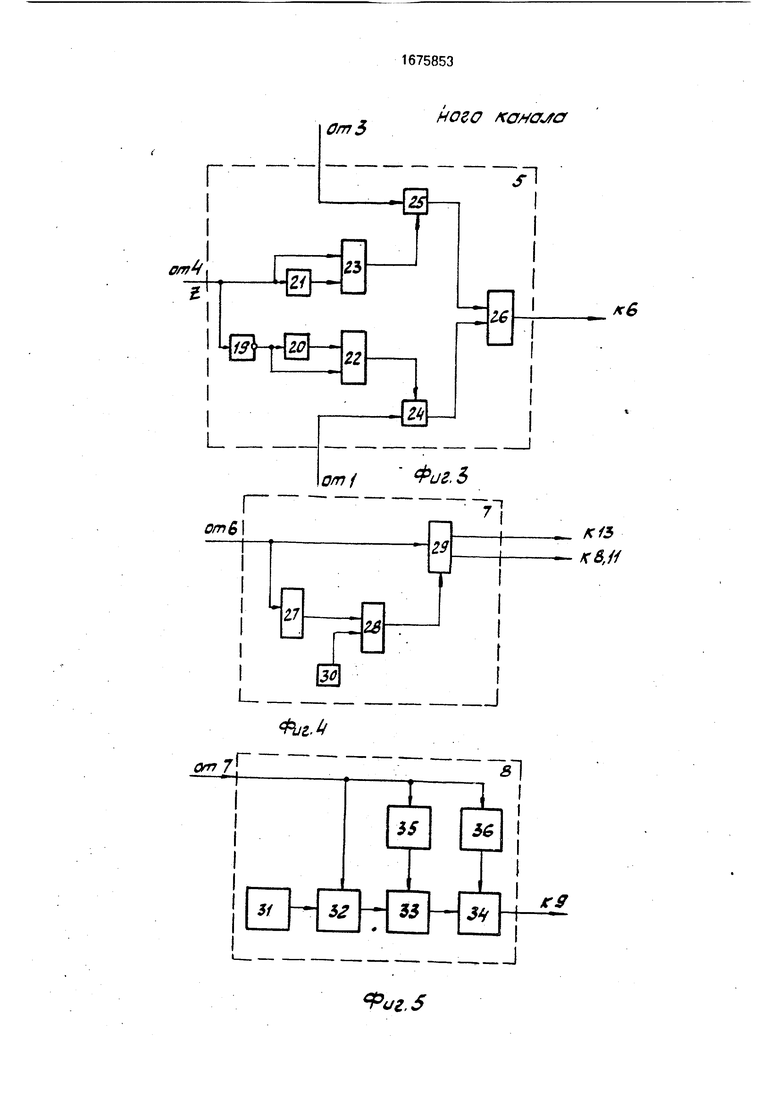

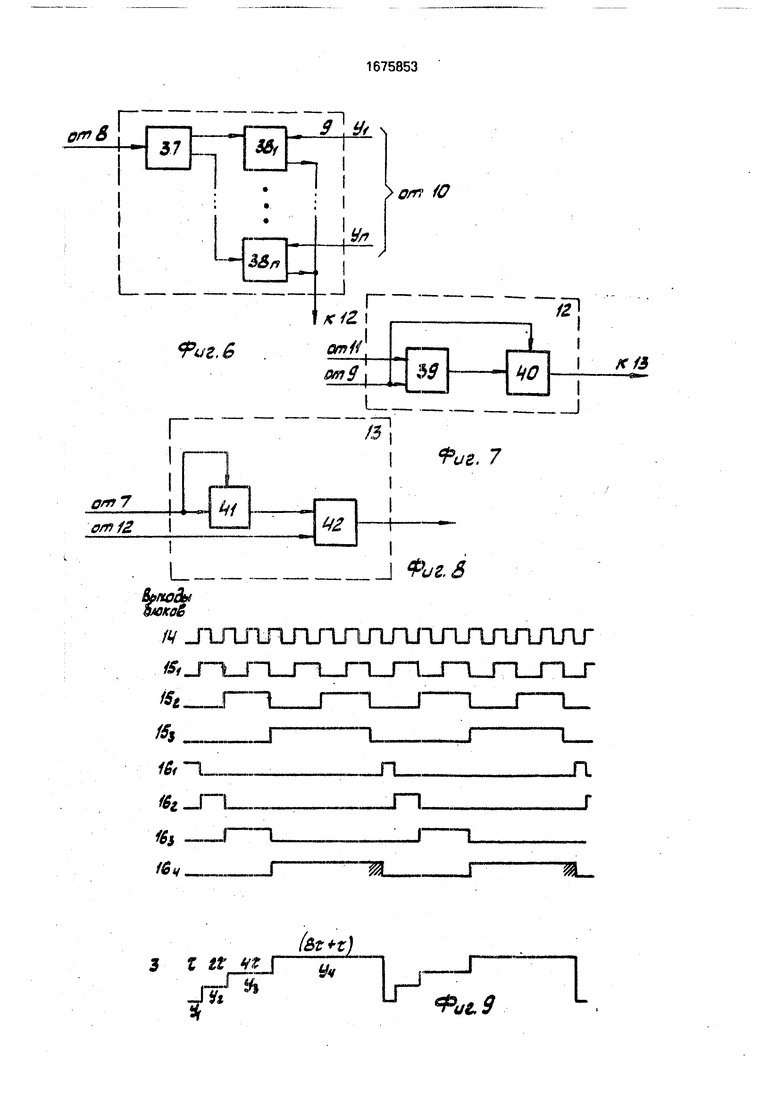

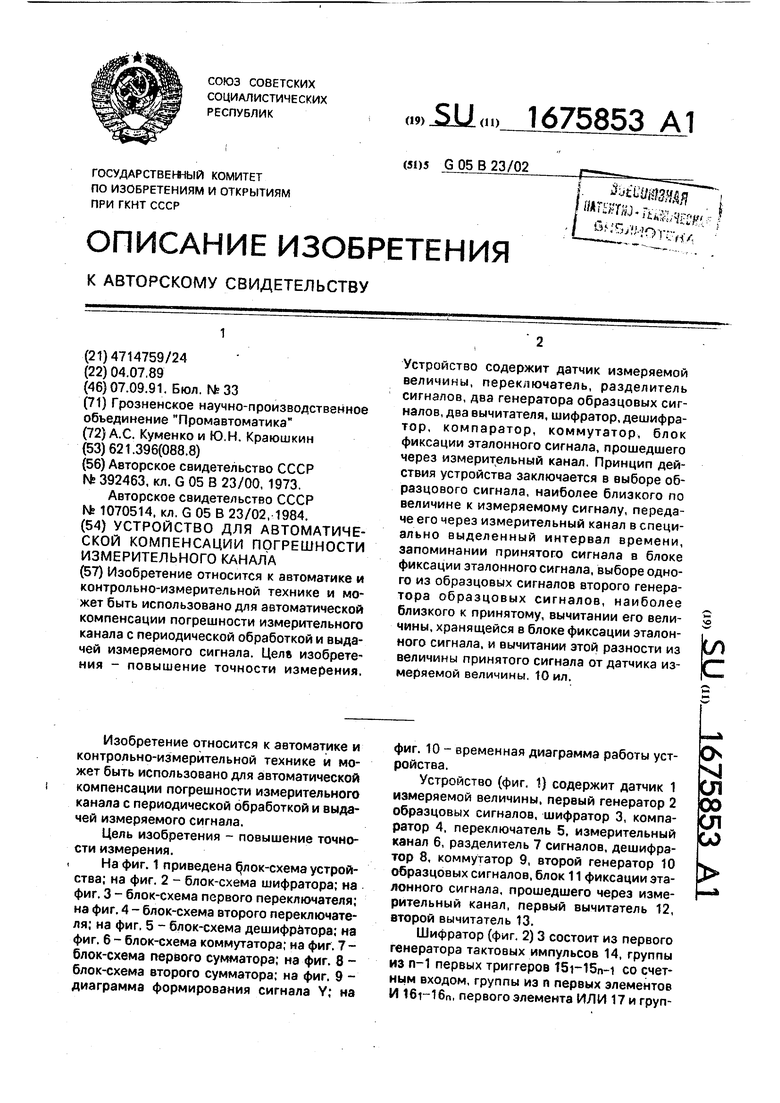

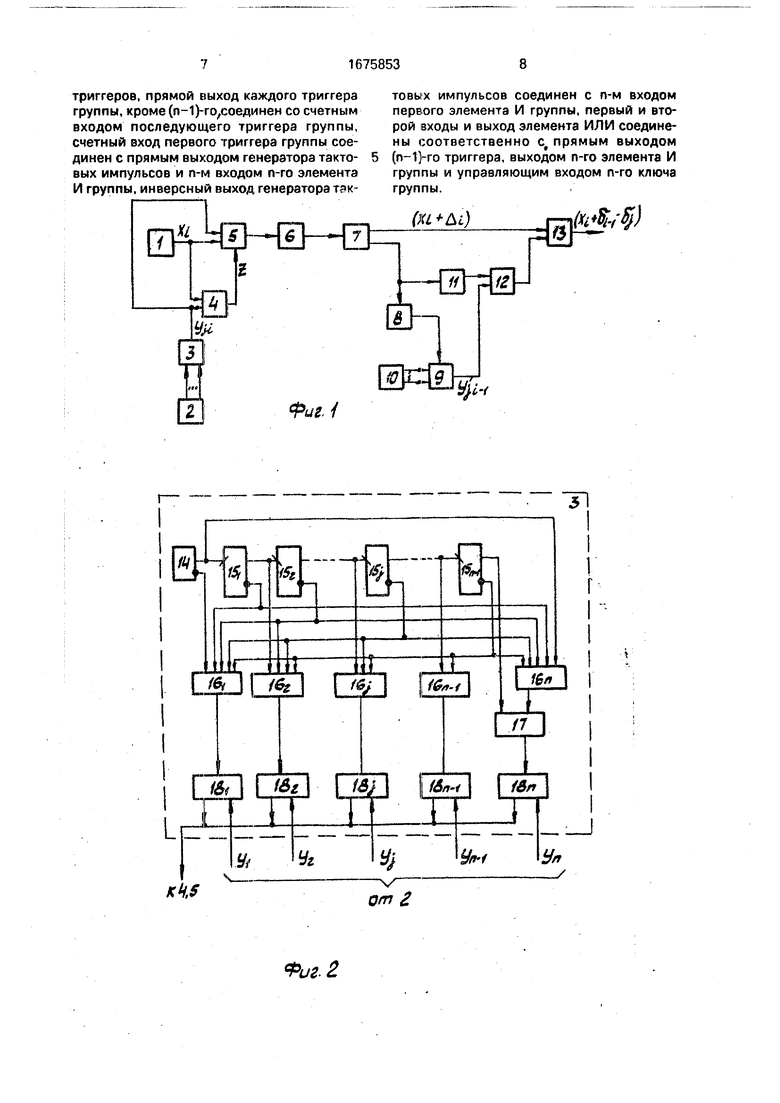

На фиг. 1 приведена б,лок-схема устройства; на фиг. 2 - блок-схема шифратора; на фиг, 3 - блок-схема первого переключателя; на фиг. 4 - блок-схема второго переключателя; на фиг. 5 - блок-схема дешифратора; на фиг. 6 - блок-схема коммутатора; на фиг. 7 - блок-схема первого сумматора; на фиг. 8 - блок-схема второго сумматора; на фиг. 9 - диаграмма формирования сигнала Y; на

фиг. 10 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит датчик 1 измеряемой величины, первый генератор 2 образцовых сигналов, шифратор 3, компаратор 4, переключатель 5, измерительный канал 6, разделитель 7 сигналов, дешифратор 8, коммутатор 9, второй генератор 10 образцовых сигналов, блок 11 фиксации эталонного сигнала, прошедшего через измерительный канал, первый вычитатель 12, второй вычитатель 13.

Шифратор (фиг. 2) 3 состоит из первого генератора тактовых импульсов 14, группы из п-1 первых триггеров 15i-15n-i со счетным входом, группы из п первых элементов И 16i-16n, первого элемента ИЛИ 17 и трупО

01 00

ел

со

пы из п первых ключей 18i-18n (устройство первоначальной установки триггеров 15i- 15n-i не показано).

Переключатель 5 (фиг, 3) состоит из инвертора 19, первого 20 и второго 21 элементов задержки, второго 22 и третьего 23 элементов И, второго 24 и третьего 25 ключей, второго элемента ИЛИ 26.

Разделитель 7 сигналов (фиг. 4) состоит из первого одновибратора 27, второго триггера 28 со счетным входом, четвертого ключа 29, второго блока 30 первоначальной установки.

Дешифратор 8 (фиг. 5) состоит из второго генератора 31 тактовых импульсов, пятого ключа 32, счетчика 33 импульсов, первого регистра 34 памяти, второго 35 и третьего 36 одновибраторов.

Коммутатор 9 (фиг. 6) состоит из дешифратора-мультиплексора 37 и группы шестых ключей 38i-38n.

Первый вычитатель 12 (фиг. 7) состоит из первого блока 39 вычитания и второго регистра 40 памяти.

Второй вычитатель 13 (фиг. 8) состоит из третьего регистра 41 памяти и второго блока 42 вычитания.

Устройство работает следующим образом.

Процесс компенсации погрешности производится периодически. Причем период измерения величины Х| (период tf) чередуется с периодом выделения погрешности (период TJI, где j соответствует величие сигнала YJ в 1-й момент времени).

В период измерения ti величина X) от датчика 1 поступает через переключатель 5, разделитель 7 и измерительный канал 6 на первый вход второго вычитателя 13, приобретая погрешность измерительного канала 6 (Xi), Таким образом, в регистре 41 памяти запоминается величина Xi+ AI. Одновременно величина Х поступает на первый вход компаратора 4, где осуществляется поиск образцового сигнала YJI «Х| (в 1-й момент времени сигнал j-ro уровня), который поступает через шифратор 3 от первого генератора 2.

Генератор 2 вырабатывает п образцовых сигналов (), которые поступают

на ключи 18i-18n. Ключ 18 срабатывает при появлении логической единицы на выходе соответствующего элемента И 16j. Продолжительность Tj включения j- го ключа 18j зависит от периода поступления импульсов г тактового генератора 14 и порядкового номера эталонного сигнала YJ.

Г, npujfn;

Tj() г, . Такая продолжительность включения и, следовательно, присутствие на выходе шифратора 3 сигнала уровня YJ формируется

схемой управления, состоящей из триггера 15i со счетным входом, срабатывающего по переднему фронту, и триггеров 152 15п-1, срабатывающих по заднему фронту импульса, элементов И 16i-16n. Длительность сигнала Yn увеличена на время г за счет элемента ИЛИ 17.

Диаграмма, поясняющая работу шифратора 3, приведена на фиг. 9, на которой показан процесс формирования на выходе

шифратора 4-ступенчатого сигнала (), каждая ступенька которого имеет определенную величину YJ и длительность Tj, т.е. происходит широтно-импульсная модуляция сигнала YI. Ступеньки имеют рэвкомерную дискретность по амплитуде AY.

В результате работы шифратора 3 на второй вход компаратора 4 поступает ступенчатый (фиг. 9) калиброванный по амплитуде и длительности сигнал. Компаратор 4

выбирает ступеньку образцового сигнала, наиболее близкого к измеряемому, и на его выходе появляется сигнал управления Z, поступающий на управляющий вход переключателя 5. Компаратор 4 работает по

следующему алгоритму,7 -

35

1. при Xi-Yj-0,5Ay 0; О, при Xi- Yj-0,5 Ay 0.

Таким образом, при Xi YJI компаратор 4 выдает сигнал и система из периода измерения переходит в период выделения погрешности TJI.

Сигнал через инвертор 19 и элемент И 22 отключает ключ 24 и с временной задержкой п, формируемой элементом 21 задержки, включает через элемент И 23 ключ 25. В результате датчик 1 отключается

от элемента ИЛИ 26 и измерительного канала 26, а через шифратор 3 подключается эталонный сигнал YJI от генератора 2 образцовых сигналов,

Обратный переход из периода выделения погрешности TJI в следующий период измерения ti-и происходит при изменении сигнала Z (), что приводит к отключению третьего ключа 25 и включению с временной задержкой TZ, формируемой элементом

20 задержки, ключа 24.

На временной диаграмме работы системы (фиг. 10) показаны импульсы Z на выходе компаратора 4 и, следовательно, диаграмма чередования сигналов Xi и YJI

на выходе измерительного канала 6. Чередование сигналов Xi и YJI происходит с соответствующими временными задержками 71 И Т2.

В период выделения погрешности TJI закодированный широтно-импульсной модуляцией сигнал YJI через первый 5, второй 7 переключатели и измерительный канал б, приобретая погрешность Aji f{Yji), поступает на дешифратор 8, блок 11 и на вычита- тель 13.

В моменты срабатывания переключателя 5 возникает временное прерывание сигнала (импульс длительностью ri). Этот импульс через измерительный канал 6 поступает на одновибратор 27 разделителя 7. Одновибратор 27 выдает импульс, переключающий триггер 28 и соответственно ключ 29. В исходное состояние триггер 28 переводится блоком 30.

Сигнал (Yji+ Ajf) с второго выхода разделителя 7 поступает на блок 11, ключ 32 и на одновибраторы 35 и 36.

Одновибратор 35 срабатывает по переднему фронту имлульса, приводя счетчик 33 в исходное состояние. Одновременно ключ 32 открывается и пропускает импульсы от генератора 31 на вход счетчика 33. Счет импульсов продолжается до окончания сигнала (Yji+ AJI), тогда ключ 32 закрывается, одновибратор 36, срабатывающий по заднему фронту импульса, инициирует запись информации со счетчика 33 в регистр 34.

Блок 11 запоминает величину сигнала (Yji+ AJI) до момента прихода следующего сигнала Yi(l+1)+ Aj(i+1). -С выхода регистра 34 сигнал, характеризующий длительность TJI, поступает на дешифратор-мультиплексор 37, который подключает один из ключей 38j. Таким образом, происходит выделение сигнала YJI , поступающего от генератора 10 образцовых сигналов. Генераторы 2 и 10 образцовых сигналов должны быть настроены так, чтобы выполнялось условие

Yi-Yj 5j Aj.

Сигнал YJ поступает на первый вход блока 39, где определяется разность (погрешность измерительного канала 6)

(Aji+Yji)-Yj i АЯ+ 5j. которая запоминается в регистре 40.

На этом заканчивается период выделения погрешности TJI и система переходит к следующему периоду измерения ti-н, в течение которого на вход регистра 41 поступает величина (Xj+i+ A1+1).

В блоке 42 происходит компенсация погрешности измерительного канала б

(Хн-1 + A i+i) - (Aji + dj) Xi+1 + di - 5j.

Учитывая, что АН-I- Ajr- (5i и являются величинами второго порядка малости по сравнению с погрешностью A i д - dj, имеется значительное повышение точности измерения.

Формула изобретения Устройство для автоматической компенсации погрешности измерительного канала, содержащее первый и второй вычитатели, первый и второй генераторы образцовых сигналов, и датчик измеряемой ве личины, выход первого вычитателя является выходом устройства, а его вход вычитаемого соединен с выходом второго вычитателя, отличающееся тем, что, с целью повышения точности измерения, а него введены блок фиксации эталонного сигнала, прошедшего через измерительный канал, коммутатор, компаратор, переключатель, разделитель сигналов, шифратор и дешифратор, причем вход датчика измеряемой величины соединен с первым информационным входом переключателя и первым входом компаратора, второй вход которого соединен с вторым информационным входом переключателя и выходом шифратора, информационные входы которого соединены с выходами первого

генератора образцового сигнала, управляющий вход переключателя соединен с выходом компаратора, а выход является выходом устройства для подключения к входу измерительного канала, вход разделителя сигналов является входом устройства для подключения к выходу измерительного канала, первый выход соединен с входом уменьшаемого второго вычитателя, второй выход - с входом дешифратора и входом

блока фиксации эталонного сигнала, прошедшего через измерительный канал, выход которого соединен с входом уменьшаемого второго вычитателя, вход вычитаемого которого соединен с выходом коммутатора,

информационные входы которого соединены с выходами второго генератора образцовых сигналов, а вход адреса с выходом дешифратора, при этом шифратор содержит генератор тактовых импульсов, группу п-1 триггеров, группу п элементов И, элемент ИЛИ и группу п ключей, информационные входы которых являются информационными входами шифратора, выходы обьединень, и являются

выходом шифратора, управляющие входы ключей групп с первого по (п-1)-й соединен с выходами соответственно элементов И группы с первого по (п-1)-й, входы которых соединены с инверсными выходами групп

триггеров, прямой выход каждого триггера группы, кроме (п- го оединен со счетным входом последующего триггера группы, счетный вход первого триггера группы соединен с прямым выходом генератора тактовых импульсов и n-м входом п-го элемента И группы, инверсный выход генератора тактовых импульсов соединен с n-м входом первого элемента И группы, первый и второй входы и выход элемента ИЛИ соединены соответственно с, прямым выходом (п-1)-го триггера, выходом n-го элемента И группы и управляющим входом n-го ключа группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для централизованного контроля параметров | 1987 |

|

SU1444717A1 |

| РАДИАЦИОННЫЙ ТОЛЩИНОМЕР ПОКРЫТИЙ | 1988 |

|

SU1805736A1 |

| Устройство для компенсации погрешностей измерительного канала | 1989 |

|

SU1755257A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Устройство для автоматической коррекции погрешностей измерительного преобразователя | 1986 |

|

SU1402980A2 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Адаптивный коммутатор | 1982 |

|

SU1061170A1 |

| Адаптивное телеизмерительное устройство | 1975 |

|

SU608186A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано для автоматической компенсации погрешности измерительного канала с периодической обработкой и выдачей измеряемого сигнала. Цел изобретения - повышение точности измерения. Устройство содержит датчик измеряемой величины, переключатель, разделитель сигналов, два генератора образцовых сигналов, два вычитателя, шифратор, дешифратор, компаратор, коммутатор, блок фиксации эталонного сигнала, прошедшего через измерительный канал. Принцип действия устройства заключается в выборе образцового сигнала, наиболее близкого по величине к измеряемому сигналу, передаче его через измерительный канал в специально выделенный интервал времени, запоминании принятого сигнала в блоке фиксации эталонного сигнала, выборе одного из образцовых сигналов второго генератора образцовых сигналов, наиболее близкого к принятому, вычитании его величины, хранящейся в блоке фиксации эталонного сигнала, и вычитании этой разности из величины принятого сигнала от датчика измеряемой величины. 10 ил.

Фиь1

Г

1

SJQirj РзГ)

I

1& 11 to I W Qi:

J

I

у

Уг

«.#

Фиг. 2.

&,-$

V.

Г

1

)

jg/rj

I

н Qi

J

-v от 2

Ум

наго канала

Фиг. 5

3 г it чг

fat+t)

fT LK

Ф«г.9

i

Выходы Влакоб

V 4

/

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ | 0 |

|

SU392463A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для компенсации погрешности измерения и диагностического контроля измерительного канала | 1982 |

|

SU1070514A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-09-07—Публикация

1989-07-04—Подача