Изобретение относится к .вычисли- телы1ой технике и может быть исаоль- зовано при настройке разрабатываемых

и контроле серийно выпускаемых циф-

5 ровыХоузлов.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контроля цифровых узлов с внутренними ю средствами программного управления.

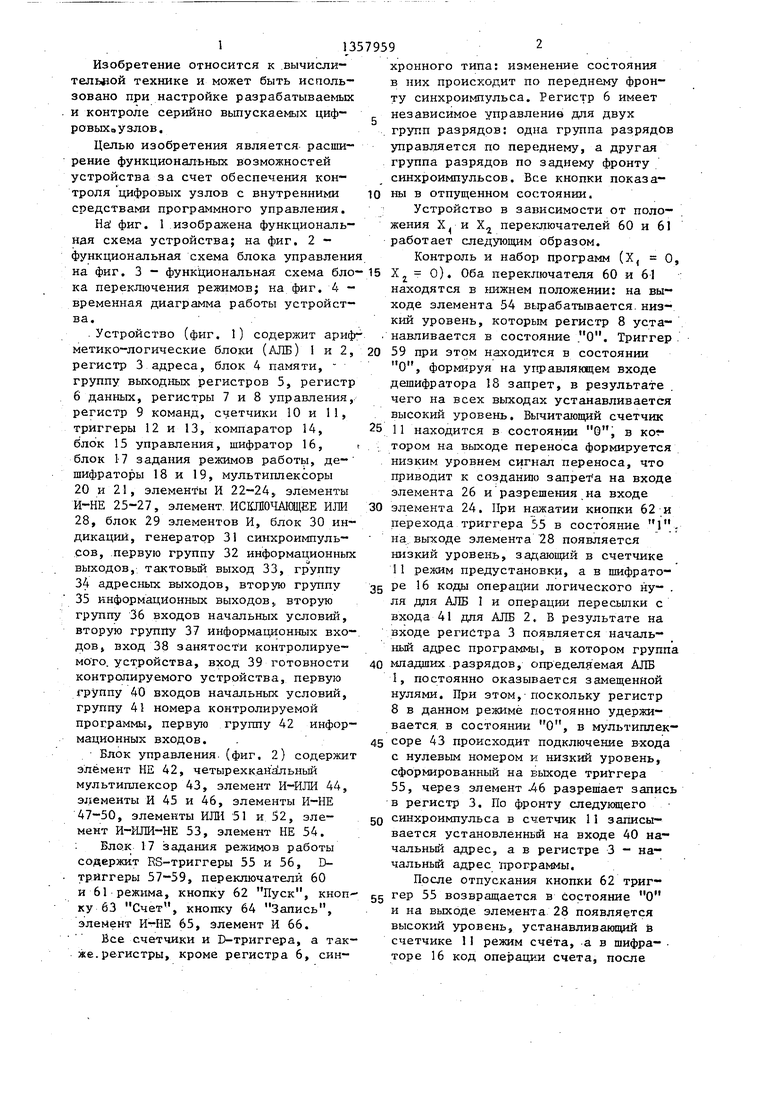

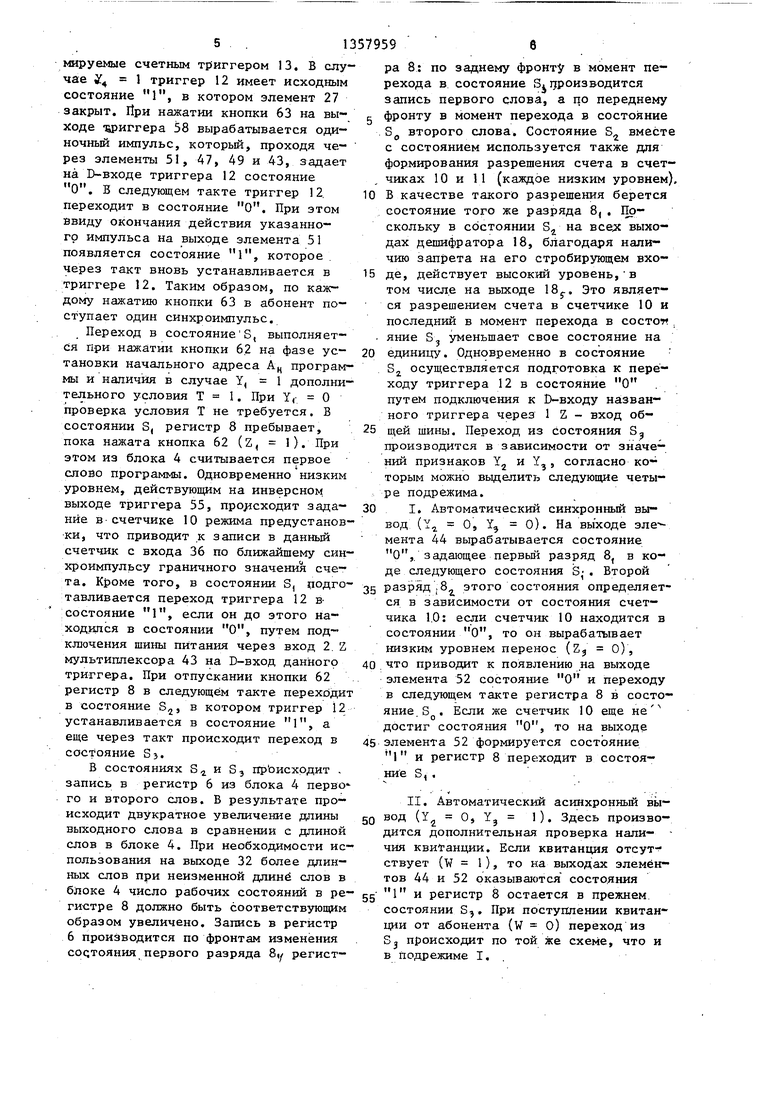

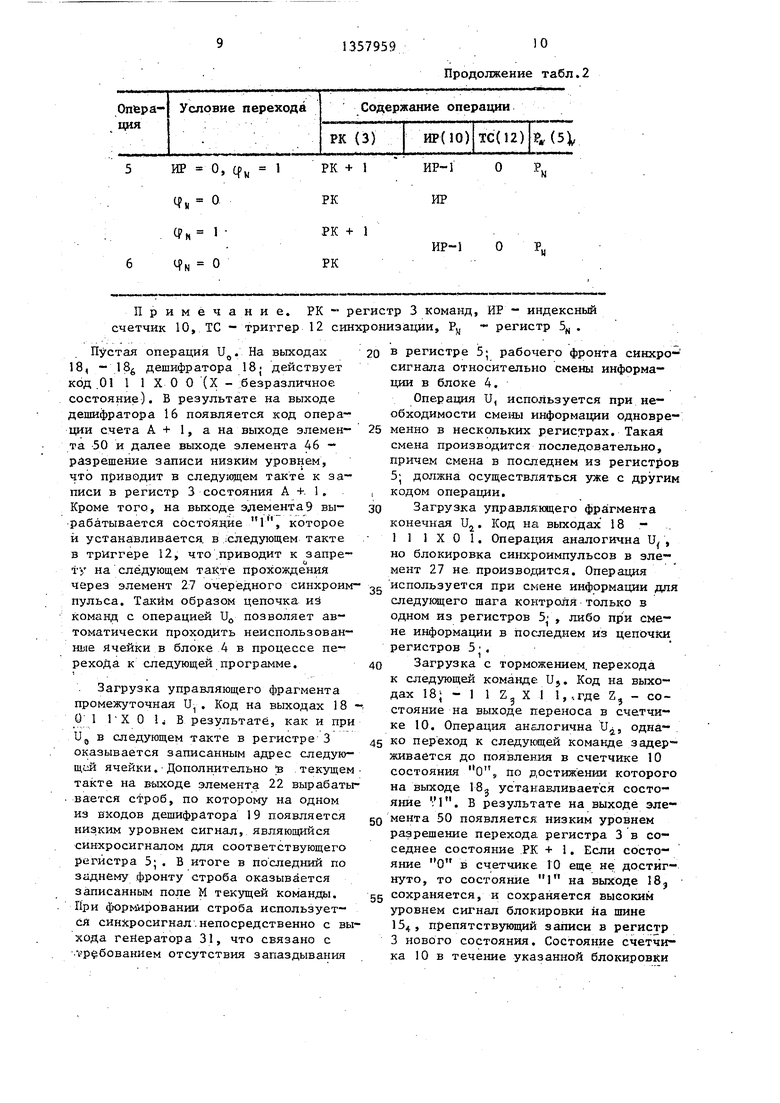

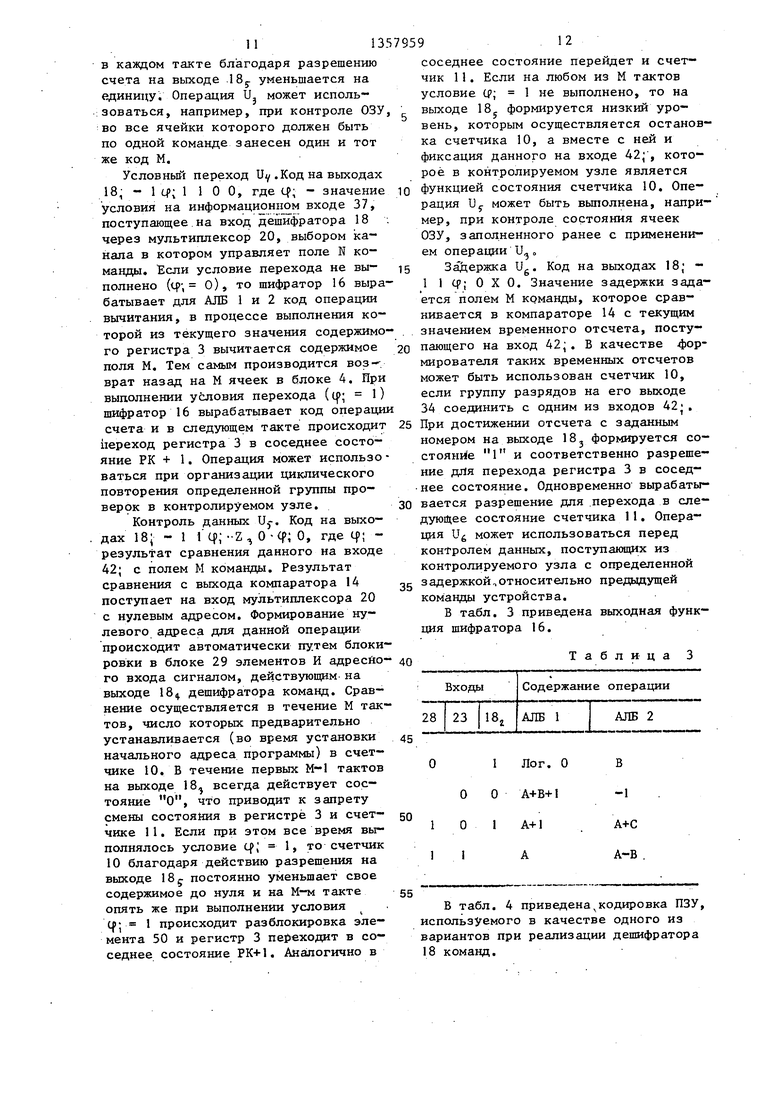

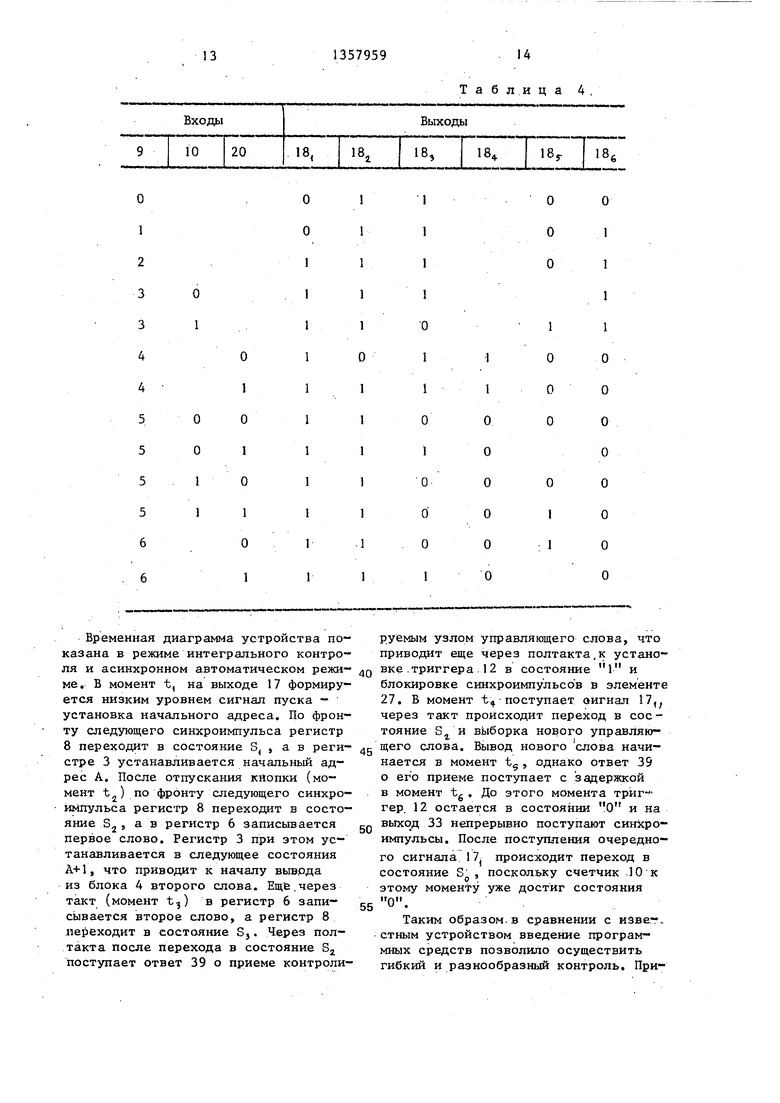

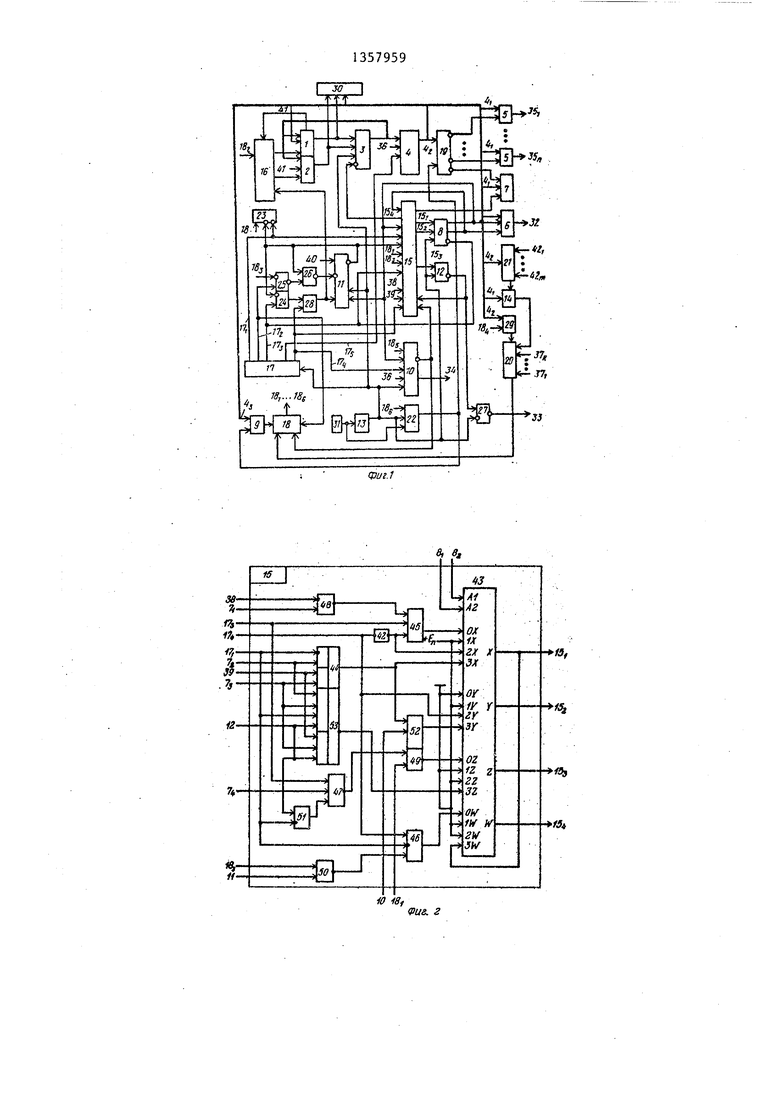

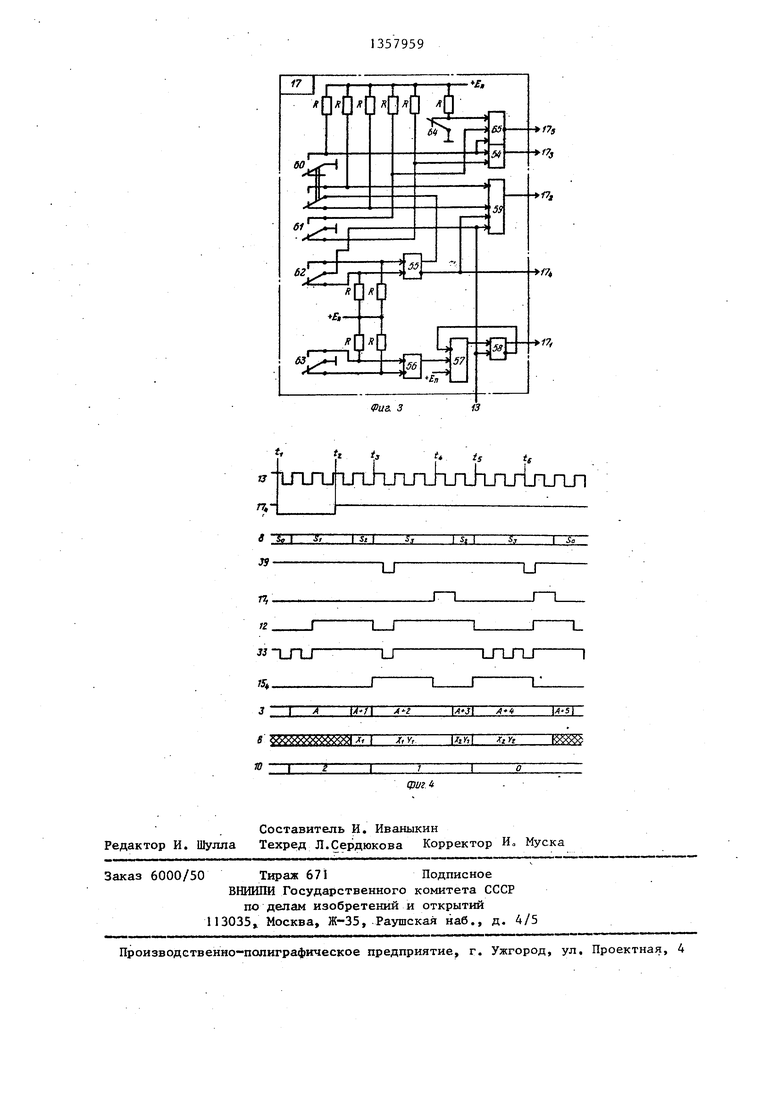

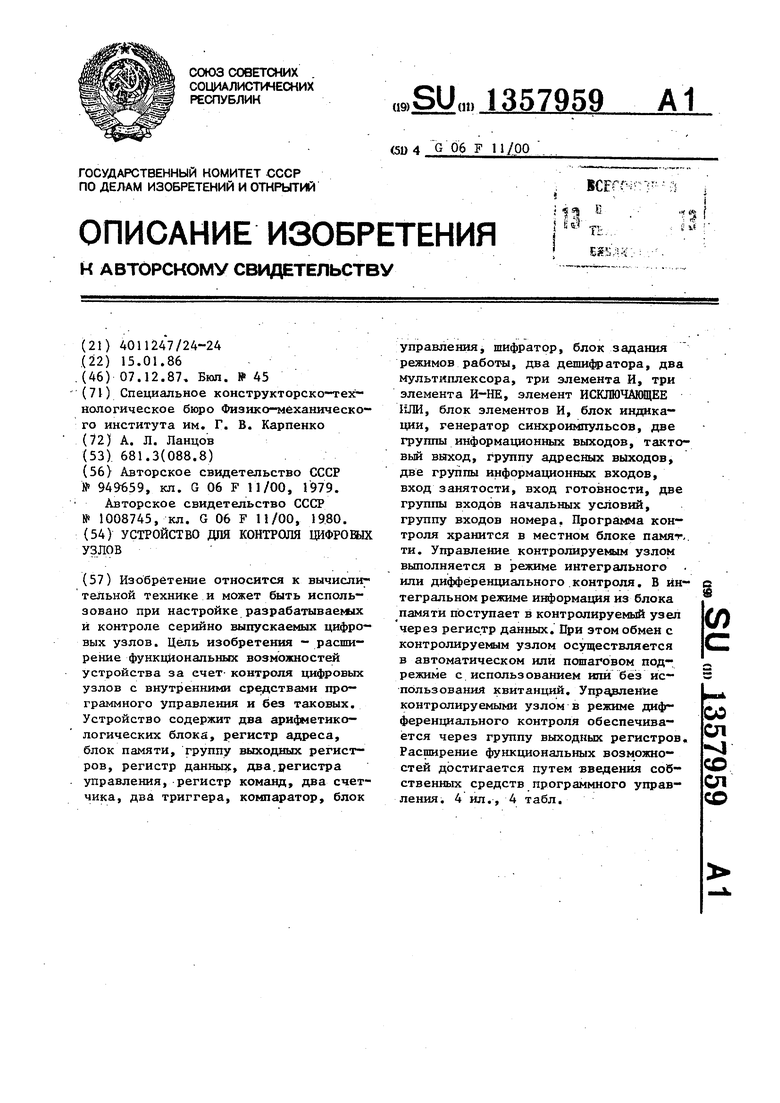

Hal фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока управления на фиг. 3 - функциональная схема бло- 15 ка переключения режимов; на фиг. 4 - временная диаграмма работы устройства.

.Устройство (фиг. 1) содержит ариф20

метико-логические блоки (АЛБ) 1 и 2, регистр 3 адреса, блок 4 памяти, группу выходных регистров 5, регистр 6 данных, регистры 7 и 8 управления, регистр 9 команд, счетчики 10 и И, триггеры 12 и 13, компаратор 14, блок 15 управления, шифратор 16, t блок 17 задания режимов работы, шифраторы 18 и 19, мультиплексоры 20 и 21, элементы И 22-24, элементы И-НЕ 25-27, элемент, ИСКЛО ШЩЕЕ ИЛИ 28, блок 29 элементов И, блок 30 индикации, генератор 31 синхроимпульсов, первую группу 32 информационных выходов, тактовьй выход 33, rpVnny

34адресных выходов, вторую группу

35информационных выходов, вторую группу 36 входов начальных условий, вторую группу 37 информационных вхо- дов вход 38 занятости контролируе- мо го. уст;ройства, вход 39 готовности контролируемого устройства, первую группу 40 входов начальных условий, группу 41 номера контролируемой программы, первую группу 42 информационных входов.

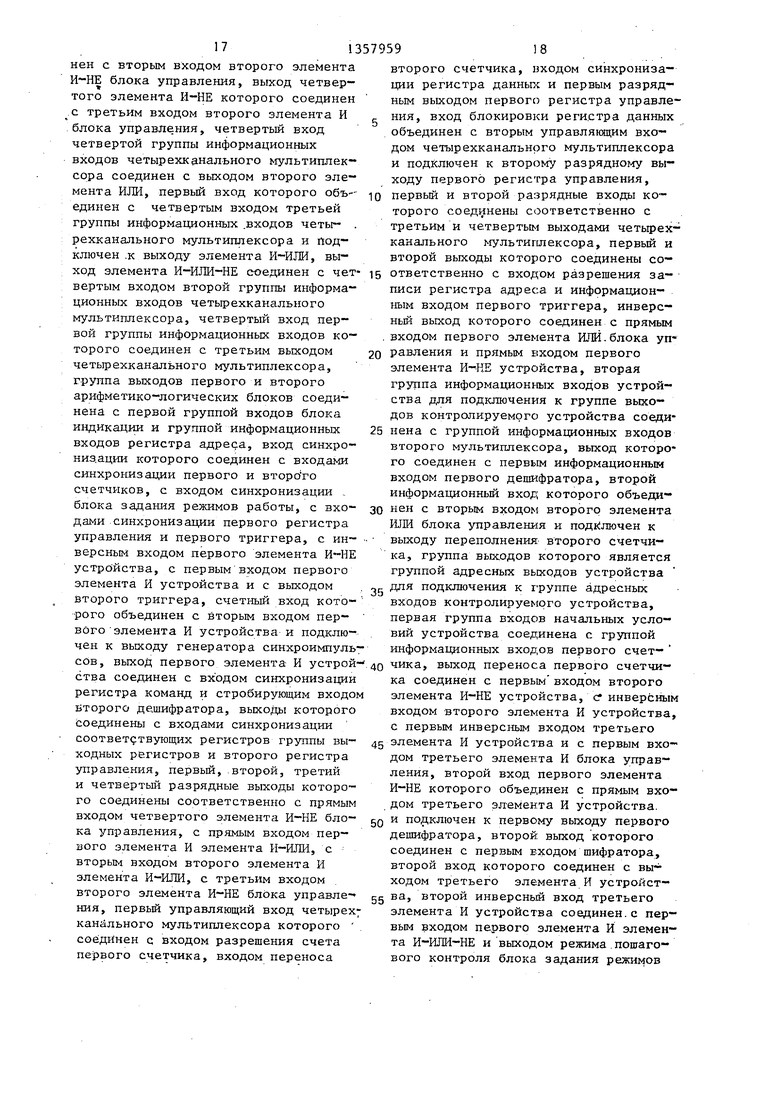

Блок управления, (фиг. 2) содержит элемент НЕ 42, четырехкан 5(льньй мультиплексор 43, элемент И-ИЛИ 44, элементы И 45 и 46, элементы И-НЕ 47-50, элементы ИЛИ 51 и 52, элемент И-ИЛИ-НЕ 53, элемент НЕ 54. ; Блок 17 задания режимов работы содержит RS-триггеры 55 и 56, D- триггеры 57-59, переключатели 60

кронного типа: изм нение состояния в них происходит по переднему фронту синхроимпульса. Регистр 6 имеет независимое управление для двух групп разрядов: одна группа разрядо управляется по переднему, а другая группа разрядов по заднему фронту синхроимпульсов. Все кнопки показаны в отпущенном состоянии.

Устройство в зависимости от поло жения Х и Х, переключателей 60 и 6 работает следующим образом.

Контроль и набор программ (Х, Xj, о). Оба переключателя 60 и 61 находятся в нижнем положении: на вы ходе элемента 54 вырабатывается, низ кий уровень, которым регистр 8 уста навливается в состояние .О. Тригге

25

30

и 61 режима, кнопку 62 Пуск, кноп- gg гер 55 возвращается в состояние О

59 при этом находится в состоянии О, формируя на управляющем входе дешифратора 18 запрет, в результате чего на всех выходах устанавливаетс высокий уровень. Вычитающий счетчик 11 находится в состоянии О, в ког тором на выходе переноса формируетс низким уровнем сигнал переноса, что приводит к созданию запрет а на вход элемента 26 и разреше шя на входе элемента 24. При нгшатии кнопки 62 перехода триггера 55 в состояние на. выходе элемента 28 появляется низкий уровень, задающий в счетчик 11 режим предустановки, а в шифрат

35 ре 16 коды операции логического нуля для АЛБ 1 и операции пересылки с входа 41 для АЛБ 2. В результате на входе регистра 3 появляется началь- ньй адрес программы, в котором груп

40 младших разрядов, определяемая АЛБ I, постоянно оказывается замещенной нулями. При этом, поскольку регист 8 в данном режиме постоянно удерживается, в состоянии О, в мультипл

45 соре 43 происходит подключение вход с нулевым номером и низкий уровень сформированный на вьгходе триггера 55, через элемент Л6 разрешает запи в регистр 3. По фронту следукяцего синхроимпульса в счетчик 11 захшсы- вается установленньй на входе 40 н чальный адрес, а в регистре 3 - на- чальньй адрес программы.

После отпускания: кнопки 62 тригiin

50

ку 63 Счет, кнопку 64 Запись, элемент 65, элемент И 66.

Все счетчики и D-триггера, а также, регистры, кроме регистра 6, син-

и на выходе элемента 28 появляется высокий уровень, устанавливающий в счетчике 1I режим счета, а в шифраторе 16 код операции счета, после

кронного типа: изм нение состояния в них происходит по переднему фронту синхроимпульса. Регистр 6 имеет независимое управление для двух групп разрядов: одна группа разрядов управляется по переднему, а другая группа разрядов по заднему фронту синхроимпульсов. Все кнопки показаны в отпущенном состоянии.

Устройство в зависимости от положения Х и Х, переключателей 60 и 61 работает следующим образом.

Контроль и набор программ (Х, О Xj, о). Оба переключателя 60 и 61 находятся в нижнем положении: на выходе элемента 54 вырабатывается, низкий уровень, которым регистр 8 устанавливается в состояние .О. Триггер

гер 55 возвращается в состояние О

59 при этом находится в состоянии О, формируя на управляющем входе дешифратора 18 запрет, в результате чего на всех выходах устанавливается высокий уровень. Вычитающий счетчик 11 находится в состоянии О, в ког- тором на выходе переноса формируется низким уровнем сигнал переноса, что приводит к созданию запрет а на входе элемента 26 и разреше шя на входе элемента 24. При нгшатии кнопки 62 и перехода триггера 55 в состояние .- на. выходе элемента 28 появляется низкий уровень, задающий в счетчике 11 режим предустановки, а в шифраторе 16 коды операции логического ну . ля для АЛБ 1 и операции пересылки с входа 41 для АЛБ 2. В результате на входе регистра 3 появляется началь- ньй адрес программы, в котором группа

младших разрядов, определяемая АЛБ I, постоянно оказывается замещенной нулями. При этом, поскольку регистр 8 в данном режиме постоянно удерживается, в состоянии О, в мультиплексоре 43 происходит подключение входа с нулевым номером и низкий уровень, сформированный на вьгходе триггера 55, через элемент Л6 разрешает запись в регистр 3. По фронту следукяцего синхроимпульса в счетчик 11 захшсы- вается установленньй на входе 40 начальный адрес, а в регистре 3 - на- чальньй адрес программы.

После отпускания: кнопки 62 тригiin i

гер 55 возвращается в состояние О

и на выходе элемента 28 появляется высокий уровень, устанавливающий в счетчике 1I режим счета, а в шифраторе 16 код операции счета, после

чего по каждому синхроимпульсу сос- тояии е счетчика 11 уменьшается на единицу, а состояние регистра 3 уве- личивается на единицу. При достижении в 11 состояния О формируется низким уровнем сигнал переноса, который создает запрет на входе элемента 26, что приводит к снятию разрешения переноса и прекращению счета в рассматриваемом счетчике. При этом . сигнал переноса на выходе счетчика 11 при его остановке сохраняется. Остановка счетчика 1I приводит к появлению запрета на входе элемента 50 и далее через элементы 46 и 43 к формированию высоким уровнем запрета записи в регистр 3. При последующем нажатии кнопки 63 Счет осуществляется запуск через противодребезговьгй триггер 56 генератора одиночных им пульсов, собранного на триггерах 57 и 58 и снятие в элементе 46 на время действия одного такта запрета на запись в регистр 3. В результате в регистре 3 происходит запись следующего адреса, отличающегося от предьщу- щего на единицу. Таким образом, осуществляется пошаговый контроль программы. При необходимости вы гюлнения записи в блок 4 по текущему адресу из регистра 3 нажимается кнопка 64 и на вькоде элемента 65 вырабатывается низким уровнем сигнал записи. В процессе пошагового контроля, когда счетчик 11 достигает состояния О и кнопка 62 оказывается отпущенной и на .шинах 17 и i 7 действуют соответственно низкий и высокий уровни на выходах элементов 23 и 28 устанавливается состояние 1,,3адающее в шифраторе 16 для АЛБ 1 код операции передачи группы мпадших разрядов, а для АЛБ 2 - код операции вычитания. В результате на индикацию в блок 30 поступает значение относительного адреса смещения относительно начального адреса программы. Причем этот адрес в регистре 3 не запоминаетс я, поскольку на вьЬсоде элемента 46 вырабатывается высоким уровнем запрет записи в этот регистр.

Интегральный контроль (Х, О, Xj 1). Режим обеспечивает групповую перегрузку информации из блока 4 памяти через выход- 32 в контролируемый цифровой узел - абонент, где она запоминается и далее в зависимости от вида абонента может быть либо,

считана обратно, как, например, в случае контроля ОЗУ, либо используется в абоненте в качестве данных или программной информации. Порядок работы в рассматриваемом режиме описывается диаграммой переходов f,Z,Y,V g

10

где 1 - Y

X, и Х

-признаки настройки, загружаемые перед на- .чалом работы из блока 4 в регистр 7;

-задаюш е режим признаки;

Т - признак на входе 38,

характеризующий низким уровнем занятость выходной магистрали 32;

W - квитанция о пригеме данного, поступающая от абонента на вход 39; Z, и Zj - состояния триггеров 55 и 58 соответственно;

ZJ - сигнала переноса в счетчике 10;

S- - состояния регистра 8, закодированные согласно табл. 1.

Таблица 1

Состояния

LA..I

8,

40

45

Состояни е БО - начальное. В нем 50 осуществляется управление только подачей синхроимпульсов для абонента. Управление выполняется в зависимости от состояния Y разряда 7 в регистре 7. Если Y4 0, то на выходе эле- 55 мента 49 вьфабатывается состояние О, триггер 12 устанавливается в состояйие О и на выход 33 устройства через элемент 27 начинают непре- |.рывно поступать синхроимпульсы, формируемые счетным ТЕ иггером 13. В случае if 1 триггер 12 имеет исходным состояние 1, в котором элемент 27

1357959б

ра 8: по заднему фронту в момент перехода в состояние Si 17роизводится

закрыт. При нажатии кнопки 63 на выходе -ьриггера 58 вырабатывается оди- ночньш импульс, который, проходя через элементы 51, 47, 49 и 43, задает на D-входе триггера 12 состояние О. В следующем такте триггер 12. переходит в состояние О. При этом ввиду окончания действия указанного импульса на выходе элемента 51 появляется состояние 1, которое, через такт вновь устанавливается в триггере 12. Таким образом, по каждому нажатию кнопки 63 в абонент поступает один синхроимпульс.

Переход в состояние S, выполняется при нажатии кнопки 62 на фазе установки начального адреса A. программы и наличия в случае Y, 1 дополнительного условия Т 1. При Y, О проверка условия Т не требуется, В состоянии S, регистр 8 пребывает, пока нажата кнопка 62 (Z, 1). При этом из блока 4 считывается первое слово программы. Одновременно низким уровнем, действующим на инверсно выходе триггера 55, про; сходит задание в-счетчике 10 режима предустановки, что приводит к записи в данный счетчик с входа 36 по ближайшему синхроимпульсу граничного значения счета. Кроме того, в состоянии S, подготавливается переход триггера 12 в- состояние 1, если он до этого на- ходипся в состоянии О, путем под- кл1очения шины питания через вход 2. Z мультиплексора 43 на D-вход данного триггера. При отпускании кнопки 62 регистр 8 в следующем такте переходит

запись первого слова, а по переднему с фронту в момеит перехода в состояние

Sg второго слова. Состояние S

вместе

с состоянием используется также для формирования разрешения счета в счетчиках 10 и 11 (каждое низким уровнем).

10 В качестве такого разрешения берется состояние того же разряда 8, . Поскольку в состоянии Sj на все:Х выходах дешифратора 18, благодаря наличию запрета на его стробирующем вхо15 де, действует высокий уровень, в

том числе на выходе 185., Это является разрешением счета в счетчике 10 и последний в момент перехода в состотг ,

20

яние S, уменьшает свое состояние на

Одновременно в состояние

J, осуществляется подготовка к пере- 12 в состояние О

единицу .3

ходу триггера 12 в состояние путем подключения к D-входу названного триггера через 1 Z - вход об- 25 щей шины. Переход из состояния Sj производится в зависимости от значений признаков Yj и Y, согласно которым можно выделить следующие четыре подрежима.

в состояние S

2

устанавливается в состояние 1

в котором триггер

11,4

еще через такт происходит переход в состояние Sj.

В состояниях S и Sj пр оисходит . запись в регистр 6 из блока 4 перво го и второго слов. В результате происходит двукратное увеличение длины выходного слова в сравнении с длиной слов в блоке 4. При необходимости использования на выходе 32 более длинных слов при неизменной длине слов в блоке 4 число рабочих состояний в ре- gg- гистре 8 должно быть соответствующим образом увеличено. Запись в регистр 6 производится по фронтам изменения состояния первого разряда 8( регист30 I. Автоматический синхронный вывод (У О, Y, о). На выходе эле-- мента 44 вырабатывается состояние О,, задающее первый разряд 8, в коде следующего состояния S . Второй

35 разряд ,8 этого состояния определяется в зависимости от состояния счетчика 1.0: если счетчик 10 находится в состоянии О, то он вырабатывает низким уровнем перенос (Zj О),

40 что приводит к появлению на выходе элемента 52 состояние О и переходу в следующем такте регистра 8 в состо- 12 яние.З . Если же счетчик 10 еще не L достиг состояния О, то на выходе

45 элемента 52 формируется состояние 1 и регистр 8 переходит в состояние S, ,

II. Автоматический асинхронньш вы- 50 вод (Y О, Yj 1). Здесь производится дополнительная проверка нали- - чия квитанции. Если квитанция отсут ствует (W 1}, то на выходах элементов 44 и 52 оказываются состо.яния 1 и регистр 8 остается в прежнем, состоянии S,. При поступлении квитанции от абонента (W О) переход из Sj происходит по той же схеме, что и в подрежиме I. ,

запись первого слова, а по переднему фронту в момеит перехода в состояние

Sg второго слова. Состояние S

вместе

с состоянием используется также для формирования разрешения счета в счетчиках 10 и 11 (каждое низким уровнем).

В качестве такого разрешения берется состояние того же разряда 8, . Поскольку в состоянии Sj на все:Х выходах дешифратора 18, благодаря наличию запрета на его стробирующем входе, действует высокий уровень, в

том числе на выходе 185., Это является разрешением счета в счетчике 10 и последний в момент перехода в состотг ,

0

яние S, уменьшает свое состояние на

Одновременно в состояние

J, осуществляется подготовка к пере- 12 в состояние О

единицу .3

ходу триггера 12 в состояние путем подключения к D-входу названного триггера через 1 Z - вход об- 5 щей шины. Переход из состояния Sj производится в зависимости от значений признаков Yj и Y, согласно которым можно выделить следующие четыре подрежима.

II. Автоматический асинхронньш вы- вод (Y О, Yj 1). Здесь произвоится дополнительная проверка нали- - чия квитанции. Если квитанция отсут ствует (W 1}, то на выходах элементов 44 и 52 оказываются состо.яния 1 и регистр 8 остается в прежнем, состоянии S,. При поступлении квитанции от абонента (W О) переход из Sj происходит по той же схеме, что и в подрежиме I. ,

III, Пошаговый синхронньй вывод

(YJ 1, Yj о). При наличии признака нового шага (Z 1) и состояния О в счетчике 10 (Z, О) на выходах элементов 44 и 52 вырабатывает- ; ся состояние О и в следующем такте регистр 8 устанавливается в состояние S.. По окончании действия одиночного импульса на выходе триггера 58 (Z о) на выходах элементов 44 и 52 появляется состояние 1 и в следующем такте регистр 8 остается в состоянии Sj, При нажатии кнопки 63 и любом состоянии в счетчике 10, отличном от нуля, на выходах элемент тов 44 и 52 формируются состояния О и соответственно, что приводит к переходу в следующем такте регистра 8; в состояние S.

IV. Пошаговый асинхронный вывод (Y 1J Yj 1). В этом подрежиме в случае одновременного наличия признаков Zj 1 и W О на выходе элемента 44 формируется состояние О переход выполняется по схеме подежима I. Если же хотя бы одно из названных условий не выполняется, то на выходах элементов 44. и 52 выабатываются состояния 1 и независимо от состояния счетчика 10 регистр 8 остается в состоянии Sj.

В подрежимах I - III триггер 12 аходится в состоянии О и разрешает в элемент 27 выдачу синхроимпульсов, пока регистр 8 находится в состоянии Sj. Переход в состояние Вг сопровожается одновременно установкой в

ИР 7 О ИР 0

tf, о 1

tfN .1

ИР о, (f „ 1

РК + 1 РК + 1

РК + 1 РК РК + 1

РК - М РК + 1 РК

триггере 12. состояния 1, выработанного элементом 53. В подрежиме IV переход триггера 12 совершается после получения первой квитации от абонента, т.е. переход триггера 12 в состо - яние 1 не обязательно сопровождает-- ся переходом регистра 8 в состояние SjCSg), который теперь определяется

дополнительным условием - нажатием кнопки 63.

Дифференциальный контроль (Х 1, Xj 0). На каждом такте работа контролируемого узла Vопределяется инфор-

мационным словом, записываемым в ре- гистры 5;. При этом в отличие от j предьщущего режима, в котором происходит безусловная замена всего управляющего слова, здесь может происхо-

дить частичная замена отдельных фрагментов старого управляющего слова с учетом реакции контролируемого узла на предыдущее управляющее слово. Работа в рассматриваемом режиме, как и

в предыдущих режимах, начинается с нажатия кнопки 62 и установки в регистре 3 начального адреса программы. После отпускания кнопки 62 и возврата триггера 55 в состояние 1, а

также установки в счетчике 11 режима счета дальнейшая работа устройства определяется уже командой, считываемой из блока 4 памяти и имеющей вид MNU. Фрагментам М, N и U команды

соответствуют группы разрядов 4, 4 и 4з. В табл. 2 приведен состав и содержание различных операций U, , реализованных в устройстве.

аблица 2

1 1 о

о о

М М

М

Примечание. РК- регистр 3 команд, ИР - индексньш счетчик 10, ТС - триггер 12 синхронизации. Р., - регистр 5 .

Пустая операция U. На выходах 18, 18 дешифратора 18; действует од .01 1 1 X О О (Х - ;безразличное остояние). В результате на выходе ешифратора 16 появляется код операии счета А + 1, а на выходе элемента 50 и далее выходе элемента 46 - азрешение записи низким уровнем, что приводит в следующем такте к записи в регистр 3 состояния А +. 1 , Кроме того, на выходе элемента9 вырабатывается состояние 1, которое и устанавливается, в :следук щем такте в триггере 12, что .приводит к запрету на следующем такте прохождения через элемент 27 очерёдного синхроимпульса. Таким образом цепочка из Команд с операцией U позволяет автоматически проходить неиспользованные ячейки в блоке 4 в процессе перехода к следующей программе.

Загрузка управляющего фрагмента промежуточная U,. Код на выходах 18 -, О 1 ГХ О Ь В результате, как и при Uj в следующем такте в регистре 3 оказывается записанным адрес следующей ячейки.Дополнительно ь текущем- такте на в-ыходе элемента 22 вырабаты- вается строб, по которому на одном из входов дешифратора 19 появляется низким уровнем сигнал, являющийся синхросигналом для соответствующего регистра 5; . В итоге в по следний по заднему фронту строба оказывается записанным поле М текущей команды. При формировании строба используется синхросигнал.непосредственно с выхода генератора 31, что связано с чф бованием отсутствия запаздывания

Продолжение табл.2

в регистре i5; рабочего фронта синхросигнала относительно смены информации в блоке 4.

Операция U, используется при необходимости смены информации одновременно в нескольких регис.трах. Такая смена производится последовательно, причем смена в последнем из регистров 5; должна осуществляться уже с другим

кодом операции,

Загрузка управлякяцего фрагмента конечная U,,. Код на выходах 18 -

1 1 1X01. Операция аналогична U, но блокировка синхроимпульсов в элемент 27 не производится. Операция

используется при смене информации для следукяцего шага контроля только в одном из регистров 5; , либо пр и смене информации в последнем из регистров 5;.

цепоч1си

40 Загрузка с торможением, перехода к следующей команде U,. Код на выходах 18; - 1 1 Z, X I 1,

-где

Z, со

стояние на выходе переноса в счетчике 10. Операция аналогична U, одна45 ко переход к следующей команде задерживается до появления в счетчике 10 состояния о, по достижении которого на выходе 182 устанавливается состояние ; . В результате на выходе эле5Q мента 50 появляется низким уровнем разрешение перехода регистра 3 в соседнее состояние РК + 1. Если состояние в счетчике 10 еще не достигнуто, то состояние 1 на выходе 18j

gg сохраняется, и сохраняется высоким уровнем сигнал блокировки на шине 154, препятствующий записи в регистр 3 нового состояния. Состояние счетчика 10 в течение указанной блокировки

в каждом такте благодаря разрешению счета на выходе 18 уменьшается на единицу. Операция Uj может исполь- ;3оваться, например, при контроле ОЗУ во все ячейки которого должен быть по одной команде занесен один и тот же код М.

Условный переход Uy.Код на выходах 18, - 1 1 1 00, где tf; - значение условия на инфopмaциpннJOм входе 37, поступающее.на вход дешифратора 18 через мультиплексор 20, выбором канала в котором управляет поле N команды. Если условие перехода не выполнено (Jf о), то шифратор 16 вырабатывает для АЛБ 1 и 2 код операции вычитания, в процессе выполнения которой из текущего значения содержимо- . значением временного отсчета, посту20 пающего на вход 42;. В качестве формирователя таких временных отсчетов может быть использован счетчик 10, если группу разрядов на его выходе 34 соединить с одним из входов 42;.

го регистра 3 вычитается содержимое поля М. Тем самым производится воз- врат назад на М ячеек в блоке 4. При выполнении условия перехода ( 1) шифратор 16 вырабатывает код операции

20 пающего на вход 42;. В качестве ф мирователя таких временных отсчето может быть использован счетчик 10, если группу разрядов на его выходе 34 соединить с одним из входов 42;

счета и в следующем такте происходит 25 При достижении отсчета с заданным

номером на выходе 18j формируется стояние 1 и соответственно разре ние для перехода регистра 3 в сосе нее состояние. Одновременно выраба

переход регистра 3 в соседнее состояние РК + 1. Операция может использо ваться при организации циклического повторения определенной группы проверок в контролируемом узле.

Контроль данных Uy. Код на выхо- дах 1В; - 1 I qii-Z, О, где tf; - результат сравнения данного на входе 42; с полем М команды. Результат сравнения с выхода компаратора 14 поступает на вход мультиплексора 20 с нулевым адресом. Формирование нулевого адреса для данной операции происходит автоматически путем блокировки в блоке 29 элементов И адресйо- 40 го входа сигналом, действующим на выходе 18 дешифратора команд. Сравнение осуществляется в течение М тактов, число которых предварительно устанавливается (во время установки 45 начального адреса программы) в счетчике 10. В течение первых М-1 тактов на выходе 18, всегда действует состояние О, что приводит к запрету смены состояния в регистре 3 и счет- 50 чике 11. Если при этом все время выполнялось условие 1, то счетчик 10 благодаря действию разрешения на выходе 18с постоянно уменьшает свое содержимое до нуля и на М-м такте 55 опять же при выполнении условия lf 1 происходит разблокировка элемента 50 и регистр 3 переходит в соседнее состояние РК+1. Аналогично в

30

gg

соседнее состояние перейдет и счетчик 11. Если на любом из М тактов условие tf; 1 не выполнено, то на выходе 18 формируется низкий уровень, которым осуществляется остановка счетчика 10, а вместе с ней и фиксация данного на входе 42;, которое в контролируемом узле является

функцией состояния счетчика 10. Операция иу может быть выполнена, напри- мер, при контроле состояния ячеек ОЗУ, заполненного ранее с применением операции

Задержка Ug. Код на выходах 18; - 1 1 tp; 0X0. Значение задержки задается полем М команды, которое сравнивается в компараторе 14 с текущим

значением временного отсчета, поступающего на вход 42;. В качестве формирователя таких временных отсчетов может быть использован счетчик 10, если группу разрядов на его выходе 34 соединить с одним из входов 42;.

номером на выходе 18j формируется состояние 1 и соответственно разрешение для перехода регистра 3 в соседнее состояние. Одновременно вырабатывается разрешение для .перехода в следующее состояние счетчика 11. Операция и может использоваться перед контролем данных, поступающих из контролируемого узла с определенной

задержкой,относительно предыдущей команды устройства.

В табл. 3 приведена выходная функция шифратора 16.

Таблица 3

-1

А+С

А-В .

В табл. 4 приведена кодировка ПЗУ, используемого в качестве одного из вариантов при реализации дешифратора 18 команд.

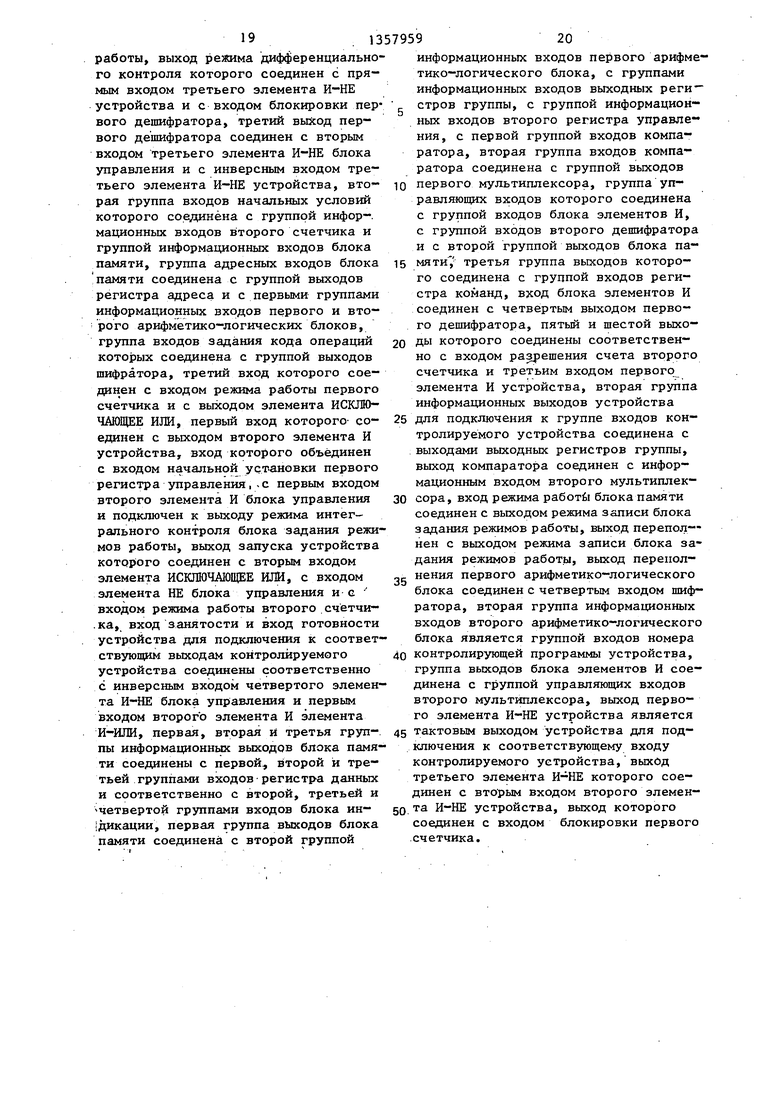

Временная диаграмма устройства показана в режиме интегрального контроля и асинхронном автоматическом режиме. В момент t, на выходе 17 формируется низким уровнем сигнал пуска - установка начального адреса. По фронту следующего синхроимпульса регистр 8 переходит в состояние S , а в регистре 3 устанавливается начальный адрес А. После отпускания кйопки (момент t2) по фронту следующего синхроимпульса регистр 8 переходит в состояние S , а в регистр 6 записывается первое слово. Регистр 3 при этом устанавливается в следующее состояния А+1, что приводит к началу выврда из блока 4 второго слова. Ещ.через такт (момент t) в регистр 6 записывается второе слово, а регистр 8 переходит в состояние Sj. Через полтакта после перехода в состояние S,, поступает ответ 39 о приеме контролиТабл.ица 4,

О 1 1

1 1

О О

о о о о о о

0

5

руемым узлом управляющего слова, что приводит еще через полтакта,к установке .триггера . 12 в состояние 1 и блокировке синхроимпульсов в элементе 27. В момент t -поступает оигнал 17, через такт происходит переход в сое - тояние Sj и выборка нового управляющего слова. Вывод нового слова начинается в момент t, однако ответ 39 о его приеме поступает с задержкой . в момент tg. До этого момента триггер. 12 остается в состоянии О и на выход 33 непрерывно поступают синхроимпульсы. После поступления очередного сигнала. П происходит переход в состояние S , поскольку счетчик 10 к этому моменту уже достиг состояния О.

Таким образом.в сравнении с извег. стным устройством введение программных средств позволило осуществить гибкий и разнообразный контроль. При5

15

чем допускается использование команд в различных представлениях,,что позволяет контролировать цифровые блоки с самыми разнообразными средствами управления, начиная с блоков, полностью лишенных таких средств, и кончая блоками, имеющими в своем составе полностью законченные схемы обмена.

Формула изобретения

Устройство для контроля цифровых узлов, содержащее первый мультиплексор, блок задания режимов работы, регистр адреса, первый и второй де- щифраторы, регистр команд, компаратор, первый счетчик,, регистр данных, первый и второй регистры управления, блок индикации, генератор синхроимпульсов, блок управления, причем первая, группа информационных входов устройства для подключения к группе вы-

ходов контролируемого устройства сое- 25 к шине потенциала логического нуля

чинена с группой входов первого мультиплексора, группа выходов регистра команд соединена с группой информационных входов первого .дешифратора, группа выходов регистра данных явля-

.ется первой группой информационных выходов устройства для подключения к группе входов контролируемого устройства, отличающееся ;тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения контроля цифровых узлов с внутренними средствами программного управления, введены шифра- .тор, два арифметико-логических блока, блок памяти, группа выходных регистров, блок элементов. И, второй мультиплексор,. второй счетчик, два триггера, три элемента И, три элемента И-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем блок управления содержит четырехканальньй мультиплексор, элемент НЕ, элемент И-ИЛИ, два элемента И, четыре элемента И-НЕ, два элемен та ИЛИ, элемент И-ИЛИ-НЕ, инверсный вход, первого элемента И блока управления соединен с прямым входом первого элемента И элемента И-ИЛИ, инверсный вход первого элемента И которого соединен с первым входом первого элемента И элемента И-.ИЛИ-НЕ с инверсным входом первого элемента Или и инверсным входом первого элемента И блока управления, выход пер-

10

5795916

вого элемента И блока управления сое-; динен с первым входом первой группы информационных входов четырехканаль- ного мультиплексора, первьй вход ; второй группы информационных входов которого соединен с выходом первого элемента И-НЕ блока управления, пер- вьш вход первого элемента И-НЕ которого соединен с выходом второго элемента И-НЕ блока управления, первьй вход второго элемента И-КЕ которого соединен с первым входом второго элемента И блока управления, выход второго элемента И которого соединен с первым входом третьей группы информационных.входов четырехканаль- ного мультиплексора, первьй вход четвертой группы информационных входов которого объединен с вторым входом второй группы информационных входов, вторым и третьим входами первой группы информационных входов четырехка- нального мультиплексора и подключены

15

20

5

0

устройства, второй вход третьей группы информационных входов четырехка- нального мультиплексора объединен с вторым входом четвертой группы ин- 0 формационных входов, третьим входом второй группы информационных входов четырехканального мультиплексора и подключен к.шине потенциала логической единицы устройства, третий вход третьей группы информационньсс входов четырехканального ryльтиплeкcopa объединен с вторым входом второго элемента И блока управления и подключен к выходу элемента НЕ, вход . которого соединен с третьим входом четвертой группы.информационных входов четырехканального мультиплексора и с первьм входом первого элемента И блока управления, второй вход первого элемента И которого соединен с выходом третьего элемента И-НЕ блока управления, первьй вход второго элемента И элемента И-ИЛИ которого объединен с первым входом второго эле- 0 мента И элемента И-ИЛИ-НЕ, второй вход второго элемента И которого соединен с вторым входом первого элемента И элемента И-ИЛИ-НЕ и вторым входом BTOisoro элемента И элемента 5 И-ИЛИ, третий вход первого элемента И элемента И-ИЛИ-НЕ соединен с третьим вхбдом второго элемента И элемента И-ИЛИ-НЕ и с входом первого элемента ИЛИ, выход которого соеди-

5

17

ен с вторым входом второго элемента -НЕ блока управления, выход четвертого элемента И-НЕ которого соединен с третьим входом второго элемента И блока управления, четвертый вход четвертой группы информационных входов четырехканального мультиплек сора соединен с выходом второго эле мента ИЛИ, первьш вход которого объ-- единен с четвертым входом третьей группы информационных .входов четы . рехканального мультиплексора и Подключен .к выходу элемента И-ИЛИ, выход элемента И-ИЛИ-НЕ соединен с четвертым входом второй группы информационных входов четырехканального мультиплексора, четвертый вход первой группы информационных входов которого соединен с третьим выходом четырехканального мультиплексора, группа выходов первого и второго арифметико-логических блоков соединена с первой группой входов блока индикации и группой информационных входов регистра адрера, вход синхро- низ.ации которого соединен с входами синхронизации первого и второ го счетчиков, с входом синхронизации . блока задания режимов работы, с входами синхронизации первого регистра управления и первого триггера, с ин- вареным входом первого элемента И-НЕ устройства, с первым входом первого элемента И устройства и с выходом второго триггера, счетный вход кото- рого объединен с вторым входом пер- вОго элемента И устройства и подключен к выходу генератора синхроимпульсов, выход первого элемента И устрой- ства соединен с входом синхронизации регистра команд и стробирующим входом второго дешифратора, Bbixo;yji которого соединены с входами синхронизации соответствующих регистров группы выходных регистров и второго регистра управления, первьй, .второй, третий и четвертый разрядные выходы которого соединены соответственно с прямым входом четвертого элемента И-НЕ блока управления, с прямым входом первого элемента И элемента И-ИЛИ, с вторьм входом второго элемента И элемента И-ИЛИ, с третьим входом второго элемента И-НЕ блОка управления, первьй управляющий вход четырех канального мультиплексора которого соединен с входом разрешения счета первого счетчика, входом переноса

- . ьй-и ом о мх

10

15

20

25

357959 8

второго счетчика, входом синхронизации регистра данных и первым разряд- ньм выходом первого регистра управления, вход блокировки регистра данных объединен с вторым управлянндим входом четырехканального мультиплексора и подключен к второму разрядному выходу первого регистра управления, первьй и второй разрядные входы которого соединены соответственно с третьим и четвертым выходами четырехканального мультигшексора, первьй и второй выходы которого соединены соответственно с входом ра.зрешения записи регистра адреса и информационным входом первого триггера, инверс- ньй выход которого соединен с прямым входом первого элемента ИЛИ.блока управления и прямым входом первого элемента И--НЕ устройства, вторая группа информационных входов устройства для подключения к группе выходов контролируемого устройства соединена с группой информационных входов второго мультиплексора, выход которого соединен с первым информационным входом первого дешифратора, второй информационньй вход которого объеди30 нен с вторым входом второго элемента ИЛИ блока управления и подключен к выходу переполнения второго счетчика, группа выходов которого является группой адресных выходов устройства для подключения к группе адресных входов контролируемого устройства, первая группа входов начальных условий устройства соединена с группой информационных входов первого счет-

40 чика, выход переноса первого счетчика соединен с первым входом второго элемента И-НЕ устройства, cf инверсным входом второго элемента И устройства, с первым инверсным входом третьего

45 элемента И устройства и с первым входом третьего элемента И блока управления, второй вход первого элемента И-НЕ которого объединен с прямым входом третьего элемента И устройства.

5Q и пор,ключен к первому выходу первого дешифратора, второй выход которого соединен с первым входом шифратора, второй вход которого соединен с вы- ходом третьего элемента И устройст-

gg ва, второй инверсный вход третьего элемента И устройства соединен.с первым входом первого элемента И элемента и выходом режима.пошагового контроля блока задания режимов

35

работы, выход режима дифференциального контроля которого соединен с прямым входом третьего элемента И-НЕ устройства и с входом блокировки первого дешифратора, третий выход первого дешифратора соединен с вторым входом третьего элемента И-НЕ блока управления и с инверсным входом третьего элемента И-НЕ устройства, вторая Группа входов начальных условий которого соединена с группой инфор-. мационных входов второго счетчика и группой информационных входов блока памяти, группа адресных входов блока памяти соединена с группой выходов регистра адреса и с первыми группами информационных входов первого и второго арифметико-логических блоков, группа входов задания кода операций которых соединена с группой выходов шифратора, третий вход которого соединен с входом режима работы первого счетчика и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первьй вход которого- соединен с выходом второго элемента И устройства, вход которого объединен с входом начальной установки первого регистра управления,,с первым входом второго элемента И блока управления и подключен к выходу режима интегрального контроля блока задания режимов работы, выход запуска устройства которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с входом элемента НЕ блока управления и с входом режима работы второго счетчи- .ка, вход занятости и вход готовности устройства для подключения к соответ- ствуюпрш выходам контролируемого устройства соединены соответственно с инверсным входом четвертого элемента И-НЕ блока управления и первым входом второго элемента И элемента И-ИЛИ, первая, вторая и третья группы информационных выходов блока памяти соединены с первой, второй и третьей группами входов регистра данных и соответственно с второй, третьей и четвертой группами входов блока ин- 1дикации, первая группа выходов блока памяти соединена с второй группой

0

5

0

информационных входов первого арифметико-логического блока, с группами информационных входов выходных регистров группы, с группой информационных входов второго регистра управления, с первой группой входов компаратора, вторая группа входов компаратора соединена с группой выходов первого мультиплексора, группа управляющих входов которого соединена с группой входов блока элементов И, с группой входов второго дешифратора и с второй группой выходов блока памяти , третья группа выходов которого соединена с группой входов регистра команд, вход блока элементов И соединен с четвертым выходом первого дешифратора, пятый и шестой выходы которого соединены соответственно с входом разрешения счета второго счетчика и третьим входом первого элемента И устройства, вторая группа информационных выходов устройства

5 для подключения к группе входов контролируемого устройства соединена с выходами выходных регистров группы, выход компаратора соединен с информационным входом второго мультиплексора, вход режима работб блока памяти соединен с выходом режима залией блока задания режимов работы, выход переполнен с выходом режима записи блока задания режимов работы, выход переполнения первого арифметико-логического блока соединен с четвертым входом шифратора, вторая группа информационных входов второго арифметико-логического блока является группой входов номера

0 контролирующей программы устройства, группа выходов блока элементов И соединена с группой управляющих входов второго мультиплексора, выход первого элемента И-НЕ устройства является

5 тактовым выходом устройства для подключения к соответствующему входу контролируемого устройства, выход третьего элемента И-НЕ которого соединен с вторым входом второго элемен-

0 та И-НЕ устройства, выход которого соединен с входом блокировки первого .счетчика.

0

5

JS,

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

Изобретение относится к вычислительной технике и может быть использовано при настройке paзpaбaтывae «llx и контроле серийно выпускаемых цифровых узлов. Цель изобретения - расширение функциональных возможностей устройства за счет контроля цифровых узлов с внутренними средствами программного управления и без таковых. Устройство содержит два арифметико- логических блока, регистр адреса, блок памяти, группу выходных регистров, регистр данных, два,регистра управления, регистр команд, два счетчика, два триггера, компаратор, блок управления, шифратор, блок задания режимов работы, два дешифратора, два мультиплексора, три элемента И, три элемента И-НЕ, элемент ИСКПЮЧАЩЕЕ Или, блок элементов И, блок индикации, генератор синхроимпульсов, две группы информационных выходов, тактовый выход, группу адресных выходов, две группы информационных входов, вход занятости, вход готовности, две группы входов начальных условий, группу входов номера. Программа контроля хранится в местном блоке памят-. ти. Управление контролируеьаом узлом выполняется в режиме интегрального или дифференциального контроля. В интегральном режиме информация из блока памяти поступает в контролируемый узел через регистр данных. При этом обмен с контролируемым узлом осуществляется в автоматическом или пошаговом подрежиме с использованием или без использования квитанций. Упр эление контролируемыми узлом в режиме дифференциального контроля обеспечивается через группу выходных регистров., Расширение функциональных возможностей достигается путем введения собственных средств программного управления . 4 ил., 4 табл. (О 00 ел со ел со

H

8i 8.

хя

10 18i

Pu&. г

17

i

60

А

Фиг. 3

f ti

lГlJ JПJ JTЛJTЛJlJlJ

S.I .1Д,

да

п,. 1г.

15,

J А

g ХКХ Ф Ф$е901- I Jr,y,

ю I г

X

Составитель И. Иваныкин Редактор И. Шулла Техред Л.Сердюкова Корректор И. Муска

Заказ 6000/50 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035 Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для обнаружения неисправностей цифровых систем | 1979 |

|

SU949659A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1986-01-15—Подача