(21)4746424/24

(22)02.10.89

(46) 07.10.91. Бюл. NJ 37

(71)Пензенский научно-исследовательский электротехнический институт

(72)Г. Н. Чижухин (53)681.325(088.8)

(56) Авторское свидетельство СССР № 1417012, кл. G 06 F 7/50, 1986.

Авторское свидетельство СССР Ns 1524045, кл. G 06 F 7/50, 1987.

(54) ЧЕТЫРЕХВХОДОВОЙ ОДНОРАЗРЯДНЫЙ СУММАТОР

(57) Изобретение относится к вычислительной технике и может использоваться при построении многооперандных арифметических устройств. Цель изобретения -упрощение и повышение быстродействия сумматора. Сумматор содержит элемент 1 сложения по модулю два, элемент И 2, элементы ИЛИ-НЕ 3.1-3.4, элемент ИЛИ-НЕ 4; элемент ИЛИ 5, входы 6.1-6.4. выходы 7.1- 7.3. Элемент ИЛИ 5 может быть выполнен монтажно. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В ДВОИЧНОМ ВОСЬМИРАЗРЯДНОМ ЧИСЛЕ | 1991 |

|

RU2030783C1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1658145A1 |

| Четырехвходовый одноразрядный сумматор | 1986 |

|

SU1374216A1 |

| Устройство для обнаружения модульных ошибок | 1988 |

|

SU1674268A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1575172A1 |

| СУММАТОР КОДОВ "1 ИЗ N" | 1997 |

|

RU2129730C1 |

| Многофункциональный логический модуль | 1985 |

|

SU1290290A1 |

| Многовходовой одноразрядный сумматор | 1988 |

|

SU1730620A1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

С/)

С

о

00 СО

о о

VJ

Изобретение относится к вычислительной технике и может использоваться для построений многооперандных быстродействующих арифметических устройств.

Цель изобретения - упрощение и повышение быстродействия сумматора.

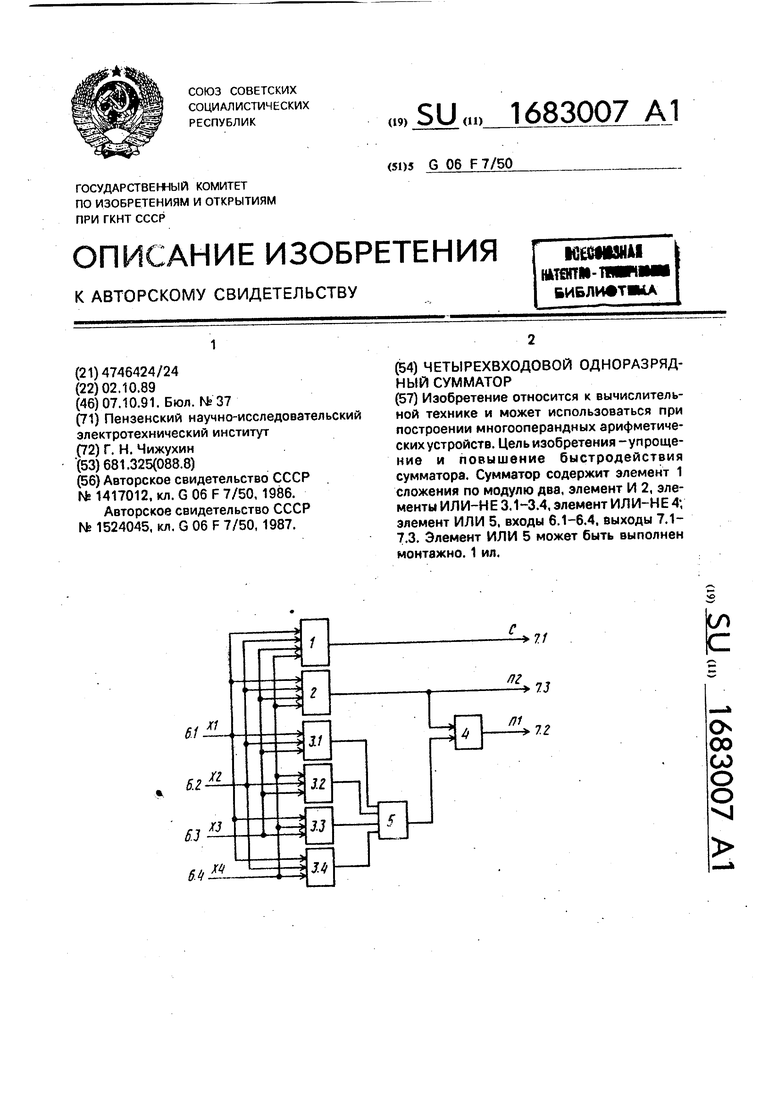

На чертеже представлена функциональная схема сумматора.

Сумматор содержит элемент 1, сложения -модулю два, элемент И 2, четыре трехаходовых элемента ИЛИ-НЕ 3.1-3.4, двухвходовой элемент ИЛИ-НЕ А, элемент ИЛИ 5, входы 6.1-6.4 (для подачи сигналов Х1, Х2, ХЗ, Х4) и выходы 7.1-7.3 (для получения сигналов суммы С, первого разряда переноса П1, второго разряда переноса П2). Элемент ИЛИ 5 может быть выполнен мон- тажно.

Сумматор работает в соответствии со следующими логическими выражениями: С Х1&Х2$ХЗФХ4

А Х2 лХ1/0 4

01

X3 yXT/X2 K4Txi X2 ХЗД Х4. Формула изобретения Четырехвходовой одноразрядный сумматор, содержащий элемент сложения по

модулю два, элемент И и первый элемент ИЛИ-НЕ, причем входы элементе сложения по модулю два и элемента И соединены с входами сумматора с первого по четвертый,

выход элемента сложения по модулю два соединен с первым выходом сумматора, выход первого элемента ИЛИ-НЕ соединен с вторым выходом сумматора, ;ыход элемента И подключен к первому входу первого

элемента ИЛИ-НЕ и к третьему выходу сумматора, отл ичаю щийсятем, что, с целью упрощения и повышения быстродействия, он содержит элементы ИЛИ-НЕ с второго по пятый и элемент ИЛИ, причем первый

вход (1+1)-го элемента ИЛИ-НЕ соединен с i-м входом сумматора ( ,.,,,4), а выход подключен к i-му входу элемента . выход которого соединен с вторым входом первого элемента ИЛИ-НЕ, вторые входы второго

и пятого элементов ИЛИ-НЕ соединение вторым входом сумматора, вторые входы третьего и четвертого элементов ИЛИ-НЕ подключены к четвертому входу сумматора, третьи входы второго и третьего элементов

ИЛИ-НЕ соединены с третьим входов сумматора, третьи входы четвертого и пятого элементов ИЛИ-НЕ подключены к пераому входу сумматора.

Авторы

Даты

1991-10-07—Публикация

1989-10-02—Подача