дьщущим значением, В результате зтого 25 роаналогового преобразователя и яв- на выходе 18 формируется отсчет вы- ляются первыми выходами фильтра, так- ходного сигнала фильтра у (в формате импульсно-кодовой модуляции), который преобразуется цифроаналоговым преобразователем 16 в аналоговую форму y(t) на выходе 19.

Таким образом, в цифровом фильтре с линейной дельта-модуляцией полностью . исключены непроизводительные затраты времени на запись накопленных

30

товый генератор, выход которого соединен со счетными входами реверсивного и первого двоичного счетчиков и первым входом блока формирования импульсов, первый выход которого подключен к входам синхронизапии накапливающих сумматоров, второй двоичный счетчик, элемент ИЛИ-ЫЕ, выход которо го соединен с управляющим входом нуль

значений произведений и задержка вре- 35 типлексора, выход переполнения иервороаналогового преобразователя и яв- яются первыми выходами фильтра, так-

товый генератор, выход которого соединен со счетными входами реверсивного и первого двоичного счетчиков и первым входом блока формирования импульсов, первый выход которого подключен к входам синхронизапии накапливающих сумматоров, второй двоичный счетчик, элемент ИЛИ-ЫЕ, выход которого соединен с управляющим входом нуль

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой фильтр с дельта-модуляцией | 1985 |

|

SU1347188A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

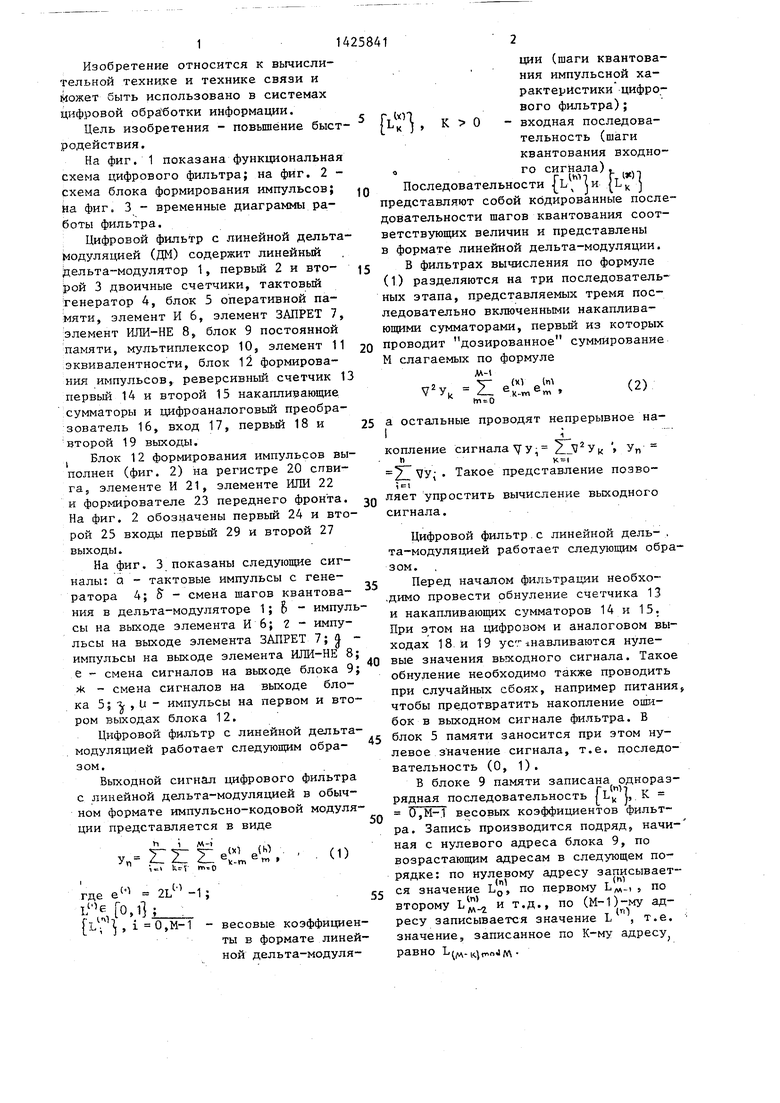

Изобретение относится к вычислительной технике и технике связи. Его использование в системах цкфровой обработки информации позволяет повысить быстродействие цифрового фильтра . Последний содержит линейный дельта-модулятор 1, двоичные счетчики 2 и 3, тактовый генератор 4, блок 5 оперативной памяти, элемент ИЛИ-НЕ 8, блок 9 постоянной памяти, JyльтишIeк- сор 10, элемент 11 эквивалентности, блок 12 формирования импульсов, ре- версивньм счетчик 13, накапливающие сумматоры 14 и 15 и цифроаналоговый преобразователь 16. Благодаря введению элемента И б и элемента ЗАПРЕТ 7 обеспечивается синхронное чтение шагов квантования входного сигнала-и значений импульсной характеристики ф1-шьтра, что уменьшает затраты време- Q ни на вычисление свертки. 1 з.п. ф-лы, 3 ил.

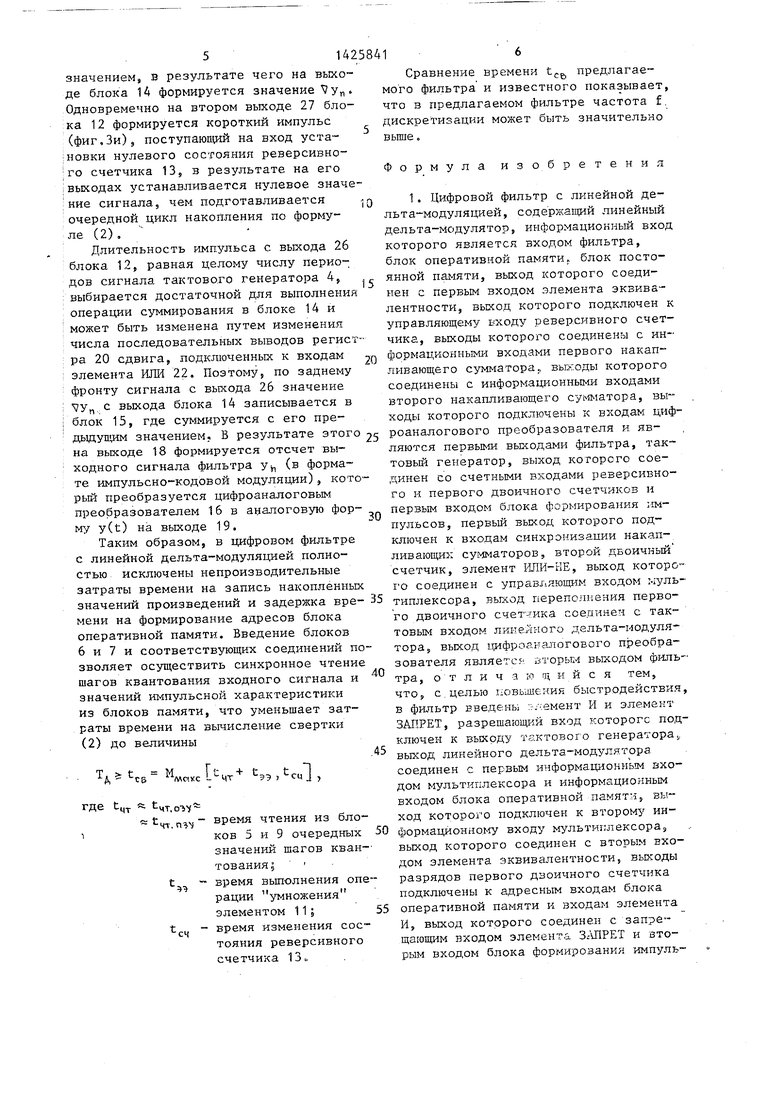

мени на формирование адресов блока оперативной памяти. Введение блоков 6 и 7 и соответствующих соединений позволяет осуществить синхронное чтение шагов квантования входного сигнала и значений импульсной характеристики из блоков памяти, что уменьшает затраты времени на вычисление свертки (2) до величины

, , ) СЦ

Л,

де t4 и; t4T,o-iV

ЧТ.

9Э

-СЧ

время чтения из блоков 5 и 9 очередных 50 значений шагов кван-- тования, время вьшолнения операции умножения элементом 11; 55 время изменения состояния реверсивного счетчика 13„

0

5

0 5

го двоичного счетчика соединен с тактовым входом линейного дельта-модулятора, выход цифроаналогового преобразователя являете зторым выходом фильтра, о т л и ч а ю Ц р и с я тем, что, с.целью повьжеиия быстродействия, в фильтр введены :г. ;емент И и элемент ЗАПРЕТ, разрешающий вход которогс подключен к выходу тактового генератора,., выход лине лного дельта-модулятора соединен с первым информационньтм входом мультиплексора и информационным входом блока оперативной памяти, выход которого подключен к второму информационному входу мьшьтиплексораэ выход которого соединен с вторым входом элемента эквивалентности, вьссоды разрядов первого двоичного счетчика подключены к адресным входам блока оперативной памяти и входам элемента И, выход которого соединен с запрещающим входом элемента ЗгШРЕТ и вторым входом блока формирования импульсов, второй вьтход которого соединен с установочным входом реверсивного счетчика, управляющий вход блока оперативной памяти подключен к выходу элемента ИЛИ-НЕ, выход элемента ЗАПРЕТ соединен с входом второго двоичного счетчика, выходы которого подключены к входам блока постоянной памяти и элемента ИЛИ-КЕ.

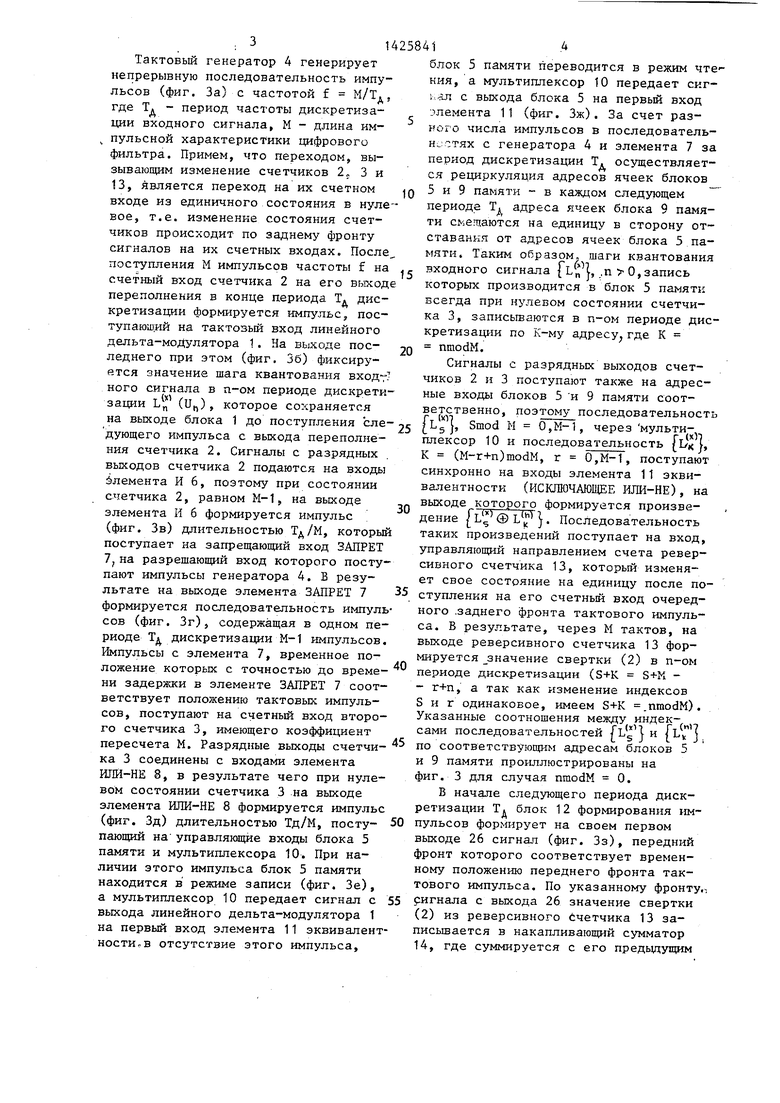

вым входом элемента или, выход перво- го разряда регистра сдвига соединен с первым входом элемента И, второй рход которого объединен с входом син- ;фонизации регистра сдвига и являгт- ся первым входом блока, выходы остальных разрядов регистра сдвига подключены к одноименным входам элемента ИЛИ, выход которого соединен с входом формирователя переднего фронта и является первым выходом блока, ин- формашюнный вход регистра сдвига и выход формирователя переднего фронта являются вторыми соответственно входом и выходом блока .

| Погрибной В.А | |||

| Бортовые системь обработки сигналов | |||

| - Киев: Наукова думка, 1984, с | |||

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Известия ВУЗов | |||

| Сер | |||

| Радиоэлектроника, 1984, т | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Авторское свидетельство СССР №,1347188, кп | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-31—Подача