Изобретение относится к информационно-измерительной технике в частности к устройствам, использующимся для исследования частотных характеристик широкого класса динамических объектов и систем.

Цель изобретения - повышение быстродействия.

Сущность изобретения состоит в том, что сигнал реакции испытуемого объекта на гармоническое воздействие sin опумножа- ется только на cos (in при этом производится два усредняющих интегрирования на двух следующих одним за другим интерваJ п

О)

где Т , а п - целое число большее двух.

лах времени длительностью 2л:

Значение интеграла на первом интервале интегрирования равно

Т/п ai р- А / sin (on + у)cos d t

0

A . , i An

sin if) +

8Л

2 ( ))+cos(P где А - амплитуда сигнала реакции;

(p- фаза сигнала реакции;

ш- частота сигнала реакции; На втором интервале интеграл равен

A

А

2 Т/п

/ sin ( ft t + f) cos fOt dt Т

An

UT

+-ёг1-е(-Г) +

+ cos(+y)

n вообще на 1-том интервале интеграл равен

- А sin - Ап

4Л

a,f s. - cos ( -. ,+(,) +

JV7T п

(l-1 )+

ON 00

Јь

Ю

| J h-f1 sin-r- os (kl --1 )Ачп(/) f чГ Inn v

n , г/1 , 2Я

si,, ji vin-- ( | -- 1 ) Лnn ч

П)

Используя знлчышя итегралог на двух соседних интервалах, потучим систему двух линейных алгебраичес кг уравнений с двумя неизвестнымиIQ С i Л sin./) i d i Acos / - a i Ci iA sin yo t Ji i Л cos уз -пм (2) где

/- 1 i n , 2л2.T , 0 .-.

Ci -r,- I- -Л- sin - - cos - - ( 2i - 1 )

1ОЛтnn V.

2 4т 01М n

2л

di -.- sin sin - i 2i - M 4яnn v

-i Л1

IIi / П 1 V

r- sincos( 2i - Л )

1лnn v

i n , 2/i , 2л .. „ ,, ч

ill - - s ns n - - ( 2i 3 )

4тnn v

,c uoiiHG Koropnti mnoi inp iotio /л cos f пожно эчписшь в виде

a. 0 i - i - a , - i di

Л sin / -r -

с i ri i - 1 - с i - 1 di

Л

,OS /

г, с i -1 i - j с rii с i - i d i - 1 Ci

При Г ольши 3KJ4 пиях 4HCiia n p.ire (.no (3) f ,o/ er ora. cTT en iiet оррекгным из-за плохой o5ycno TGHii зет матрицы коэффи циесюв систспы уравнений (2) В этом ел/ чае вместо (3) мохно воспользоваться известными специально разработамныгм методами решения системы уравнений с плохо оЬуслоиленными матрицами коэффи циентоо или не делать величину n настолько большой, чтобы матрица становились плохо обусловленной

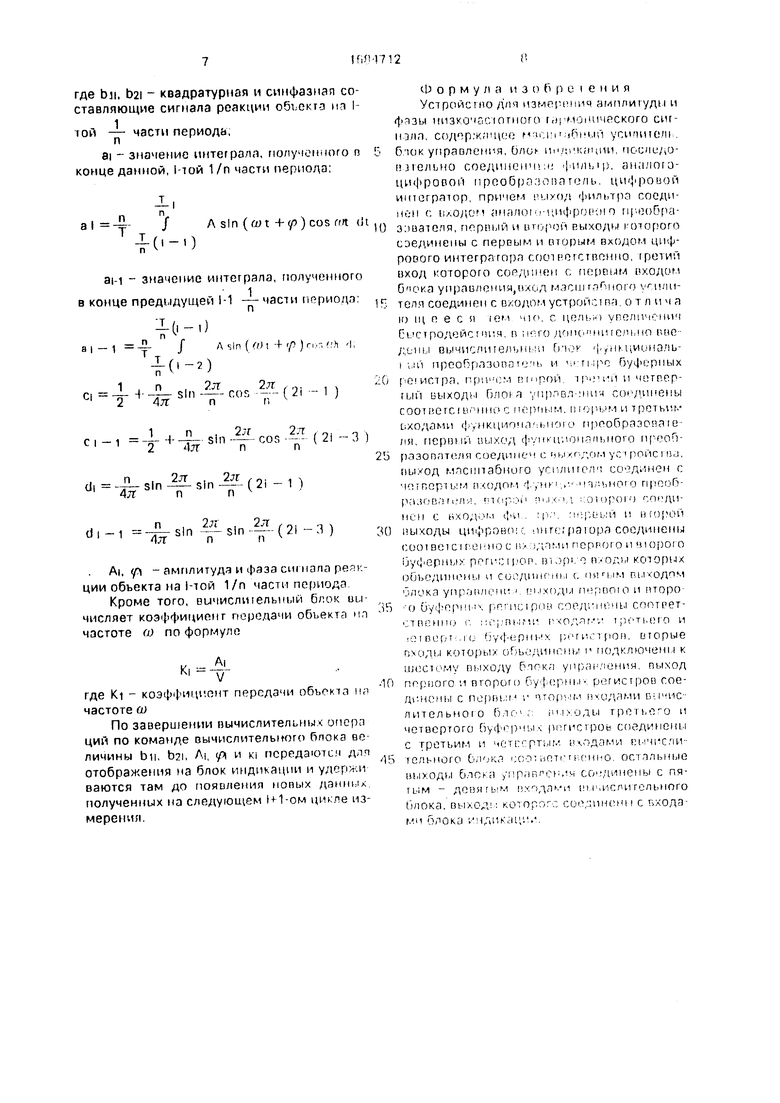

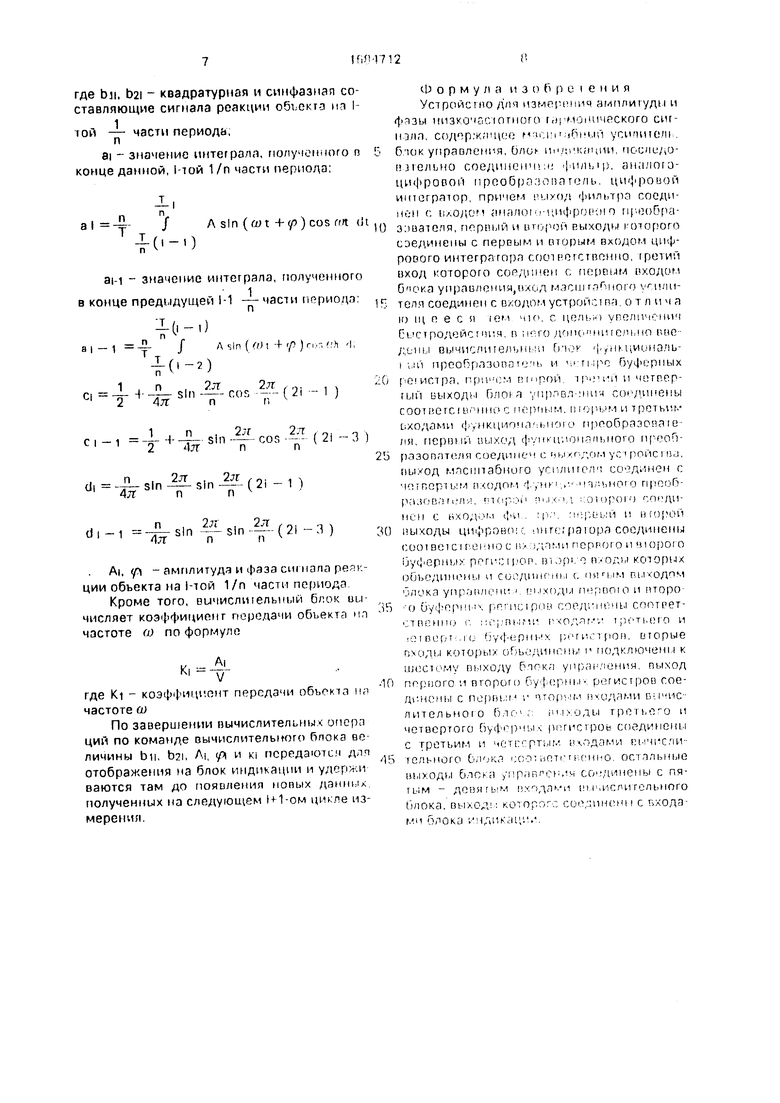

На фиг 1 представлена функциональ пая схема устройство на фиг 2 функциональная схема блока учривления, нэ фиг 3 фyнкциoнз t aя СХРМТ цифрового интег ратсра

Устройство дпч измерение аг птитудм и фазы низкочастотною гармоническою сш- налз содержит блок 1 угф пчения fj/ чцио папы1 1 ппгч,)п пть 2 итс ипаГмг ш усилитель 3, фи/н,гр ци |фовои преобрэзовап;ль 5 цифроиоп инто-р-этс n G, буферные рошсгри 7 и 8 гичиг иг п ный

IQ

|

V

)

30

10

V

г 0

Г. О

Ьлок 9, буферные регистры 10 и 11, блок 12

индикации

Пыходы блока 1 управления соединены со входами функционального преобразова- Tfjiq 2, цифровою шпгтр нора 6, буферных регистров 7, 8, 10 и 11 и вычисли1елыюго блока 9, выход функционального преобра- зс.оягеля 2 через ПОСЛСДОУЭТРЛЬНО соеди- ноннус |илыр Л, анапого цифровой 11р1 оГ)|)азоЕШ1аль 5 цифровой интегратор 6 буферные регистры 7, 8, 10 и 11, вычислительный блок 9 соединен со входами блока индикации 12, выход масштабною усилите- лч 3 соединен со входим функционального преобразователя 2

Функциональная блока управле- п 1Л 1 прип,1рца на ((jHi 2 Он содр|| пг три Г), ( ерн.нч рргисгрн 13 11 ib входы кото- ituiKifq входт«и Плою ,нравления 1 («шмер 1G лиьию зтдер кки 17, счетчики 18 13 линию задерч ки 20 линию зтдержки 22, LJMI 23 Выход регистра 13 соединен со вводом цифро аналогового преобразователя (ЦАП1 3 и кроме гсш, он является вто- рчм 1ы.(лдом упри uoMifciu блока выход ЦИ1 ро аналоговою (if Пра иватцпя 23 соединен с одиннадцатым выходом блока уп- ртвления выход буферною регистра 14 сосДьмен L выход м бльга у рзолбния и лромс TO fj подкл Ч 5н ко входу управляв f 01 )тапмсрч 16 f 1ход которого соединен со пи лин,т )адг |Н ки 1 / счетчика 18 г .кп 19 г ьиид линии задержки 17 соединен г , ротьим блока у прав л е- i и S DI i/o,/i г,.н ) 1C под Л1)чеп к четвертому ) Ґправ|г чия выход г ( мч IK i i J ГОРДИН- и и if г 11 м вы чодом бло- /я Ч вления и i POML иго соединен со i /одами линии задержки 20 и счетчика 21, L ход 1,четчика 19 соединен с вы чодом буферною регистра 15 который соединен с девятым выходом блока управления, выход счетчика 21 соединен с восьмым выходом блока управления г ы л од линии задержки 20 подключен к пятому выходу блока управления и соединен со входом линии задержки 2 выход которой соединен с первым и седьмым выходами блока управления

Функциональная схема цифровою ин- et ратора 6 приведена на фиг 3 Он содер- кит счетчик 24 суммэюр 25 первый вход которого соединен с первым входом цифровою интегратора и кроме того, второй вход иединен со входсм счетчика 24 и вторым кодом цифрового интегратора выход сум- птора 25 соединен с первым выходом циф- ювого интегратора, а выход счетчика 24 гоединен со вторым выходом цифрового интегратора, третий вход сумматора 25 связан

со вторым входом сметчика 24 и соединен с третьим входом цифрового интегратора.

Устройство, изображенное на фиг. 1 и предназначенное для реализации предлагаемого способа, функционирует следующим образом.

Измерения начинаются с ввода о блок управления 1, например, при помощи ключевых регистров, исходных данных эеспери- меита: V - амплитуда гармонического

1л воздействия: , где w - угловая частого N та гармонического воздействия;

2л N

квант аргумента функционального преобразования 2- , где - - принятая в экс- пп

перименте часть периода,в течение которой производится интегрирование N - число квантов функционального преобразователя 2, в результате введения исходных данных на втором выходе блока 1 управления устанавливается аналоговая величина, равная заданной амплитуде гармонического воздействия, которая поступает на аналоговый вход sin-ного канала преобразователя 2. На выходе программируемого таймера через

каждый интервал времени - начинают появляться импульсы а на выходе счетчика, рассчитанного на максимально допустимое число N-1, будет с каждым новым импульсом программируемого таймера устанавливаться периодически линейно возрастающее во времени число в пределах от 0 до N-1. которое передается на вход преобразователя 2 для выполнения тригонометрических преобразований. На выходе sin-ного канала преобразователя 2 для тригонометрических преобразований образуется гармонический аналоговый сиг нал Usln ал, который подается на вход испытуемого объекта. Сигнал Asin( (Ч + р) с выхода обь- екта через масштабный усилитель 3 поступает на аналоговый вход cos-ного канала преобразователя 2 для тригонометрических преобразований, на выходе которого образуется аналоговая величина Asin(c/)t + y)cos ft) t, представляющая собой произведение реакции объекта (Asin(wt - у) на cos ш. Для обеспечения благоприятных условий функционирования аналого-цифрового преобразователя 5 выходной сигнал преобразователя 2 для выполнения тригонометрических преобразований подвергается фильтрации, что позволяет очистить его от аддитивных помех накопившихся в предыдущих блоках преобразований. В выполнении операции цифрового осредняющего интегрирования участвуют аналого-цифровой преобразователь 5 цифровой интегратор б и вычислительный блок 9. Аналого-цифровой преобразователь 5 в режиме внутреннего запуска периодически производит преобразование величины (wt p)cos(i). В момент завершения очередного преобразования на первом выходе аналого-цифрового преобразователя 5 устанавливается цифровой результат преобразования, а на втором его выходе появляется импульс, сигнализирующий о завершении цикла преобразования, под действием которого в сумматоре 25 выполняется операция сложения полученного результата преобразования с ранее накопленной суммой, а в счетчике прибавляется единица. В момент, когда в счетчике 19 блока управления 1 накопятся очередные

N - единиц, сигналом о его переполнении

содержимое буферных регистров 7 и 8, в которых содержатся результаты цифрового интегрирования на предыдущем интервале

Т

продолжительностью - , будет переписано в буферные регистры 10 и 11, а затем в буферные регистры 7 и 8 будет переписано содержимое выходных регистров счетчика 24 и сумматора 25, после чего эти регистры будут обнулены и начнется новый цикл интегрирования. Далее по задержанному в линиях задержки 20 и 22 сигналу переполнения счетчика 19 инициализируется работа вычислительного блока , который переписывает во внутренную память содержимое регистров 7, 8, 10 и 11 и выполняет операции деления содержимого регистра 8 на содержимое регистра 7, содержимого регистра 11 (аи) на содержимое регистра 10, что и дает средние значения интеграла ai на i-той и аи на i-1-ой

-- части периода.

Далее вычислительный блок приозво- дит вычисление в соответствии с соотношениями

bi,

ai d i - 1 - a i - 1 di

Ci d i - 1 -ci - i di

- ai c 1 a i 1 c 21 - с i

arctg

D2J

bii

Ai .r

где Ьи, b2i - квадратурная и синфазная составляющие сигнала реакции обтектз m I

тй - части периода,

ai - значение интеграла, полученного п конце данной, I той 1/п части периода

||

JЛ Sin (О) t + р ) COS «П. Ill

- 0-0

п ч

ai i - значение интеграла, полученного в конце предыдущей 1-1 - части периода -Ц,-,)

П г

JЛ In ( П) f /) )п t Л

- ( -О n v

1 , п . я2тг , г, . .

ci T-t-4irSln -cos , (2l - )

С 1-1 -g-H

п , 2jr2.Т /r. i

-г- sin cos - ( 2i - 3 )

4тгnn

-fc nJ;r« -Tr 2 -1

2л

2л

.П,/Jt,.t f

CJ.-1 --sin -(2I-J)

AI, уч - амплитуда и фаза cm нала pppi ции объекта на i-той 1/п части периода

Кроме того, вичислтельныи бгок ULI числяет коэффициент передачи объекта i частоте у по формуле

„ А, М - v

где KI - коэффициент передачи обьокта lui частоте ш

По завершении вычислительных оперп ций по команде вычислительного бпока ве личины bii b2i, AI (р( и KI передают длп отображения на блок индикации и удер и ваются там до появления новых данннл полученных на следуюи ем И1 ом ци пе из мерения

Формула и з о Ь р L i e н и я

Устройство длч НЗМР; риич ампли уди и

фТЗЫ , 10ТНОГО Г.1, МлШЧРСКОГО СИГ

шла к.гцоо мщ i rtcnuo H б IOK управления Олоь иш чсмиш MCL iu/to плельно соединепч с |илыр аначого цифровой прсобра опа голь цифровой интегратор причем чхо/i фипьгрт гоеди

HUI ( Ь/ОДС1 ciHcUlOl ЦИфрГЧ )0 П|0()

0 з шатепя первый и второй выходы i оборот соединены с первые и вторым входом цифрового интегратора соответственно третий вход roroporo СОРДПНРН с порпым uxo/uifi

0пока умрав/1рния,ихид f ппи пг иги п г или Г телч соединен с входом устрой чгч о т л и ч а

то ц Р е с я IPM но г цр и i ним CL Cтродеиспи ч в к го цопс нигел но i во / они оычио штельн и Г) i | иционапь

1п воват ч и in рг б/фсрпых ( О истра гр i t м гмппои ч iii ii и

run ьиходн fJnni a , мш coi/Hii ei bi rooTi erciu iu ппип шорпм и третыч- сходами ) ,нкципчл ию| о ri ioo6paTonaie ля первни иич д 1 им; ч гпыюю rij fori Ь разопатоля гоедипс11 с пи/г /on vr pniici в j мчсипабниго п лигет1 соединен с

К1 i Ппр Т L 1 В ОДОГ 1 } , ИМ Ml iHOl О ПрО( Г

р i н в г л г т ; I ll n opoi ) г осцп HLH t ьход n it и tJL и п и орои

0 РЬКОДЫ цифров(1 шг( грашра соединены ( ooiBeic.it ei нос в ,4пми псрг ою и чюрото oycj ерни port ||пр и i pi n «од) i которых ииьпдинснч и нп miriiM пиодпм лока упр juni MI- MI пд| i гт, пп| о и второ

r) О Us | г i i PII ( орд MI MI i СПОТПРТ

Т В Hllirji , П1 Ч. I O,, Т ,Н Т) (М П И

м BUI т if у | ( pin « |(гг 1(ои иторые Г)ч i,Tii которы/ ,iiMt мы Р no,v лючен i к

ШР1Л MV ВПХОДУ fTTKrl ЮНИЯ ПЫЧОД

0 nof но го м второго t (ч| HI i т |)ов гое

Д НОНЫ С ПОрЫ ( , 4TOf) М В «ОД 1МИ D I ИС ЛПТелЬНОТО ())Ди ГрРТ I И

четвертого бу4 Р Р гипров соединены с третьим и if T i-pTi IN в. дами п л спи 1 тс/ ьного G Юг i с т LiOTi г и нно ос тьные выходи бпгрс ., iptimrt /ч соединены с пя TLIM - дгмзя ьм одп и 141 игпигелиюго

1 ЛОКа Btl/СД ( LI ШНеММ С ВлОДЗ МИ ПЛОКО . 1 riiU Н, .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синфазной и квадратурной составляющих основной гармоники переменного тока | 1990 |

|

SU1712893A2 |

| УСТРОЙСТВО АНАЛИЗА УЗКОПОЛОСНОГО НИЗКОЧАСТОТНОГО АНАЛОГОВОГО СИГНАЛА | 1991 |

|

RU2065610C1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Фазовый анализатор | 1977 |

|

SU892336A1 |

| Сейсмостанция | 1987 |

|

SU1430924A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1538143A2 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1320902A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU681553A1 |

Изобретение относится к информационно-измерительной технике, в частности к устройствам, использующимся для исследования частотных характеристик широкого класса динамических объектов и систем. Цель изобретения - повышение быстродействия - достигается за счет введения в устройство вычислительного блока 9, функционального преобразователя 2, буферных регистров 7, 8, 10, 11 и образования новых функциональных связей. Устройство также содержит блок 1 управления, масштабный усилитель 3, фильтр 4, аналого-цифровой преобразователь 5, цифровой интегратор 6, блок 12 индикации. 3 ил.

lui/891

VJ

фиг.З

| Анализатор частотных характеристик | 1977 |

|

SU813298A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-10-15—Публикация

1988-12-14—Подача