2

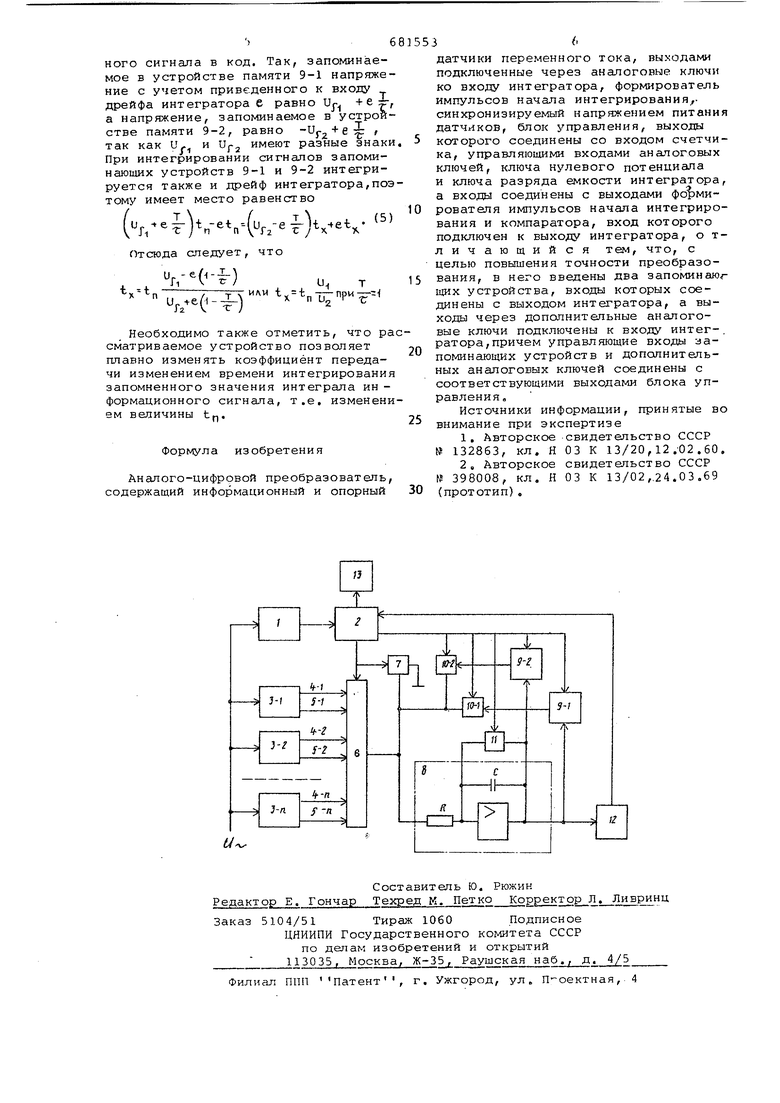

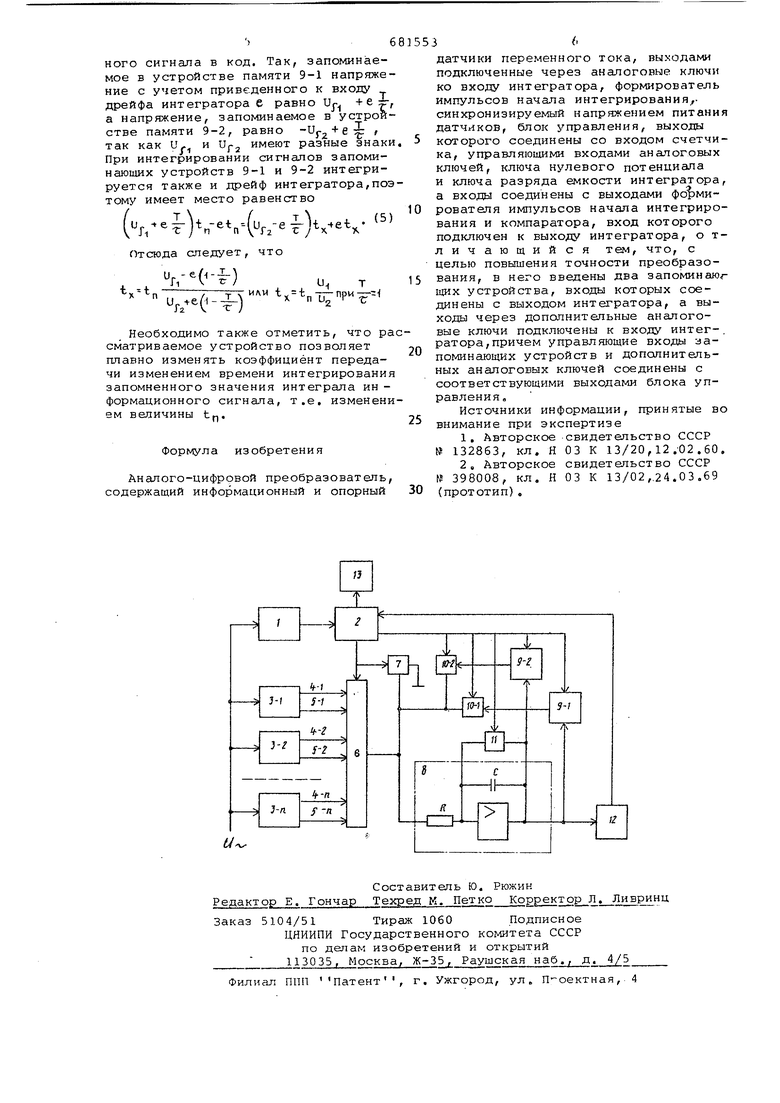

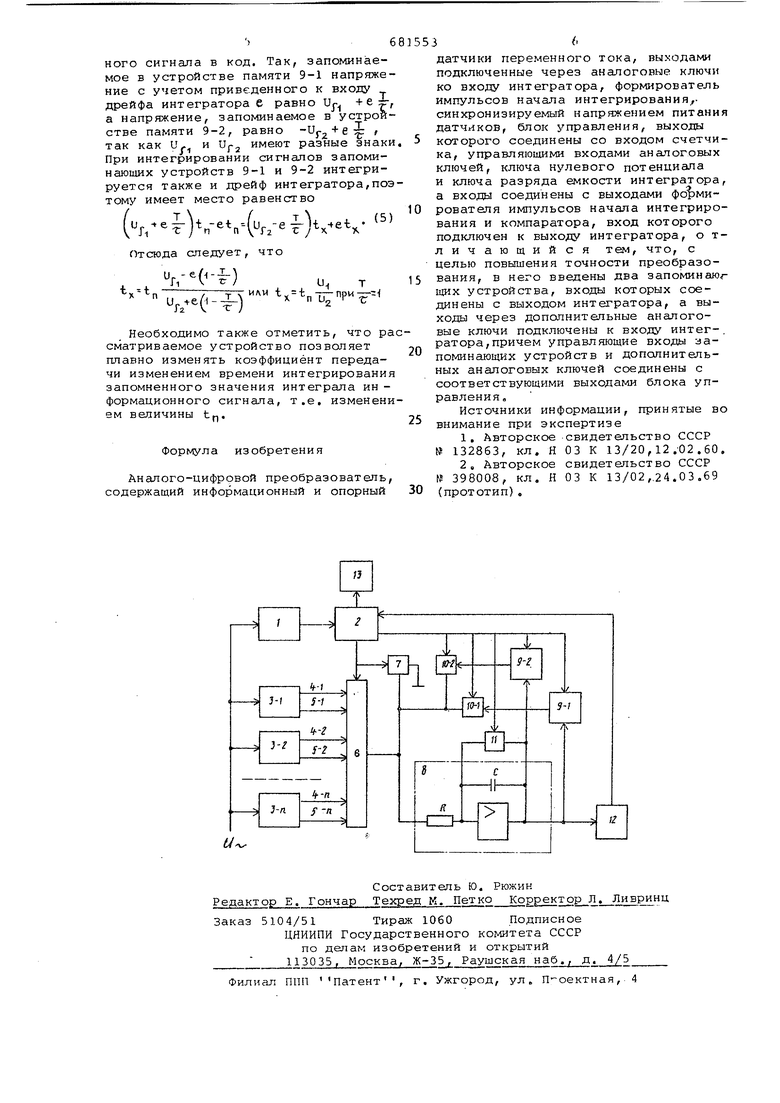

перемещений 3-1, 3-2,...3-n с информационными выходами (обмотками) 4-1, 4-2,.,,4-п и опорными выходами (обм:л-ками) 5-1,5-2 ,,. ,5-п, эапитываемые напряжением переменного тока U-, аналоговые ключи б информационных и опорных выходов датчиков, ключ 7 нулевого потенциала, аналоговый интегратор 8, запоминающие устройства 9-1 9-2, аналогокле 10-1, 10-2 на выходах запоминающих устройств,ключ 11 разряда емкости интегратора, компаратор 12, кодирующий счетчик 13,

Устройство работает следующим образом, В некоторый момент времени в блоке управления 2 вырабатывается состояние интегрирование сигнала с информационного выхода 1-го датчика , С момента прихода на, блок 2 импульса начала интегрирования, вырабатываемого формирователем 1,этот блок формирует команду на коммутацию соответствующего ключа 6, в результате чего информационный выход i -го датчика подключается к входу интегратора 8, Процесс интегрирования сигнала с информсьционного выхода происходит в течение времени Т, Затем данный ключ входного сигнала размыкается, замыкается ключ 7 нулевого потенциала. Выходное напряжение интегратора 8 по сигналу блока 2 запоминается в устройстве памяти 9-1. После этого замыкается ключ 11 и интегратор 8 обнуляется.

Далее следует аналогичный процесс интегрирования сигнала с опорного выхода того же датчика с запоминанием интеграла этого сигнала в устройстве памяти 9-2 и последующим обнулением интегратора.

После этого блок 2 вырабатывает сигнал, замыкающий ключ 10-1 на интервал времени t {, в течение которого интегрируется напряжение, хранящееся в устройстве памяти 9-1. По окончании этого интервала времени ключ 10-1 размыкается, а замыкается ключ 10-2 и одновременно запускается кодирующий счетчик 13. Начинается прслдесс разряда интегратора напряжением, хранящимся в устройстве памяти 9-2, так как напряжения, хранящиеся в запоминающих устройствах 9-1 и 9-2, - противоположной полярности, что обеспечивается соответствующим выбором моментов начала интегрирования сигналов измерительного и опорного выходов 1 -го датчика,Через интервал времени t интегратор разряжается, компаратор 12 изменяет свое состояние и по его сигналу блок 2 прекращает формирование кода в счетчике 13.

Формирователь импульсов 1 формирует сигналы начала интегрирования таким образом, чтобы за время т знак ,интегрируемого напряжения не менял:ся и его интервал был максимальным,Это обеспечивается тем, что ногда.нальный сдвиг фаз между выходныг ш (информационными и опорными) напряжениями и напряжением питания (возбуждения) трансформаторных датчиков известен и учтен в схеме,

Рабага преобразователя описывается следующими уравнениями:

Up (ULit+4)di)

Up Ju sin(ujt + 4-vn:)d-t,

Га т:

1 п--игг-ь,

где и амплитуда напряжения инфсфмационной обмотки;

U2амплитуда напряжения опорной обмотки; Ч

начальная фаза интегрирования сигналов датчиков,

tr- постоянная времени интегрирования интегратора;

твремя интегрирования информационного и опорного сигналов;

и

интеграл информационного

и сигнала;

и

интеграл опорного сигнала;

/2

tn время интегрирования интеграла информационного сигнала;

tv кодируемый временной интервал .

Реально от датчика к датчику и при изменении вноиних воздействий среды сдвиг фаз выходных напряжений относительно напряжения питания датчика меняется. Но отноиение проинтегрированных значений информационного и опорного сигналов не меняется в силу свойства трансформаторных датчиков перемещений сохранять постоянным отношение ЭДС информационной и опорной обмоток при постоянной координате перемещения, независимо от колебаний напряжения возбуждения по амплитуде и частоте и наличия возмущающих воздействий, т.е.

В силу этого, независимо от изменений ш , Т и Ч , выходной код преобразуемого сигнала определяется как

N,, N(4)

где f - частота импульсов заполнения

временного интервала N - число импульсов, заполняющих

временной интервал t. При выполнении условия Т t достигается подавление влияния собственного дрейфа аналогового интегратора на точность преобразования ниформацион) кого сигнала в код. Так, запоминаемое в устройстве памяти 9-1 напряже ние с учетом приведенного к входу дрейфа интегратора е равно Uj- F а напряжение, запоминаемое в устрой стве памяти 9-2, равно -Uj-. + е i так как U.. и Uj- имеют разные знак При интегрировании сигналов запоминающих устройств 9-1 и 9-2 интегрируется также и дрейф интегратора,поэ тому имеет место равенство )(«т)ч- ЧОтсюда следует, что ггЧ-i-) -с Jи т Необходимо также отметить, что ра сматриваемое устройство позволяет плавно изменять коэффициент передачи изменением времени интегрировани запомненного значения интеграла ин формационного сигнала, т.е. изменени ем величины t Формула изобретения Аналого-цифровой преобразователь, содержащий информационный и опорный ( датчики переменного тока, выходами подключенные через аналоговые ключи ко входу интегратора, формирователь импульсов начала интегрирования/синхронизируемый напряжением питания датчиков, блок управления, выходы которого соединены со входом счетчика, управляющими входами аналоговых ключей, ключа нулевого потенциала и ключа разряда емкости интегратора, а входы соединены с выходами формирователя импульсов начала интегрирования и компаратора, вход которого подключен к выходу интегратора, о тличающийся тем, что, с целью повышения точности преобразования, в него введены два запоминеио щих устройства, входы которых соединены с выходом интегратора, а выходы через дополнительные аналоговые ключи подключены к входу интег-. ратора,причем управляющие входы запоминающих устройств и дополнительных аналоговых ключей соединены с соответствующими выходами блока управления. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 132863, кл. Н 03 К 13/20,12.02.60. 2.Авторское свидетельство СССР № 398008, кл. Н 03 К 13/02 ,,24.0 3 .69 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Преобразователь сигнала в его среднее значение | 1978 |

|

SU748135A1 |

| Интегратор | 1978 |

|

SU744628A2 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Способ аналого-цифрового преобразования | 1978 |

|

SU723771A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1975 |

|

SU684738A1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ | 2012 |

|

RU2521305C2 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

Авторы

Даты

1979-08-25—Публикация

1974-08-19—Подача