Фиг.1

Изобретение относится к вычислительной технике и можег использоваться для построения надежных многопроцессорных контроллеров.

Цель изобретения - увеличение надеж ности и достоверности выдаваемой информации.

На фиг. 1 представлена структурная схема многопроцессорной системы; на фиг. 2 структурная схема блока контроля; на фиг. 3 структурная схема блока формирования свертки: на фиг. 4-структурная схема блока реконфигурации; на фиг. Ь - структурная схема блока арбитра; на фиг. 6 - алгоритм функционирования вычислительного блока.

Многопроцессорная система (фиг. 1) содержит вычислительные модули 1i.. 1/i, , блок 2 арбитра, блок 3 реконфигурации, контроллер 4,блок 5 контроля,селектор 6 адреса, элемент И 7, блок 8 формирования свертки, элемент 9 задержки.

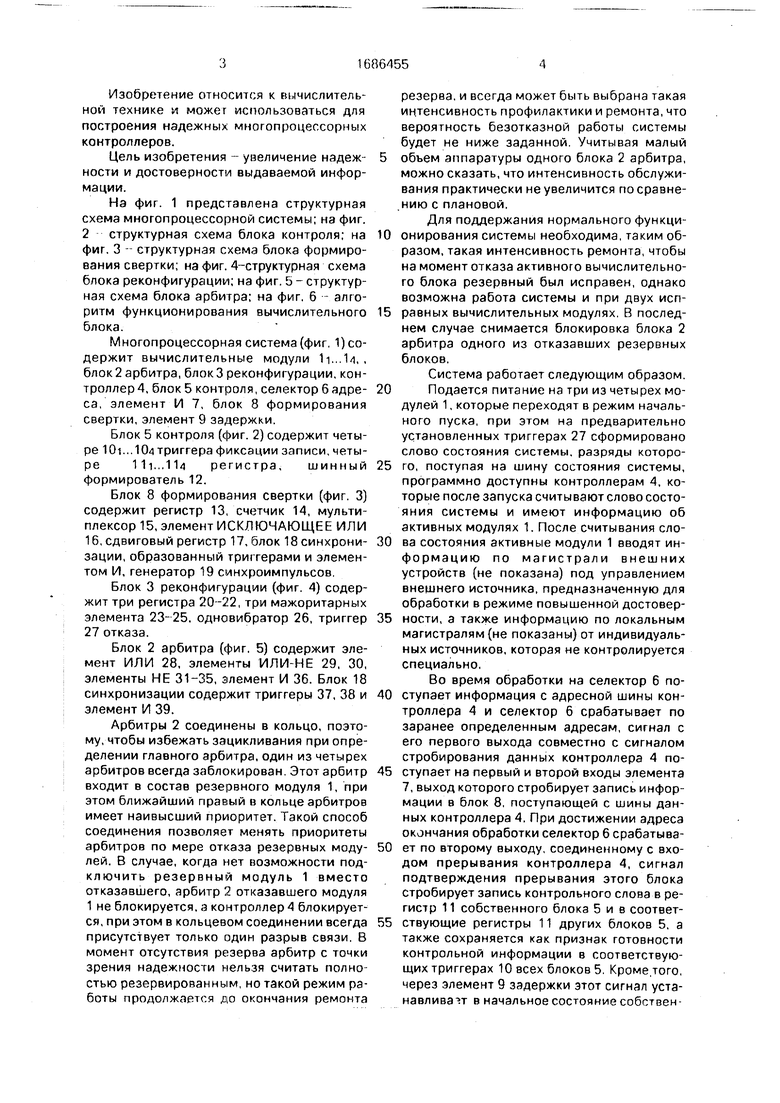

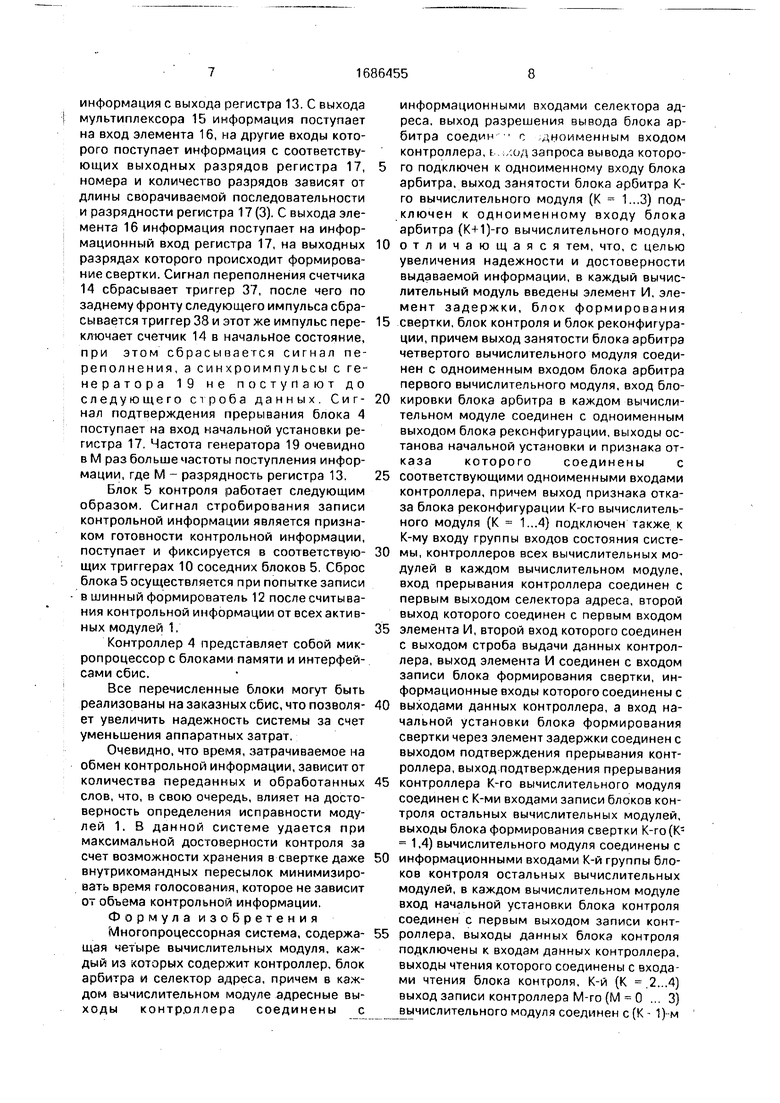

Блок 5 контроля (фиг. 2) содержит четыре 101...104триггера фиксации записи, четыре11i... регистра, шинный формирователь 12.

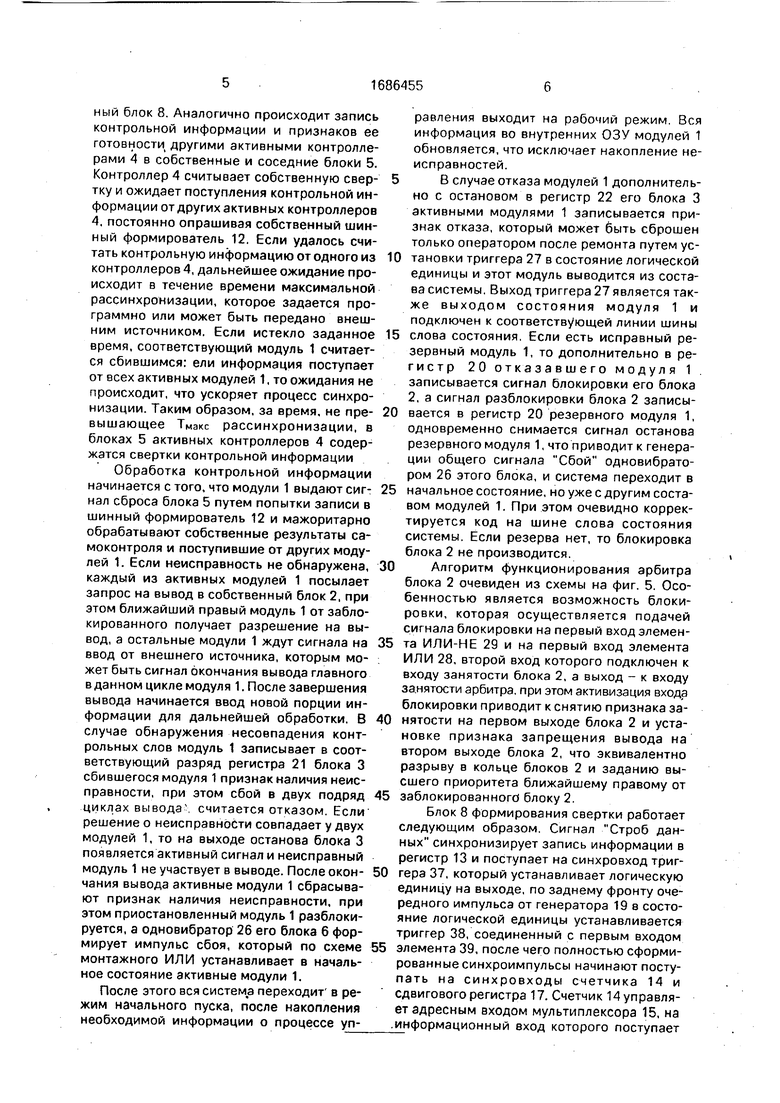

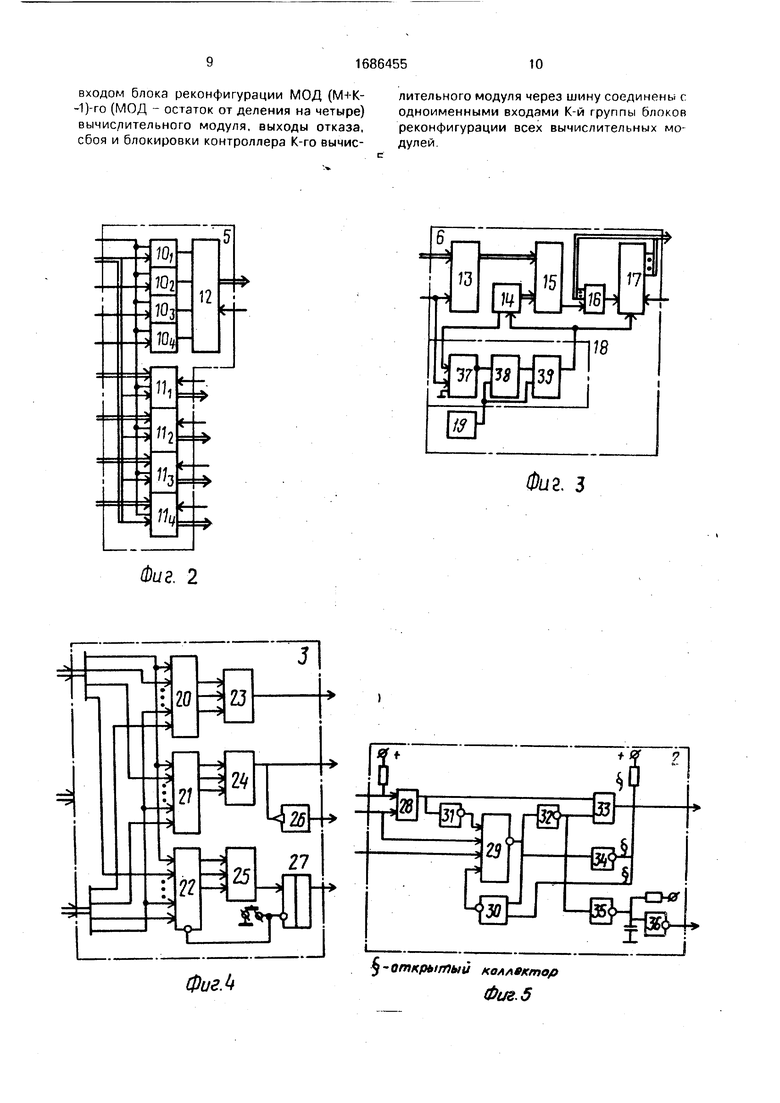

Блок 8 формирования свертки (фиг. 3) содержит регистр 13, счетчик 14, мультиплексор 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, сдвиговый регистр 17, блок 18 синхронизации, образованный триггерами и элементом И, генератор 19 синхроимпульсов.

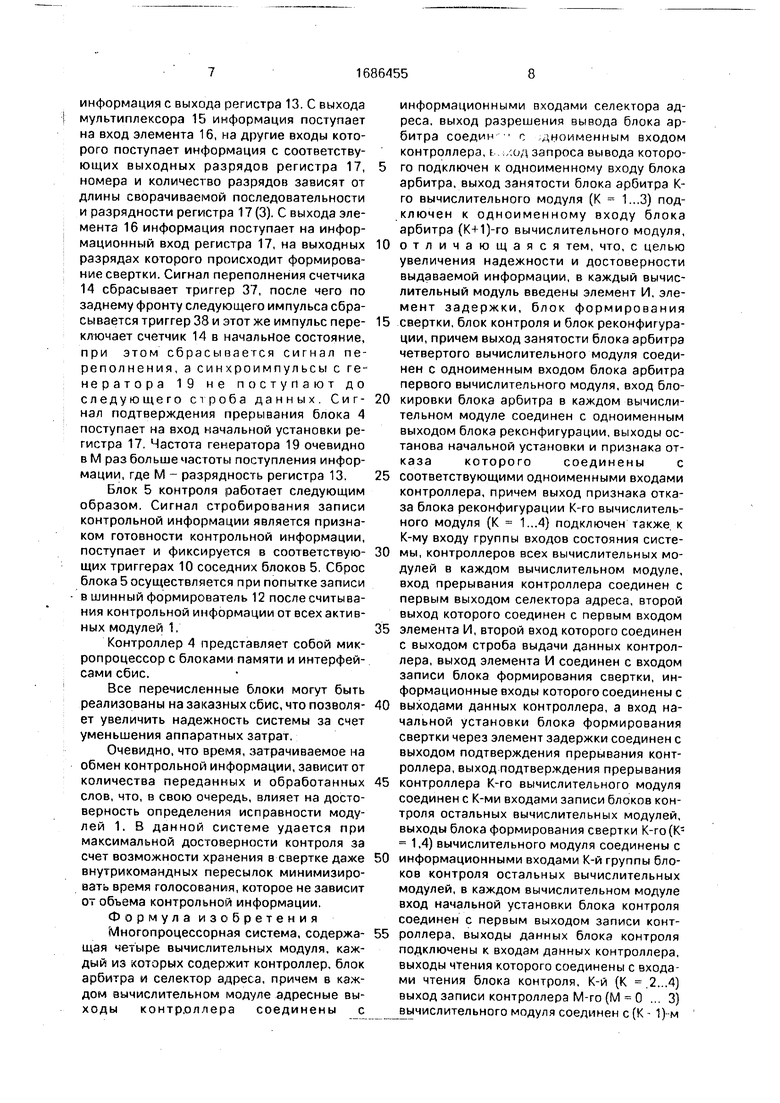

Блок 3 реконфигурации (фиг. 4) содержит три регистра 20-22, три мажоритарных элемента 23-25, одновибратор 26, триггер 27 отказа.

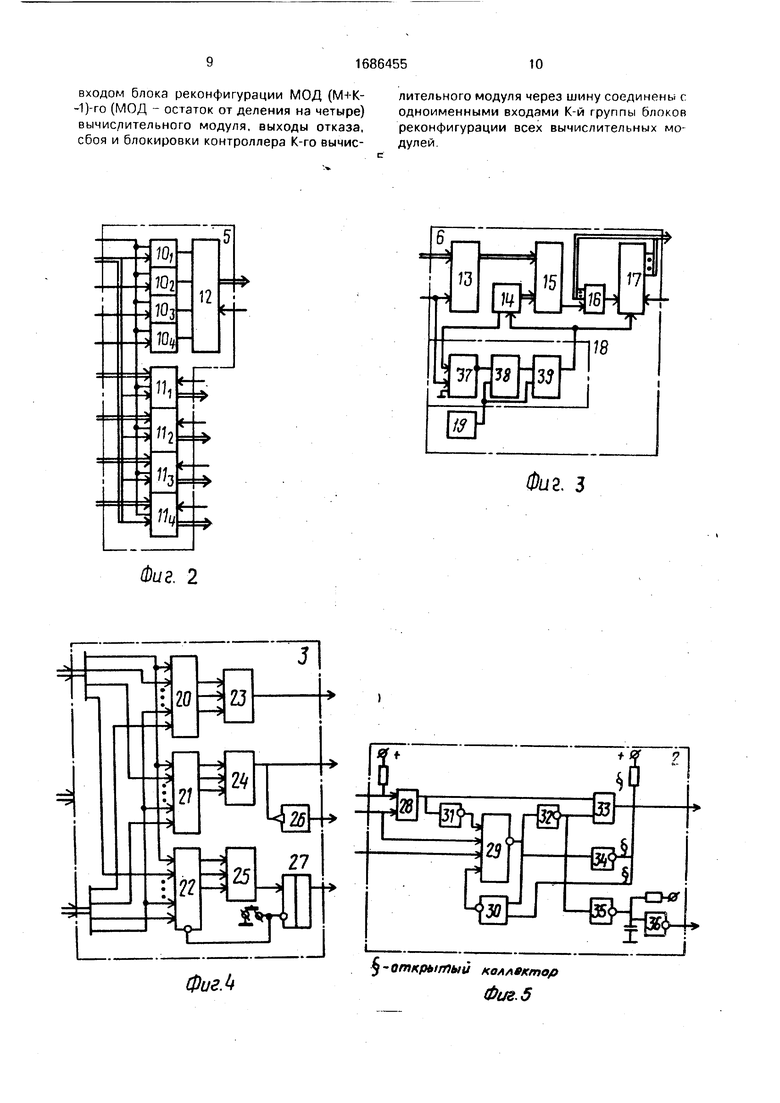

Блок 2 арбитра (фиг. 5) содержит элемент ИЛИ 28. элементы МЛИ-НЕ 29, 30, элементы НЕ 31-35, элемент И 36. Блок 18 синхронизации содержит триггеры 37, 38 и элемент И 39.

Арбитры 2 соединены в кольцо, поэтому, чтобы избежать зацикливания при определении главного арбитра, один из четырех арбитров всегда заблокирован. Этот арбитр входит в состав резервного модуля 1, при этом ближайший правый в кольце арбитров имеет наивысший приоритет. Такой способ соединения позволяет менять приоритеты арбитров по мере отказа резервных модулей. В случае, когда нет возможности подключить резервный модуль 1 вместо отказавшего, арбитр 2 отказавшего модуля 1 не блокируется, а контроллер 4 блокируется, при этом в кольцевом соединении всегда присутствует только один разрыв связи. В момент отсутствия резерва арбитр с точки зрения надежности нельзя считать полно стью резервированным, но такой режим работы продолжается до окончания ремонта

резерва, и всегда может быть выбрана такая интенсивность профилактики и ремонта, что вероятность безотказной работы системы будет не ниже заданной. Учитывая малый

обьем аппаратуры одного блока 2 арбитра, можно сказать, что интенсивность обслуживания практически не увеличится по сравнению с плановой.

Для поддержания нормального функци0 онирования системы необходима, таким образом, такая интенсивность ремонта, чтобы на момент отказа активного вычислительного блока резервный был исправен, однако возможна работа системы и при двух исп5 равных вычислительных модулях. В последнем случае снимается блокировка блока 2 арбитра одного из отказавших резервных блоков.

Система работает следующим образом.

0Подается питание на три из четырех модулей 1, которые переходят в режим начального пуска, при этом на предварительно установленных триггерах 27 сформировано слово состояния системы, разряды которо5 го, поступая на шину состояния системы, программно доступны контроллерам 4, которые после запуска считывают слово состояния системы и имеют информацию об активных модулях 1. После считывания сло0 ва состояния активные модули 1 вводят информацию по магистрали внешних устройств (не показана) под управлением внешнего источника, предназначенную для обработки в режиме повышенной достовер5 ности, а также информацию по локальным магистралям (не показаны) от индивидуальных источников, которая не контролируется специально.

Во время обработки на селектор 6 по0 ступает информация с адресной шины контроллера 4 и селектор 6 срабатывает по заранее определенным адресам, сигнал с его первого выхода совместно с сигналом стробирования данных контроллера 4 по5 ступает на первый и второй входы элемента 7, выход которого стробирует запись информации в блок 8. поступающей с шины данных контроллера 4. При достижении адреса окончания обработки селектор 6 срабатыва0 ет по второму выходу, соединенному с входом прерывания контроллера 4, сигнал подтверждения прерывания этого блока стробирует запись контрольного слова в регистр 11 собственного блока 5 и в соответ5 ствующие регистры 11 других блоков 5, а также сохраняется как признак готовности контрольной информации в соответствующих триггерах 10 всех блоков 5. Кроме того, через элемент 9 задержки этот сигнал устанавливает в начальное состояние собствен

ныи блок 8. Аналогично происходит запись контрольной информации и признаков ее готовности другими активными контроллерами 4 в собственные и соседние блоки 5. Контроллер 4 считывает собственную свертку и ожидает поступления контрольной информации от других активных контроллеров 4. постоянно опрашивая собственный шинный формирователь 12. Если удалось считать контрольную информацию от одного из контроллеров 4, дальнейшее ожидание происходит в течение времени максимальной рассинхронизации, которое задается программно или может быть передано внешним источником. Если истекло заданное время, соответствующий модуль 1 считается сбившимся: ели информация поступает от всех активных модулей 1. то ожидания не происходит, что ускоряет процесс синхронизации. Таким образом, за время, не превышающее Тмакс рассинхронизации. в блоках 5 активных контроллеров 4 содержатся свертки контрольной информации

Обработка контрольной информации начинается с того, что модули 1 выдают сигнал сброса блока 5 путем попытки записи в шинный формирователь 12 и мажоритарно обрабатывают собственные результаты самоконтроля и поступившие от других модулей 1. Если неисправность не обнаружена, каждый из активных модулей 1 посылает запрос на вывод в собственный блок 2, при этом ближайший правый модуль 1 от заблокированного получает разрешение на вывод, а остальные модули 1 ждут сигнала на ввод от внешнего источника, которым может быть сигнал окончания вывода главного в данном цикле модуля 1. После завершения вывода начинается ввод новой порции информации для дальнейшей обработки. В случае обнаружения несовпадения контрольных слов модуль 1 записывает в соответствующий разряд регистра 21 блока 3 сбившегося модуля 1 признак наличия неисправности, при этом сбой в двух подряд циклах вывода считается отказом. Если решение о неисправности совпадает у двух модулей 1, то на выходе останова блока 3 появляется активный сигнал и неисправный модуль 1 не участвует в выводе. После окончания вывода активные модули 1 сбрасывают признак наличия неисправности, при этом приостановленный модуль 1 разблокируется, а одновибратор 26 его блока 6 формирует импульс сбоя, который по схеме монтажного ИЛИ устанавливает в начальное состояние активные модули 1.

После этого вся система переходит в режим начального пуска, после накопления необходимой информации о процессе управления выходит на рабочий режим. Вся информация во внутренних ОЗУ модулей 1 обновляется, что исключает накопление неисправностей.

5В случае отказа модулей 1 дополнительно с остановом в регистр 22 его блока 3 активными модулями 1 записывается признак отказа, который может быть сброшен только оператором после ремонта путем ус- 10 танонки триггера 27 в состояние логической единицы и этот модуль выводится из состава системы. Выход триггера 27 является также выходом состояния модуля 1 и подключен к соответствующей линии шины 15 слова состояния. Если есть исправный резервный модуль 1, то дополнительно в регистр 20 отказавшего модуля 1 записывается сигнал блокировки его блока 2, а сигнал разблокировки блока 2 записы0 вается в регистр 20 резервного модуля 1, одновременно снимается сигнал останова резервного модуля 1, что приводит к генерации общего сигнала Сбой одновибрато- ром 26 этого блока, и система переходит в

5 начальное состояние, но уже с другим составом модулей 1. При этом очевидно корректируется код на шине слова состояния системы. Если резерва нет, то блокировка блока 2 не производится.

0Алгоритм функционирования арбитра

блока 2 очевиден из схемы на фиг. 5. Особенностью является возможность блокировки, которая осуществляется подачей сигнала блокировки на первый вход элемен5 та ИЛИ-НЕ 29 и на первый вход элемента ИЛИ 28, второй вход которого подключен к входу занятости блока 2, а выход - к входу занятости арбитра, при этом активизация входа блокировки приводит к снятию признака за0 нятости на первом выходе блока 2 и установке признака запрещения вывода на втором выходе блока 2, что эквивалентно разрыву в кольце блоков 2 и заданию высшего приоритета ближайшему правому от

5 заблокированного блоку 2.

Блок 8 формирования свертки работает следующим образом. Сигнал Строб данных синхронизирует запись информации в регистр 13 и поступает на синхровход триг0 гера 37, который устанавливает логическую единицу на выходе, по заднему фронту очередного импульса от генератора 19 в состояние логической единицы устанавливается триггер 38, соединенный с первым входом

5 элемента 39, после чего полностью сформированные синхроимпульсы начинают поступать на синхровходы счетчика 14 и сдвигового регистра 17. Счетчик 14 управляет адресным входом мультиплексора 15, на информационный вход которого поступает

информация с выхода регистра 13. С выхода мультиплексора 15 информация поступает на вход элемента 16, на другие входы которого поступает информация с соответствующих выходных разрядов регистра 17, номера и количество разрядов зависят от длины сворачиваемой последовательности и разрядности регистра 17 (3). С выхода элемента 16 информация поступает на информационный вход регистра 17, на выходных разрядах которого происходит формирование свертки. Сигнал переполнения счетчика 14 сбрасывает триггер 37, после чего по заднему фронту следующего импульса сбрасывается триггер 38 и этот же импульс переключает счетчик 14 в начальное состояние, при этом сбрасывается сигнал переполнения, а синхроимпульсы с генератора 19 не поступают до следующего строба данных. Сигнал подтверждения прерывания блока 4 поступает на вход начальной установки регистра 17. Частота генератора 19 очевидно в М раз больше частоты поступления информации, где М - разрядность регистра 13.

Блок 5 контроля работает следующим образом. Сигнал стробирования записи контрольной информации является признаком готовности контрольной информации, поступает и фиксируется в соответствующих триггерах 10 соседних блоков 5. Сброс блока 5 осуществляется при попытке записи в шинный формирователь 12 после считывания контрольной информации от всех активных модулей 1.

Контроллер 4 представляет собой микропроцессор с блоками памяти и интерфейсами сбис.

Все перечисленные блоки могут быть реализованы на заказных сбис, что позволяет увеличить надежность системы за счет уменьшения аппаратных затрат.

Очевидно, что время, затрачиваемое на обмен контрольной информации, зависит от количества переданных и обработанных слов, что, в свою очередь, влияет на достоверность определения исправности модулей 1. В данной системе удается при максимальной достоверности контроля за счет возможности хранения в свертке даже внутрикомандных пересылок минимизировать время голосования, которое не зависит от объема контрольной информации.

Формула изобретения

Многопроцессорная система, содержащая четыре вычислительных модуля, каждый из которых содержит контроллер, блок арбитра и селектор адреса, причем в каждом вычислительном модуле адресные выходы контрлллера соединены с

информационными входами селектора адреса, выход разрешения вывода блока арбитра соедин г дноименным входом контроллера, f u, запроса вывода которого подключен к одноименному входу блока арбитра, выход занятости блока арбитра К- го вычислительного модуля (К 1...3) подключен к одноименному входу блока арбитра (К+1)-го вычислительного модуля,

0 отличающаяся тем, что, с целью увеличения надежности и достоверности выдаваемой информации, в каждый вычислительный модуль введены элемент И. элемент задержки, блок формирования

5 свертки, блок контроля и блок реконфигурации, причем выход занятости блока арбитра четвертого вычислительного модуля соединен с одноименным входом блока арбитра первого вычислительного модуля, вход бло0 кировки блока арбитра в каждом вычислительном модуле соединен с одноименным выходом блока реконфигурации, выходы останова начальной установки и признака отказакоторогосоединеныс

5 соответствующими одноименными входами контроллера, причем выход признака отказа блока реконфигурации К-го вычислительного модуля (К 1...4) подключен также к К-му входу группы входов состояния систе0 мы, контроллеров всех вычислительных модулей в каждом вычислительном модуле, вход прерывания контроллера соединен с первым выходом селектора адреса, второй выход которого соединен с первым входом

5 элемента И, второй вход которого соединен с выходом строба выдачи данных контроллера, выход элемента И соединен с входом записи блока формирования свертки, информационные входы которого соединены с

0 выходами данных контроллера, а вход начальной установки блока формирования свертки через элемент задержки соединен с выходом подтверждения прерывания контроллера, выход подтверждения прерывания

5 контроллера К-го вычислительного модуля соединен с К-ми входами записи блоков контроля остальных вычислительных модулей, выходы блока формирования свертки К-го(К 1,4) вычислительного модуля соединены с

0 информационными входами К-й группы блоков контроля остальных вычислительных модулей, в каждом вычислительном модуле вход начальной установки блока контроля соединен с первым выходом записи конт5 роллера, выходы данных блока контроля подключены к входам данных контроллера, выходы чтения которого соединены с входами чтения блока контроля, К-й (К 2...4) выход записи контроллера М-го (М 0 ... 3) вычислительного модуля соединен с (К 1) м

входом блока реконфигурации МОД (М- К-лительного модуля через шину соединрны i

-1)-го (МОД - остаток отделения на четыре)одноименными входами К-й группы h/тюв

вычислительного модуля, выходы отказа,реконфигурации всех вычислительных мо

сбоя и блокировки контроллера К-го вычис-дулей

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Система обработки информации | 1990 |

|

SU1795468A1 |

| МНОГОПРОЦЕССОРНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 1993 |

|

RU2054710C1 |

Изобретение относится к вычислительной технике и может использоваться для построения надежных многопроцессорных контроллеров. Цель изобретения - увеличение надежности и достоверности выдаваемой информации. Система содержит вычислительные модули 1, блок 2 арбитра, блок 3 реконфигурации, контроллер 4, блок 5 контроля, селектор 6 адреса, элемент И 7, блок 8 формирования свертки и элемент 9 задержки, б ил.

ю,

Юг Ю

12

Щ

п,

И2

11

Фиг. 2

ФигМ

Фиг. з

§-откр 1тыу коллектор

Фив. 5

Ввод, обработка информации, эяпнсь по прерыванию спортки контрольной информации в блок 5, чтение собственной свертки

Чтение регистра II до появления признаков записи от активных блоков 4 о соответствии со словом состояния

Чтение контрольной информации от активного блока 4 и ожидание и точение TMCLK рассинхро- ниэации другого блоха 4, если он есть

Если ожидаемый блок 4 не выдал информацию, пометить его неисправным и начать голосование контрольной ин|Ьопмаиии

Если есть несовпадение, выдать остамор на соответствующий блок 4 /разряд регистра 21/

Запрос на вывод, если есть разрешение - начать вывод /сигнал окончания вывода/; иначе ждать окончания вывода

Если был сигнал останова, то если есть резерв и это отказ, то заблокировать арбитр этого блока 4, разблокировать резервный блок 4. Общий сброс Если сбой - то общий сброс

L

ФЪ+С

| Резервированная система | 1982 |

|

SU1101827A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Григорьев В.Л | |||

| Программирование однокристальных микропроцессоров | |||

| М.: Энергоатомиздат, 1987, с.273-276 | |||

Авторы

Даты

1991-10-23—Публикация

1989-08-29—Подача