Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении вычислительных систем повышенной надежности.

Известно резервированное устройство, содержащее два основных и S резервных блоков, блок контроля, выходной блок, позволяющее при несовпадении выходных сигналов основных блоков подключать взамен отказавшего блока исправный из резерва. Недостатком этого устройства является большое количество ненагруженного резервного оборудования.

Наиболее близким по технической сущности к предлагаемой вычислительной системе является резервированная вычислительная система, содержащая резервированные процессоры, коммутаторы вывода информации, модули памяти, устройство для управления реконфигурацией вычислительной системы, коммутаторы вывода информации и блок сравнения. Контроль функционирования системы обеспечивается параллельной работы пары процессоров в течение такта контроля путем сравнения конечных результатов. Обнаружение отказавшего процессора осуществляется путем анализа параллельной работы следующей пары процессоров [1] Недостатком такой системы является невозможность обнаружения нарушений правильности функционирования процессоров вычислительной системы, которые не влияют на конечные результаты работы выполняемых программ за время такта контроля.

Программы, выполняемые на процессорах, могут быть связаны с обработкой массивов информации, могут предполагать вычисление промежуточных результатов, которые используются другими процессорами. В этом случае неисправность процессора не всегда повлечет за собой искажение конечного результата работы выполняемой программы.

Целью изобретения является повышение достоверности контроля функционирования резервированной вычислительной системы.

Достигается это тем, что в резервированную вычислительную систему, содержащую первый, второй и третий резервируемые процессоры, первый, второй и третий коммутаторы вывода информации, первый и второй модули памяти, первый, второй и третий коммутаторы ввода информации, четвертый коммутатор ввода информации, введены регистр на триггерах со счетными входами, первый и второй элементы ИЛИ, триггер со счетным входом, первый и второй элемент И, первый и второй элемент задержки, причем каждый процессор включает в свой состав узел контроля, содержащий многоканальный сигнатурный анализатор, первый и второй RS-триггеры, третий элемент И. Первый и второй управляющие входы узла контроля подключены соответственно к S-входам первого и второго RS-триггера, выходы которых соединены соответственно с первым и вторым входами третьего элемента И, выход третьего элемента И подключен к выходу уведомления узла контроля, третий управляющий вход узла контроля подключен к входам сброса первого и второго RS-триггеров и многоканального сигнатурного анализатора, четвертый и пятый управляющие входы узла контроля соединены соответственно с синхровходом и управляющим входом многоканального сигнатурного анализатора. Информационные входы и выходы многоканального сигнатурного анализатора объединены в двунаправленную информационную шину узла контроля, выходы уведомления узлов контроля первого, второго, третьего процессоров подключены соответственно к первому, второму, третьему входам второго элемента ИЛИ и к первому, второму, третьему входам управления четвертого коммутатора вывода информации. Информационный выход четвертого коммутатора вывода информации подключен к счетным входам триггеров регистра, выходы которого соединены с входами первого элемента ИЛИ. Выход первого элемента ИЛИ подключен к первому входу первого элемента И, выход второго элемента ИЛИ подключен к входу первого элемента задержки, к входу счетного триггера и синхровходу регистра на триггерах со счетными входами. Инверсный выход триггера со счетным входом подключен к первому входу второго элемента И, второй вход которого соединен с выходом первого элемента задержки. Выход второго элемента И соединен с вторым входом первого элемента И, выход которого является выходом сигнала об ошибке и подключен к входу второго элемента задержки. Выход второго элемента задержки подключен к входу сброса регистра на триггерах со счетными входами.

Сопоставительный анализ с аналогами и прототипом показывает, что заявляемая система отличается наличием новых элементов и связей между ними.

Таким образом, заявляемая вычислительная система соответствует критерию "новизна".

Сравнение заявляемого решения с другими техническими решениями показывает, что введенные в устройство элементы вычислительной техники широко известны.

Однако при их введении в указанной связи с остальными элементами схемы в заявляемую вычислительную систему, последняя приобретает дополнительное свойство обнаруживать нарушения правиль- ности функционирования, которые не приводят к искажению конечного результата работы выполняемых программ. Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

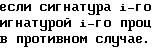

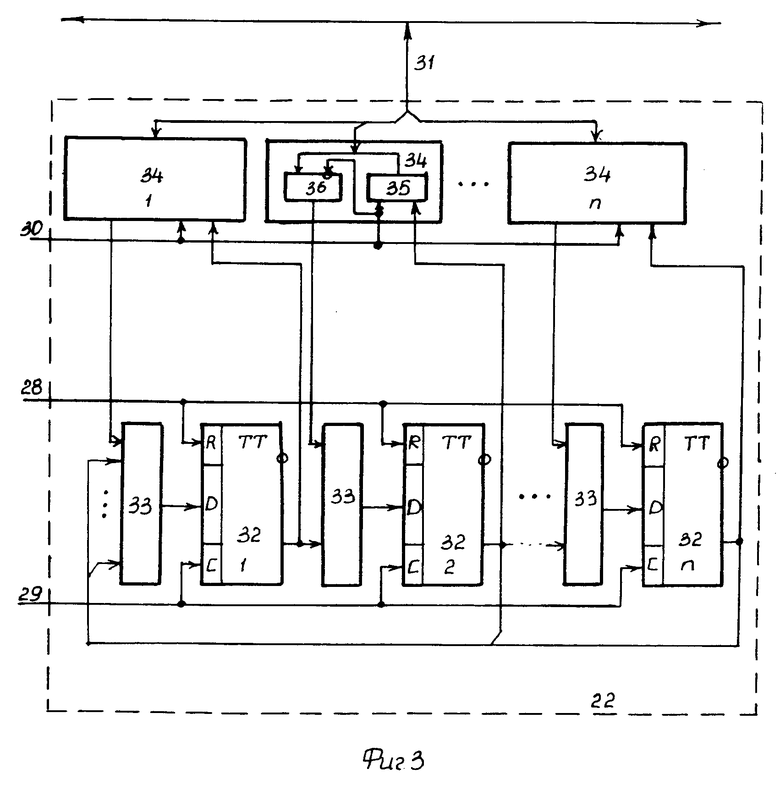

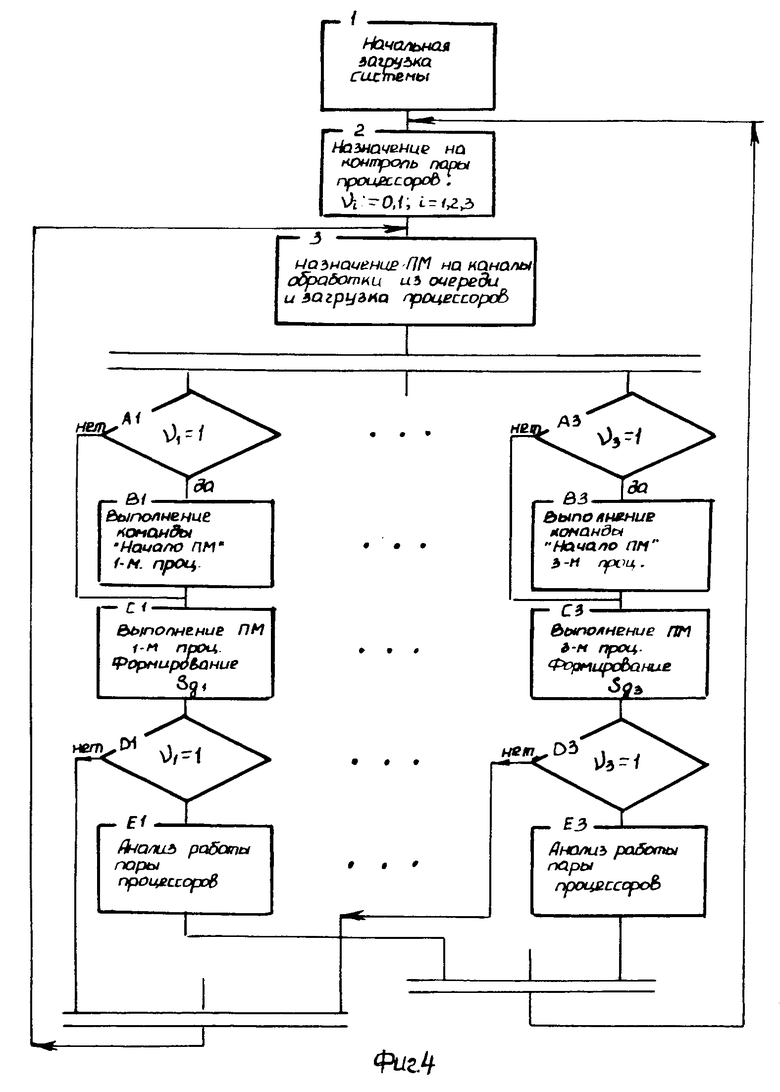

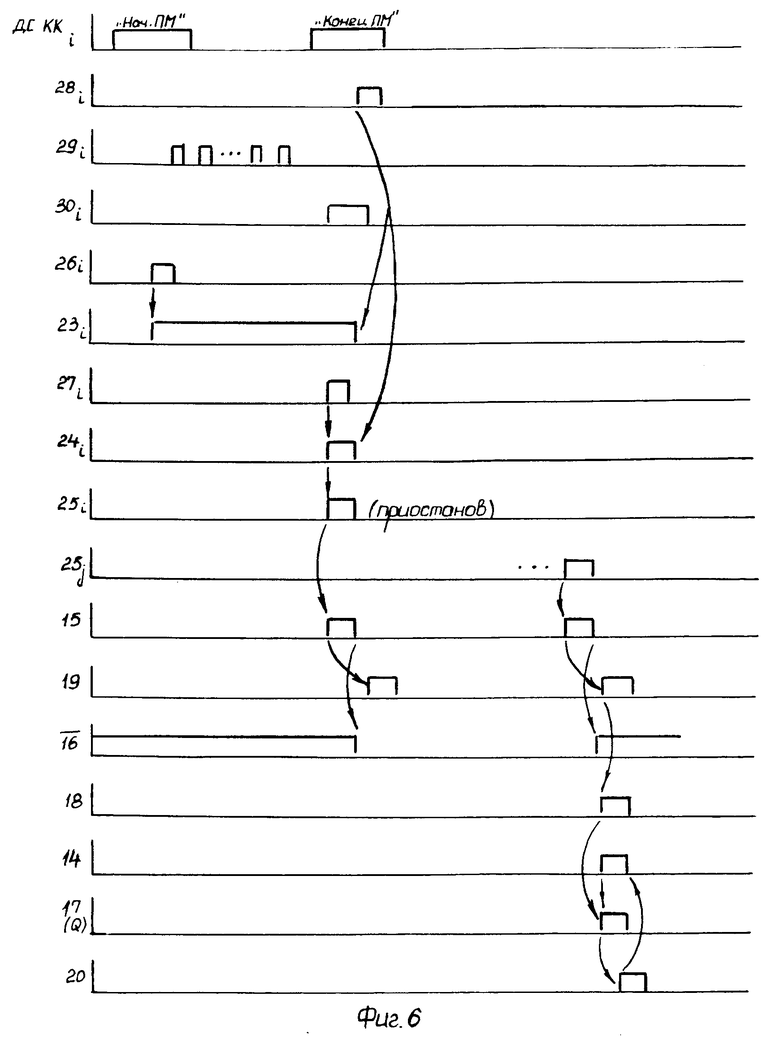

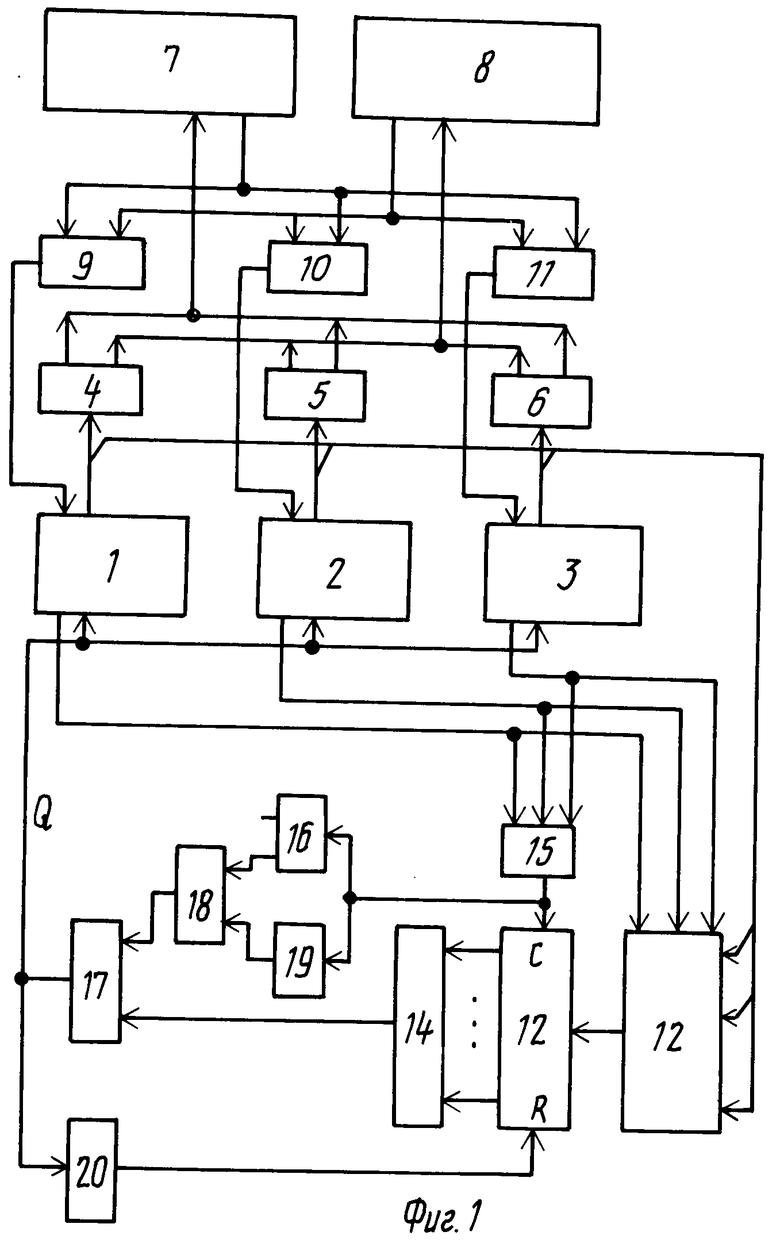

На фиг. 1 приведена структурная схема резервированной вычислительной системы; на фиг. 2 структурная схема узла контроля одного процессора; на фиг. 3 схема многоканального сигнатурного анализатора; на фиг. 4, 5 алгоритм управления контролем и реконфигурацией резервированной вычислительной системы; на фиг. 6 временные диаграммы работы средств контроля резервированной вычислительной системы.

Резервированная вычислительная система содержит первый 1, второй 2 и третий 3 процессоры, первый 4, второй 5 и третий 6 коммутаторы вывода информации, первый 7 и второй 8 модули памяти, первый 9, второй 10 и третий 11 коммутаторы ввода информации, четвертый коммутатор 12 вывода информации, регистр на триггерах со счетными входами 13, первый элемент ИЛИ 14, второй элемент ИЛИ 15, триггер со счетным входом 16, первый элемент И 17, второй элемент И 18, первый и второй элементы задержки 19, 20, причем каждый процессор содержит узел контроля 21. Узел контроля 21 (фиг. 2) содержит многоканальный сигнатурный анализатор 22, первый и второй RS-триггеры 23, 24, третий элемент И 25. Первый, второй, третий, четвертый и пятый управляющие входы 26, 27, 28, 29, 30 узла контроля являются выходами формирователя управляющих сигналов процессора, по которым подаются сигналы начала такта контроля данного процессора пары, окончания такта контроля данного процессора пары, сброса, синхронизации, управления выдачей данных многоканального сигнатурного анализатора. Двунаправленная шина узла контроля 31 является внутренней шиной данных и команд процессора.

Многоканальный сигнатурный анализатор 22 (фиг. 3) содержит регистр сдвига, состоящий из n двухтактных триггеров 32, n сумматоров по модулю два 33 и n шинных формирователей 34, каждый из которых включает в свой состав два элемента И 35, 36.

Первый, второй, третий информационные входы четвертого коммутатора вывода информации 12 соединены соответственно с информационными выходами первого 1, второго 2, третьего 3 процессоров, информационные выходы первого 1, второго 2, третьего 3 процессоров подключены соответственно к информационным входам первого 4, второго 5, третьего 6 коммутаторов вывода информации, первые информационные выходы которых соединены с информационными входами первого 7 модуля памяти. Вторые информационные выходы первого 4, второго 5, третьего 6 коммутаторов вывода информации соединены с информационным входом второго 8 модуля памяти, информационный выход первого 7 модуля памяти подключен к первым информационным входам первого 9, второго 10, третьего 11 коммутаторов ввода информации, информационный выход второго модуля памяти подключен ко вторым информационным входам первого 9, второго 10, третьего 11 коммутаторов ввода информации, неинформационные выходы которых соединены соответственно с информационными входами первого 1, второго 2, третьего 3 процессоров. Первый 26 и второй 27 управляющие входы узла контроля 21 подключены соответственно к S-входам первого 23 и второго 24 RS-триггера, выходы которых соединены соответственно с первым и вторым входами третьего 25 элемента И, выход которого подключен к выходу уведомления узла контроля, третий 28 управляющий вход узла контроля подключен к входам сброса первого 23, второго 24 RS'-триггеров и многоканального сигнатурного анализатора 22, четвертый 29 и пятый 30 управляющие входы узла контроля соединены соответственно с синхровходом и управляющим входом многоканального сигнатурного анализатора 22, двунаправленная шина узла контроля 31 подключена к внутренней шине данных и команд процессора, выходы уведомления узлов контроля первого 1, второго 2, третьего 3 процессоров подключены соответственно к первому, второму, третьему входам второго элемента ИЛИ 15 и к первому, второму, третьему входам управления четвертого коммутатора вывода информации 12, информационный выход которого подключен к счетным входам триггеров регистра 13. Выходы регистра на триггерах со счетными входами 13 соединены с входами первого элемента ИЛИ 14, выходы которого подключены к первому входу первого элемента И 17, выход второго элемента ИЛИ 15 подключен к входу первого элемента задержки 19 к входу счетного триггера 16 и синхровходу регистра на триггерах со счетными входами 13. Выход первого элемента задержки 19 и инверсный выход счетного триггера 16 соединены соответственно с первым и вторым входом второго элемента И 18, выход которого подключен к второму входу первого элемента И 17. Выход первого элемента И 17 является выходом сигнала об ошибке Q и подключен к входу второго элемента задержки 20 и к входу прерывания первого 1, второго 2, третьего 3 процессоров, выход второго элемента задержки 20 соединен с входом сброса регистра на триггерах со счетными входами 13.

В сигнатурном анализаторе 22 первые входы сумматоров по модулю два 33 подключены к выходам элементов И 36 соответствующих шинных формирователей 34, выходы сумматоров по модулю два 33 соединены с информационными входами соответствующих триггеров 32. Информа- ционный выход каждого i-го триггера 32 подключен ко второму входу (i + 1)-го сумматора 33. Кроме этого, к остальным входам первого сумматора 33 подключены выходы триггера 32 в соответствии с заданным характеристическим полиномом. Выходы триггеров 32 подключены к первым входам элементов И 35 соответствующих шинных формирователей 34. Выходы элементов И 35 соединены соответственно с прямыми входами элементов И 36 и подключены к двунаправленной шине узла контроля 31. Инверсный вход элемента И 36 соединен со вторым входом элемента И 35 соответствующего шинного формирователя и подключен к управляющему входу узла контроля 30.

Шинный формирователь 34 работает следующим образом.

По единичному значению сигнала на управляющем входе 30 сигнал с первого входа элемента И 35 через элемент И 35 поступает на линию двунаправленной шины 31. По нулевому значению сигнала на управляющем входе 30 имеет место передача сигнала с линии двунаправленной шины 31 на выход элемента И 36.

Шинным формирователем двунаправленной шины 31 может являться микросхема серии К569АП26.

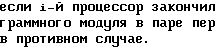

Контроль правильности функционирования резервированной вычислительной системы заключается в следующем. Программа разбивается на функционально законченные программные модули (ПМ). Время выполнения вычислительной системы задачи разбивается на N тактов контроля. Такт контроля соответствует времени выполнения в процессоре отдельного ПМ. На выполнение каждого ПМ назначается один канал обработки, который представляет собой либо пару параллельно работающих процессоров (полный канал обработки), либо один процессор (неполный канал обработки). В начале каждого такта контроля происходит назначение ПМ на канал обработки из очереди и загрузка процессоров. Во время выполнения программного модуля парой процессоров с внутренней шины данных каждого из них формируется сигнатура команд и (или) данных. Это позволяет по окончании выполнения программного модуля парой процессоров выявить наличие отказа или сбоя одного из процессоров путем сравнения полученных сигнатур. В случае несовпадения полученных сигнатур осуществляется повторный счет данного программного модуля той же парой процессоров. Если при повторном счете произошло совпадение сформированных сигнатур, то делается вывод о возникновении слоя в предыдущем такте контроля. Если при повторном счете вновь произошло несовпадение сигнатур, то в следующем такте путем анализа параллельной работы следующей пары процессоров определяется какой из процессоров отказал. Если в третьем такте контроля сигнатуры не совпали, то отказал тот процессор, который работал в этой и в предыдущей паре. Если же сигнатуры совпали, то отказал процессор, который работал в предыдущей паре.

Варианты назначения процессоров в пары для контроля представлены в таблице.

Работа резервированной вычислительной системы может быть представлена в виде алгоритма (фиг. 4). Сущность реализации алгоритма заключается в выполнении следующих действий.

Символ 1. Выполняются процедуры начальной нагрузки вычислительной системы.

Символ 2. Выполняется процедура назначения на контроль пары процессоров, которая формирует вектор ν= (ν1, ν2,ν3). Причем νi 1. Когда i-й процессор включен в пару взаимопроверяемых процессоров (i 1, 2, 3).

Символ 3. Выполняется процедура назначения и загрузки ПМ на канал обработки из очереди готовых к выполнению ПМ. Функция процедуры заключается в том, что из очереди выбирается ПМ и осуществляется загрузка процессора для его выполнения.

Символы А 1.3. Проверяется входит ли i-й процессор в пару взаимопроверяемых процессоров. Если условие выполняется, то осуществляется переход к символу В 1.3, иначе осуществляется переход к символу С 1.3 соответственно.

Символы В 1.3. Устанавливается факт начала выполнения ПМ в процессоре полного канала обработки, путем исполнения команды: "Начало программного модуля".

Символы С 1.3. Выполнение назначенных ПМ на соответствующих процессорах, а также формирование сигнатуры последовательности команд и (или) данных этого ПМ в сигнатурном анализаторе.

Символы D 1.3. Выполняют действия аналогично символам А 1.3. Если νi 1, то переход к символам Е 1.3 соответственно, иначе переход к символу 3.

Символы Е 1.3. Выполнение процедуры анализа работы пары процессоров. Процедура анализа работы представлена следующими символами (фиг. 5).

Символ е 1. Устанавливается факт окончания выполнения ПМ i-м процессором путем исполнения команды "Конец программного модуля".

Символ е 2. Вывод сигнатуры i-го процессора в регистр 13.

Символ е 3. Проверяется: первым ли i-й процессор в паре взаимопроверяемых процессоров закончил выполнение ПМ. Переменная μ может принимать следующие значения:

μ

о

о в

в

Если μ 1, то выполняются символы е 4, е 5, е 6, иначе выполняются символы е 7, е 8.

Символы е 4. Сравниваются сигнатуры пары взаимопроверяемых процессоров i и j в регистре 13 (i,j 1, 2, 3, i ≠ j) и вырабатывается сигнал Q:

Q

с

с е

е

Символ е 5. Сигнал Q передается в регистр состояния контроллера прерывания процессора.

Символ е 6. Анализируется возникшая ситуация. При Q 0 работа пары взаимопроверяемых процессоров считается правильной. При Q 1 назначается повторный счет, либо производится назначение пары взаимопроверяемых процессоров. В этом случае работа резервированной вычислительной системы считается неправильной.

После выявления отказавшего процессора производится реконфигурация резервируемой вычислительной системы, которая заключается в исключении отказавшего процессора из ресурсов системы. Переход к символу 2.

Символ е 7. Переменной μ присваивается значение, равное единице.

Символ е 8. Процессор, который первым завершил выполнение ПМ из пары взаимопроверяемых процессоров, приостанавливается до момента завершения выполнения идентичного ПМ другим процессором. Переход к символу 2.

Реализация данного алгоритма функционирования резервированной системы может быть возложена на операционную систему. Команды "Начало программного модуля" и "Конец программного модуля" представляют собой специальные команды операционной системы. При выполнении в процессоре команды "Начало программного модуля" разрешается формирование сигнатуры последовательности команд или команд и данных в сигнатурном анализаторе 22. При выполнении в процессоре команды "Конец программного модуля" осуществляется выдача сформированной сигнатуры из сигнатурного анализатора 22 на информационный выход процессора.

Разбиение программы на ПМ может быть осуществлено специальной программой операционной системы, которая перед выполнением ПМ осуществляет выдачу в процессор для исполнения команды "Начало программного модуля" после выполнения ПМ. Такие действия выполняются всякий раз на процессорах, входящих в пару, перед выполнением и после выполнения ПМ.

Резервированная вычислительная система работает следующим образом.

Перед началом выполнения программных модулей на процессорах производится начальная загрузка системы. После этого назначается на контроль пара процессоров.

Пусть в полный канал обработки включены первый и второй процессоры, а в неполный канал обработки третий процессор.

Предварительно выполняются начальные установки процессоров и сброс в нулевое состояние сигнатурного анализатора 22, триггеров 23, 24, 16 и регистра 13 (на фигурах цепи сброса условно не показаны). Затем назначаются ПМ из очереди на каналы обработки и осуществляется загрузка процессоров. После этого в первом и втором процессорах выполняются команды "Начало программного модуля". По этой команде на одном из выходов дешифратора кода команд процессора вырабатывается управляющий сигнал, который поступает в формирователь управляющих сигналов процессора, имитируя в нем выработку сигналов на входах 26, 27, 28, 29, 30 в соответствующие моменты времени (фиг. 6).

По сигналу на входе 26 узла контроля, вырабатываемого в результате исполнения команды "Начало программного модуля", первый RS-триггер 23 устанавливается в единичное состояние. На выходе формирователя управляющих сигналов процессора вырабатывается сигнал нулевого потенциала, который по входу 30 поступает на инверсные входы элементов И 36 шинных формирователей 34 сигнатурного анализатора и подключает двунаправленную шину 31 узла контроля 21 на прием информации.

Затем выполняется последовательность команд ПМ, назначенного на данный процессор.

Адрес первой команды ПМ передается в памяти для выборки команды. Считанная из памяти команда, поступает на информационный вход процессора и через порт ввода-вывода процессора на внутреннюю шину данных и команд процессора. Одновременно из формирователя управляющих сигналов процессора по входу 29 поступает синхроимпульс, по которому осуществляется свертка считанной команды в сигнатурном анализаторе 22. Считанная из памяти команда принимается в регистр команд процессора для выполнения. После этого формируются адреса операндов данной камеры, которые передаются в память. Считанные из памяти операнды сворачиваются в сигнатурном анализаторе 22 аналогичным образом.

В дальнейшем сигнатурный анализатор 22 осуществляет свертку остальных команд и (или) данных ПМ.

Пусть в данном такте контроля процессор 1 закончил выполнение ПМ первым. Тогда в нем выполняется команда: "Конец программного модуля". Код операции команды передается на вход дешифратора из команд процессора, где декодируется и единичный сигнал с одного из его выходов поступает в формирователь управляющих сигналов процессора.

По сигналу с выхода дешифратора на выходе формирователя управляющих сигналов вырабатывается сигнал единичного потенциала, который поступает по входу 30 в сигнатурный анализатор 22. По этому сигналу в сигнатурном анализаторе двунаправленная шина 31 узла контроля переключается на передачу содержимого сигнатурного анализатора 22 через порт ввода-вывода на информационный выход процессора через элемент И 35. Одновременно по сигналу с выхода формирователя управляющих сигналов процессора по входу 27 осуществляется установка триггера 24 в единичное состояние. Сигналы единичных потенциалов с выходов первого 23 и второго 24 TS+триггеров поступают на первый и второй входы элемента И 25, на выходе которого вырабатывается сигнал единичного потенциала. Сигнал с выхода элемента И 25 поступает на первый вход элемента ИЛИ 15 и на первый управляющий вход коммутатора 12. По сигналу на первом управляющем входе коммутатора 12 осуществляется коммутация информационного выхода первого процессора на вход регистра 13. Сигнал с выхода элемента И 25 через элемент ИЛИ 15 поступает на синхровход регистра 13, по которому осуществляется запись сформированной в первом процессоре сигнатуры в первый ярус триггеров регистра 13.

Одновременно сигнал с выхода ИЛИ 15 поступает на вход первого элемента задержки 19 и на счетный вход триггера 16. После этого на выходе формирователя управляющих сигналов вырабатывается сигнал сброса, который по входу 28 сбрасывает в нулевое состояние сигнатурный анализатор 22 и триггера 23 и 24. Сигналы нулевых потенциалов с выходов триггеров 23 и 24 поступают соответственно на первый и второй входы элементов И 25, на выходе которого формируется сигнал нулевого потенциала. Нулевой уровень сигнала на выходе элемента И 25 через элемент ИЛИ 15 передается на вход триггера со счетным входом 16, устанавливая его в единичное состояние, а также на синхровход регистра 13, по которому осуществляется запись содержимого первого яруса триггеров регистра 13 во второй ярус.

После этого процессор 1 приостанавливается до момента окончания выполнения ПМ вторым процессором. После окончания выполнения ПМ во втором процессоре в нем осуществляется исполнение команды "Конец программного модуля" и выдача сформированной сигнатуры на информационный выход процессора. Одновременно вырабатывается сигнал единичного потенциала на выходе элемента И 25 второго процессора, который поступает на второй вход элемента ИЛИ 15 и на второй управляющий вход коммутатора 12. По сигналу на втором управляющем входе коммутатора 12 осуществляется передача информации второго процессора на вход регистра 13. Сигнал с выхода элемента И 25 второго процессора через элемент ИЛИ 15 поступает на синхровход регистра 13, по которому в регистре формируется поразрядная сумма по модулю два содержимого регистра с информацией на его входах и запись сформированной суммы в первый ярус триггеров регистра 13.

После этого формирователем управляющих сигналов на входе 28 узла контроля вырабатывается сигнал сброса, по которому сигнатурный анализатор 22 и триггера 23, 24 второго процессора сбрасываются в нулевое состояние. На выходе элемента И 25 второго процессора формируется сигнал нулевого потенциала. По сигналу с выхода элемента И 25 осуществляется запись сформированной поразрядной суммы из первого яруса триггеров регистра 13 во второй ярус, а также сброс триггера 16 в нулевое состояние. Сигнал единичного потенциала с инверсного выхода триггера 16 поступает на первый вход элемента 18, на второй вход которого подается сигнал с выхода элемента задержки 19. Величина задержки выбирается такой, чтобы обеспечить выработку сигнала Q после приема сигнатуры второго процессора пары в регистр 13.

Пусть процессоры 1 и 2 в данном такте контроля работали правильно. Тогда в результате поразрядной суммы по модулю два сигнатуры сформированной в первом процессоре с сигнатурой второго процессора произойдет обнуление разрядов регистра 13. Нулевые сигналы с выходов регистра 13 поступают на входы элемента ИЛИ 14, на выходе которого формируется сигнал нулевого потенциала. По сигналу с выхода элемента И 18 сигнал с выхода элемента ИЛИ 14 через элемент И 17 поступает на вход прерывания контроллера прерывания каждого процессора. Так как в рассматриваемом случае произошло сравнение сигнатур пары взаимопроверяемых процессоров и сигнал Q 0, то в результате анализа содержимого регистра состояния контроллера прерывания делается вывод о правильной работе пары процессоров.

Затем первый процессор выходит из состояния ожидания, осуществляется назначение и подготовка к работе новой пары взаимопроверяемых процессоров. Аналогичным образом происходит функционирование резервированной вычислительной системы в следующем такте контроля.

Пусть процессоры 1 и 2 в текущем такте контроля работали неверно. Тогда в результате сравнения сигнатур первого и второго процессоров в регистре 13 на выходе элемента И 17 вырабатывается сигнал ошибки Q единичного потенциала, который поступает на вход прерывания каждого процессора и на вход элемента задержки 20. Сигнал Q, задержанный на элементе задержки 20, поступает на вход сброса регистра 13, обнуляя его. Величина задержки выбирается такой, чтобы обеспечить прием сигнала об ошибке Q в регистр состояния контроллера прерывания процессора. По единичному содержимому соответствующего триггера регистра состояния контроллера прерывания второго процессора делается вывод о неверной работе пары процессоров.

После этого назначается режим повторного счета, либо предназначение пары взаимопроверяемых процессоров После выявления отказавшего процессора производится реконфигурация вычислительной системы.

Таким образом, предлагаемая резервированная вычислительная система по сравнению с известной обеспечивает обнаружение нарушений правильности функционирования процессоров вычислительной системы, которые не влияют на конечные результаты работы выполняемых программ за время такта контроля, а также не требует жесткой синхронизации работ пары взаимопроверяемых процессоров при выполнении одинаковых ПМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1377859A1 |

| Устройство для управления резервированной вычислительной системой | 1989 |

|

SU1755399A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645959A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных систем повышенной надежности. Сущность изобретения состоит в формировании и сравнении сигнатур потока команд и/или/ данной пары взаимопроверяемых вычислительных блоков. Резервированная вычислительная система содержит три вычислительных блока 1,2,3, три блока вывода 4,5,6, два блока памяти 7,8, три блока ввода 9,10,11, коммутатор 12, регистр 13, два элемента ИЛИ 14,15, триггер 16, два элемента И 17,18, два элемента задержки 19,20. Каждый вычислительный блок содержит блок контроля 21, содержащий многоканальный сигнатурный анализатор 22, первый и второй триггеры 23,24, элемент И 25 и обеспечивающий проверку функционирования пары вычислительных блоков в каждом такте контроля. Такт контроля соответствует времени выполнения в вычислительном блоке отдельного программного модуля. На взаимопроверяемые вычислительные блоки назначаются одинаковые программные модули. Контроль осуществляется путем формирования в каждом такте контроля двух сигнатур каждой пары вычислительных блоков. Результат сложения по модулю два этих двух сигнатур при правильной работе пары вычислительных блоков равен нулю, а в случае появления неисправности, приводящей к нарушению правильной работы, равен единице. 1 з.п. ф-лы, 6 ил. 1 табл.

| Трехканальная резервированная вычислительная система | 1983 |

|

SU1156274A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1995-07-09—Публикация

1991-06-05—Подача