Изобретение относится к вычислительной технике и может быть использовано для автоматизации научных и прикладных исследований, а также при создании высокопроизводительных и высоконадежных вычислительных комплексов.

Известна система, содержащая микропроцессор с памятью, процессор управления каналом данных, программную память, мультиплексор, адресный регистр, регистр страниц, процессор обработки прерываний, регистр данных позволяет производить обработку информации, но обладает недостаточным быстродействием.

Также известна система, содержащая две ЭВМ второго уровня, два канала второго уровня, два блока сопряжения, два адап- тера, блок коммутации, блок шин и каналы первого уровня, позволяет производить автоматизацию исследований, но обладает недостаточным быстродействием ввиду больших затрат времени на программные переключения коммутатора каналов.

Наиболее близким техническим решением является система, содержащая первый и второй вычислительные блоки второго уровня, первый и второй блоки сопряжения, первую и вторую группы блоков обработки информации, блок умощнения магистрали, вторые входы-выходы которого соединены с входами-выходами блоков обработки информации второй группы, блок арбитра магистрали, входы-выходы которого соединены с входами-выходами блоков обработки информации второй группы, первые входы-выходы блока умощнения магистрали соединены с первыми входами- выходами первого и второго блоков сопряжения и входами-выходами блоков обработки информации первой группы, входы-выходы первого и второго вычислительных блоков второго уровня соединены с вторыми входами-выходами первого и второго блоков сопряжения соответственно, позволяет автоматизировать исследования. В прототипе сбой информации на любом из

Х|

ю ел

4

о

00

информационных входов-выходов системы не будет замечен системой и приведет к снижению достоверности обрабатываемой информации и низкой эффективности ее обработки. Выход из строя любого узла в блоке обработки информации (блока связи, вычислительного блока и т.д.) приведет к нарушению работоспособности всего информационного канала, потере большого объема информации и к снижению надежности работы системы, а обработка больших объемов некорректированной информации конечными вычислительными устройствами (ступенями) приводит к большим временным затратам на выполняемые операции.

Цель изобретения - повышение надежности системы за счет передачи функций отказавших вычислительных блоков блокам из ненагруженного резерва и коррекции обрабатываемых данных.

Это достигается тем, что в известную систему, содержащую первый и второй вычислительные блоки, группу из Н вычислительных блоков, первый и второй блоки сопряжения, арбитр магистрали и расширитель магистрали, причем информационные входы-выходы первой группы первого вычислительного блока подключены соответственнок информационным входам-выходам первой группы первого блока сопряжения, информационные входы-выходы первой группы второго вычислительного блока подключены соответственно к информационным входам-выходам первой группы второго блока сопряжения, информационные входы-выходы второй группы первого блока сопряжения, инфор- маиионные входы-выходы второй группы второго блока сопряжения и информационные входы-выходы вычислительных блоков С первого по Н/2-й группы соединены через первую магистраль и подключены соответственно к информационным входам-выходам расширителя магистрали, информационные входы-выходы второй группы которого через вторую магистраль соединены соответственно с информационными входами-выходами первой группы вычислительных блоков с (Н/2 - 1)-го по Н-й и подключены соотвтествнено к информационным входам-выходам арбитра магистрали, информационные входы-выходы групп с первой по Н-ю системы подключены соответственно к информационным входам- выходам вторых групп вычислительных блоков с первого по Н-й группы, при этом каждый вычислительный блок группы содержит узел сопряжения, вычислительный узел и узел ввода-вывода, причем в каждом

вычислительном блоке группы информационные входы-выходы первой группы блока подключены соответственно к информационным входам-выходам первой группы узла сопряжения, информационные входы-выхо- ды второй группы которого подключены соответственно к информационным входам-выходам первой группы вычислительного узла, информационные входы-вы

ходы второй группы которого подключены

соответственно к информационным входам- выходам первой группы узла ввода-вывода, информацинные входы-выходы второй группы которого подключены соответствен.5 но к информационным входам-выходам второй группы блока, введены третий вычислительный блок, третий блок сопряжения, мажоритарный узел и с первого по (Н/3 - 1)-й блоки контроля, при этом управляю0 щие входы-выходы а-ro, (а-1)-го и (а-2) вычислительных блоков группы (где а 1,...,Н-2) через (а-2)/3-ю магистраль управления подключены соответственно ко входу запуска (а-2)/3-го блока контроля, инфор5 мэционные выходы а-го, (а-1)-го и (а-2)-го вычислительного блока группы подключены соответственно к информационным входам первой, второй и третьей групп (а-2)/3-го блока контроля, первый, второй и третий

0 выходы которого подключены соответственно ко входам останова а-го, (а-1)-го и (а-2)-го вычислительных блоков группы, четвертый, пятый и шестой выходы (а-2)/3-го блока контроля подключены ко входам запуска а-го,

5 (а-1)-го и (а-2)-го вычислительных блоков группы, седьмой выход (а-2)/3-го блока контроля подключен к управляющим входам а- го,(а-1)-го и (а-2)-го вычислительных блоков группы, восьмой выход (а-2)/3-го блока кон0 троля подключен ко входам прерывания а-ro, (а-1)-го и (а-2)-го вычислительных блоков группы, информационные входы-выходы первой группы третьего вычислительного блока подключены соответственно к инфор5 ма.ционным входам-выходам первой группы третьего блока сопряжения, информационные входы-выходы второй группы которого через первую магистраль подключены к информационным входам-выходам вторых

0 групп первого и второго вычислительных . блоков, к информационным входам-выходам первых групп вычислительных блоков с первого по Н/2-й группы и к информационным входам-выходам первой группы расши5 рителя магистрали, информационные выходы первых групп первого, второго и третьего вычислительных блоков подключены соответственно к информационным входам первой, второй и третьей групп (Н/3-1)-го блока контроля, информациейные выходы второй группы первого, второго и третьего вычислительных блоков подключены соответственно к информационным входам первой, второй и третьей групп мажоритарного узла, выходы которого подключенысоответственно к информационным выходам системы, управляющие входы-выходы первого, второго и третьего вычислительных блоков через (а- 2)/3+1-ю магистраль управления соединены между собой и подключены соответственно ко входу запуска (Н 3/-1)-го блока контроля, первый, второй и третий выходы которого подключены соответственно ко входам останова первого, второго и третьего вычислительных блоков, четвертый, пятый и шестой выходы (Н/3-1)-го блока контроля подключены соответственно ко входам запуска первого, второго и третьего вычислительных блоков, седьмой выход (Н/3-1)-го блока контроля подключен к управляющим входам первого, второго и третьего вычислительных блоков, восьмой выход (Н/З-1-го блока контроля подключен ко входам прерывания первого, второго и третьего вычислительных блоков с первой по (Н/3-1)-ю группы входов входов задания резервных каналов системы подключены соответственно к информационным входам четвертых групп блоков контроля с первого по (Н/3-1)-й, при этом в каждом вычислительном блоке группы управляющий вход вычислительного блока подключен ко входу запуска тестовых проверок вычислительного узла, вход прерывания вычислительного блока подключен ко входу прерывания вычислительного узла, вход запуска вычислительного блока подключен ко входу запуска вычислительного узла, вход останова вычислительного блока подключен к управляющему входу блока ввода-вывода и ко входу останова вычислительного блока, управляющие входы-выходы группы которого подключены к управляющим входам-выходам вычислительного узла, причем каждый блок контроля содержит генератор тактовых импульсов, первый, второй и третий уз- лы сравнения, с первого по шестой триггеры, с первого по четвертый элементы НЕ, элемент задержки, с первого по шестой элементы И и элемент ИЛИ, при этом в каждом блоке контроля информационные входы первой группы блкоа подключены соответственно к информационным входам первых групп первого и второго узлов сравнения, выходы которых подключены соот- ветствнено к первым входам первого и второго элементов И, информационные входы второй группы подключены соответственно к информационным входам второй

группы первого узла сравнения и соответственно к информационным входам первой группы третьего узла сравнения, выход которого подключен к первому входу третьего 5 элемента И, выход которого подключен к первому входу элемента ИЛИ и к информационному входу первого триггера, выход которого подключен к первым входам четвертого и пятого элементов И, выходы кото0 рых подключены соответственно ко второму и к третьему выходам блока, информационные входы третьей группы которого подключенысоответственно к информационным входам вторых групп вто5 рого и третьего узлов сравнения, выход элемента ИЛИ подключен ко входу первого элемента НЕ, ко входам синхронизации второго, третьего и четвертого триггеров и к седьмому выходу блока контроля, первый,

0 второй и третий информационные входы четвертой группы которого подключены соответственно ко входам установки в единицу второго, третьего и четвертоого триггеров, выход второго триггера подклю5 чен к пятому выходу блока и ко входу второго элемента НЕ, выход которого подключен ко вторым входам первого и третьего элементов И, выход первого элемента И подключен ко второму входу элемента ИЛИ и к

0 информационному входу пятого триггера, выход которого подключен ко второму входу четвертого элемента И и к первому входу шестого элемента И, выход которого подключен к первому выходу блока, выход

5 третьего триггера подключен к шестому выходу блока и ко входу третьего элемента НЕ, выход которого подключен к третьему входу третьего элемента И и ко второму входу второго элемента И, выход которого подключен

0 к третьему входу элемента ИЛИ и к информационному входу шестого триггера, выход которого подключен ко вторым входам пятого и шестого элементов И, выход четвертого триггера подключен к четвертому выходу

5 блока и ко входу четвертого элемента НЕ, выход которого подключен к третьим вхй- дам первого и второго элементов И, выход первого элемента НЕ подключен ко входу элемента задержки, выход которого под0 ключей к восьмому выходу блока, вход запуска которого подключен ко входу запуска генератора тактовых импульсов, выход которого подключен ко входам синхронизации первого, пятого и шестого триггеров.

5 Заявляемое техническое решение отличается от прототипа наличием третьего вы- числительного узла, третьего блока сопряжения, мажоритарного узла, (Н/3:1) блоков контроля и новой организацией связей.

Предложенное решение осуществляется с помощью известных в науке и технике блоков и элементов. Однако решение, содержащее предложенный состав и соединение указанных блоков, нам неизвестно, Кроме того, достигнуто новое свойство совокупности указанных известных блоков, отличное от свойств, присущих в отдельности каждому отличительному признаку - по- вышение эффективности обработки откорретированных данных надежности системы и сокращение времени на конечную обработку данных за счет организации проверки входной информации, передачи функций отказавших блоков обработки ин- формации блокам из ненагруженного резерва и передачи вычислительным блокам, следующего уровня проверенных и откорректированных данных.

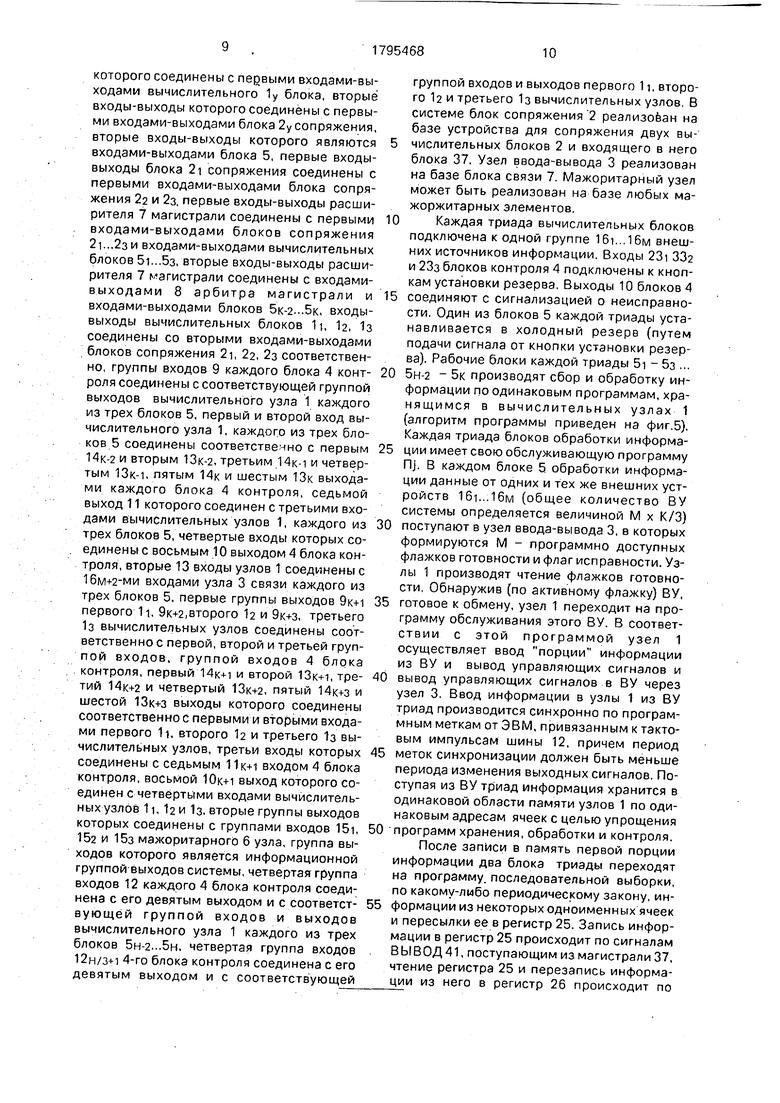

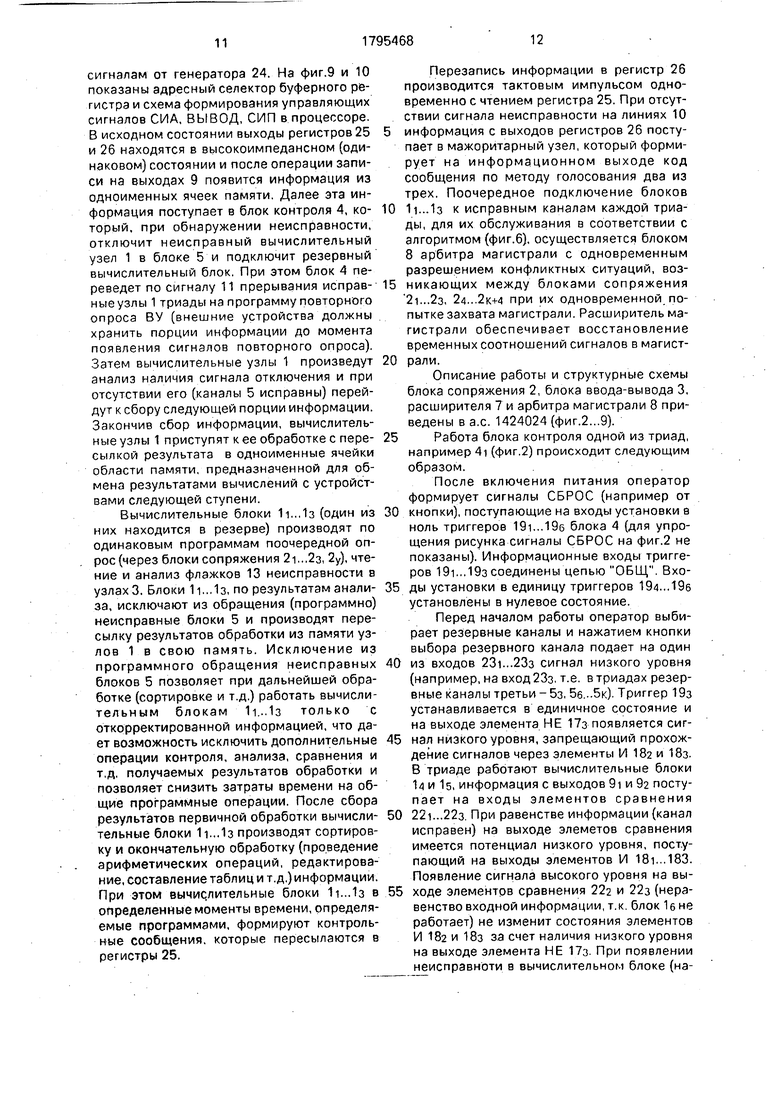

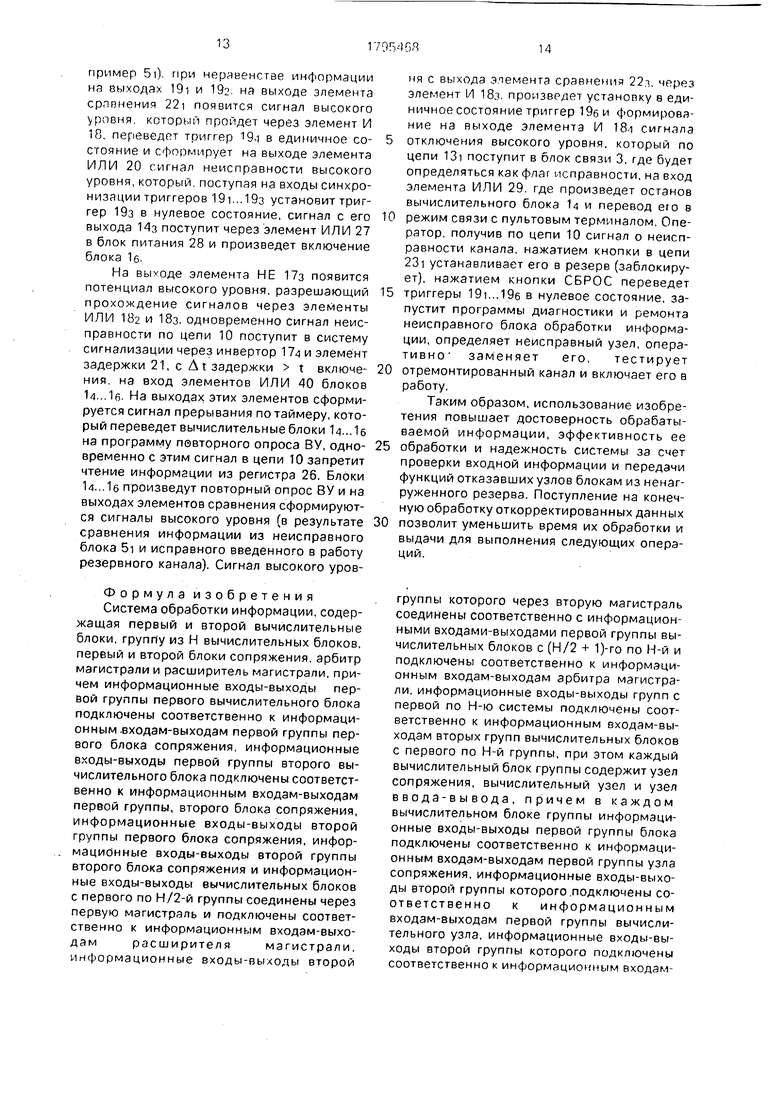

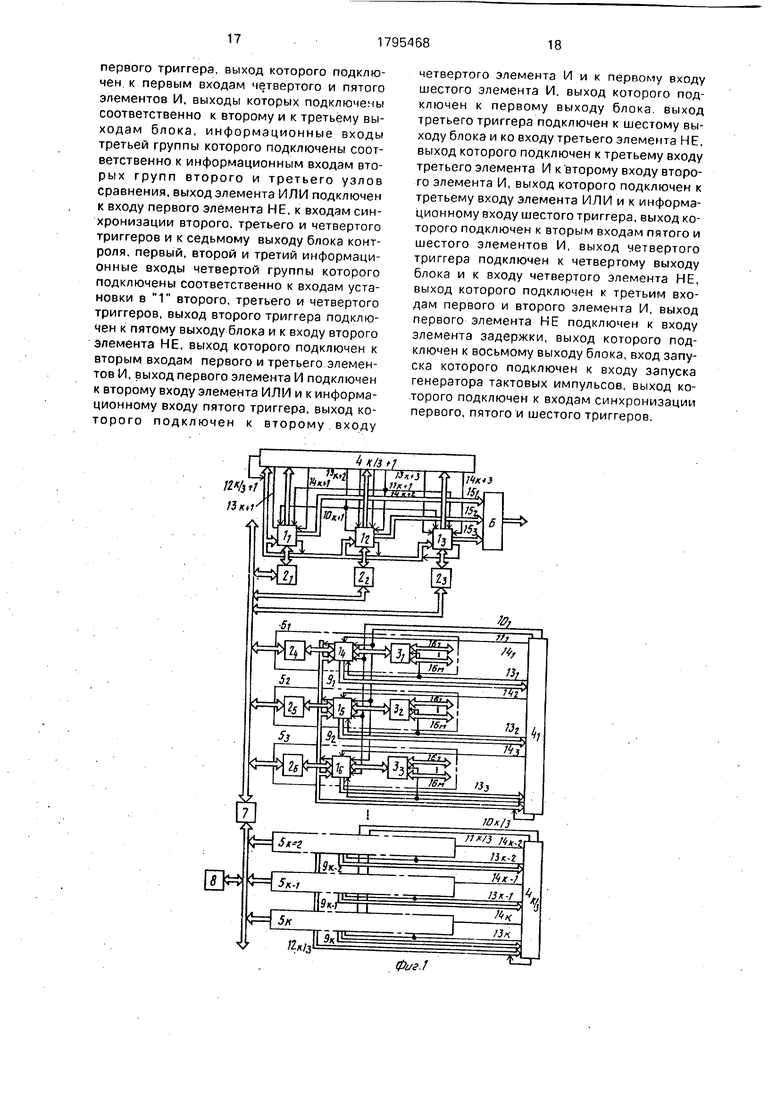

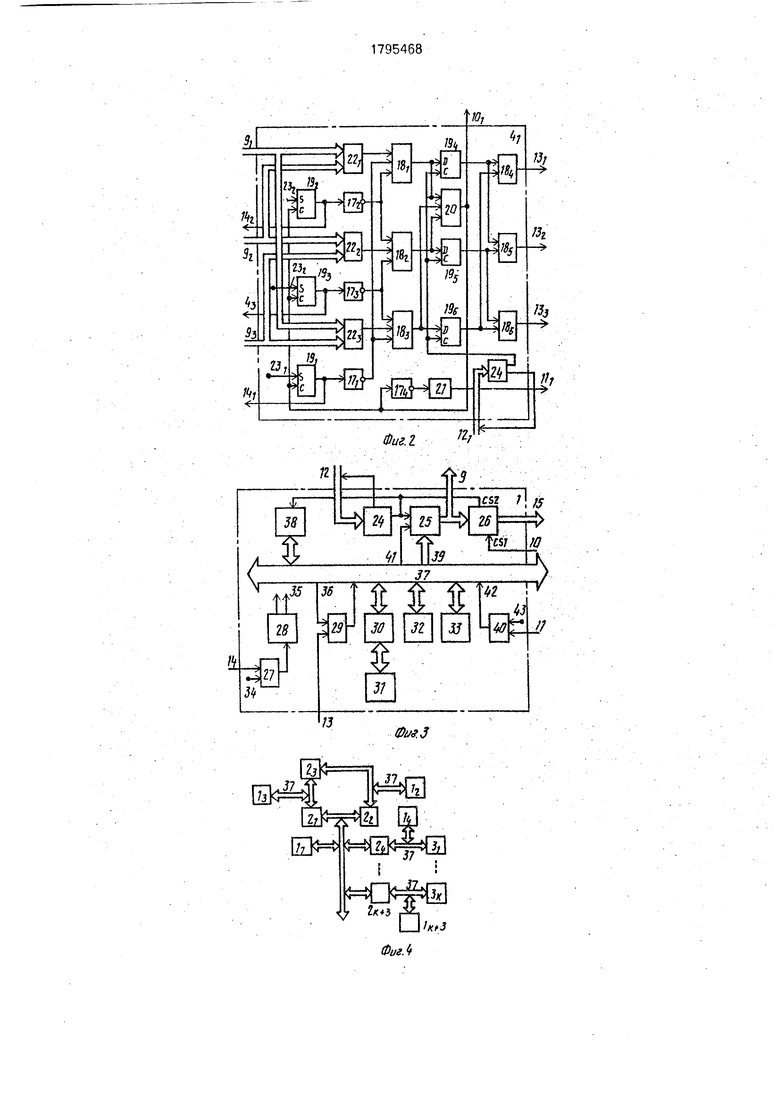

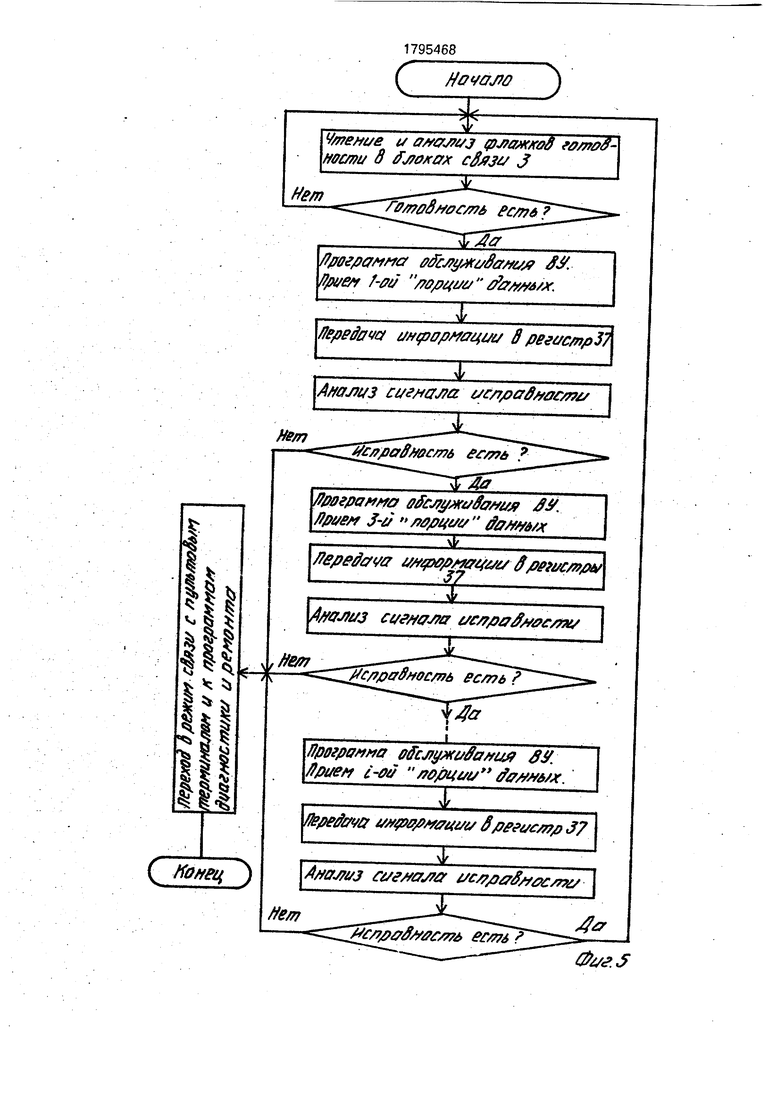

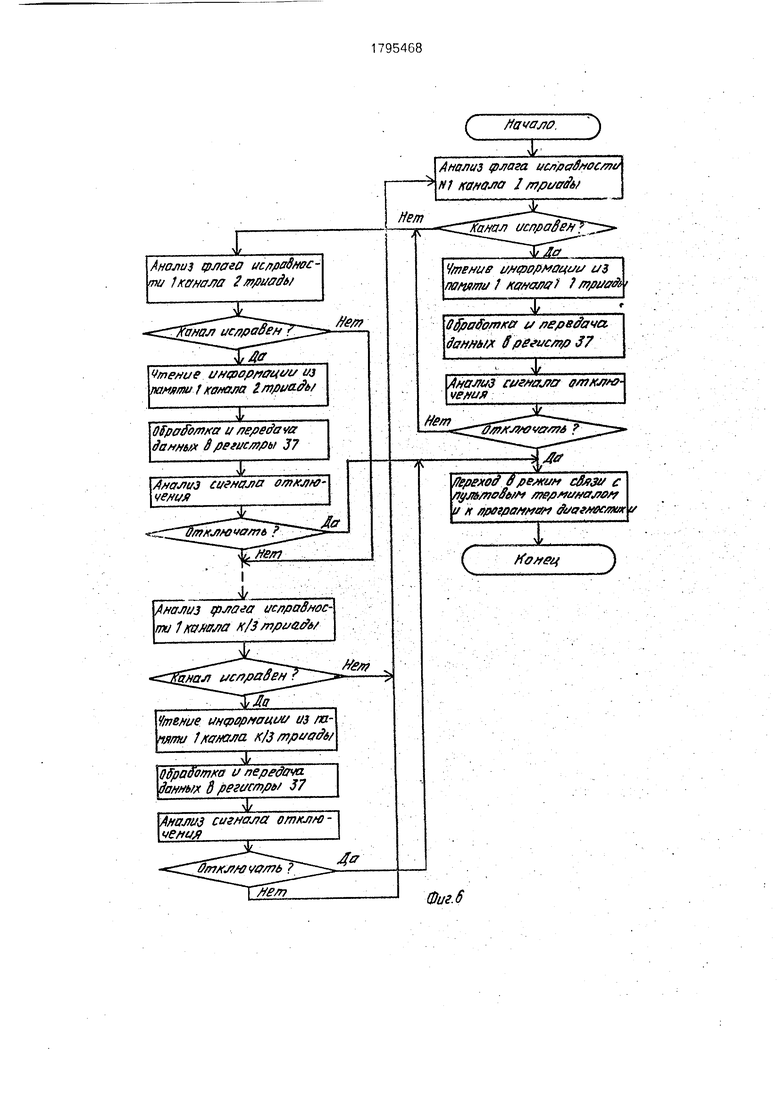

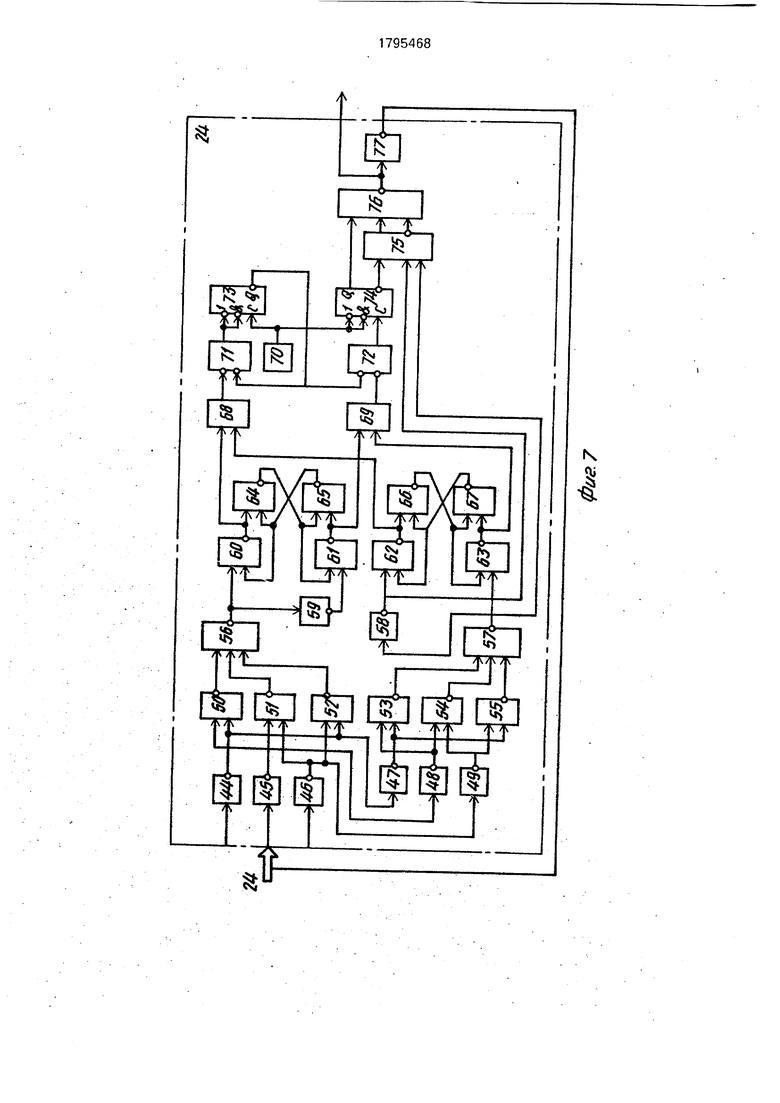

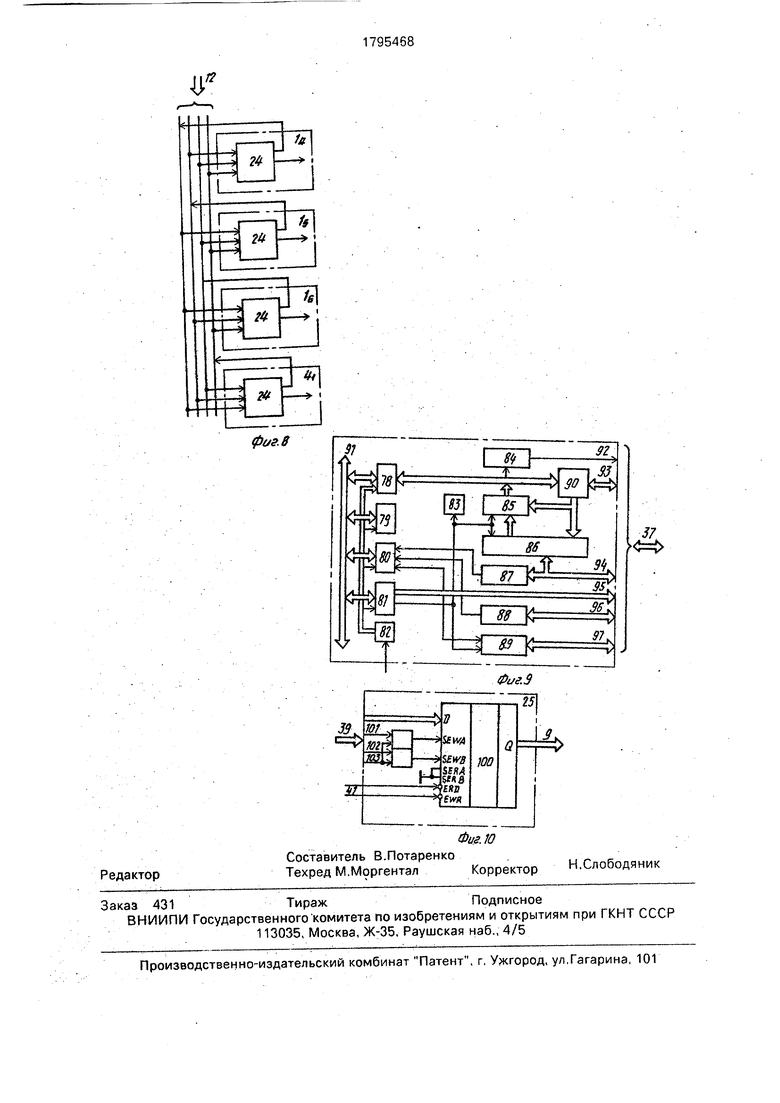

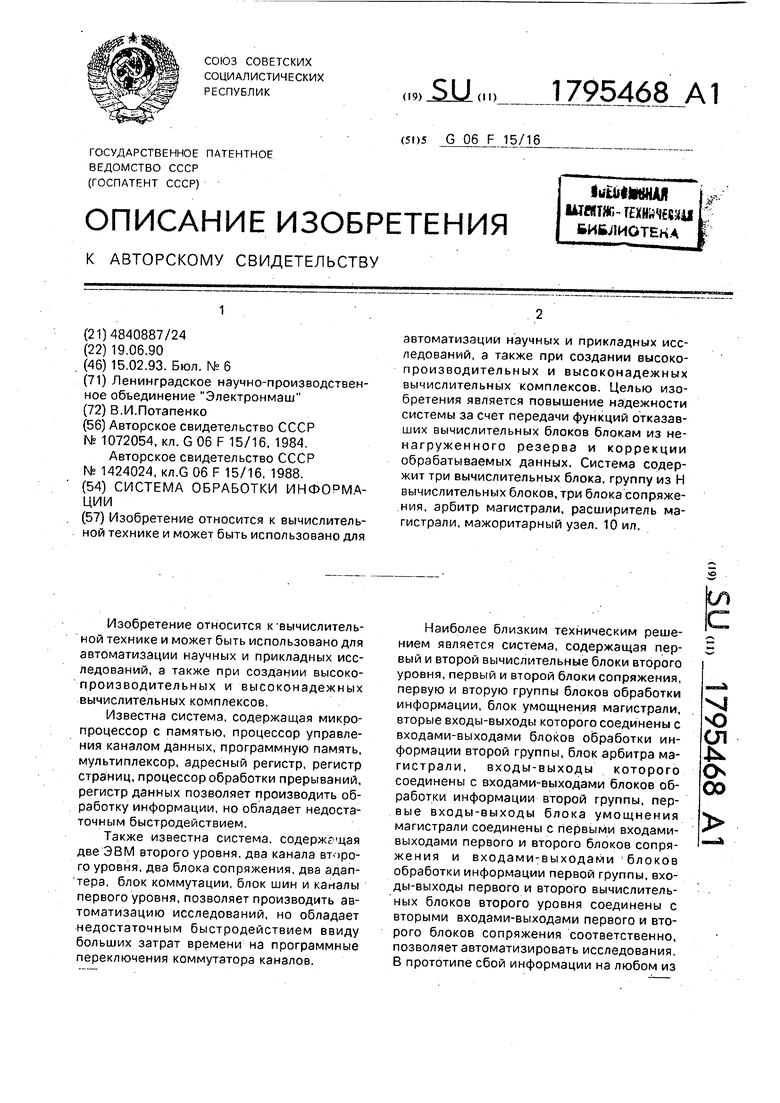

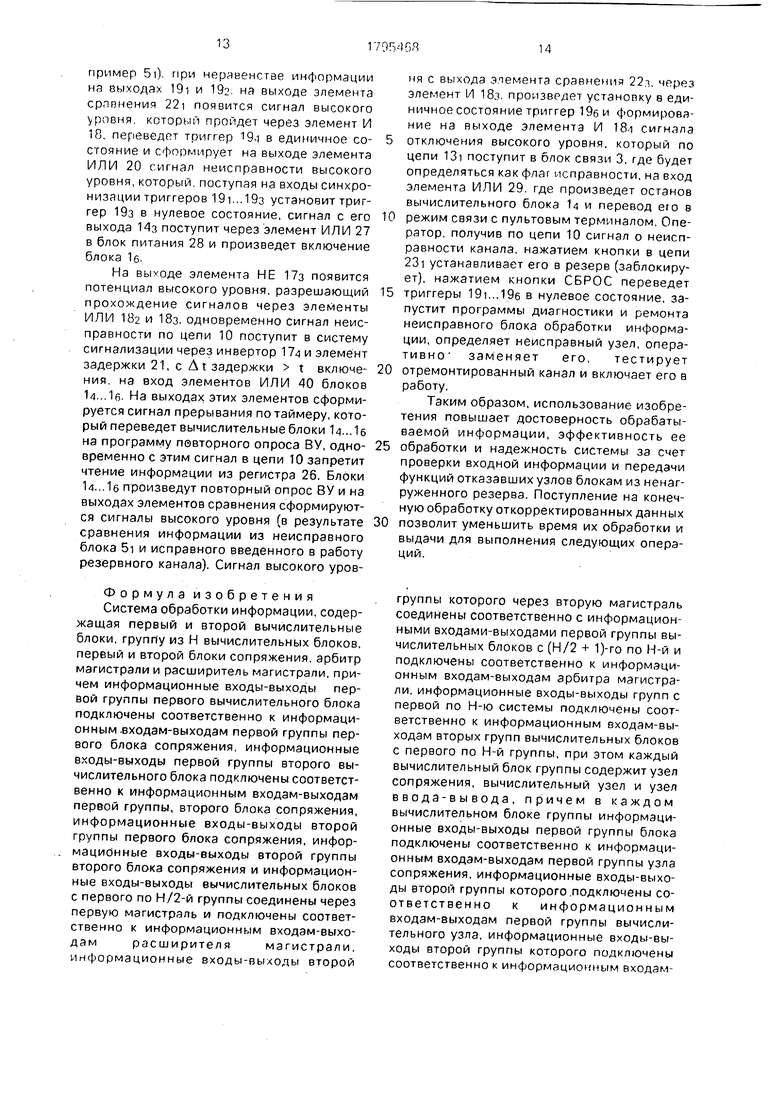

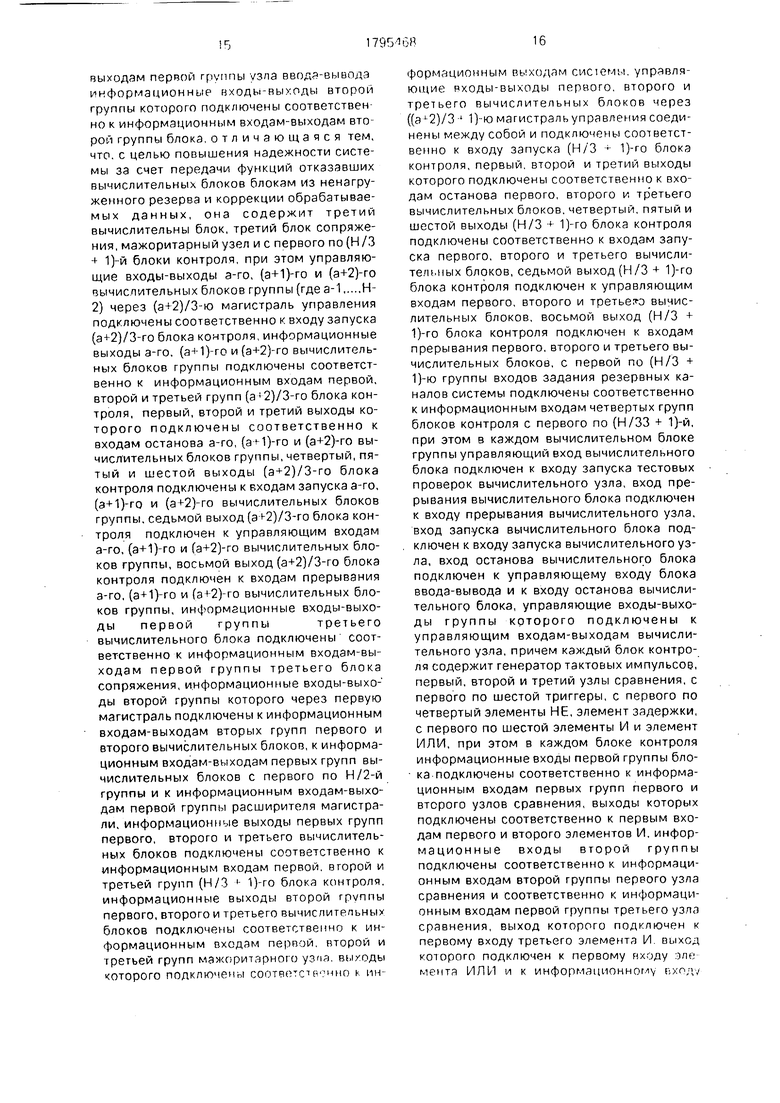

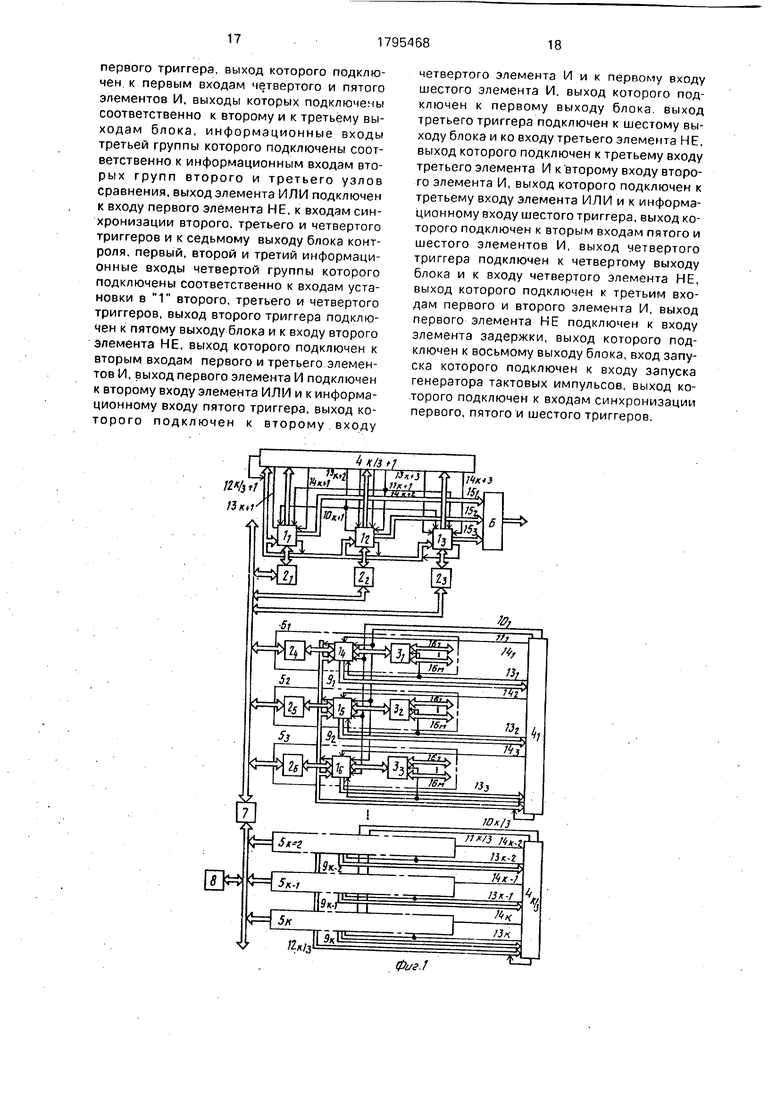

На фиг.1 приведена структурная схема предлагаемой системы; на фиг.2 - пример реализации блока контроля; на фиг.З.- пример реализации вычислительного блока; на фиг.4 - схема соединения вычислительных блоков с блоками сопряжения и узлами вер- да-вывода; на фиг.5 - алгоритм работы в.ы- числительного блока; на фиг.6 - алгоритм работы вычислительного узла; на фиг.7 - пример реализации генератора импульсов; на фиг.8 - пример схемы соединений гене- раторов импульсов; на фиг.9 - пример реализации процессора; на фиг.10 - пример реализации буферного регистра.

На фиг.1 позицией 1i, г, 1з обозначены вычислительные блоки, 14...1н-з- вычисли- тельные узлы; 2i, 2a, 2з- первый, второй и третий блоки сопряжения; 24...2н-з - сопряжения; Зч.-.Зн - узлы ввода-вывода; 41...4н/з-1 - блоки контроля; 5i,.,5iH - группа вычислительных блоков; б - мэжоритар- ный узел; 7 - расширитель магистрали; 8 - арбитр магистрали; 9 - первая шина контроля информации; 10 - линия сигнала неисправности в триаде блоков обработки информации; 11 - линия сигнала прерыва- имя программы; 12 - шина синхронизации; 13 - линия сигнала отключения неисправного вычислительного блока; 14 - линия сигнала включения резервного вычислительного блока; 15 - вторая шина контроля информа- ции; 16i...16w - группа информационных входов-выходов системы.

На фиг,2 позицией 17i... обозначены элементы НЕ; 18i...l8e - элементы И; 19i..,l9e триггеры; 20-элементы ИЛИ; 21 - элемент задержки; 221....22з- первый... третий узлы сравнения; 23 - линия сигнала от кнопки выбора резервного вычислительного блока; 24 - генератор тактовых импульсов.

На фиг.З позицией 25 обозначен первый регистр данных (например 585ИР12); 26 - второй; 27 - первый элемент ИЛИ; 28 - источник питания; 29 - передатчик (например 559ИП1); 30 - устройство управления вводом-выводом; 31 -устройство ввода-вывода; 32 - постоянное запоминающее устройство (ПЗУ); 33 - оперативное Запоминающее устройство (ОЗУ); 34 - линия сигнала от клавиши включения постоянного напряжения; 35 - линия сигналов питания; 36 - линия сигнала ОСТАНОВ ; 37 - магистраль ОБЩАЯ 38 - процессор; 39

- шина сигналов АДРЕС/ДАННЫЕ, СНА; 40

- второй элемент ИЛИ; 41 - линия сигнала ВЫВОД ; 42-линия сигнала 43 - иния сигнала от клавиши ТАЙМЕР.

На фиг.7 позицией 44...49 обозначены инверторы; 50...57 -элементы И-НЕ; 58, 59

-элементы НЕ; 60...67-элементы И-НЕ;68, 69 - элементы И; 70 - генератор импульсов; 71, 72 - элементы ИЛИ; 73, 74 - ждущие мультивибраторы (например 155АП); 75, 76

мажоритарные элементы; 77 - передатчик например 559ИП1);

На фйг.9 позицией 78 обозначен узел АЛУ; 79-узел микропрограммного запоминающего устройства; 80 - узел управления; 81 - дешифратор спецсигналов; 82 - формирователь тактовых последовательностей 01...04 (например рис. 5,78 в 3); 83 - узел внутреннего ввода; 84-дешифратор ВУ; 85 - мультиплексор канала; 86- резидентная память; 87 - узел управления каналом; 88 - зел управления прерыванием; 89 - узел предоставления канала; 90 - приемо-пёре- датчики канала; .91- магистраль микроканала; 92 - линия сигнала ВУ; 93 - шина ДА00...15; 94 - шина сигналов СИА, БАЙТ, ВВОД, ВЫВОД, СИП; 95 РГН, СБРОС, РАБОТА; , ПОСТ, ОСТ. ПРТ, ТПР, ППР; 97:. ТПД, ПВ, ППД.

На фиг.10 позицией 98, 99 обозначены триггеры (цепи установки Р и S соединены с +5В через 1 ком), 100 - буферный регистр например 555ИР26); 101, 102 - линия сигнала адреса АО, А1; 103 - линия сигнала СИА.

Система (фиг,1) содержит три вычислительных блока 1i, 1з, 1з. три блока 2i, 2.2, 2з сопряжения, группу из вычислительных блоков 5, (Н/3-1) блоков 4 контроля, мажоритарный 6 узел, расширитель 7 магистрали, 8 арбитр магистрали, причем каждый блок 5i, где I 1...К, содержит блок сопряжения 2У, где у 4,..К, вычислительный блок 1У. узел Связи 3 и группу информационных 1б1..,16м входов-выходов системы, информационные входы-выходы системы соединены с входаи-выходами узла 3 связи, входы-выходы

которого соединены с первыми входами-выходами вычислительного 1у блока, вторые входы-выходы которого соединены с первыми входами-выходами блока 2У сопряжения, вторые входы-выходы которого являются входами-выходами блока 5, первые входы- выходы блока 2i сопряжения соединены с первыми входами-выходами блока сопряжения 22 и 2з, первые входы-выходы расширителя 7 магистрали соединены с первыми входами-выходами блоков сопряжения 21...2зи входами-выходами вычислительных блоков 51...5з, вторые входы-выходы расширителя 7 магистрали соединены с входами- выходами 8 арбитра магистрали и входами-выходами блоков 5к-2.-5к, входы- выходы вычислительных блоков 11, 12, 1з соединены со вторыми входами-выходами блоков сопряжения 2i, 22, 2з соответственно, группы входов 9 каждого блока 4 контроля соединены с соответствующей группой выходов вычислительного узла 1 каждого из трех блоков 5, первый и второй вход вычислительного узла 1, каждого из трех блоков 5 соединены соответственно с первым 14к-2 и вторым 13к-2, третьим 14к-1 и четвертым 13к-1. пятым 14к и шестым 13к выходами каждого блока 4 контроля, седьмой выход 11 которого соединен с третьими входами вычислительных узлов 1, каждого из трех блоков 5, четвертые входы которых соединены с восьмым 10 выходом 4 блока контроля, вторые 13 входы узлов 1 соединены с 16м+2-ми входами узла 3 связи каждого из трех блоков 5, первые группы выходов 9к+1 первого ft, 9K+2jBToporo 12 и 9к+з, третьего 1з вычислительных узлов соединены соответственно с первой,второй и третьей группой входов, группой входов 4 блока контроля, первый 14к-м и второй 13к+1, третий 14к+2 и четвертый 13к+2, пятый 14к+з и шестой 13к+з выходы которого соединены соответственно с первыми и вторыми входами первого 1i, второго 12 и третьего 1з вычислительных узлов, третьи входы которых соединены с седьмым 11к+1 входом 4 блока контроля, восьмой 10к+1 выход которого соединен с четвёртыми входами вычислительных узлов 11,12 и 1з, вторые группы выходов которых соединены с группами входов 15i, 152 и 15з мажоритарного 6 узла, группа выходов которого является информационной группой выходов системы, четвертая группа входов 12 каждого 4 блока контроля соединена с его девятым выходом и с соответствующей группой входов и выходов вычислительного узла 1 каждого из трех блоков 5н-2...5н, четвертая группа входов 12н/з+1 4-го блока контроля соединена с его девятым выходом и с соответствующей

группой входов и выходов первого 11, второго 12 и третьего 1з вычислительных узлов. В системе блок сопряжения 2 реализован на базе устройства для сопряжения двух вы- числительных блоков 2 и входящего в него блока 37, Узел ввода-вывода 3 реализован на базе блока связи 7. Мажоритарный узел может быть реализован на базе любых мэ- жоржитарных элементов.

0 Каждая триада вычислительных блоков подключена к одной группе 16ь..16м внешних источников информации. Входы 23i 332 и 23з блоков контроля 4 подключены к кнопкам установки резерва. Выходы 10 блоков 4

5 соединяют с сигнализацией о неисправности. Один из блоков 5 каждой триады устанавливается в холодный резерв (путем подачи сигнала от кнопки установки резерва). Рабочие блоки каждой триады 5i - 5з ...

0 5н-2 5к производят сбор и обработку информации по одинаковым программам, хра- нящимся в вычислительных узлах 1 (алгоритм программы приведен на фиг.5). Каждая триада блоков обработки информа5 ции имеет свою обслуживающую программу flj. В каждом блоке 5 обработки информации данные от одних и тех же внешних устройств 1б1...1бм (общее количество ВУ системы определяется величиной М х К/3)

0 поступают в узел ввода-вывода 3, в которых формируются М - программно доступных флажков готовности и флаг исправности. Узлы 1 производят чтение флажков готовности. Обнаружив (по активному флажку) ВУ,

5 готовое к обмену, узел 1 переходит на программу обслуживания этого ВУ. В соответствии с этой программой узел 1 осуществляет ввод порции информации из ВУ и вывод управляющих сигналов и

0 вывод управляющих сигналов в ВУ через узел 3. Ввод информации в узлы 1 из ВУ триад производится синхронно по программным меткам от ЭВМ, привязанным к тактовым импульсам шины 12, причем период

5 меток синхронизации должен быть меньше периода изменения выходных сигналов. Поступая из ВУ триад информация хранится в одинаковой области памяти узлов 1 по одинаковым адресам ячеек с целью упрощения

0 программ хранения, обработки и контроля.

После записи в память первой порции

информации два блока триады переходят

на программу, последовательной выборки,

по какому-либо периодическому закону, ин5 формации из некоторых одноименных ячеек и пересылки ее в регистр 25. Запись информации в регистр 25 происходит по сигналам ВЫВОД 41, поступающим из магистрали 37, чтение регистра 25 и перезапись информации из него в регистр 26 происходит по

сигналам от генератора 24. На фиг.9 и 10 показаны адресный селектор буферного регистра и схема формирования управляющих сигналов СИА, ВЫВОД, СИП в процессоре. В исходном состоянии выходы регистров 25 и 26 находятся в высокоимпедансном (одинаковом) состоянии и после операции записи на выходах 9 появится информация из одноименных ячеек памяти. Далее эта информация поступает в блок контроля 4, который, при обнаружении неисправности, отключит неисправный вычислительный узел 1 в блоке 5 и подключит резервный вычислительный блок. При этом блок 4 переведет по сигналу 11 прерывания исправные узлы 1 триады на программу повторного опроса ВУ (внешние устройства должны хранить порции информации до момента появления сигналов повторного опроса). Затем вычислительные узлы 1 произведут анализ наличия сигнала отключения и при отсутствии его (каналы 5 исправны) перейдут к сбору следующей порции информации. Закончив сбор информации, вычислительные узлы 1 приступят к ее обработке с пересылкой результата в одноименные ячейки области памяти, предназначенной для обмена результатами вычислений с устройствами следующей ступени.

Вычислительные блоки 11...1з (один из них находится в резерве) производят по одинаковым программам поочередной опрос (через блоки сопряжения 21...2з, 2У), чтение и анализ флажков 13 неисправности в узлах 3. Блоки 11...1з, по результатам анализа, исключают из обращения (программно) неисправные блоки 5 и производят пересылку результатов обработки из памяти узлов 1 в свою память. Исключение из программного обращения неисправных блоков 5 позволяет при дальнейшей обработке (сортировке и т.д.) работать вычисли- тельным блокам 1ч...1з только с откорректированной информацией, что дает возможность исключить дополнительные операции контроля, анализа, сравнения и т,д, получаемых результатов обработки и позволяет снизить затраты времени на общие программные операции. После сбора результатов первичной обработки вычислительные блоки 11.,.1з производят сортировку и окончательную обработку(проведение арифметических операций, редактирование, составление таблиц и т.д.) информации. При этом вычислительные блоки 1i...l3 в определенные моменты времени, определяемые программами, формируют контрольные сообщения, которые пересылаются в регистры 25.

Перезапись информации в регистр 26 производится тактовым импульсом одновременно с чтением регистра 25. При отсутствии сигнала неисправности на линиях 10

информация с выходов регистров 26 поступает в мажоритарный узел, который формирует на информационном выходе код сообщения по методу голосования два из трех. Поочередное подключение блоков

0 11...1з к исправным каналам каждой триады, для их обслуживания в соответствии с алгоритмом (фиг.6), осуществляется блоком 8 арбитра магистрали с одновременным разрешением конфликтных ситуаций, воз5 никающих между блоками сопряжения 21...2з, 24...2к+4 при их одновременной попытке захвата магистрали. Расширитель магистрали обеспечивает восстановление временных соотношений сигналов в магист0 рали.

Описание работы и структурные схемы блока сопряжения 2, блока ввода-вывода 3, расширителя 7 и арбитра магистрали 8 приведены в а.с. 1424024 (фиг.2...9).

5 Работа блока контроля одной из триад, например 4i (фиг.2) происходит следующим образом.

После включения питания оператор формирует сигналы СБРОС (например от

0 кнопки), поступающие на входы установки в ноль триггеров 19i...19e блока 4 (для упрощения рисунка сигналы СБРОС на фиг.2 не показаны). Информационные входы триггеров 19-|...19з соединены цепью ОБЩ. Вхо5 ды установки в единицу триггеров 194...19е установлены в нулевое состояние.

Перед началом работы оператор выбирает резервные каналы и нажатием кнопки выбора резервного канала подает на один

0 из входов 231...23з сигнал низкого уровня (например, на вход 23з, т.е. в триадах резервные каналы третьи - 5з, 5е...5к). Триггер 19з устанавливается в единичное состояние и на выходе элемента НЕ 17з появляется сиг5 нал низкого уровня, запрещающий прохождение сигналов через элементы И 182 и 18з. В триаде работают вычислительные блоки 14 и 1б, информация с выходов 9i и 9а поступает на входы элементов сравнения

0 221...22з. При равенстве информации (канал исправен) на выходе элеметов сравнения имеется потенциал низкого уровня, поступающий на выходы элементов И 18i...183. Появление сигнала высокого уровня на вы5 ходе элементов сравнения 22а и 22з (неравенство входной информации, т.к. блок 1ене работает) не изменит состояния элементов И 182 и 18з за счет наличия низкого уровня на выходе элемента НЕ 17з. При появлении неисправноти в вычислительном блоке (например 5i). при неравенстве информации на выходах 19i и 192. на выходе элемента срлвнения 22i появится сигнал высокого уровня, который пройдет через элемент И 18, переведет триггер 19.1 в единичное состояние и сформирует на выходе элемента ИЛИ 20 сигнал неисправности высокого уровня, который, поступая на входы синхронизации триггеров 191...19з установит триггер 19з е нулевое состояние, сигнал с его выхода 14з поступит через элемент ИЛИ 27 в блок питания 28 и произведет включение блока 1б.

На выходе элемента НЕ 17з появится потенциал высокого уровня, разрешающий прохождение сигналов через элементы ИЛИ 182 и 18з, одновременно сигнал неисправности по цепи 10 поступит в систему сигнализации через инвертор 17 и элемент задержки 21, с At задержки t включения, на вход элементов ИЛИ 40 блоков 14...1б. На выходах этих элементов сформируется сигнал прерывания по таймеру, который переведет вычислительные блоки 14...1е на программу повторного опроса ВУ, одновременно с этим сигнал в цепи 10 запретит чтение информации из регистра 26. Блоки Ь...1б произведут повторный опрос ВУ и на выходах элементов сравнения сформируются сигналы высокого уровня (в результате сравнения информации из неисправного блока 5i и исправного введенного в работу резервного канала). Сигнал высокого уровФормула изобретения Система обработки информации, содержащая первый и второй вычислительные блоки, группу из Н вычислительных блоков, первый и второй блоки сопряжения, арбитр магистрали и расширитель магистрали, причем информационные входы-выходы первой группы первого вычислительного блока подключены соответственно к информационным .входам-выходам первой группы первого блока сопряжения, информационные входы-выходы первой группы второго вычислительного блока подключены соответственно к информационным входам-выходам первой группы, второго блока сопряжения, информационные входы-выходы второй группы первого блока сопряжения, информационные входы-выходы второй группы второго блока сопряжения и информационные входы-выходы вычислительных блоков с первого по Н/2-й группы соединены через первую магистраль и подключены соответственно к информационным входам-выходамрасширителя магистрали, информационные входы-выходы второй

ня с выхода элемента сравнения 22л, через элемент И 18з. произведет установку в единичное состояние триггер 19еи формирование на выходе элемента И 18-1 сигнала

отключения высокого уровня, который по цепи 13i поступит в блок связи 3, где будет определяться как флаг исправности, на вход элемента ИЛИ 29. где произведет останов вычислительного блока 14 и перевод его в

режим связи с пультовым терминалом. Оператор, получив по цепи 10 сигнал о неисправности канала, нажатием кнопки в цепи 23i устанавливает его в резерв (заблокирует), нажатием кнопки СБРОС переведет

триггеры 19i...19e в нулевое состояние, запустит программы диагностики и ремонта неисправного блока обработки информации, определяет неисправный узел, оперативно заменяет его, тестирует

отремонтированный канал и включает его в работу.

Таким образом, использование изобретения повышает достоверность обрабатываемой информации, эффективность ее

обработки и надежность системы за счет проверки входной информации и передачи функций отказавших узлов блокам из ненагруженного резерва. Поступление на конечную обработку откорректированных данных

позволит уменьшить время их обработки и выдачи для выполнения следующих операций.

группы которого через вторую магистраль соединены соответственно с информационными входами-выходами первой группы вычислительных блоков с (Н/2 + 1)-го по Н-й и подключены соответственно к информационным входам-выходам арбитра магистрали, информационные входы-выходы групп с первой по Н-ю системы подключены соответственно к информационным входам-выходам вторых групп вычислительных блоков с первого по Н-й группы, при этом каждый вычислительный блок группы содержит узел сопряжения, вычислительный узел и узел ввода-вывода, причем в каждом вычислительном блоке группы информационные входы-выходы первой группы блока подключены соответственно к информационным входам-выходам первой группы узла сопряжения, информационные входы-выходы второй группы которого .подключены соответственно к информационным входам-выходам первой группы вычислительного узла, информационные входы-выходы второй группы которого подключены соответственно к информационным входамвыходам первой группы узла ввода-вывода информационные входы-выходы второй группы которого подключены соответственно к информационным входам-выходам второй группы блока, отличающаяся тем, что. с целью повышения надежности системы за счет передачи функций отказавших вычислительных блоков блокам из ненагруженного резерва и коррекции обрабатываемых данных, она содержит третий вычислительны блок, третий блок сопряжения, мажоритарный узел и с первого по(Н/3 + 1)-й блоки контроля, при этом управляющие входы-выходы а-го, (а+1)-го и (а+2)-го вычислительных блоков группы (где а-1 ,....Н- 2) через (а+2)/3-ю магистраль управления подключены соответственно к входу запуска (а+2)/3-го блока контроля, информационные выходы а-го. (а-Н)-го и(а+2)-го вычислительных блоков группы подключены соответственно к информационным входам первой, второй и третьей групп (а 2)/3-го блока контроля, первый, второй и третий выходы которого подключены соответственно к входам останова а-го, (аИ)-го и (а+2)-го вычислительных блоков группы, четвертый,пятый и шестой выходы (а+2)/3-го блока контроля подключены к входам запуска а-го, (а+1)-го и (а+2)-го вычислительных блоков группы, седьмой выход (э+2)/3-го блока контроля подключен к управляющим входам а-го, (а+1)-го и (а+2)-го вычислительных блоков группы, восьмой выход (а+2)/3-го блока контроля подключен к входам прерывания а-го, (а+1)-го и (а+2)-го вычислительных блоков группы, информационные входы-выходы первой группытретьего вычислительного блока подключены соответственно к информационным входам-выходам первой группы третьего блока сопряжения, информационные входы-выхо- ды второй группы которого через первую магистраль подключены к информационным входам-выходам вторых групп первого и второго вычислительных блоков, к информационным входам-выходам первых групп вычислительных блоков с первого по Н/2-й группы и к информационным входам-выходам первой группы расширителя магистрали, информационные выходы первых групп первого, второго и третьего вычислительных блоков подключены соответственно к информационным входам первой, второй и третьей групп (Н/3 1)-го блока контроля, информационные выходы второй группы первого, второго и третьего вычислительных блоков подключены соответственно к информационным входам первой, второй и третьей групп мажоритарного узпа. выходы которого подключены соответственно к информационным выходам . управляющие входы-выходы первого, второго и третьего вычислительных блоков через ((a L2)/3 д 1)-ю магистраль управления соединены между собой и подключены соответственно к входу запуска (Н/3 - 1)-го блока контроля, первый, второй и третий выходы которого подключены соответственно к входам останова первого, второго и третьего вычислительных блоков, четвертый, пятый и шестой выходы (Н/3 + 1)-го блока контроля подключены соответственно к входам запуска первого, второго и третьего вычислительных блоков, седьмой выход (Н/3 + 1)-го блока контроля подключен к управляющим входам первого, второго и третьего вычислительных блоков, восьмой выход (Н/3 + 1)-го блока контроля подключен к входам прерывания первого, второго и третьего вычислительных блоков, с первой по (Н/3 + 1)-ю группы входов задания резервных каналов системы подключены соответственно к информационным входам четвертых групп блоков контроля с первого по (Н/33 + 1)-й, при этом в каждом вычислительном блоке группы управляющий вход вычислительного блока подключен к входу запуска тестовых проверок вычислительного узла, вход прерывания вычислительного блока подключен к входу прерывания вычислительного узла, вход запуска вычислительного блока подключей к входу запуска вычислительного узла, вход останова вычислительного блока подключен к управляющему входу блока ввода-вывода и к входу останова вычислительного блока, управляющие входы-выходы группы которого подключены к управляющим входам-выходам вычислительного узла, причем каждый блок контроля содержит генератор тактовых импульсов, первый, второй и третий узлы сравнения, с первого по шестой триггеры, с первого по четвертый элементы НЕ, элемент задержки, с первого по шестой элементы И и элемент ИЛИ, при этом в каждом блоке контроля информационные входы первой группы блока подключены соответственно к информационным входам первых групп первого и второго узлов сравнения, выходы которых подключены соответственно к первым входам первого и второго элементов 1/1, информационные входы второй группы подключены соответственно к информационным входам второй группы первого узла сравнения и соответственно к информационным входам первой группы третьего узла сравнения, выход которого подключен к первому входу третьего элемента И. выход которого подключен к первому входу элемента ИЛИ и к информационному вход/

первого триггера, выход которого подключен, к первым входам четвертого и пятого элементов И, выходы которых подключены соответственно к второму и к третьему выходам блока, информационные входы третьей группы которого подключены соответственно к информационным входам вторых групп второго и третьего узлов сравнения, выход элемента ИЛИ подключен к входу первого элемента НЕ. к входам синхронизации второго, третьего и четвертого триггеров и к седьмому выходу блока контроля, первый, второй и третий информационные входы четвертой группы которого подключены соответственно к входам установки в 1 второго, третьего и четвертого триггеров, выход второго триггера подключен к пятому выходу блока и к входу второго элемента НЕ, выход которого подключен к вторым входам первого и третьего элементов И, выход первого элемента И подключен к второму входу элемента ИЛИ и к информационному входу пятого триггера, выход которого подключен к второму . входу

четвертого элемента И и к первому входу шестого элемента И, выход которого подключен к первому выходу блока, выход третьего триггера подключен к шестому выходу блока и ко входу третьего элемента НЕ, выход которого подключен к третьему входу третьего элемента И к второму входу второго элемента И, выход которого подключен к третьему входу элемента ИЛИ и к информационному входу шестого триггера, выход которого подключен к вторым входам пятого и шестого элементов И, выход четвертого триггера подключен к четвертому выходу блока и к входу четвертого элемента НЕ, выход которого подключен к третьим входам первого и второго элемента И, выход первого элемента НЕ подключен к входу элемента задержки, выход которого подключен к восьмому выходу блока, вход запуска которого подключен к входу запуска генератора тактовых импульсов, выход которого подключен к входам синхронизации первого, пятого и шестого триггеров.

f J

| название | год | авторы | номер документа |

|---|---|---|---|

| Многомашинная вычислительная система | 1990 |

|

SU1798798A1 |

| Микроэлектронная вычислительная машина | 1979 |

|

SU1061606A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1529243A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| Вычислительная система | 1989 |

|

SU1633417A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1990 |

|

SU1783531A1 |

Изобретение относится к вычислительной технике и может быть использовано для автоматизации научных и прикладных исследований, а также при создании высокопроизводительных и высоконадежных вычислительных комплексов. Целью изобретения является повышение надежности системы за счет передачи функций отказавших вычислительных блоков блокам из ненагруженного резерва и коррекции обрабатываемых данных. Система содержит три вычислительных блока, группу из Н вычислительных блоков, три блока сопряжения, арбитр магистрали, расширитель магистрали, мажоритарный узел. 10 ил.

Чтение ts флажюв ютяо- мслш 8 faoxax cfaw J

fo/n

Программа айлужг/Вя/я// №. ff/w&f f-fft/ яорцш 0b#/&/x.

fffpefava Ј/мер0рмацш 8 petvc&ptf

Анализ ct/wasra t/c/7/ afa0&r &

Hem

ffpoepavMo fffcj%pxt/Jh ftu9 №. flpve 3-t/ я00цм 0ff#w/x

JJL

-)

/tepefavff и/яр0рмуцЈ/Ј/ 00ew/00v

T

AffWi/j cvMffjra t/tstpafafff/Tx/

.Нем

j/c/ 0a&Hoc/n6 ес/пь 4&

Программа 0$мужи0а#ия #У. ffpt/ен i-ffi/ /юрщм tfffjpwx.

Ifepetfffva юфержгшм fip&t/csvp 37

( Конец )

d#ffJ7#j &/e#as7& isc/r/jafoee/nz/

/ 0/ffff3#0C/ff&

Я0

teff/)Crff№Cff 6 Л777

JJL

j/c/ 0a&Hoc/n6 ес/пь 4&

Анализ флага it смрадности 1 канала 2 мриады

ч/пение UHtpopftffyt/t/ из памяти f канала 2mpt/eu t /

Анализ флага исправности 1 камла к/3 mptsutfu/

Holfj млраЗен Jtii

№я

Чтение инф0рмаш& из т- пяти 1 канала K/3mflt/afa/

О&раоотка и передача данных ft регистры J7

С

Начале,

D

-

1:

- . - U- - ---J-r---I- .-. L--T1I UUU--

Анализ флага u&ipafaoc/nt/ N1 канала 2 mpvafa

jtawui vcnpaJetT

-

Ч/newff и#1р0р&аць и аз fXf/tfffftt/ / канала} трмай

Анализ мгмаукг- ve/fuj

ss

J

§.

Фиг.З 25

| Мультипроцессорный крейтконтроллер | 1980 |

|

SU1072054A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

Авторы

Даты

1993-02-15—Публикация

1990-06-19—Подача