Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации и выделения данных | 1989 |

|

SU1675943A1 |

| Устройство фазовой синхронизации для дискового накопителя цифровых данных | 1988 |

|

SU1615799A1 |

| Частотно-фазовый компаратор | 1981 |

|

SU983978A1 |

| Генератор синхросигналов | 1977 |

|

SU744719A1 |

| Широтно-импульсный регулятор для управления вентильным преобразователем | 1983 |

|

SU1181074A1 |

| Устройство для измерения артериального давления крови | 1985 |

|

SU1426537A1 |

| Устройство для программного управления | 1986 |

|

SU1397880A1 |

| УСТРОЙСТВО РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО, ФАЗОМАНИПУЛИРОВАННОГО И ПРОСТОГО СИГНАЛОВ | 1983 |

|

SU1840993A1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

Изобретение относится к технике измерения частот и фаз импульсных сигналов и может быть использовано в системах синхронизации двоичной информации, воспроизводимой с носителя магнитной записи. Цель изобретения - повышение точности фазового сравнения за счет уменьшения зоны нечувствительности. Частотно-фазовый компаратор содержит первый и второй триггеры 1 и 2, элемент3 совпадения, выполненный с использованием элемента И-НЕ, первый выход 4 частотно-фазового компаратора, одновибратор 5, первый вход 6 устройства, третий триггер 7, элемент ИЛИ 8, инвертор 9, элемент И 10, второй выход 11 устройства, второй вход 12 устройства, шина 13 управляющего сигнала. Цель достигается за счет того, что при нулевой разности фаз, входных сигналов осуществляется формирование выходных импульсов равной длительности. 4 ил.

О 00 00

со

00

ю

Изобретение относится к технике измерения частот и фаз импульсных сигналов и может быть использовано в системах синхронизации двоичной информации, воспроизводимой с носителя магнитной записи.

Цель изобретения - повышение точности фазового сравнения за счет уменьшения зоны нечувствительности.

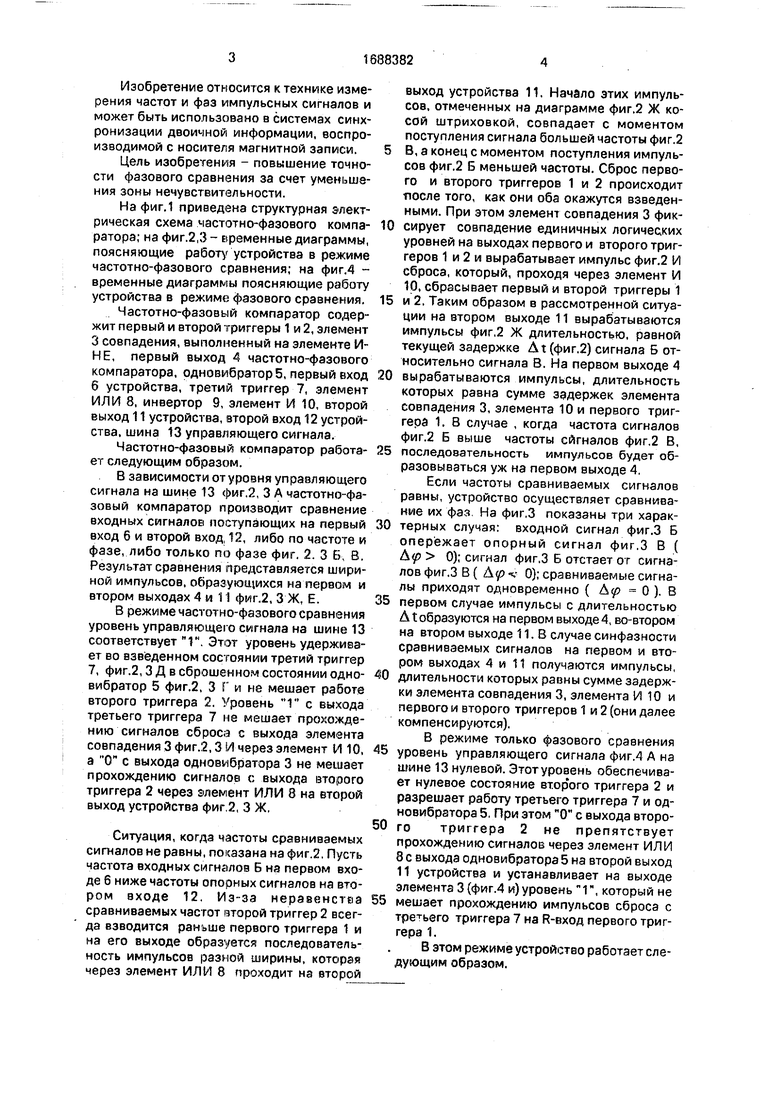

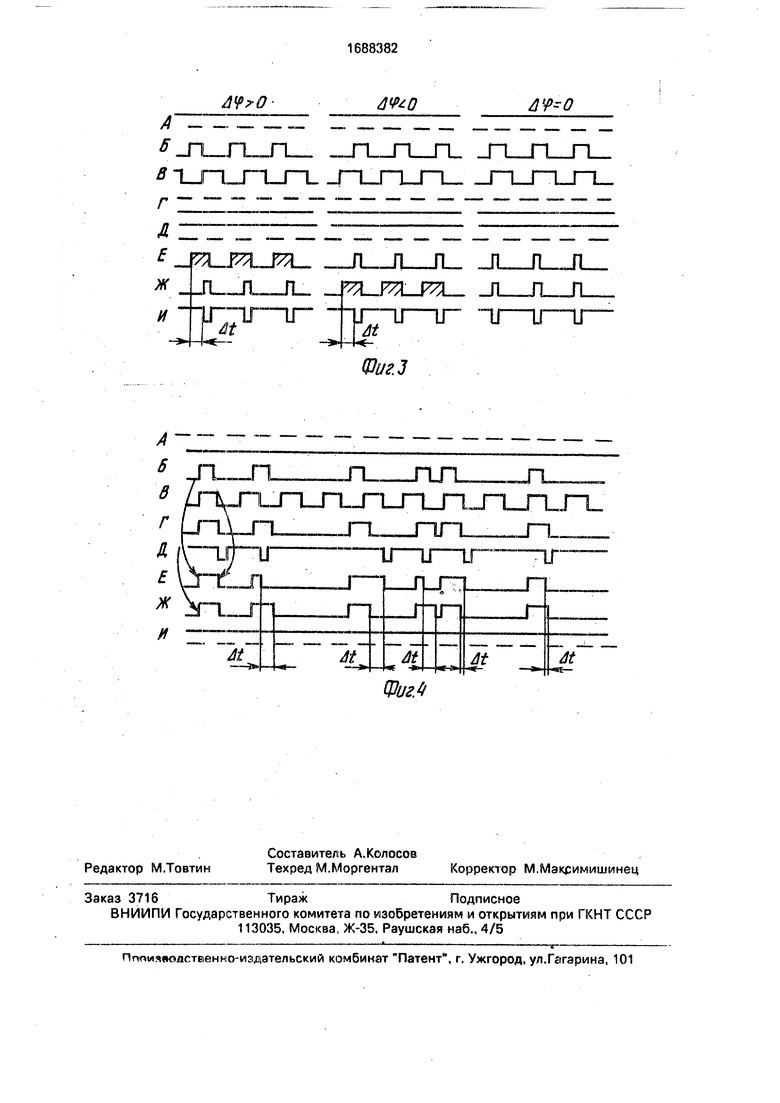

На фиг.1 приведена структурная электрическая схема частотно-фазового компаратора; на фиг.2,3 - временные диаграммы, поясняющие работу устройства в режиме частотно-фазового сравнения; на фиг.4 - временные диаграммы поясняющие работу устройства в режиме фазового сравнения.

Частотно-фазовый компаратор содержит первый и второй триггеры 1 и 2, элемент 3 совпадения, выполненный на элементе И- НЕ, первый выход 4 частотно-фазового компаратора, одновибратор 5, первый вход 6 устройства, третий триггер 7, элемент ИЛИ 8, инвертор 9, элемент И 10, второй выход 11 устройства, второй вход 12 устройства, шина 13 управляющего сигнала.

Частотно-фазовый компаратор работает следующим образом.

В зависимости от уровня управляющего сигнала на шине 13 фиг,2, 3 А частотно-фазовый компаратор производит сравнение входных сигналов поступающих на первый вход б и второй вход, 12, либо по частоте и фазе, либо только по фазе фиг. 2. 3 5, В. Результат сравнения представляется шириной импульсов, образующихся на первом и втором выходах 4 и 11 фиг,2, 3 Ж, Е.

В режиме частотно-фазового сравнения уровень управляющего сигнала на шине 13 соответствует Г. Этот уровень удерживает во взведенном состоянии третий триггер 7, фиг.2,3 Д в сброшенном состоянии одно- вибратор 5 фиг.2, 3 Г и не мешает работе второго триггера 2. Уровень Г с выхода третьего триггера 7 не мешает прохождению сигналов сброса с выхода элемента совпадения 3 фиг.2,3 И через элемент И 10, а О с выхода одновибратора 3 не мешает прохождению сигналов с выхода второго триггера 2 через элемент ИЛИ 8 на второй выход устройства фиг.2, 3 Ж.

Ситуация, когда частоты сравниваемых сигналов не равны, показана на фиг.2. Пусть частота входных сигналов Б на первом входе 6 ниже частоты опорных сигналов на втором входе 12. Из-за неравенства сравниваемых частот второй триггер 2 всегда взводится раньше первого триггера 1 и на его выходе образуется последовательность импульсов разной ширины, которая через элемент ИЛИ 8 проходит на второй

выход устройства 11, Начало этих импульсов, отмеченных на диаграмме фиг.2 Ж косой штриховкой, совпадает с моментом поступления сигнала большей частоты фиг.2

В, а конец с моментом поступления импульсов фиг,2 Б меньшей частоты. Сброс первого и второго триггеров 1 и 2 происходит после того, как они оба окажутся взведенными. При этом элемент совпадения 3 фиксирует совпадение единичных логических уровней на выходах первого и второго триггеров 1 и 2 и вырабатывает импульс фиг.2 И сброса, который, проходя через элемент И 10, сбрасывает первый и второй триггеры 1

и 2. Таким образом в рассмотренной ситуации на втором выходе 11 вырабатываются импульсы фиг.2 Ж длительностью, равной текущей задержке At (фиг.2) сигнала Б относительно сигнала В. На первом выходе 4

вырабатываются импульсы, длительность которых равна сумме задержек элемента совпадения 3, элемента 10 и первого триггера 1. В случае , когда частота сигналов фиг.2 Б выше частоты сигналов фиг.2 В,

последовательность импульсов будет образовываться уж на первом выходе 4.

Если частоты сравниваемых сигналов равны, устройство осуществляет сравнивание их фаз На фиг.З показаны три характерных случая: входной сигнал фиг.З Б опережает опорный сигнал фиг.З В ( Д 0); сигнал фиг.З Б отстает от сигналов фиг.З В ( 0); сравниваемые сигналы приходят одновременно ( Д 0 ). В

первом случае импульсы с длительностью Д t образуются на первом выходе 4, во-втором на втором выходе 11. В случае синфазности сравниваемых сигналов на первом и втором выходах 4 и 11 получаются импульсы,

длительности которых равны сумме задержки элемента совпадения 3, элемента И 10 и первого и второго триггеров 1 и 2 (они далее компенсируются).

В режиме только фазового сравнения

уровень управляющего сигнала фиг.4 А на шине 13 нулевой. Этотуровень обеспечивает нулевое состояние второго триггера 2 и разрешает работу третьего триггера 7 и одновибратора 5. При этом О с выхода второго триггера 2 не препятствует прохождению сигналов через элемент ИЛИ 8 с выхода одновибратора 5 на второй выход 11 устройства и устанавливает на выходе элемента 3(фиг.4 и) уровень 1, который не

мешает прохождению импульсов сброса с третьего триггера 7 на R-вход первого триггера 1.

В этом режиме устройство работает следующим образом.

На первый вход 6 устройства поступают импульсы фиг.4 Б информационного кода, расположенные на случайном расстоянии друг от друга, а на второй вход 12 опорный сигнал фиг.4 В. Каждый импульс фиг.4 Б взводит первый триггер 1 и запускает одно- вибратор 5, длительность импульса фиг.4 Г которого равна половине периода опорного сигнала. 1 с выхода первого триггера 1 разрешает сброс третьего триггера (фиг,4 д) который происходит в момент прихода среза импульса опорного сигнала. Это в свою очередь приводит к сбросу триггера 1, который приводит в исходное состояние третий триггер 7. Сигнал ошибки в предлагаемом устройстве, представляется в виде разности длительности двух импульсов фиг.4 Е и Ж, ширина первого из которых равна задержке между фронтом входного импульса и срезом импульса опорного сигнала.

По сравнению с прототипом в предлагаемом частотно-фазовом компараторе исключена зона нечувствительности, вызванная неопределенностью при одновременном срабатывании триггеров. Это преимущественно при сохранении достоинств прототипа позволяет использовать устройство в качестве датчика рассогласования системы фазовой синхронизации информации, воспроизводимой с магнитного носителя.

А б В

Г Л

IALJI

JftY77L Y77/ J777Z fy-Jbb-S77 if77

и U U U LJ U U U

фиг. Z

Формула изобретения

Частотно-фазовый компаратор, содержащий первый и второй триггеры, R-входы которых объединены, а выходы подключены к входам элемента совпадения, одновибра- тор. вход запуска которого является первым входом компаратора, и третий триггер, о т- личающийся тем, что, с целью повышения точности фазового сравнения за счет уменьшения зоны нечувствительности, в него введены элемент ИЛИ, инвертор и элемент И, причем первый и второй входы элемента ИЛИ соединены с выходами второго триггера и одновибратора соответственно, С - вход второго триггера является вторым входом компаратора и через инвертор соединен с С-входом третьего триггера, выходы третьего триггера и элемента совпадения соединены с входами элемента И, выход которого соединен с R-входом первого триггера, причем D-входы второго и третьего D-триггеров и вход сброса одно- вибратора соединены с шиной управляющего сигнала D- и С-входы первого триггера соответственно соединены с шиной логической единицы и первым входом устройства, а S-вход третьего триггера соединен с первым выходом устройства и выходом первого триггера, выход элемента ИЛИ является вторым выходом компаратора.

Л

Л

П

Л.

А 6

В

Г

Л

Е Ж

И

пап

А б В Г

Д Ј Ж И

JV-0

п п п п п п

Фиг.З

п

пп.

п

и-и-и

и

Фиг.4

| Частотно-фазовый компаратор | 1981 |

|

SU983978A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-30—Публикация

1989-10-11—Подача