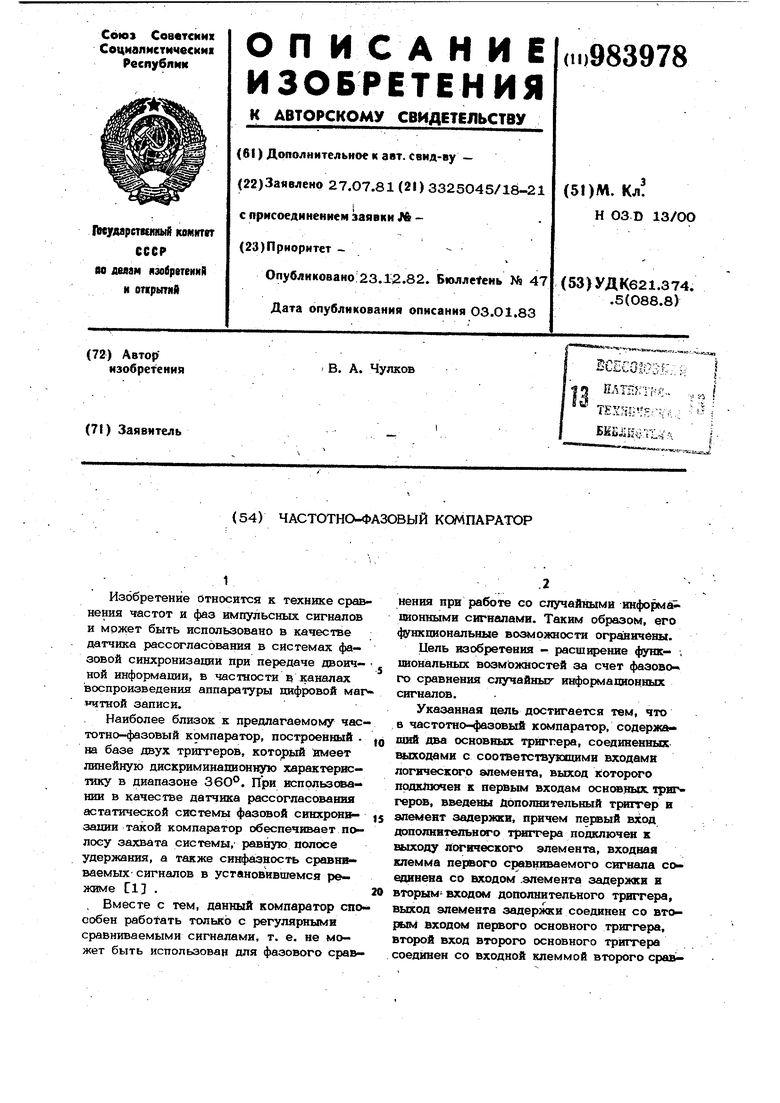

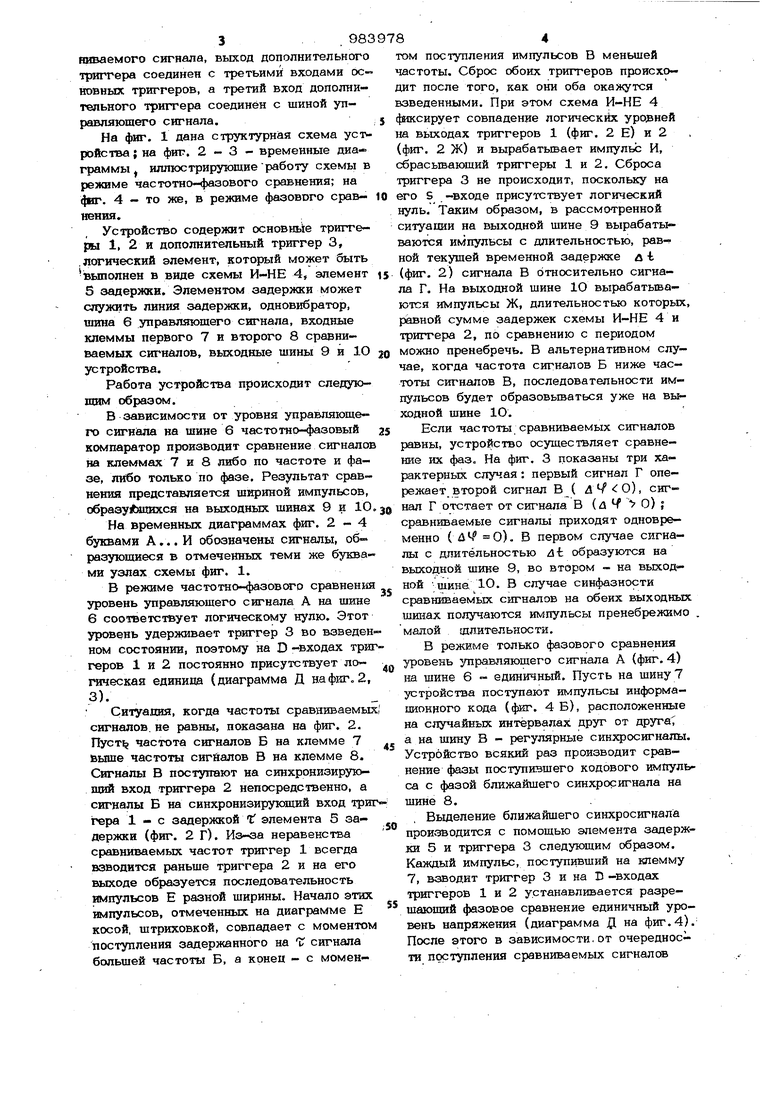

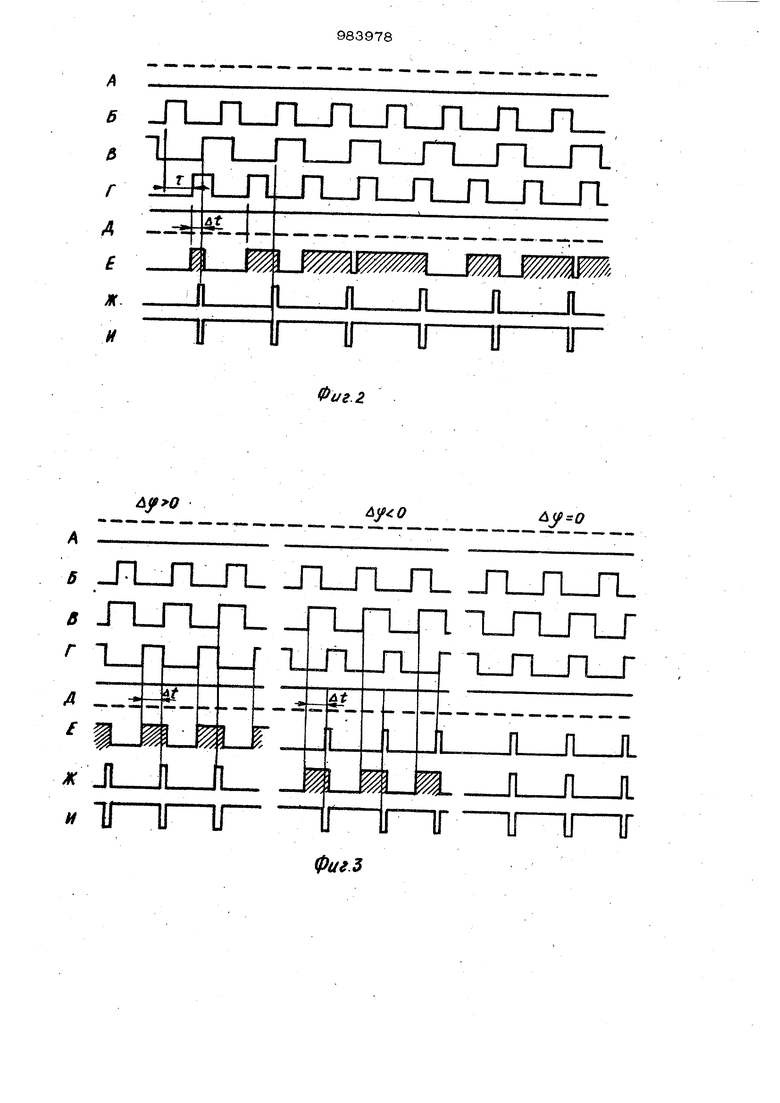

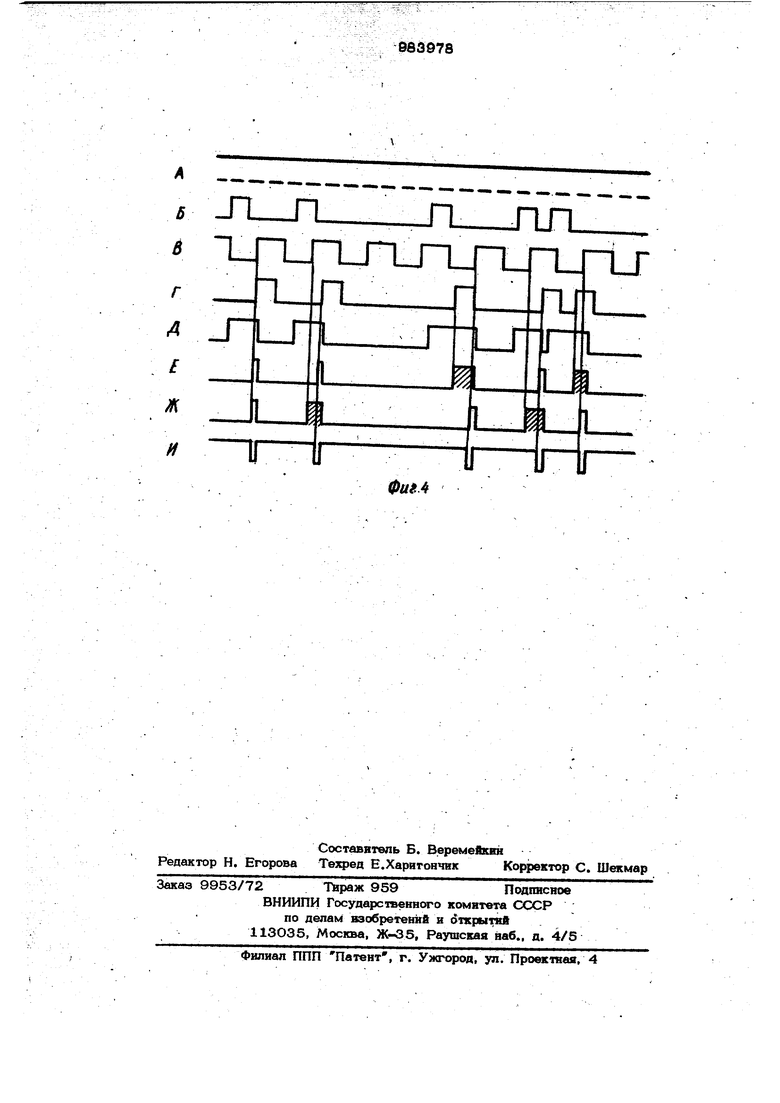

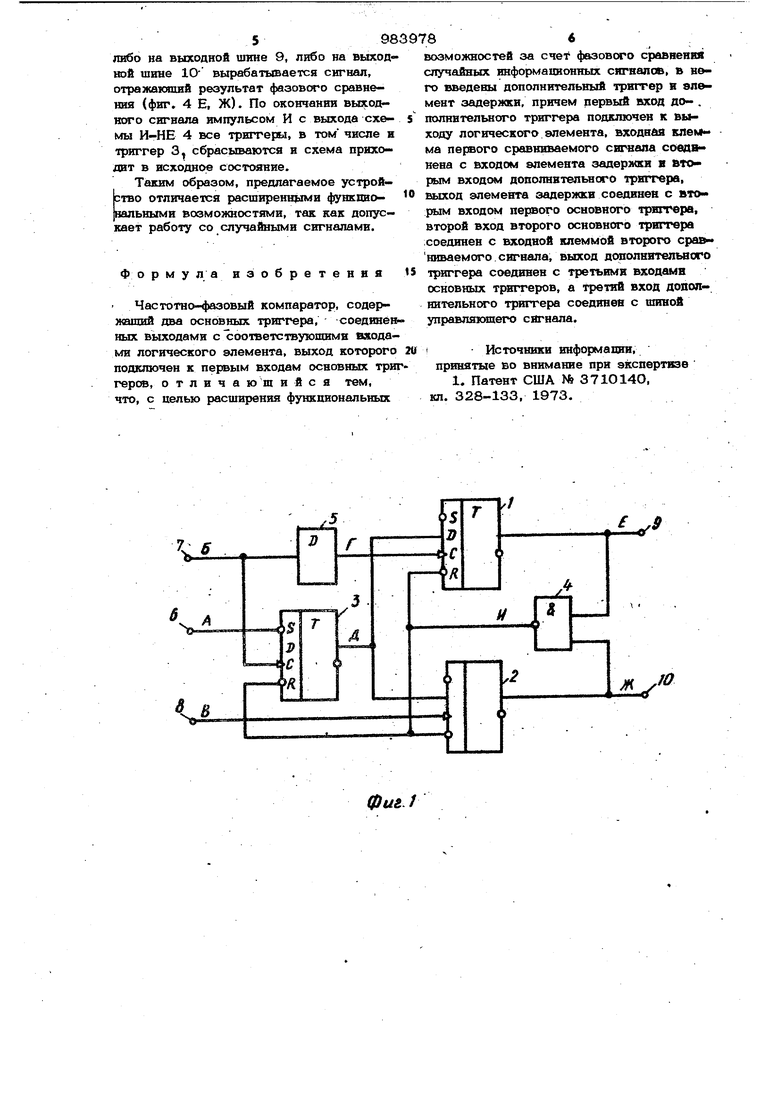

Изобретение отнсюится к технике срав нения частот и фаз импульсных сигналов и мржет быть использовано в качестве датчика рассогласования в системах фазовой синхронизации при передаче двоичной информации, в частности в каналах воспроизведения аппаратуры цифровой маг п1тной записи. Наиболее близок к предлагаемому час тотно-фазовый компаратор, построенный . на базе двух тригтеров, который имеет линейную дискримина1шон1 ГК характервстку в диапазоне ЗбО. При использсжании в качестве датчика рассогласования астатической системы фазовой синхронизации такой компаратор обеспечивает полосу захвата системы, равную полосе удержания, а также синфазность сравниваемых сигналов в ус твновившемся режиме Cl3 . Вместе с тем, данный компаратор cno собен работать только с регулярными сравниваемыми сигналами, т. е. не может быть использован для фазового сравнения при работе со случайными информа пионными сигналами. Таким образом, его функциональные возможности ограничены. Цель изобретения - расшсфение функ- , шональных возможностей за счет фазового сравнения случайныг информационных сигналов. Указанная цель достигается тем, что 8 частотно-фазовый компаратор, содержа ший два основных триггера, соединенных ш 1ходами с соответствующими входами логического элемента, выход которого подключен к первым входам оснстных триггеров, введены дополнительный трптер в элемент задержки, причем первый вход дополнительного триггера подключен к выходу логического элемента, входная клемма первого сравниваемого сигнала соединена со входом .элемента задержки и вторым входом дополнительного триггера, выход элемента задержки соединен со вто1Я 1м входом первого основного триггера, второй вход второго основного триггера соединен со входной клеммой второго срав3.983 ниваемого сигнала, выход дополнительного триггера соединен с третьими входами основных триггеров, а третий вход дополнительного триггера соединён с шиной управляющего сигнала. На фиг. 1 дана структурная схема уст ройства; на фиг. 2 - 3 - временные диаграммы иллюстрирующиеработу схемы в режиме частотно- зазового сравнения; на фнр. 4 - то же, в режиме фазового сравнения. Устройство содержит ocHOBHbte триггеры 1, 2 и дополнительный триггер 3, .логический элемент, который может быть Выполнен в виде схемы И-НЕ 4, элемент 5задержки. Элементом задержки может служить линия задержки, одновибратор, шина 6 управляющего сигнала, входные клеммы первого 7 и второго 8 сравниваемых сигналов, выходные шины 9 и 1О устройства. Работа устройства происходит следующим образом. В зависимости от уровня управляющего CHrHiana на шине 6 частотно-фазовый компаратор производит сравнение сигналов на клеммах 7 и 8 либо по частоте и фазе, либо только по фазе. Результат сравнения представляется шириной импульсов, обраэуЛяцихся на выходных шинах 9 и lO. На временных диаграммах фиг. 2-4 буквами А... И обозначены сигналы, образующиеся в отмеченных теми же буквами узлах схемы фиг. 1. В режиме частотно-фазового сравнения уровень управляющего сигнала А на шине 6соответс-тует логическому нулю. Этот уровень удерживает триггер 3 во взведенном состоянии, поэтоьлу на D -входах триг геров 1 и 2 постоянно присутствует ло гическая единииа (диаграмма Д нафкГо2, Ситуация, когда частоты сравниваемых сигналов, не равны, показана на фиг. 2. Пуст частота сигналов Б на клемме 7 выше частоты сигйалов В на клемме 8. Сигналы В поступают на синхронизирующий вход триггера 2 непосредственно, а

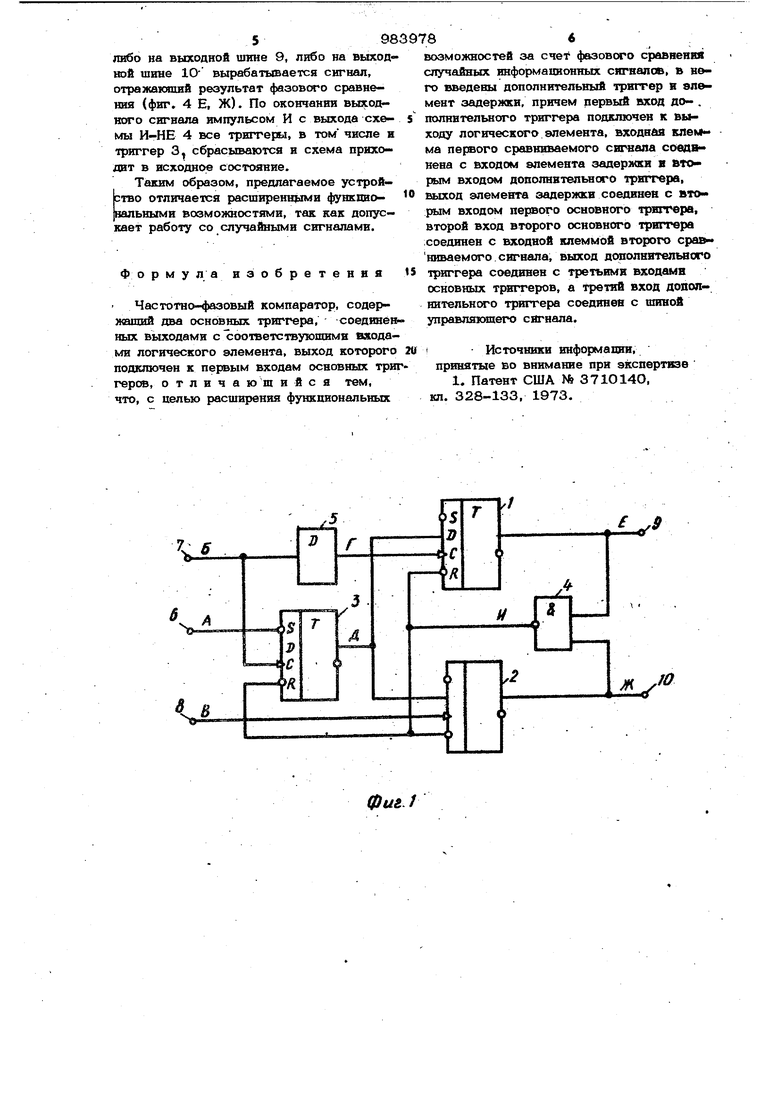

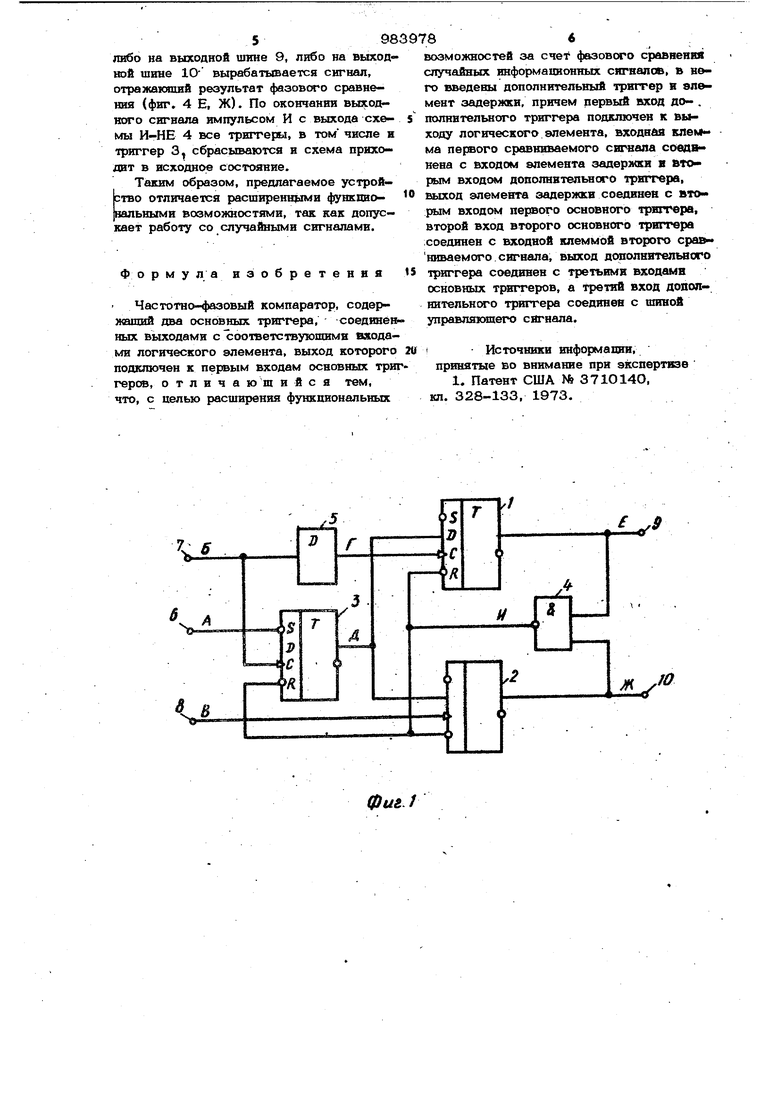

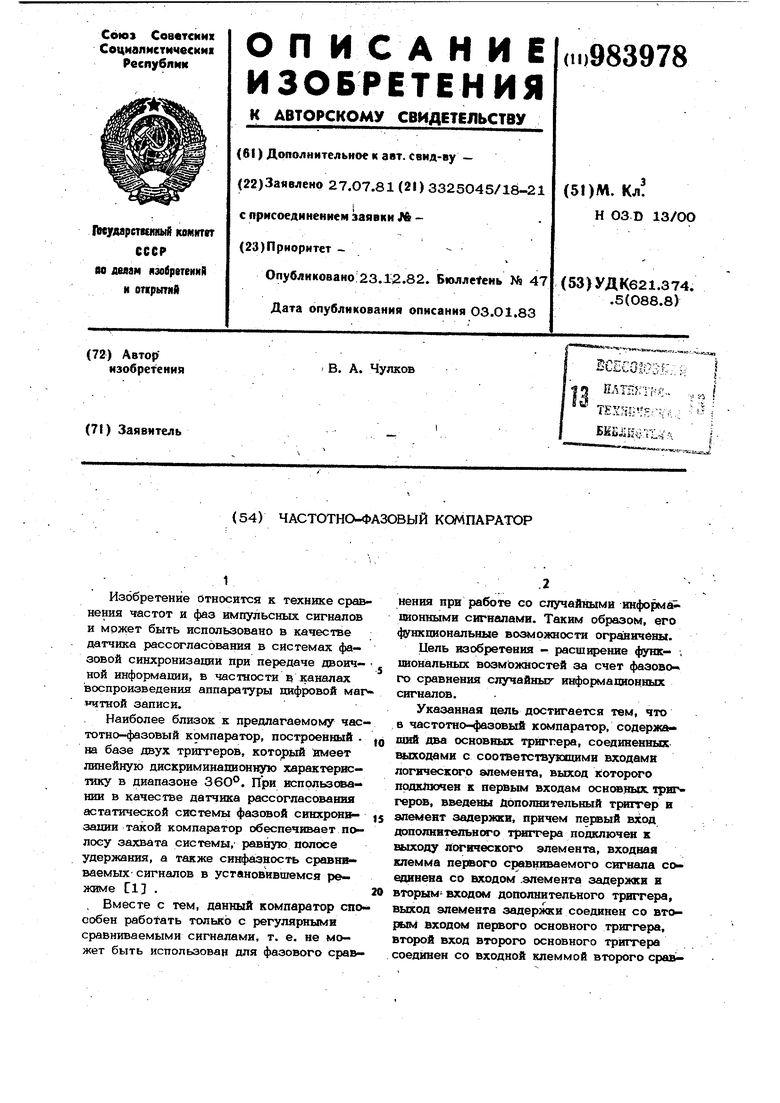

сигналы Б на синхронизирующий вход триг-; шине 8. гера 1-е задержкой t элемента 5 задержки (фиг. 2 Г). неравенства сравниваемых частот триггер 1 всегда взводится раньше триггера 2 к на его выходе образуется последовательность импульсов Е разной ширины. Начало этих импульсов, отмеченных на диаграмме Е косой, штриховкой, совпадает с моментом поступления задержанного на 1 сигнала большей частоты Б, а конец - с момен84том поступления импульсов В меньшей частоты. Сброс обоих триггеров происходат после того, как они оба окажутся взведенными. При этом схема И-НЕ 4 4 п сирует совпадение логических урорней на выходах триггеров 1 (фиг. 2 Е) и 2 (фиг. 2 Ж) и вырабатьтает импульс И, сбрасьюаюший триггеры 1 и 2. Сброса триггера 3 не происходит, поскольку на его S -входе присутствует логический нуль. Таким образом, в рассмотренной ситуации на выходной шине 9 вырабатываются импульсы с длительностью, текущей временной задержке Ai (фиг. 2) сигнала В относительно сигнала Г. На выходной шине 10 вырабатываются импульсы Ж, длительностью которых, равной сумме задержек схемы И-НЕ 4 и триггера 2, по сравнению с периодом можно пренебречь. В альтернативном случае, когда частота сигналов Б ниже частоты сигналов В, последовательности импульсов будет образовьгоаться уже на выходной щине 1О. Если частоты сравниваемых сигналов равны, устройство осуществляет сравнение их фаз. На фиг. 3 показаны три характерных случая: первый сигнал Г опережает второй сигнал В ( 4 / О), сигнал Г отстает от сигнала В (а Ч О) j сравниваемые сигналы приходят одновременно (иЧ 0). В первом случае сигналы с длительностью dt образуются на выходной шине 9, во втором - на выход ной шине 1О. В случае синфазности сравниваемЫх сигналов на обеих выходных mKiiax получаются импульсы пренебрежимо . малой , щлительности. В режиме только фазового сравнения уровень управляющего сигнала А (фиг. 4) единичный. Пусть на шину 7 на шине 6 устройства поступают импульсы информационного кода (фиг. 4 Б), расположенные на случайных интервалах друг от друга7 а на шину В - регулярные синхросигналы. Устройство всякий раз производит сравнение фазы поступившего кодового импульса с фазой ближайшего синхросигнала на Вьщеление ближайшего синхросигнала производится с помощью элемента задержки 5 и триггера 3 следующим образом. Каждый импульс, поступивший на клемму 7, взводит триггер 3 и на D -входах триггеров 1 и 2 устанавливается разрешающий фазовое сравнение единичный уровень напряжения (диаграмма Д на фиг. 4). После этого в зависимости, от очередности поступления сравниваемых сигналов лябо на выходной шине 9, либо на выходной шине 10 вырабатьюается снгнал, отражающий результат фазового сравнения (фиг. 4 Е, ж). По окончании вьссодного сигнала импульсом И с выхода схемы И-НЕ 4 все триггеры, в том числе и триггер 3, сбрасываются и схема приходит в исходное состояние. Таким образом, предлагаемое устройство отличается расширешщмн функшо|нальными возможностями, так как допускает работу со случайными сигналами. Формула изобретения Частотно-фазовый компаратор, содержащий два основных триггера, соединё ных выходами с Соответствующими входами логического элемента, выход которого подключен к переым входам основных три1г герое, отличающийся тем, что, с целью расширения функпиональных возможностей за счет фазового сравнения случайных информационных сигналов, в ного введены дополнительный триггер и элемент задержки, причем первый вход до- . полнительного триггера подключен к выходу логического элемента, входная клемма первого сравниваемого сигнала соедвнена с входом элемента задержки в &то рым входом дополнительного триггера, выход элемента задержки соединен с вторым входом первого основного триггера, второй вход второго основного триггера соединен с входной клеммой второго срав« ниваемого сигнала, выход дсшолнитешАого триггера соединен с третьими входами основных триггеров, а третий BXOJK дополнительного триггера соединен с шиной управляющего сигнала. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3710140, кл. 328-133, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой синхронизации для дискового накопителя цифровых данных | 1988 |

|

SU1615799A1 |

| Цифровой частотно-фазовый компаратор | 1985 |

|

SU1248025A1 |

| Частотно-фазовый компаратор | 1989 |

|

SU1688382A1 |

| Устройство выделения информации из частотно-модулированного сигнала | 1977 |

|

SU622148A1 |

| Широтно-импульсный частотно-фазовый детектор | 1982 |

|

SU1075368A1 |

| Устройство для синхронизации воспроизведения информации | 1987 |

|

SU1465909A1 |

| Устройство воспроизведения информации с оптического носителя | 1986 |

|

SU1345248A1 |

| УСТРОЙСТВО АНАЛОГОВОГО ДАТЧИКА УГЛА ФАЗОВОГО СДВИГА МЕЖДУ НАПРЯЖЕНИЕМ И ТОКОМ | 2011 |

|

RU2492572C2 |

| Устройство для декодирования сигнала воспроизведения магнитной записи | 1985 |

|

SU1304071A1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

Фи& / Щ..Ш 1 п

Фив. 2

(0 п .ШШ п п и и II Л . 5 1-. п

лл

Авторы

Даты

1982-12-23—Публикация

1981-07-27—Подача