О 00 00

со ю

00

Изобретение относится к импульсной технике и предназначено для использования в аналого-цифровых системах различного назначения, выполненных по КМОП технологии быстродействующих БИС и СБИС.

Цель изобретения - расширение области применения за счет уменьшения емкости выходных узлов.

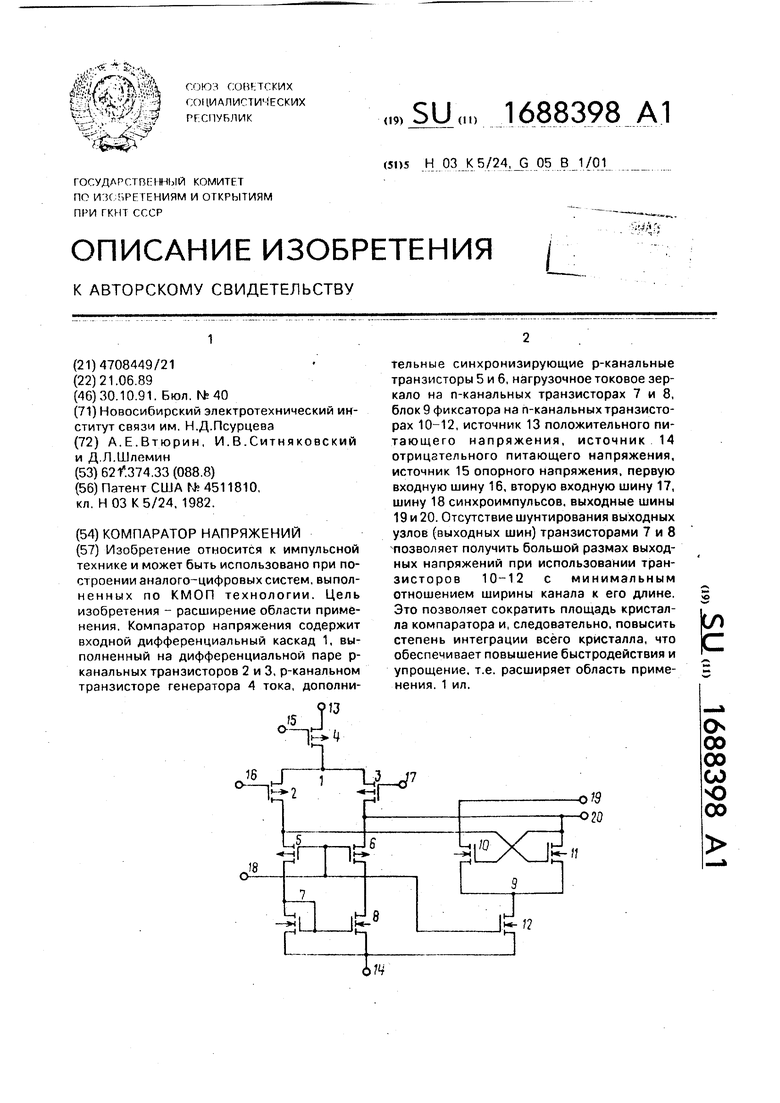

На чертеже изображена принципиальная электрическая схема предлагаемого компаратора напряжений, на которой под МОП-транзисторами с каналами первого типа проводимости подразумеваются р-ка- нальные МОП-транзисторы, под МОП-транзисторами с каналами второго типа проводимости подразумеваются п-ка- нальные МОП-транзисторы, а под первой шиной источника питания - отрицательная шина источника питания.

Компаратор напряжений содержит входной дифференциальный каскад 1, выполненный на дифференциальной паре р- канальных транзисторов 2 и 3, р-канальном транзисторе генератора 4 тока, дополнительные синхронизирующие р-канальные транзисторы 5 и 6, нагрузочное токовое зеркало на n-канальных транзисторах 7 и 8, а также блока 9 фиксатора на п-канальных транзисторах 10-12, источник 13 положительного питающего напряжения, источник 14 отрицательного питающего напряжения, источник 15 опорного напряжения, первую входную шину 16, вторую входную шину 17, шину 18 синхроимпульсов, выходные шины 19 и 20. При этом входной дифференциальный каскад состоит из генератора 4 тока, выполненного на МОП-транзисторах с каналом первого типа проводимости, дифференциальной пары МОП-транзисторов 2 и 3 с каналами первого типа проводимости, нагрузки в виде токового зеркала на МОП- транзисторах 7 и 8 с каналами второго типа проводимости и блок 9 фиксатора, содержащий синхронизирующий МОП-транзистор 12 с каналом второго типа проводимости, исток которого подключен к первой шине источника 14 питания, затвор подключен к шине 18 синхроимпульсов, а сток соединен с истоками двух МОП-транзисторов 10 и 11 с каналами второго типа проводимости, при этом затвор и сток первого из этих транзисторов 10 подключен к стоку и затвор соответственно второго из этих транзисторов 11, причем стоки последних двух транзисторов 10 и 11 подключены к стокам транзисторов 2 и 3 дифференциальной пары и к выходным шинам устройства, два дополнительных синхронизирующих МОП-транзистора 5 и 6 с каналами первого типа проводимости, истоки которых соединены

со стоками транзисторов 2 и 3 дифФорпнци- альной пары, а стоки со стоками транзи сторов 7 и В токового зеркала, при этом затворы дополнительных синхронизирующих транзисторов 5 и 6 подключены к шине 18 синхроимпульсов.

Компаратор напряжений работает следующим образом.

Предположим, что на шине 18 синхро0 импульсов имеется низкий логический уровень. При этом транзисторы 5 и 6 открыты и не оказывают влияния на работу дифференциального каскада 1, так как сопротивление канала открытого МОП-транзистора пре5 небрежимо мало по сравнению с динамическим сопротивлением нагрузки токового зеркала. Разность уровней напряжений на выходных шинах 19 и 20 соответствует усиленной разности входных сигналов, подан0 ных на затворы транзисторов шин 16 и 17. В момент подачи на шину 18 синхроимпульса транзисторы 5 и 6 закрываются, устраняя таким образом шунтирование выходных шин 19 и 20 транзисторами 7 и 8. При этом

5 транзистор 12 фиксатора открывается и фиксатор срабатывает, устанавливая на выходных шинах 19 и 20 логические уровни, соответствующие разности входных напряжений. Так как при подаче синхроимпульса

0 отсутствует шунтирование выходных шин транзисторами токового зеркала, как указывалось выше, то весь ток. транзистора генератора 4 протекает либо через транзисторы 10 и 12, либо 11 и 12, в зависимости от

5 полярности разности входных напряжений. Другими словами, один из транзисторов 10 или 11 закрыт, следовательно, на его стоке установится уровень напряжения, близкий к напряжению источника 13 питания. Соот0 ветственно другой из указанных транзисторов находится в ненасыщенном состоянии и сопротивление его канала значительно меньше, чем сопротивление канала одного из транзисторов 2 и 3 и транзистора генера5 тора 4, работающих в режиме насыщения. Это означает, что на соответствующей выходной шине устанавливается уровень напряжения, близкий к напряжению источника 14 питания. Отсутствие шунтиро0 вания выходных шин транзисторами 7 и 8 позволяет получить большой размах выходных напряжений при использовании транзисторов 10-12 с минимальным отношением ширины канала к его длине.

5 Это позволяет сократить площадь кристалла ИС, занимаемую компаратором и, следовательно, повысить степень интеграции всего кристалла. Кроме того, при этом значительно уменьшается емкость выходных шин, следовательно, повышается быстродействие, что позволяет отказаться от разрядки емкостей выходных шин при помощи подключения МОП-транзистора между выходными шинами и использования генератора импульсов разрядки. Разрядка указанных шин происходит достаточно быстро через транзисторы 5, 7 и 6, 8 после установления на шине 18 низкого логического уровня.

Формула изобретения Компаратор напряжений, содержащий входной дифференциальный каскад, состоящий из генератора постоянного тока, выполненного на МОП-транзисторе с каналом первого типа проводимости, дифференциальную пару МОП-транзисторов с каналами первого типа проводимости, затворы которых подключены к входным шинам компаратора, нагрузки в виде токового зеркала на МОП-транзисторах с каналами второго типа проводимости, истоки которых подключены к первому источнику напряжения питания.

и блок фиксатора, содержащий синхронизирующий МОП-транзистор с каналом второго типа проводимости, исток которого подключен к первому источнику напряжения питания, затвор соединен с шиной синхроимпульсов, а сток соединен с истоками двух МОП-транзисторов с каналами второго типа проводимости, затвор и исток первого из которых подключены к стоку и

затвору соответственно второго из этих транзисторов, а стоки подключены к стокам транзисторов дифференциальной пары и выходным шинам устройства, отличающийся тем, что, с целью расширения

области применения, в дифференциальный каскад введены два дополнительных синхронизирующих МОП-транзистора с каналами первого типа проводимости, истоки которых подключены к стокам транзисторов

дифференциального каскада, стоки - к стокам транзисторов токового зеркала, а затворы подключены к шине синхроимпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ КМОП КОМПАРАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2019913C1 |

| НИЗКОВОЛЬТНОЕ КМОП ТОКОВОЕ ЗЕРКАЛО | 2013 |

|

RU2544780C1 |

| ВЫСОКОЧАСТОТНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ СТАБИЛИЗАЦИИ ТОКА КОЛЛЕКТОРА | 2012 |

|

RU2509407C1 |

| Интегральный К-МОП дифференциальный усилитель | 1988 |

|

SU1575850A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| Многопороговый КМОП-компаратор тока | 1985 |

|

SU1309288A1 |

| ПРЕЦИЗИОННЫЙ КМОП УСИЛИТЕЛЬ | 2005 |

|

RU2310270C1 |

| Интегральный компаратор на КМОП-транзисторах | 1988 |

|

SU1552366A1 |

| Компаратор | 1979 |

|

SU843179A1 |

Изобретение относится к импульсной технике и может быть использовано при пост роении аналого-цифровых систем, выпол- ненных по КМОП технологии. Цель изобретения - расширение области применения. Компаратор напряжения содержит входной дифференциальный каскад 1, выполненный на дифференциальной паре р- канальных транзисторов 2 и 3, р-канальном транзисторе генератора 4 тока, дополнительные синхронизирующие р-канальные транзисторы 5 и 6. нагрузочное токовое зеркало на n-канальных транзисторах 7 и 8, блок 9 фиксатора на n-канальных транзисторах 10-12, источник 13 положительного питающего напряжения, источник 14 отрицательного питающего напряжения, источник 15 опорного напряжения, первую входную шину 16, вторую входную шину 17, шину 18 синхроимпульсов, выходные шины 19 и 20. Отсутствие шунтирования выходных узлов (выходных шин) транзисторами 7 и 8 позволяет получить большой размах выходных напряжений при использовании транзисторов 10-12 с минимальным отношением ширины канала к его длине. Это позволяет сократить площадь кристалла компаратора и, следовательно, повысить степень интеграции всего кристалла, что обеспечивает повышение быстродействия и упрощение, т.е. расширяет область применения. 1 ил. И

| Патент США № 4511810 | |||

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-10-30—Публикация

1989-06-21—Подача