J7

СП

ел

N3

сс о

05

Изобретение относится к импульсной технике и может быть использовано в устройствах преобразования информации, а также в контрольно-измеритель- с ных устройствах.

Цель изобретения - повышение точности путем уменьшения входного напряжения смещения нуля устройства и расширение области применения за счет ю расширения диапазона входных напряжений по синфазной составляющей сигна- ла.

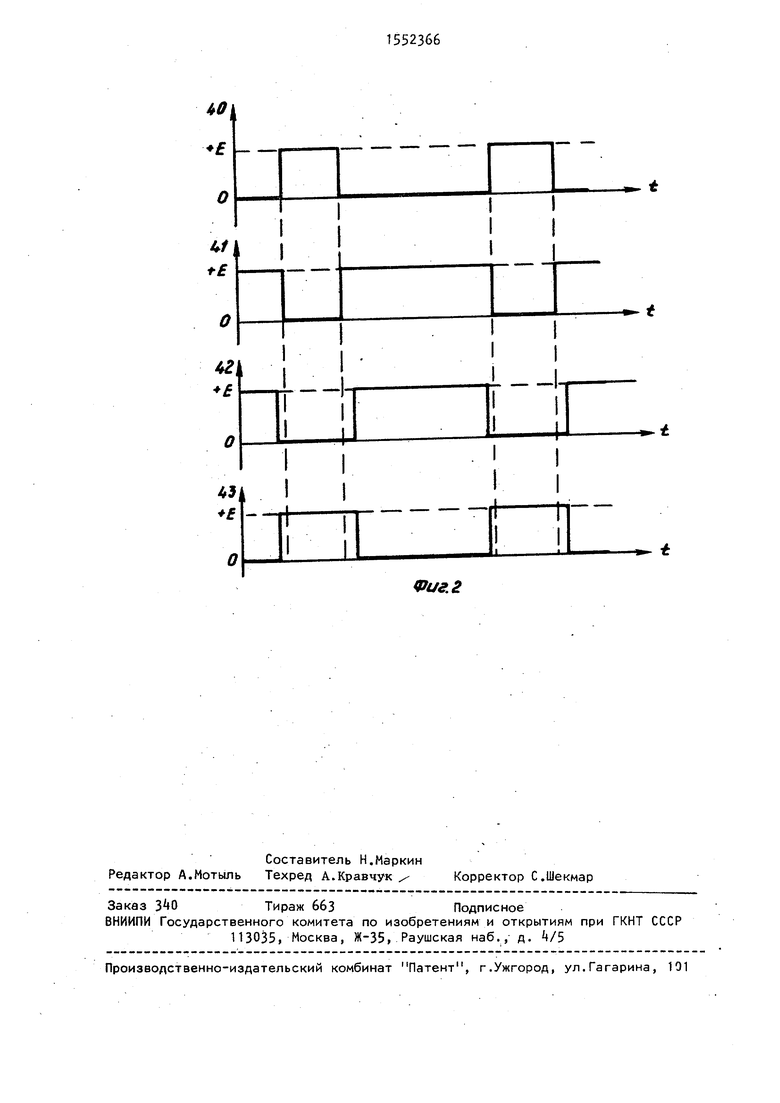

На фиг. 1 представлена принципиальная схема компаратора; на фиг.2- )5 диаграмма тактирующих импульсов.

Интегральный компаратор на КМОП- транзисторах содержит первый 1 и второй 2 дифференциальные усилители, выходной усилитель 3, первый и второй 20 конденсаторы k и 5 и коммутаторы 6- 11, каждый из которых содержит п- и р-канальные транзисторы, имеющие общие исток и сток, причем первый дифференциальный усилитель 2 содержит 25 n-канальный транзистор 12, подключенный истоком к общей шине 13, а затвором - к шине источника смещения, к его стоку подключены истоки управляющих n-канальных транзисторов 15 зо и 16, затворы которых являются соответственно входами 17 и 18 второго дифференциального усилителя, а к стокам, являющимся соответственно выходами 19 и 20 второго дифференциального усилителя 2 подключены соответственно стоки р-канальных нагрузочных транзисторов 21 и 22, истоки которых подключены к положительной шине 23 питания, а затворы - к выходу .„ 19, а между выходами 19 и 20 навстречу друг другу включены два диода 24 и 25.

Первый дифференциальный усилитель 1 содержит n-канальный транзистор 26, подключенный истоком к общей шине 13, а затвором - к шине источника смещения, к его стоку подключены истоки управляющих n-канальных транзисторов 27 и 28, затворы которых являются - соответственно входами 29 и 30 первого дифференциального усилителя, а к стокам, являющимся соответственно выходами 31 и 32 первого дифференциального усилителя 1, подключены соответственно стоки р-канальных нагрузочных транзисторов 33 и 3, истоки которых подключены к положительной шине 23 питания, а затворы - к

35

55

5

0 5 о „

-

5

5

выходу 31, выходной усилитель 3 содержит n-канальный транзистор 35, истоком подключенный к общей шине 13, а затворы - к шине И источника смещения, и р-канальный транзистор 36, истоком подключенный к положительной шине 23 питания, стоки транзисторов 35 и 36 объединены и подключены к выходной шине 37, коммутатор 6 включен между первой обкладкой первого конденсатора 4, подсоединенной к входу 17, затвором транзистора 36, подсоединенным к выходу 32.

Кроме того, коммутатор 7 включен между первой обкладкой второго конденсатора 5, подсоединенной к входу

18,и выходам 30, подключенным к выходу 20, вход 29 подключен к выходу

19,коммутатор 8 включен между первой входной шиной 38 и второй обкладкой второго конденсатора 5, коммутатор 9 - между шиной 38 и второй об- кладкой первого конденсатора 4, коммутатор 10 - между второй входной шиной 39 устройства и второй обкладкой второго конденсатора 5, коммутатор 11 - между шиной 39 и второй обкладкой первого конденсатора 4. Затворы п- и р-канальных транзисторов коммутаторов 6, 7, 9 и 10 подключены соответственно к шинам 0, k тактовых сигналов, затворы п- и р-канальных транзисторов коммутаторов 8 и 11 подключены соответственно к шинам k2, 3 тактовых сигналов, подложки всех р-канальных транзисторов подключены

к положительной шине 23 питания, подложки n-канальных транзисторов 15, 16, 23, 2Д - к соответствующим истокам, а остальных n-канальных транзисторов - к общей шине 13.

Устройство работает следующим образом.

Компаратор имеет режимы настройки и сравнения. Диаграмма тактирующих импульсов (фиг.2) построена таким образом, чтобы не было сквозных токов между входами устройства на фронтах переключения коммутаторов. В режиме настройки открыты транзисторы коммутаторов 6, 7, 9 и 10, при этом во втором дифференциальном усилителе 2 вход 18 закорачивается с выходом

20,а вход 17 подключается к выходу 32 первого дифференциального усилителя 1, замыкая таким образом цепь обратной связи по двум каскадам. Кон

5

денсатор Ц через коммутатор У подклчен к входной шине 38, а конденсато 5 через коммутатор 10 - к входной шине 39. Так как в режиме настройки транзистор 16 находится в диодном включении (закорочены сток с затвором) , общий коэффициент усиления по петле обратной связи определяется в основном коэффициентом усиления первого дифференциального усилителя и не является высоким (не более 102). Это позволяет для подавления возможных колебаний обойтись узловыми емкостями без корректирующих конденсаторов, специально подключаемых в момент настройки. Таким образом, в момент настройки на входе 17 устанавливается потенциал, равный сумме напряжений на входе 18 и некоторого напряжения, равного смещению нуля по двум дифференциальным усилителям 1 и 2. При этом конденсатор заряжется до напряжения

иг - (и

8

см).

напряжение сигнала на входе 39;

входное смещение нуля по двум каскадам компаратора; напряжение на входе 18 в режиме настройки. сатор 5 заряжается до напря

U4

где U( - напряжение на первом входе

38 устройства.

В момент сравнения транзисторы коммутаторов 6, 7, 9 и 10 закрываются, а коммутаторы 8 и 11 открываются, При этом разрывается обратная связь с выхода второго дифференциального усилителя на вход второго, а затвор и сток транзистора 16 размыкаются. Первые обкладки конденсаторов k и 5 - меняют свое подключение, при этом на входе 17 получают напряжение

U« + см+ (U4 - на входе 18

U

U,), (3)

U - (Ue - U,).СО

Таким образом, на входы второго дифференциального усилителя подается разностное напряжение

U

8

- (и4 - и,).

(5)

10

20

25

30

35

,

40

45

50

Из выражений (3), (М и (5) видно, что результирующее напряжение, подаваемое на входы второго дифференциального усилителя 2, не зависит от уровня синфазной составляющей сигнала (оно все время привязано к уровню напряжения U ,й), что позволяет получить нижнюю границу входных сигналов по синфазной составляющей, равную напряжению общей шины. При этом для пороговых напряжений р-канальных 15 транзисторов, равных 0,5 В, и напряжения питания, равного 1,5 В, диапазон входных напряжений по синфазной составляющей увеличивается в 1,5 раза.

В значение величины дифференциальной разности (5) входит - входное напряжение смещения нуля по двум каскадам компаратора, что практически определяет полное входное напряжение смещения нуля компаратора, так как влияние выходного каскада на эту величину незначительно. Таким образом, происходит полная настройка нуля компаратора. Наличие трех каскадов усиления позволяет добиться высокой чувствительности компаратора (не менее 200 мкВ). Типичным входным напряжением смещения нуля прототипа является значение 5 мВ. Предлагаемое устройство позволяет не менее чем на порядок уменьшить данную величину.

На входы второго дифференциального усилителя подается удвоенная разность входных напряжений, что позволяет уменьшить требования к величине емкостей конденсаторов и 5 (для хорошей передачи сигналов эти величины должны на порядок превышать затворные емкости транзисторов 15 и 16).

Таким образом, в предлагаемом устройстве получен положительный эффект, выраженный в повышении точности путем уменьшения входного напряжения смещения нуля устройства и в расширении области применения за счет расширения диапазона входных напряжений по синфазной составляющей сигнала.

Формула изобретения

Интегральный компаратор на КМОП- транзисторах, содержащий дифференциальный усилитель и выходной каскад, выход которого подключен к выходной

шине, при этом дифференциальный усилитель содержит первый п-канальный транзистор, затвор которого подключен к шине источника смещения, исток- к общей шине, а сток - к истокам второго и третьего n-канальных транзисторов, затворы которых являются соответственно первым и вторым входами, а стоки - первым и вторым выходами дифференциального усилителя, к которым соответственно подключены стоки четвертого и пятого р-канальных тран- з сторов, истоки которых подключены к положительной шине питания, а зат- воры - к первому выходу дифференциального усилителя, выходной усилитель содержит р-канальный транзистор, исток которого подключен к положительной шине питания, затвор является входом выходного каскада, а сток подключен к выходной шине и стоку п-ка- нального транзистора, исток которого подключен к общей шине, а затвор соединен с шиной источника смещения, вход выходного усилителя подключен к второму выходу дифференциального усилителя а подложка каждого из МОП-транзисторов закорочена с соответствующим истоком, первый и второй коммутаторы и конденсатор, отличающийся тем, что, с целью повышения точности путем уменьшения входного напряжения, смещения нуля устройства и расширения области применения за счет расширения диапазона входных напряжений по синфазной составляющей сигнала, в него введены четыре шины тактовых сигналов, второй конденсатор, второй дифференциальный усилитель, аналогичный первому, третий, четвертый, пятый и шестой коммутаторы, каждый из которых

содержит р- n-tn-канальный транзистор с общими стоками и истоками, причем первый коммутатор включен между входом выходного усилителя и первым входом первого дифференциального усилителя, к которому подключена также певая обкладка первого конденсатора, второй коммутатор включен между вторым выходом и вторым входом первого дифференциального усилителя, к которому подключена также первая обкладка второго конденсатора, третий коммутатор подключен между первой входной шиной устройства и второй обкладкой второго конденсатора, четвертый коммутатор - между первой входной шиной устройства и второй обкладкой первого конденсатора, пятый коммутатор - между второй входной шиной устройства и второй обкладкой второго конденсатора, шестой коммутатор - между второй входной шиной устройства и второй обкладкой первого конденсатора, затворы n-канальных транзисторов первого, второго, четвертого и пятого коммутаторов подключены к шине первого тактового сигнала, затворы р-канальных транзисторов тех же коммутаторов - к шине второго тактового сигнала, затворы п-канальных транзисторов третьего и шестого коммутаторов подключены к шине третьего тактового сигнала, а затворы р-канальных транзисторов тех же коммутаторов - к шине четвертого тактового сигнала, подложки р-канальных транзисторов коммутаторов подключены к положительной шине питания, а подложки n-канальных транзисторов коммутаторов - к общей шине.

- Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| Источник опорного напряжения | 1990 |

|

SU1748224A1 |

| ПРЕЦИЗИОННЫЙ КМОП УСИЛИТЕЛЬ | 2005 |

|

RU2310270C1 |

| Операционный усилитель | 1989 |

|

SU1695491A1 |

| Усилительное устройство | 1988 |

|

SU1571749A1 |

| КМОП усилитель с чоппер стабилизацией и способ калибровки | 2019 |

|

RU2724989C1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Операционный усилитель | 1989 |

|

SU1672554A1 |

| Дифференциатор для обработки аналоговых сигналов (варианты) | 2016 |

|

RU2628243C1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах преобразования информации, а также в контрольно-измерительных устройствах. Цель изобретения - повышение точности и расширение области применения. Введение в интегральный компаратор на КМОП транзисторах, ссодержащий два дифференциальных усилителя 1, 2 и выходной усилитель 3, двух конденсаторов 4, 5, коммутаторов 6 - 11 позволило повысить точность путем уменьшения входного напряжения смещения нуля устройства и расширить область применения за счет расширения диапазона входных напряжений по синфазной составляющей сигнала. Кроме того, дифференциальные усилители 1, 2 выполнены на N-канальных транзисторах 12, 26, 15, 16, 21, 2, 33, 34, 27, 28, а коммутаторы - на N- и P-канальный транзисторах, имеющих общие сток и исток. 2 ил.

Фиг. 2

| Подъемный механизм | 1961 |

|

SU150606A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ( ИНТЕГРАЛЬНЫЙ КОМПАРАТОР НА КМОП- -ТРАНЗИСТОРАХ | |||

Авторы

Даты

1990-03-23—Публикация

1988-02-18—Подача