(54)КОМПАРАТОР

38431

НИИ, удельных крутизн транзисторов и др.}.

Цель изобретения - снижение погрешности компаратора.

Указанная цель достигается тем, , что в компаратор, содержащийосновной и дополнительный дифференцисшьные каскады, каждый из которых состоит из генератора тока в цепи обратной связи и двух параллельных диф- ю ференциальных плеч, состоящих из последовательно включенных управляющего МОП-транзистора и нагрузочного МОП-транзистора, включенных между генератором тока-и шиной питания, 15 вход дополнительного дифференциаль.ного каскада соединен с первым входом компаратора, введены первый и второй конденсаторы,- первый, второй, третий и четвертый коммутирующие МОП- 20 транзисторы, причем затворы п.ервого и второго МОП-транзистороа подключены к первой и второй шинам управляющего сигнала, сток и исток первого коммутирующего МОП-транзистора подключены со-25 ответственно к первому и второму вхо-, дам дополнительного дифференциального каскада, сток и исток второго коммутирующего МОП-транзистора под ключены соответственно ко второ- JQ му входу компаратора и второму входу дополнительного дифференциаль-., ного каскада, затворы третьего и четвертого коммутирующих МОП-транзисторов подключены к входной шине, сток и исток третьего коммутирующего МОПтранзистора подключены соответственно к первому выходу дополнительного и первому входу основного дифференциальных каскадов, сток и исток чет- Q вертого коммутирующего МОП-транзистора подключены соответственно ко второму выходу дополнительного и второму входу основного дифференциальных каскадов, а дервый и второй кон- 5 денсаторы включены между затворами и стоками управляющих МОП-транзисторов основного-дифференциального каскада, а затворы нагрузочных МОПтранзисторов основного и дополни- jg тельного дифференциальных каскадов попарно объединены.

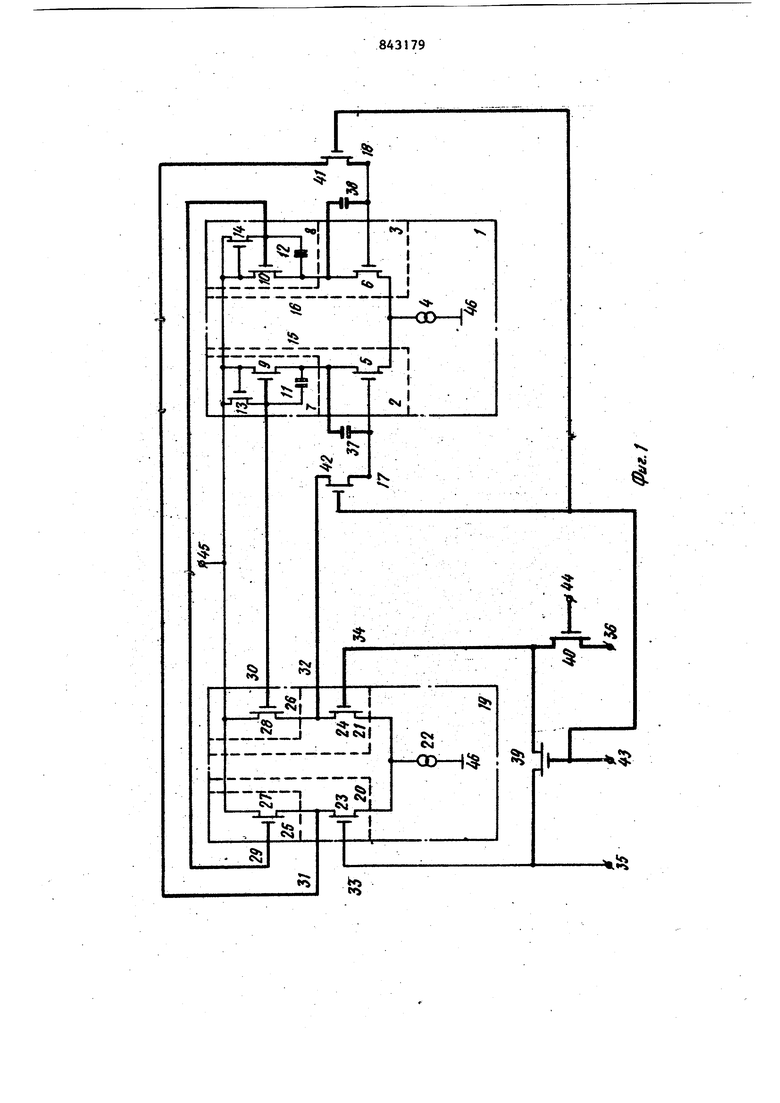

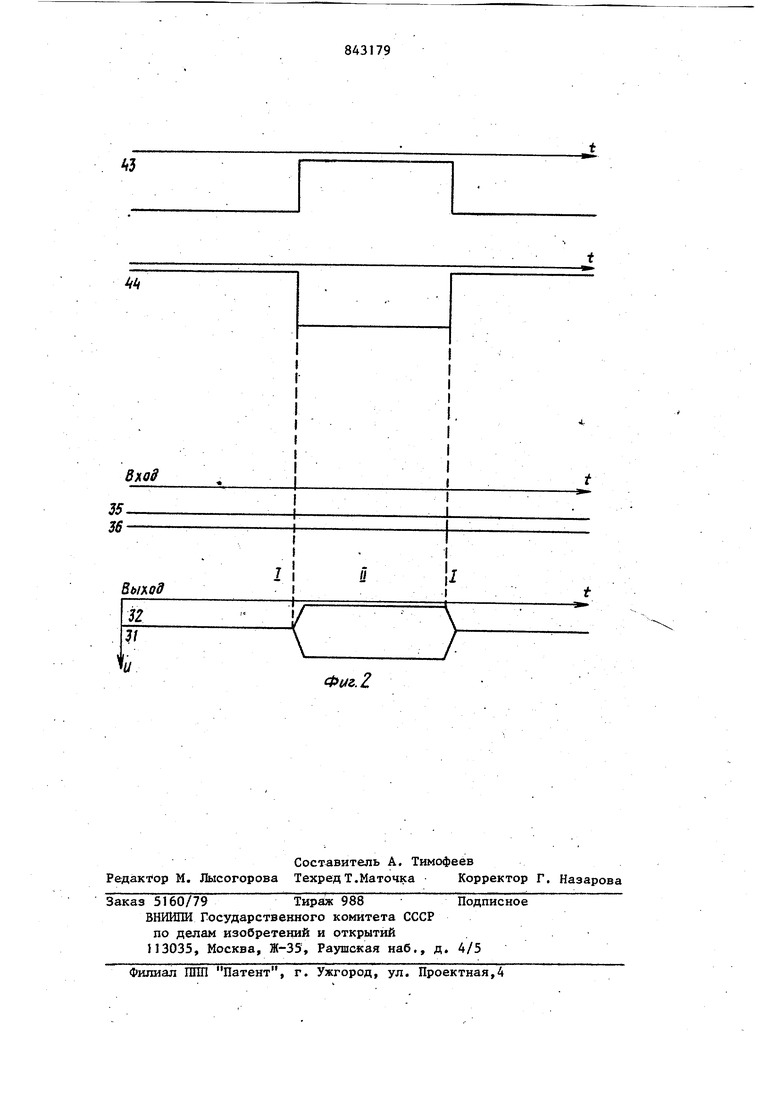

На фиг. 1 представлена принципиальная злектрическая схема предлагаемого компаратора на МДП-транзисторах; jj .на фиг. 2 - эпюры напряжений управляющих, входных и выходных сигналов.

Компаратор на МДП-транзисторах содержит основной дифференциальный

79 ,4

каскад 1, два дифференциальных плеча 2 и 3, генератор 4 тока, два управляющих МОП-транзистора 5 и 6, два нагрузочных МОП-элемента 7 и 8, нагрузочные МОП-транзисторы 9 и 10, конденсаторы 11 и 12 обратной связи нагрузочного элемента,заряжающие транзисторы 13 и 14, выходы 15 и 16 основного дифференциального каскада входы 17 и 18 основного дифференциального каскада, дополнительный дифференциальный каскад 19, два дифференциальных плеча 20 и 21,генератор 22 тока, два управляюпщх транзистора 23 и 24, р,ва нагрузочных элемента 25 и 26, нагрузочные МОПтранзисторы 27 и 28, затворы 29 и 30 нагрузочных транзисторов.выходы 31 и 32 компаратора, входы 33 и 34 дополнительного дифференциального каскада, два входа 35 и 36 компаратора, конденсаторы 37 и 38 обратной связи, четыре коммутирующие транзистора 39-42, шины 43 и 44 управляющего сигнала,шины 45 питания и земли 46.

Основной дифференциальный каскад, имеет два параллельных дифференциальных плеча 2 и 3, каждое из которых состоит из последователь,но включенных управляющих МОП-транзисторов 5 и 6 и нагрузочных элементов 7 и 8, общие узлы которых 15 и 16 являются выходом основного дифференциального каскада. Истоки управляющих Ж)Птранзисторов 5 и 6 объединены и подключены к пшне 46 земли через генератор 4 тока. Нагрузочные элементы 7 и 8 содержат нагрузочные МОП-транзисторы 9 и10, стоки которых подключены к шине 45 питания, заряжающие транзисторы 13 и 14, подключенные стоком и затвором к шине 45 питания, а истоком - к затворам нагрузочных МОП-транзисторов 29 и 30 и конденсаторы 11 и 12 обратной связи нагрузочных элементов, включенные между затвором и истоком нагрузочных транзисторов 9 и 10.

Два конденсатора 37 и 38 обратной связи включены между затвором и стоком управляющих МОП-транзисторов 5 и 6.

Дополнительный дифференциа льный каскад 19 имеет два параллельных дифференциальных плеча 20 и 21, каждое из которых состоит из последовательно включенных управляющих МОПтранзисторов 23 и 24 и нагрузочных

58431

элементов 25 и 26, общие узлы которых являются выходом компаратора 31 и 32. Истоки управляющих МОП-транзисторов- 23 и 24 объединены и подключены к шине 46 земли через генератор 5 22 тока.

Нагрузочные элементы 25 и 26 есть нагрузочные МОП-транзисторы 27 и 28, стоки которых подключень к щине 45 питания, а затворы попарно ю объединены с затворами транзисторов 9 и 10. Затвор транзистора 23 подключен к первому входу .35 компаратора.

Затвор транзистора 24 подключен к 15 истокам двух коммутирующих транзисторов 39 и 40, стоки которых соединены с первым 35 и вторым 36 входами компаратора.

Выход .компаратора 31 подключен к 20стоку транзистора 41, а выход 32 - к стоку транзистора 4. Истоки транзисторов 41 и 42 подключены входам 18 и 17 основного дифференциального каскада соответственно. 25

Затворы транзисторов 39, 41 и 42 соединены с шиной 43 управляющего сигнала, затвор транзистора 40 - с шиной 44.

Рассмотрим работу компаратора на 3G МДП-транзисторах.

Сигналы управления на шинах 43 и .44 обуславливают два режима работы компаратора(см. фиг. 2)- режим автокоррекции (.Ои режим линейного уси- 3S ления(11).

Работа компаратора начинается с режима автокоррекции, когда на шине

43появляется высокий уровень напряженийЧздесь и далее подразумевается абсолютное-значение)а на шине

44- низкий.

Затвор транзистора 24 через открытый транзистор 39 подключается ко входу 35 компаратора.

На оба входа 33 и 34 дополнительного дифференциального каскада подано одно и то же напря жение.

Коммутацией выходов 31 и 32 до- JQ полнительного дифференциального каска да ко входам L7 и 18 основного с помощью открытых транзисторов 41 и 42 компаратор вводится в режим глубокой отрицательной обратной связи (ОС). i 55 Такая отрицательная ОС при одном и том же напряжении на входах 33 и 34 стремится свести к нулю разность напряжений на выходах 31 и 32 компара794 .

тора.возникающую из-за технологически или режимно обусловленной несим 1етрии плеч, компенсируя любую несимметрию усилителя изменением сопротивления нагрузочных МОП-транзисторо 27 и 28.

Действительно, предположим, что из-за разброса технологических параметров пороговое напряжение транзистора 23 больше, чем транзистора 24. В режиме автокорреляции, когда на затворы этих транзисторов входов 33 и 35 подано одно и то же напряжение, проводимость транзистора 23 меньше, чем транзистора 24 и на выходе 31 потенциал устанавливается выше, чем на выходе 32.

Напряжения с выходов 31 и 32 чере открытые.транзисторы 41 и 42 подаютс на входы 17 и 18, уменьшая проводимость транзистора 5 относительно транзистора 6.

Напряжение на выходе 15 превышает напряжение на выходе 16 и через конденсаторы М и }2 передается на затворы 29 и 30 нагрузочных МОП-транзисторов 27 и 28Jстремясь ликвидировать первоначальную несимметрию напряжений на выходах 31 и 32.

Эта же обратная связь удерживает компаратор в устойчивом сбалансированном состоянии в активной области.

Автокорректировка, т.е. выравнивание и симметрирование дифференциальных каскадов, подготавливает, компаратор к режиму линейного усиления .

Режим линейного усиления- начинаеся, когда на шине 43 появляется низкий уровень напряжения, а на 44 высокий. Тем самым вход 34 дополнительного дифференциального каскада отключается от первого входа 35 комIпаратора и через коммутирующий транзистор 40 подключается ко второму входу 36 компаратора.

Дополнительный дифференциальный каскад I9 усиливает разность сигналов, подаваемых на входы 35 и 36 компаратора.

-

В это время транзисторы 41 и 42 выключены и связи между выходами 31 и 32 дополнительного дифференциального каскада, и входами 17 и 18 основного нет, а общее сбалансированное состояние системы сохраняется благодаря хранению напряжения на конденсаторах 37 и 38, Таким образом, благодаря введенным связям и элементам повышается точность компаратора. Формула изобретения Компаратор, содержащий основ1 й и дополнительный дифференциальные каскады, каждый из которых состоит и генератора тока в цепи обратной связи и двух параллельных дифференциаль ных плеч, состоящих из последователь но вкЛоченньггс управляющего МОП-гранзистора и нагрузочного МОП-транз.истора, включенных между генератором тока и шиной питания, вход дополнительного дифференциального каскада соединен с первьм входом компаратора отличающи я тем,что,с целью снижения погрешности компарато Б него введешь первый и второй коиде саторы, первый, второй, третий и чет вертый коммутирующие МОП-транзисторы причем затворы первого и второго МОП транзисторов подключены к первой и второй шинам управляющего сигнала, сток и исток первого коммутирующего МОП-транзистора подключены соответственно к первому и второму входам дополнительного дифференциального каскада, сток и исток второго коммутирующего МОП-транзистора подключены соответственно ко второму входу компаратора и второму входу дополнительного дифференциального каскада, затворы третьего и четвертого коммутирующих МОП-транзисторов подключены к входной шине, сток и исток третьего коммутирующего МОП-транзистора подключены соответственно к первому выходу дополнительного и первому входу основного дифференциального каскадов, сток и исток четвертого коммутирующего МОП-транзистора подключены соответственно ко второму выходу дополнительного и второму входу основного дифференциальных каскадов, а первый и второй конденсаторы рключены между затворами и стоками управляющих МОП-транйисторов основного дифференциального каскада, а затворы нагрузочных МОПтранзисторов основного и дополнительного дифференциальных каскадов попарно объединеш 1., Источники информации, принятые во внимание при экспертизе 1. Патент Франции № 2255746, кл. Н 03 К 3/35, 1975. . 2. Патент США № 3886468, кл. Н 03 К 3/353, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный компаратор на КМОП-транзисторах | 1988 |

|

SU1552366A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Генератор импульсов | 1979 |

|

SU834841A1 |

| ПРЕЦИЗИОННЫЙ КМОП УСИЛИТЕЛЬ | 2005 |

|

RU2310270C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КМОП КОМПАРАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2019913C1 |

| Фотоприемная ячейка | 1989 |

|

SU1619344A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

Авторы

Даты

1981-06-30—Публикация

1979-06-19—Подача