Г7з о о

-си- I-о-,

I I

Si

5 х;

L.TJ

о

00

оо

Ј

N5

Изобретение относится к технике связи и вычислительной технике и может использоваться в системах передачи информации,

Цель изобретения - повышение помехоустойчивости кодека и обеспечение независимости его характеристик от тактовой частоты.

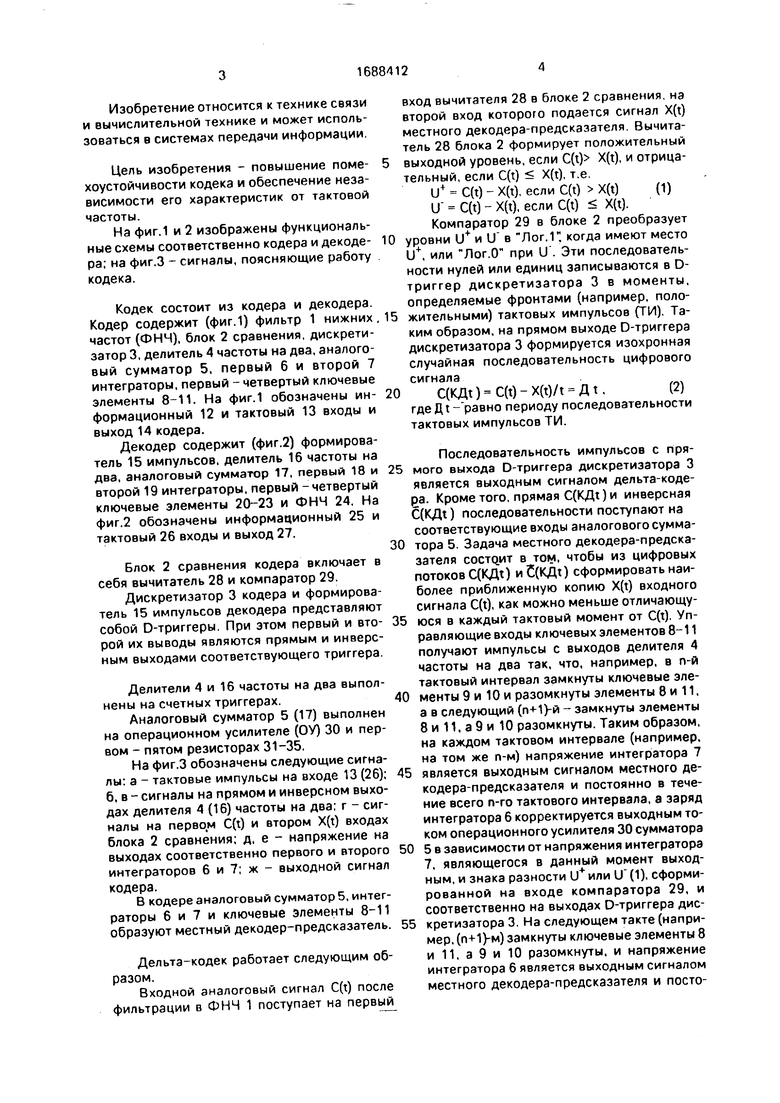

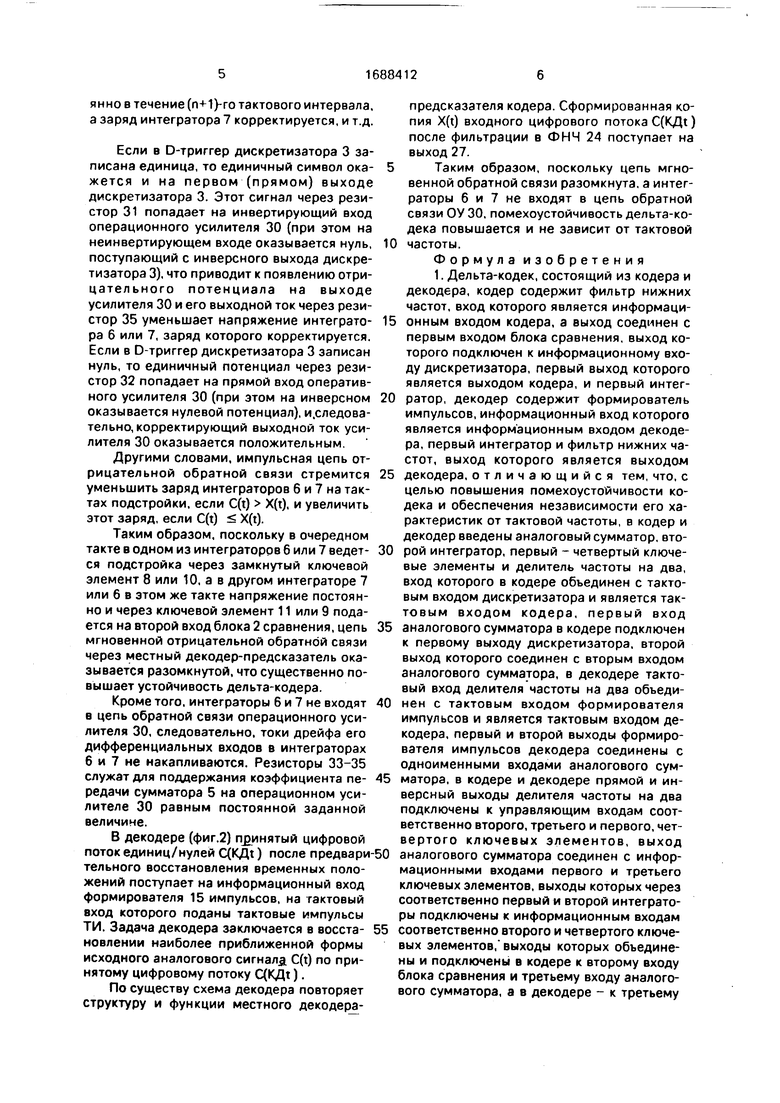

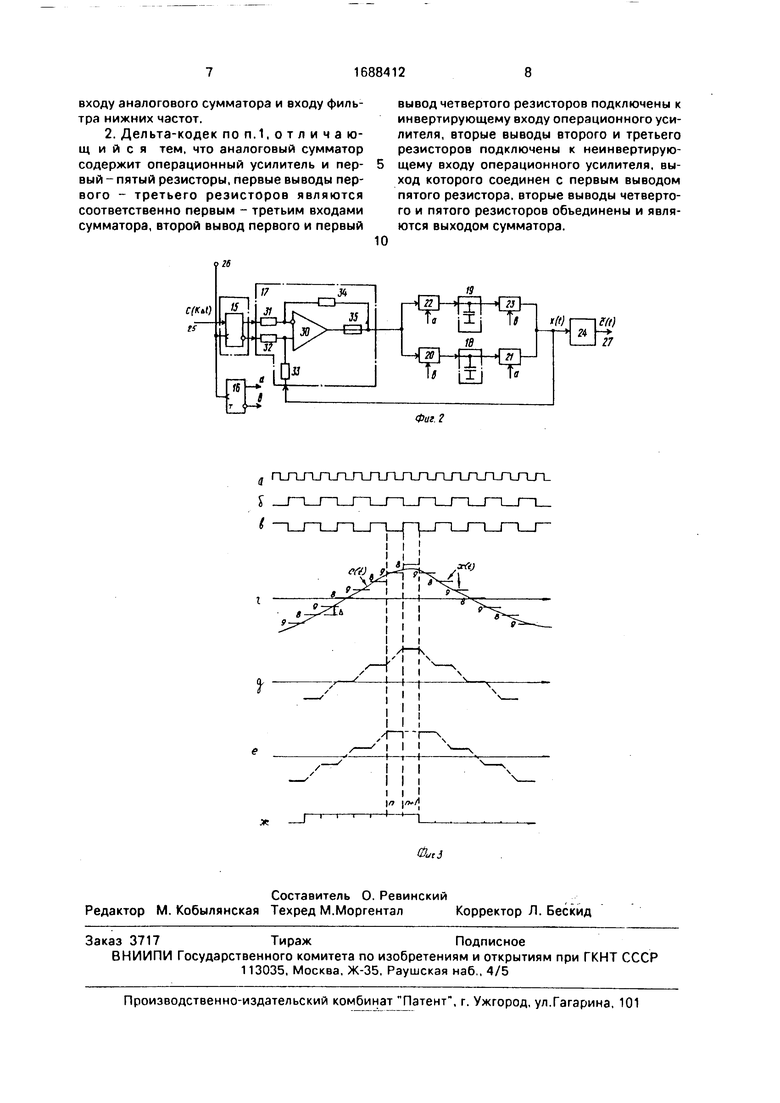

На фиг.1 и 2 изображены функциональные схемы соответственно кодера и декодера; на фиг.З - сигналы, поясняющие работу кодека.

Кодек состоит из кодера и декодера. Кодер содержит (фиг.1) фильтр 1 нижних, частот (ФНЧ), блок 2 сравнения, дискрети- затор 3, делитель 4 частоты на два, аналоговый сумматор 5, первый 6 и второй 7 интеграторы, первый - четвертый ключевые элементы 8-11. На фиг.1 обозначены информационный 12 и тактовый 13 входы и выход 14 кодера.

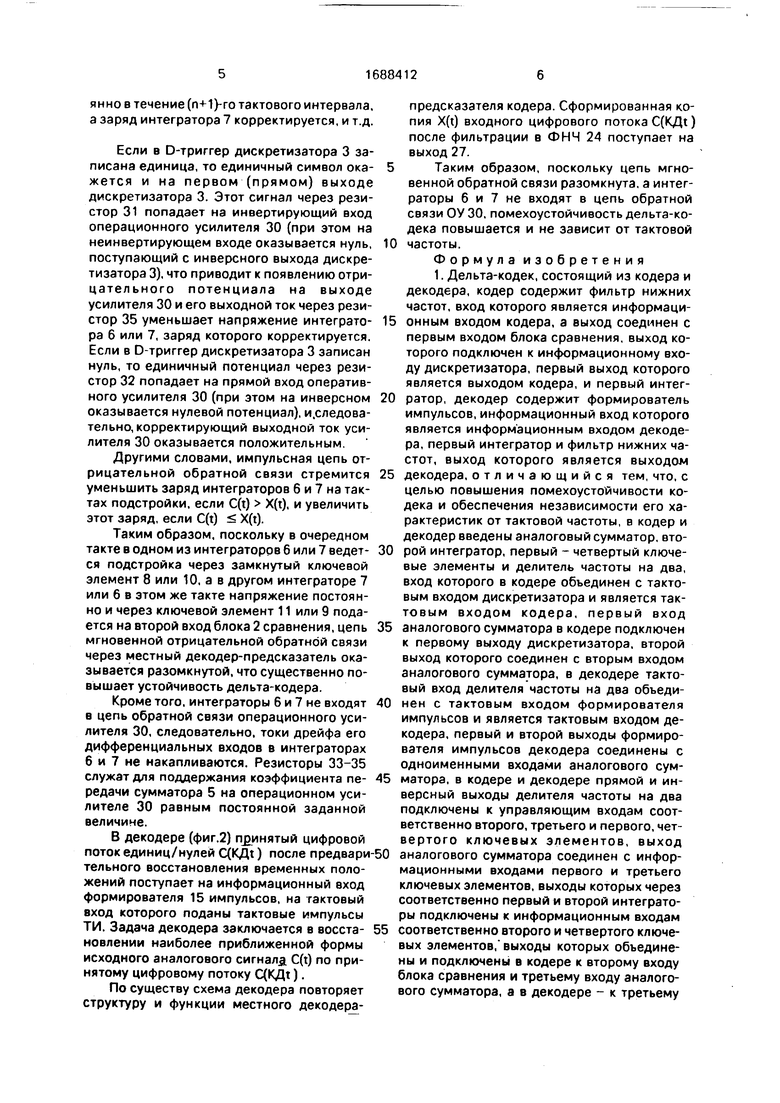

Декодер содержит (фиг.2) формирователь 15 импульсов, делитель 16 частоты на два, аналоговый сумматор 17, первый 18 и второй 19 интеграторы, первый-четвертый ключевые элементы 20-23 и ФНЧ 24, На фиг.2 обозначены информационный 25 и тактовый 26 входы и выход 27.

Блок 2 сравнения кодера включает в себя вычитатель 28 и компаратор 29.

Дискретизатор 3 кодера и формирователь 15 импульсов декодера представляют собой D-триггеры. При этом первый и второй их выводы являются прямым и инверсным выходами соответствующего триггера.

Делители 4 и 16 частоты на два выполнены на счетных триггерах.

Аналоговый сумматор 5 (17) выполнен на операционном усилителе (ОУ) 30 и первом - пятом резисторах 31-35.

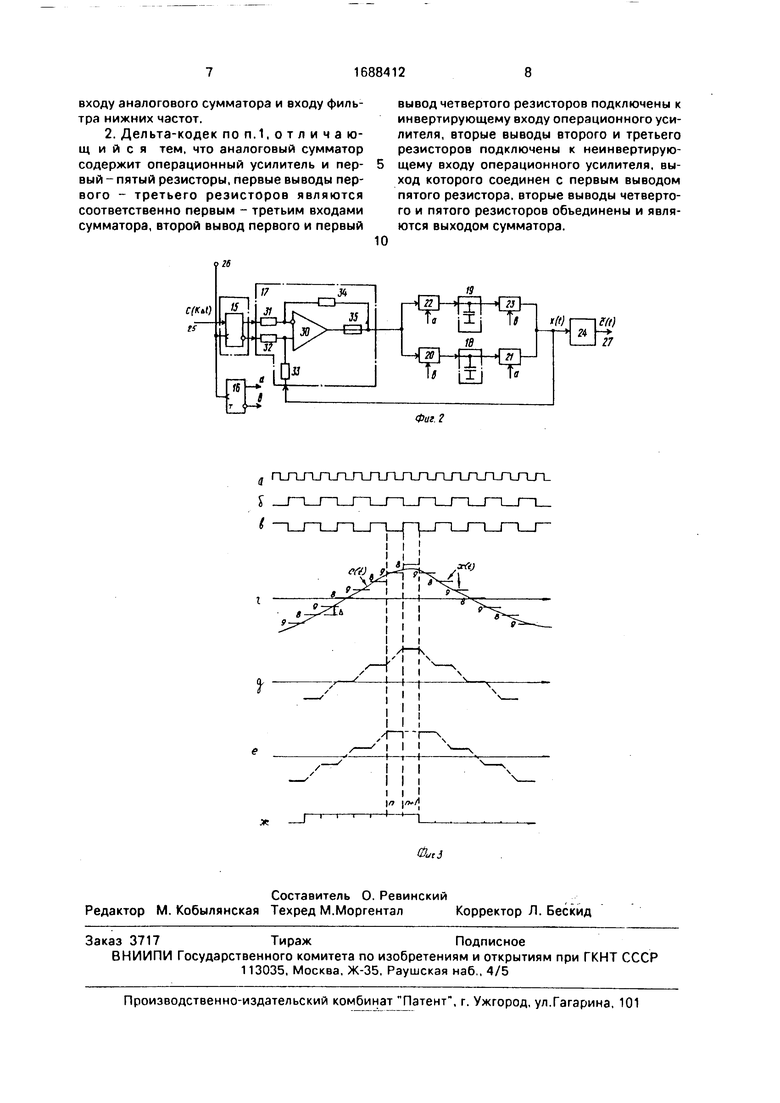

На фиг.З обозначены следующие сигналы: а - тактовые импульсы на входе 13 (26); б, в - сигналы на прямом и инверсном выходах делителя 4 (16) частоты на два; г - сигналы на первом C(t) и втором X(t) входах блока 2 сравнения; д, е - напряжение на выходах соответственно первого и второго интеграторов 6 и 7; ж - выходной сигнал кодера.

В кодере аналоговый сумматор 5, интеграторы 6 и 7 и ключевые элементы 8-11 образуют местный декодер-предсказатель.

Дельта-кодек работает следующим образом.

Входной аналоговый сигнал C(t) после фильтрации в ФНЧ 1 поступает на первый

вход вычитателя 28 в блоке 2 сравнения, на второй вход которого подается сигнал X(t) местного декодера-предсказателя. Вычитатель 28 блока 2 формирует положительный

выходной уровень, если C(t) X(t), и отрицательный, если C(t) X(t), т.е.

U+ C(t) - X(t), если C(t) X(t)(1)

U C(t) - X(t), если C(t) X(t). Компаратор 29 в блоке 2 преобразует

уровни U и U в Лог.1 когда имеют место U+, или Лог.О при U . Эти последовательности нулей или единиц записываются в D- триггер дискретизатора 3 в моменты, определяемые фронтами (например, положительными) тактовых импульсов (ТИ). Таким образом, на прямом выходе D-триггера дискретизатора 3 формируется изохронная случайная последовательность цифрового сигнала

С((г)-Х(г)Л Дт.(2)

где Д t - равно периоду последовательности тактовых импульсов ТИ.

Последовательность импульсов с прямого выхода D-триггера дискретизатора 3 является выходным сигналом дельта-кодера. Кроме того, прямая С(КДх) и инверсная С(КДО последовательности поступают на соответствующие входы аналогового сумматора 5. Задача местного декодера-предсказателя COCTQHT в том, чтобы из цифровых потоков С(КД1) иС(КДт) сформировать наиболее приближенную копию X(t) входного сигнала C(t), как можно меньше отличающуюся в каждый тактовый момент от С(х). Управляющие входы ключевых элементов 8-11 получают импульсы с выходов делителя 4 частоты на два так, что, например, в п-й тактовый интервал замкнуты ключевые элементы 9 и 10 и разомкнуты элементы 8 и 11, а в следующий (п+1)-й - замкнуты элементы 8 и 11, а 9 и 10 разомкнуты. Таким образом, на каждом тактовом интервале (например, на том же n-м) напряжение интегратора 7

является выходным сигналом местного декодера-предсказателя и постоянно в течение всего n-го тактового интервала, а заряд интегратора 6 корректируется выходным током операционного усилителя 30 сумматора

0 5 в зависимости от напряжения интегратора 7, являющегося в данный момент выходным, и знака разности U или U (1), сформированной на входе компаратора 29, и соответственно на выходах D-триггера дис5 кретизатора 3. На следующем такте (например, (п+1)-м) замкнуты ключевые элементы 8 и 11, а 9 и 10 разомкнуты, и напряжение интегратора 6 является выходным сигналом местного декодера-предсказателя и постоянно в течение (п+1)-го тактового интервала, а заряд интегратора 7 корректируется, и т.д.

Если в D-триггер дискретизатора 3 записана единица, то единичный символ ока- жется и на первом (прямом) выходе дискретизатора 3. Этот сигнал через резистор 31 попадает на инвертирующий вход операционного усилителя 30 (при этом на неинвертирующем входе оказывается нуль, поступающий с инверсного выхода дискретизатора 3), что приводит к появлению отри- цательного потенциала на выходе усилителя 30 и его выходной ток через резистор 35 уменьшает напряжение интеграто- ра 6 или 7, заряд которого корректируется. Если в D-триггер дискретизатора 3 записан нуль, то единичный потенциал через резистор 32 попадает на прямой вход оперативного усилителя 30 (при этом на инверсном оказывается нулевой потенциал), и.следова- тельно, корректирующий выходной ток усилителя 30 оказывается положительным.

Другими словами, импульсная цепь отрицательной обратной связи стремится уменьшить заряд интеграторов 6 и 7 на тактах подстройки, если C(t) X(t), и увеличить этот заряд, если C(t) X(t).

Таким образом, поскольку в очередном такте в одном из интеграторов 6 или 7 ведет- ся подстройка через замкнутый ключевой элемент 8 или 10, а в другом интеграторе 7 или 6 в этом же такте напряжение постоянно и через ключевой элемент 11 или 9 подается на второй вход блока 2 сравнения, цепь мгновенной отрицательной обратной связи через местный декодер-предсказатель оказывается разомкнутой, что существенно повышает устойчивость дельта-кодера.

Кроме того, интеграторы 6 и 7 не входят в цепь обратной связи операционного усилителя 30, следовательно, токи дрейфа его дифференциальных входов в интеграторах 6 и 7 не накапливаются. Резисторы 33-35 служат для поддержания коэффициента пе- редачи сумматора 5 на операционном усилителе 30 равным постоянной заданной величине.

В декодере (фиг.2) принятый цифровой поток единиц/нулей С(КД1) после предвари тельного восстановления временных положений поступает на информационный вход формирователя 15 импульсов, на тактовый вход которого поданы тактовые импульсы ТИ. Задача декодера заключается в восста- новлении наиболее приближенной формы исходного аналогового сигнала C(t) по принятому цифровому потоку С(КДт).

По существу схема декодера повторяет структуру и функции местного декодерапредсказателя кодера. Сформированная копия X(t) входного цифрового потока С(КД1) после фильтрации в ФНЧ 24 поступает на выход 27.

Таким образом, поскольку цепь мгновенной обратной связи разомкнута, а интеграторы б и 7 не входят в цепь обратной связи ОУ 30, помехоустойчивость дельта-кодека повышается и не зависит от тактовой частоты.

Формула изобретения 1. Дельта-кодек, состоящий из кодера и декодера, кодер содержит фильтр нижних частот, вход которого является информационным входом кодера, а выход соединен с первым входом блока сравнения, выход которого подключен к информационному входу дискретизатора, первый выход которого является выходом кодера, и первый интегратор, декодер содержит формирователь импульсов, информационный вход которого является информационным входом декодера, первый интегратор и фильтр нижних частот, выход которого является выходом декодера, отличающийся тем, что, с целью повышения помехоустойчивости кодека и обеспечения независимости его характеристик от тактовой частоты, в кодер и декодер введены аналоговый сумматор, второй интегратор, первый - четвертый ключевые элементы и делитель частоты на два, вход которого в кодере объединен с тактовым входом дискретизатора и является тактовым входом кодера, первый вход аналогового сумматора в кодере подключен к первому выходу дискретизатора, второй выход которого соединен с вторым входом аналогового сумматора, в декодере тактовый вход делителя частоты на два объединен с тактовым входом формирователя импульсов и является тактовым входом декодера, первый и второй выходы формирователя импульсов декодера соединены с одноименными входами аналогового сумматора, в кодере и декодере прямой и инверсный выходы делителя частоты на два подключены к управляющим входам соответственно второго, третьего и первого, чет- вертого ключевых элементов, выход аналогового сумматора соединен с информационными входами первого и третьего ключевых элементов, выходы которых через соответственно первый и второй интеграторы подключены к информационным входам соответственно второго и четвертого ключевых элементов, выходы которых объединены и подключены в кодере к второму входу блока сравнения и третьему входу аналогового сумматора, а в декодере - к третьему

входу аналогового сумматора и входу фильтра нижних частот.

2. Дельта-кодек по п. 1. о т л и ч а ю- щ и и с я тем, что аналоговый сумматор содержит операционный усилитель и первый - пятый резисторы, первые выводы первого - третьего резисторов являются соответственно первым - третьим входами сумматора, второй вывод первого и первый

0

вывод четвертого резисторов подключены к инвертирующему входу операционного усилителя, вторые выводы второго и третьего резисторов подключены к неинвертирующему входу операционного усилителя, выход которого соединен с первым выводом пятого резистора, вторые выводы четвертого и пятого резисторов объединены и являются выходом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ДЕЛЬТА КОДЕК | 2013 |

|

RU2530294C1 |

| ДЕЛЬТА-КОДЕК | 1998 |

|

RU2172554C2 |

| Кодек системы связи | 1983 |

|

SU1150770A1 |

| Дельта-декодер | 1986 |

|

SU1381714A1 |

| Дельта-сигма-кодер | 1988 |

|

SU1527712A1 |

| Дельта-кодер | 1988 |

|

SU1605310A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Устройство для измерения шума квантования дельта-кодека | 1987 |

|

SU1450121A1 |

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО РАДИОСВЯЗИ И МНОГОРЕЖИМНЫЙ СОТОВЫЙ РАДИОТЕЛЕФОН | 1993 |

|

RU2128886C1 |

| Устройство для транскодирования сигналов с адаптивной дельта-модуляцией и импульсно-кодовой модуляцией | 1990 |

|

SU1805547A1 |

Изобретение относится к технике связи и вычислительной технике и позволяет повысить помехоустойчивость кодека и обеспечить независимость его характеристик от тактовой частоты. Дельта-кодек состоит из кодера и декодера. Кодер содержит фильтр 1 нижних частот, блок 2 сравнения, дискре- тизатор 3 и интегратор 6. Благодаря введению делителя 4 частоты на два, аналогового сумматора 5, интегратора 7 и ключевых элементов 8-11 обеспечивается размыкание цепи мгновенной обратной связи и исключение интеграторов 6 и 7 из цепи обратной связи операционного усилителя 30 сумматора 5. 1 з.п. ф-лы, 3 ил.

njnjTJOJTjajiruT-njajTJTJ jnjTj-L

Фиг 2

/нл-к

| Патент США I 4433311, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Дельта-модуляция | |||

| Теория и применение | |||

| /Под ред | |||

| М.Д.Бенедиктова, - М.: Связь, 1976, с | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-10-30—Публикация

1989-08-07—Подача