ff)

Изобретение относится к вычислительной технике и технике связи и может быть использовано в цифровых системах связи, измерений, те,чеме- ханики,

Цель изобретения - повышение точности кодирования входного сигнала.

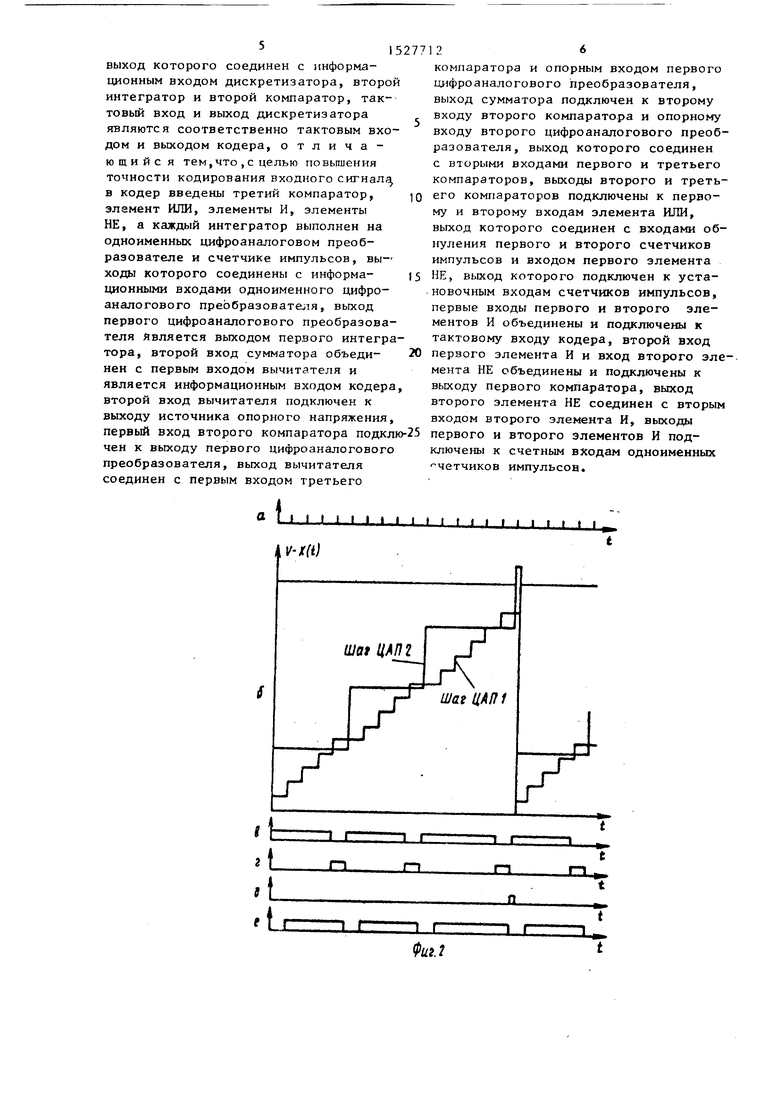

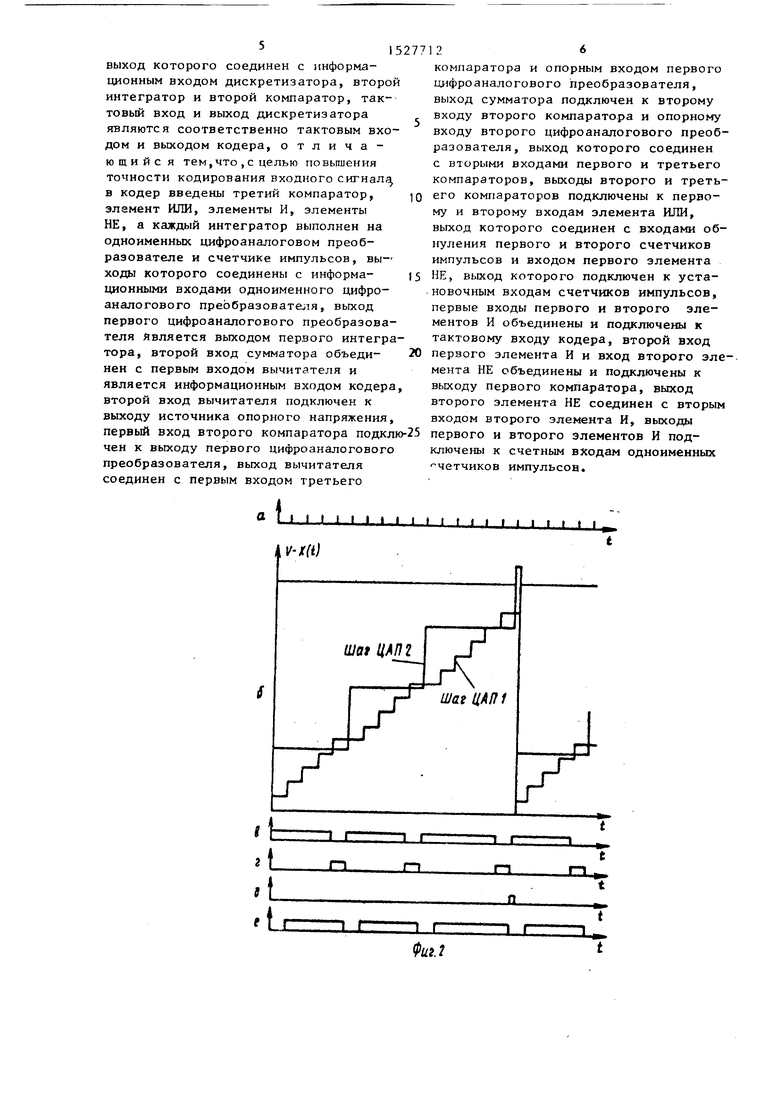

На фиг.1 приведена функциональная схема дельта-сигма-кодера; на фиг.2 - временные диаграмьл его работы.

Дельта-сигма-кодер содержит вы- читатель 1, сумматор 2, источник 3 опортюго напряже} ия, первый и второй элемента И А и 5 и первый и второй элементы НЕ 6 и 7, элемент ИПИ 8, дискретизатор 9, первый - третий компараторы 10 - 12 и первый и второй интеграторы 13 и 14, каждый из которых включает в себя счетчик 15 импульсов и цифроаналоговый преобразователь (ЦАП) 16. На фиг.1 обозначены информационньм и тактовый входы 17 и 18.

Дельта-сигма-кодер работает еле- дующим образом

На вход 18 приходят тактовые импульсы (фиГо2а), входной сигнал X(t) поступает с входа 17 на вычита- тель I и сумматор 2, которые предназ начены .цля формирований размера шага

первого 16.1 и второго 16.2 ЦАП соответственно (фиг.26). В зависимости от величины входного напряжения на KOhiiiapaTope 10 на его выходе вырабатывается сигнал (фиг.2в), а на выходе второго элемента НЕ 7 - инверсньш синал (фиг.2г), которые дискретизиру- ются во времени первым и вторым эле ментами И 4 и 5 и далее, в противо- фазе, управляют первым 15.1 и вторым 15с2 счетчиками.

.Пля удобства рассмотрения предполжим, что на вход 17 кодера поступает положительное напряжение X(t), нахо- дящееся в пределах О X(t) V и не изменяющееся во времени. В этом случ сигнал на выходе первого ЦАГГ 16.1 меньше сигнала на выходе второго 11ДП 16.2 и на выходе Компаратора 10 появляется логическая 1, которая в hWHenT прихода стробирующего импульса изменяет текущее состояние первого ЦДП 16.1 на единицу. В случае, если напряжение на выходе первого ЦАП 16.1 по-прежнему меньше напряжения на выходе второго ЦАП 16.2, компаратор 10 остается в том же состоянии. В противном случае на выходе компара

с

5 0

5

о

Q

5

тора 10 появляется О, который далее инвертируется элементом НЕ 7 и через второй элемент И 5 изменяет с.- стояние второго счетчика 15.2 и второго ЦАП 16.2.

Таким образом осуществляется отсчет шагов на выходе первого ЦАП 16.1, размер которых пропорционален разности V - X(t), относительно шагов на выходе второго ЦАП 16.2, размер которых пропорционален сумме V + + X(t) с тем же коэффициентом пропорциональности, причем остаток от каждого предыдущего отсчета переносится на следующий отсчет. Непрерывность отслеживания определяется разрядностью первого и второго ЦАП 16, т.е. временем прохождения полного цикла от начала счета до- сброса.

Второй II и третий 12 компараторы, элемент ИЛИ 8 и первый элемент НЕ 6 служат для формирования сигнала сброса (фиг.2д), которьш вырабатывается в случае, когда сигнал одного из ЦАП 16 превысит соответствующий опорный уровень для первого ЦАП 16.1 V - X(t) или для второго ЦАП 16.2 V + X(t). При этом не происходит разрыв текущей пачки, что могло бы привести к дополнительной ошибке преобразования.

Дискретизатор 9 служит для формиро вания выходной цифровой последовательности кодера (фиг.2е).

Таким образом происходит преобразование аналогового напряжения в цифровой вид. Функции интеграторов 13 и 14 выполняют соответственно первые счетчик 15.1 и ЦАП 16.1 и вторые счетчик 15.2 и ЦАП 16.2. Следовательно, точность преобразования целиком определяется разрядностью счетчиков 15 и ЦАП 16. Для простоты рассмотрения на временных диаграммах (фиг.2) проиллюстрированы варианты с четырехразрядными счетчиками 15 и ЦАП 16. Практически достаточно высокие качественные характеристики достигаются при применении 8-12 и более разрядных ЦАПо

Формула изобретения

Дельта-сигма-кодер, содержащий вычислитель, источник опорного напряжения, выход которого соединен с первым входом сумматора, первый интегратор, выход которого подключен к первому входу первого компаратора.

515

выход которого соединен с информационным входом дискретизатора, второй интегратор и второй компаратор, тактовый вход и выход дискретизатора являются соответственно тактовым входом и выходом кодера, отличающийся тем,что , с целью повьпиения точности кодирования входного сигналу в кодер введены третий компаратор, элемент ИЛИ, элементы И, элементы НЕ, а каждый интегратор выполнен на одноименных цифроаналоговом преобразователе и счетчике импульсов, вы- ходы которого соединены с информа- дноиными входами одноименного цифро- аналогового преобразователя, выход первого цифроанапогового преобразователя йвляется выходом первого интегратора, второй вход сумматора объеди- нен с первым входом вычитателя и является информационным входом кодера второй вход вычитателя подключен к выходу источника опорного напряжения, первый вход второго компаратора подкл чен к выходу первого цифроаналогового преобразователя, выход вычитателя соединен с первым входом третьего

компаратора и опорным входом первого цифроаналогового преобразователя, выход сумматора подключен к второму входу второго компаратора и опорному входу второго цифроаналогового преобразователя, выход которого соединен с вторыми входами первого и третьего компараторов, выходы второго и третьего компараторов подключены к первому и второму входам элемента ИЛИ, выход которого соединен с входами об- 1гуления первого и второго счетчиков импульсов и входом первого элемента НЕ, выход которого подключен к установочным входам счетчиков импульсов, первые входы первого и второго элементов И объединены и подключены к тактовому входу кодера, второй вход первого элемента И и вход второго элемента НЕ объединены и подключены к выходу первого компаратора, выход второго элемента НЕ соединен с вторым входом второго элемента И, выходы первого и второго элементов И подключены к счетным входам одноименных четчиков импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-сигма-кодер | 1989 |

|

SU1656684A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| Дельта-кодек | 1989 |

|

SU1688412A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Аналого-цифровой интегратор | 1979 |

|

SU842868A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| СИГМА-ДЕЛЬТА-АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2145149C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| УСТРОЙСТВО И СПОСОБ ПРЕОБРАЗОВАНИЯ АНАЛОГОВОГО СИГНАЛА В ЦИФРОВУЮ ФОРМУ, УСТРОЙСТВО И СПОСОБ ПРЕОБРАЗОВАНИЯ МНОЖЕСТВА ДВОИЧНО-КОДИРОВАННЫХ ЧИСЛОВЫХ ОТСЧЕТОВ СИГНАЛА В АНАЛОГОВЫЙ СИГНАЛ | 1994 |

|

RU2159505C2 |

| Дельта-модулятор | 1988 |

|

SU1658383A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в цифровых системах связи, измерений, телемеханики позволяет повысить точность кодирования входного сигнала. Дельта-сигма-кодер содержит вычитатель 1, сумматор 2, источник 3 опорного напряжения, дискретизатор 9, компараторы 10, 11 и интеграторы 13, 14. Благодаря введению элементов И 4, 5, элементов НЕ 6, 7, элемента ИЛИ 8, компаратора 12 и выполнению каждого из интеграторов 13, 14 на счетчике 15 импульсов и цифроаналоговом преобразователе 16 точность кодирования определяется разрядностью счетчиков 15 и преобразователей 16. 2 ил.

1

1 ±

I I I I t 1 1 I I I I I I

Авторы

Даты

1989-12-07—Публикация

1988-02-02—Подача