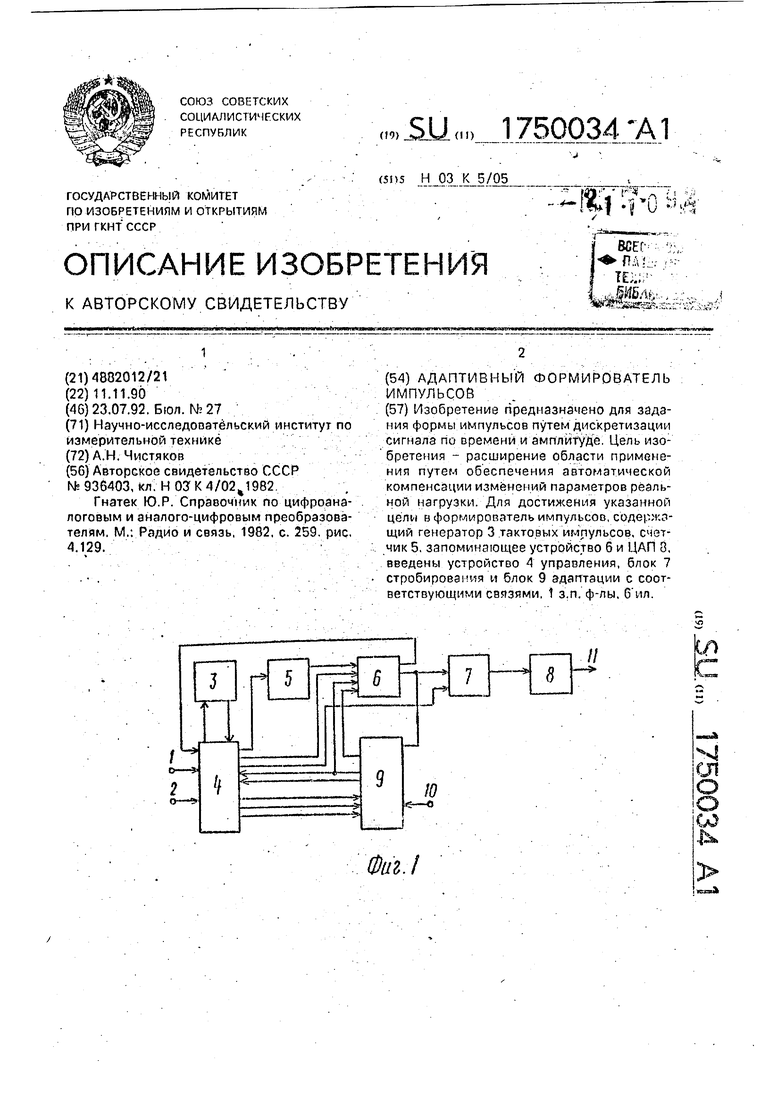

Фиг. I

Изобретение относится к радиотехнике и импульсной технике и предназначено для задания формы импульсов.

Цель изобретения - расширение области применения путем обеспечения автоматической компенсации изменений параметров реальной нагрузки в процессе эксплуатации.

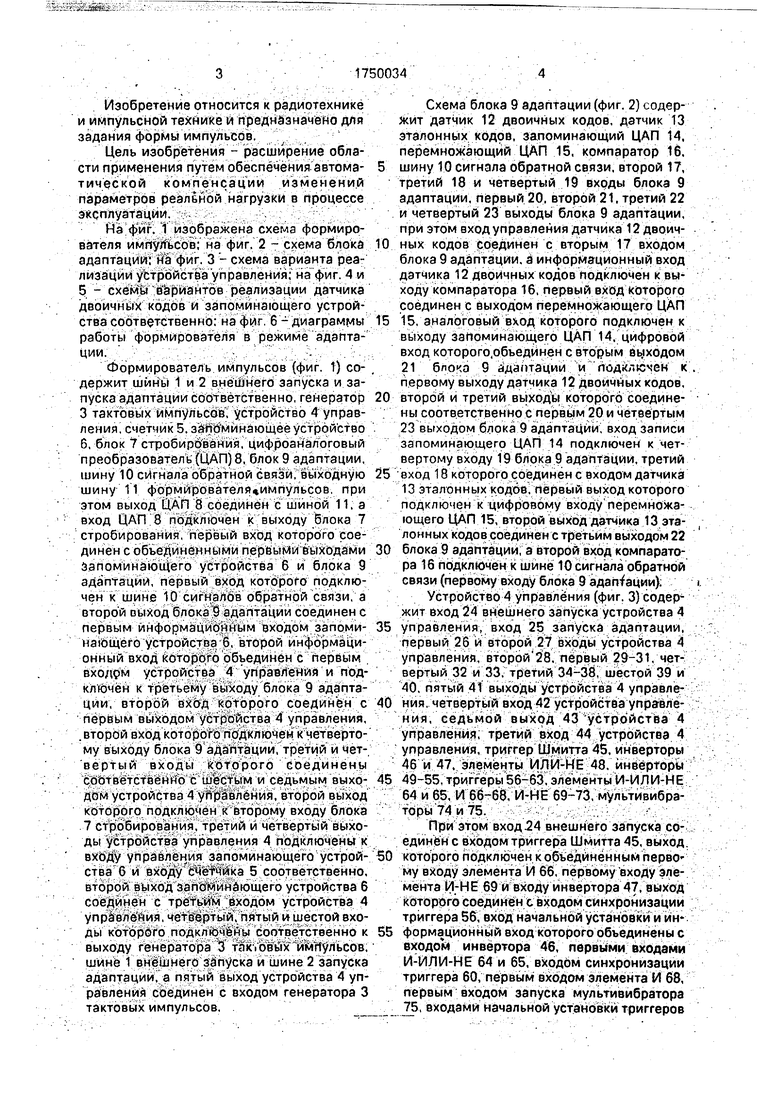

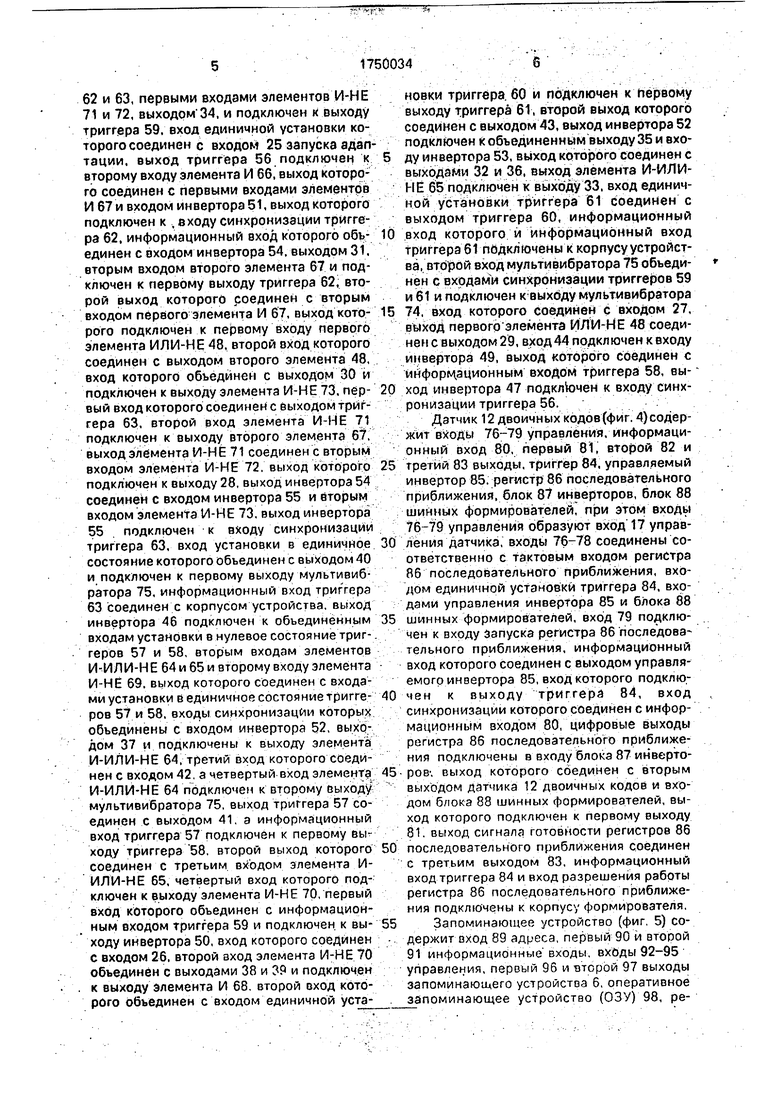

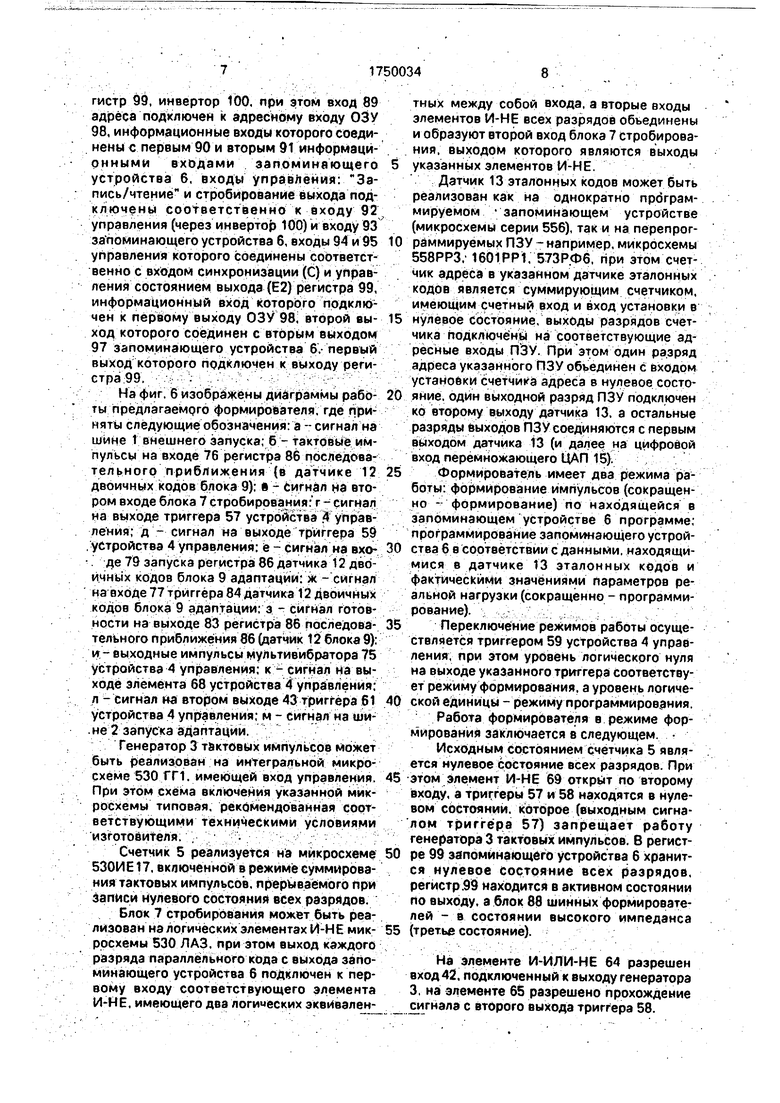

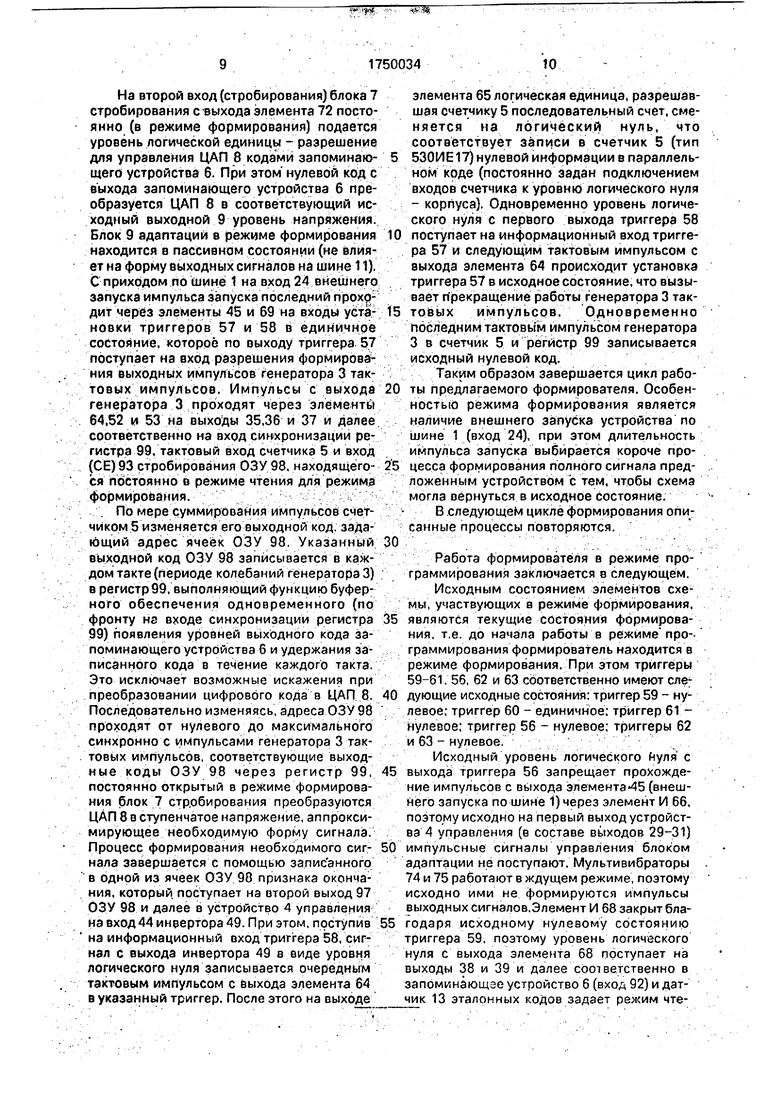

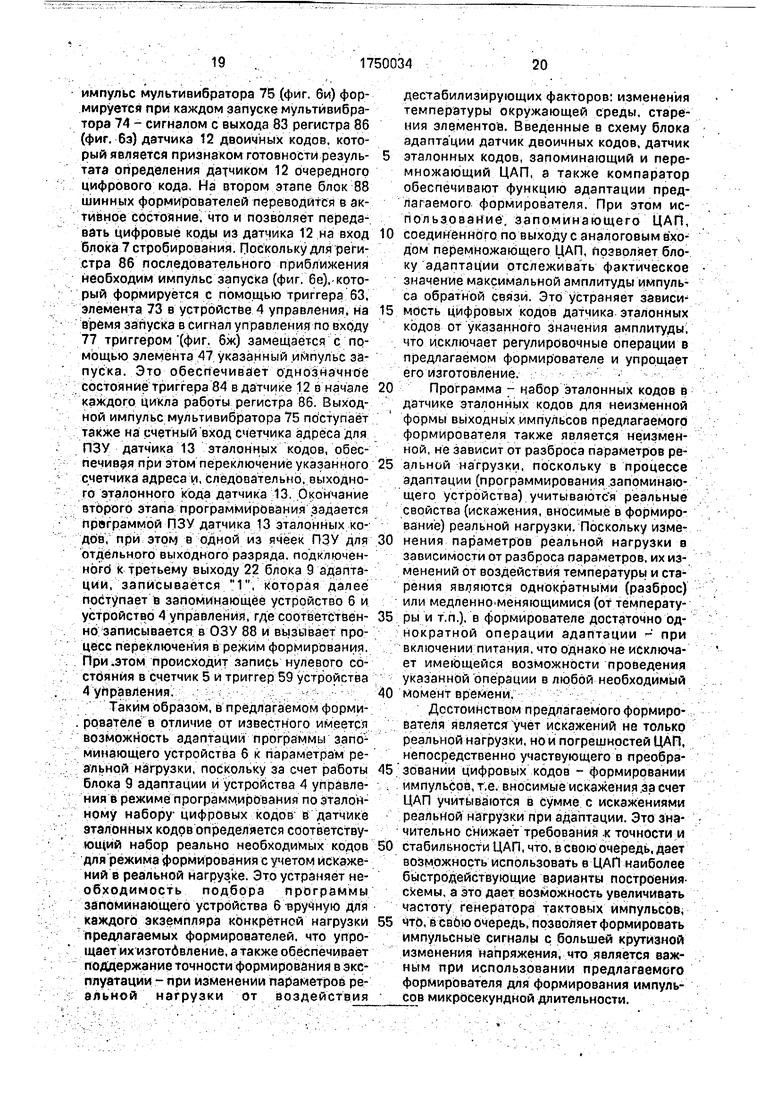

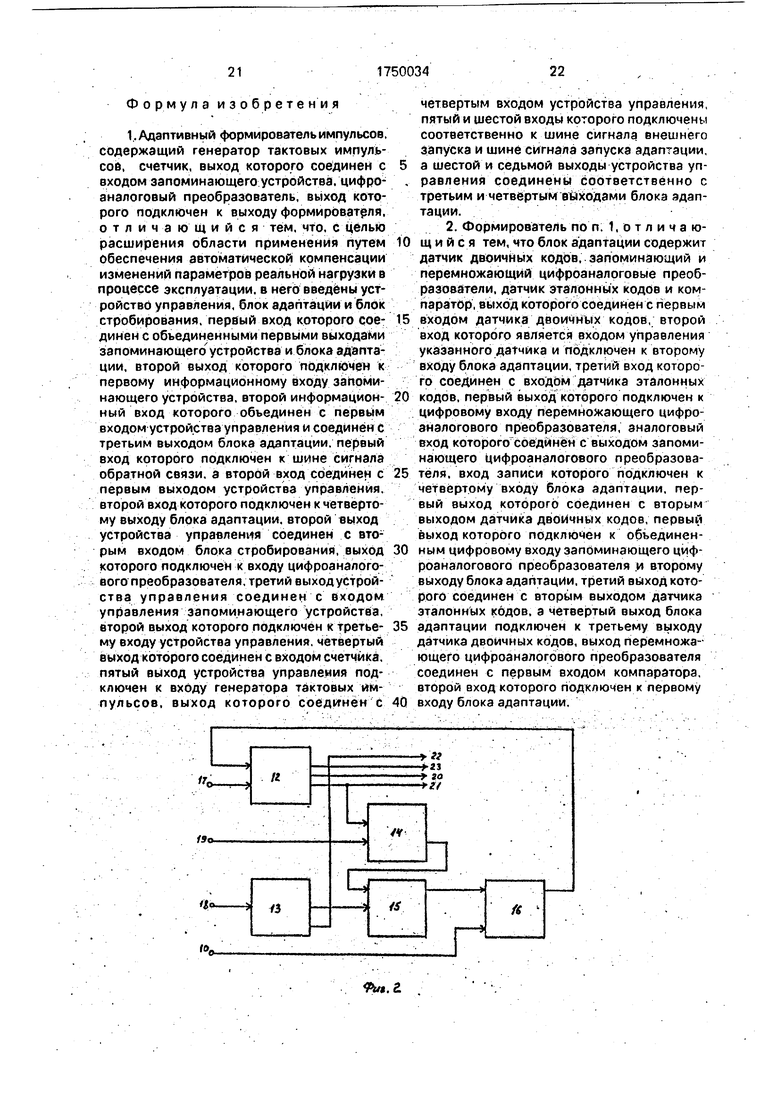

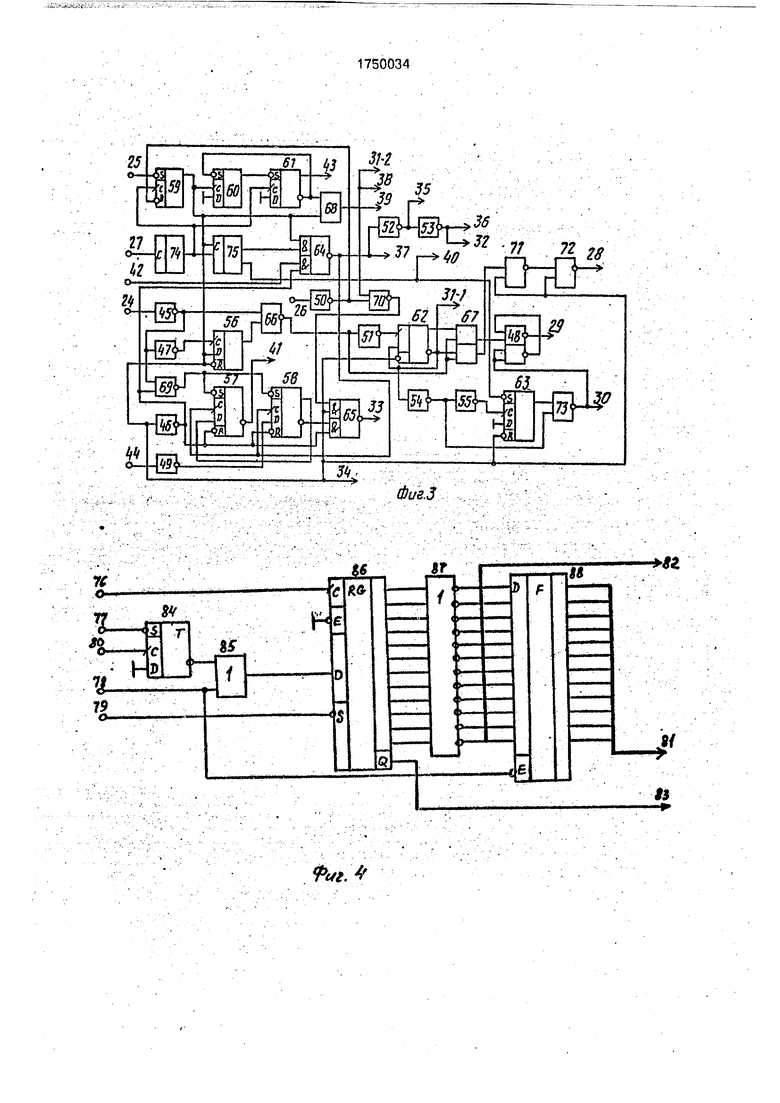

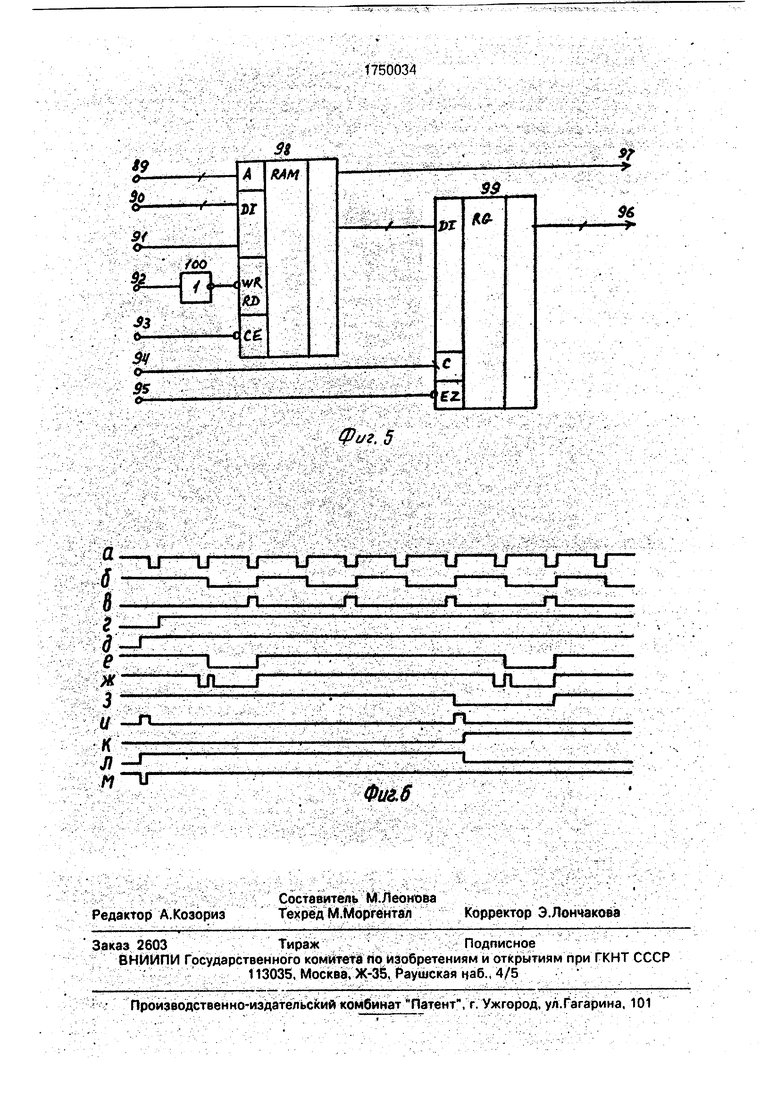

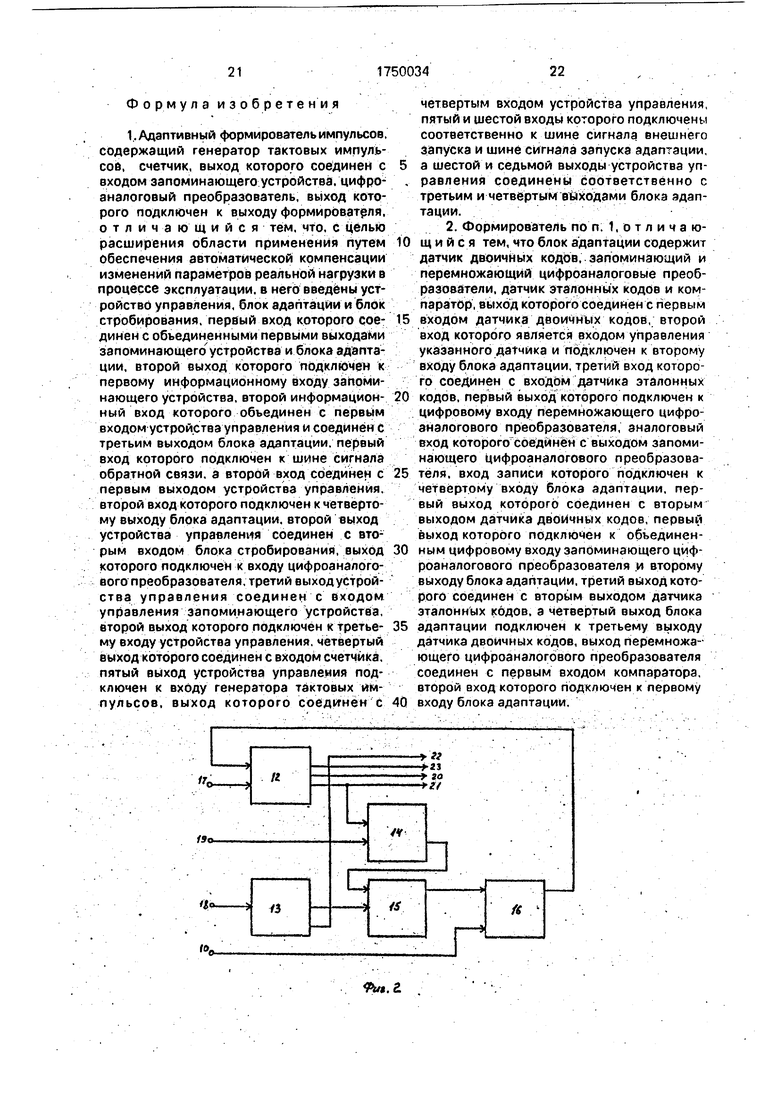

На фиг. 1 изображена схема формирователя импульсов; на фиг. 2 - схема блока адаптации: на фиг. 3 - схема варианта реализации устройства управления; на фиг 4 и 5 - схемы вариантов реализации датчика двоичных кодов и запоминающего устройства соответственно: на фиг 6 - диаграммы работы формирователя в режиме адаптации.

Формирователь импульсов (фиг 1) содержит шины 1 и 2 внешнего запуска и запуска адаптации соответственно, генератор 3 тактовых импульсов, устройство 4 управления счетчик 5, залбминающее устройство б, блок 7 стробирования, цифроаналоговый преобразователь (ЦАП) 8, блок 9 адаптации, шину 10 сигнала обратной связи, выходную шину 11 формирователячимпульсов при этом выход ЦАП 8 соединен с шиной 11. а вход ЦАП 8 подключен к выходу блока 7 стробирования первый вход которого соединен с объединенными первыми выходами Запоминающего устройства 6 и блока 9 адаптации, первый вход которого подключен к шине 10 сигналов обратной связи, а второй выход блока S адаптации соединен с первым информационным входом запоминающего устройства 6, второй информационный вход которого объединен с первым входом устройства 4 управления и подключен к третьему выходу блока 9 адаптации, второй вход которого соединен с первым выходом устройства 4 управления, .второй вход которого подключен к четвертому выходу блока 9 адаптации, третий и четвертый входы которого соединены соответственно с шестым и седьмым выходом устройства 4 управления, второй выход которого подключен к второму входу блока 7 стробирования, третий и четвертый выходы устройства управления 4 подключены к входу управления запоминающего устройства б и входу ечетЧйка 5 соответственно, второй выход запоминающего устройства 6 соединен с третьем входом устройства 4 управления, четвертый, пятый и шестой входы которого подключейы соответственно к выходу генератора 3 так.овых импульсов, шине 1 внешнего запуска и шине 2 запуска адаптации, а пятый выход устройства 4 управления соединен с входом генератора 3 тактовых импульсов.

Схема блока 9 адаптации (фиг. 2) содержит датчик 12 двоичных кодов, датчик 13 эталонных кодов, запоминающий ЦАП 14, перемножающий ЦАП 15. компаратор 16.

шину 10 сигнала обратной связи, второй 17, третий 18 и четвертый 19 входы блока 9 адаптации, первый 20, второй 21. третий 22 и четвертый 23 выходы блока 9 адаптации, при этом вход управления датчика 12 двоичных кодов соединен с вторым 17 входом блока 9 адаптации, а информационный вход датчика 12 двоичных кодов подключен к выходу компаратора 16, первый вход которого соединен с выходом перемножающего ЦАП

15, аналоговый вход которого подключен к выходу запоминающего ЦАП 14. цифровой вход которого.обьединен с вторым выходом 21 блока 9 адаптации и .юхен к . первому выходу датчика 12 двоичных кодов,

второй и третий выходы которого соединены соответственно с первым 20 и четвертым 23 выходом блока 9 адаптации вход записи запоминающего ЦАП 14 подключен к четвертому входу 19 блока 9 адаптации, третий

вход 18 которого соединен с входом датчика 13 эталонных кодов, первый выход которого подключен к цифровому входу перемножающего ЦАП 15, второй выход датчика 13 эталонных кодов соединен с третьим выходом 22

блока 9 адаптации, а второй вход компаратора 16 подключен к шине 10 сигнала обратной связи (первому входу блока 9 адаптации). i

Устройство 4 управления (фиг. 3) содержит вход 24 внешнего запуска устройства 4

управления, вход 25 запуска адаптации, первый 26 и второй 27 входы устройства 4 управления, второй 28. первый 29-31, четвертый 32 и 33, третий 34-38, шестой 39 и 40, пятый 41 выходы устройства 4 управления четвертый вход 42 устройства управления, седьмой выход 43 устройства 4 управления, третий вход 44 устройства 4 управления, триггер Шмитта 45, инверторы 46 и 47, элементы ИЛИ-НЕ 48. инверторы

49-55, триггеры 56-63, элементы И-ИЛИ-НЕ 64 и 65, И 66-68, И-НЕ 69-73, мультивибраторы 74 и 75.

При этом вход .24 внешнего запуска соединён с входом триггера Шмитта 45, выход

которого подключен к объединенным первому входу элемента И 66, первому входу элемента И-НЕ 69 и входу инвертора 47, выход которого соединен с входом синхронизации триггера 56, вход начальной установки и ин

5 формационный вход которого объединены с входом инвертора 46, первыми входами И-ИЛИ-НЕ 64 и 65, входом синхронизации триггера 60, первым входом элемента И 68, первым входом запуска мультивибратора

jf5, входами начальной установки триггеров

62и 63, первыми входами элементов И-НЕ 71 и 72, выходом 34, и подключен к выходу триггера 59, вход единичной установки которого соединен с входом 25 запуска адаптации, выход триггера 56 подключен к второму входу элемента И 66, выход которого соединен с первыми входами элементов

И 67 и входом инвертора 51, выход которого подключен к , входу синхронизации триггера 62, информационный вход которого объ- единен с входом инвертора 54, выходом 31, вторым входом второго элемента 67 и подключен к первому выходу триггера 62, второй выход которого соединен с вторым входом первого элемента И 67, выход кото- рого подключен к первому входу первого элемента И Л И-НЕ 48, второй вход которого соединен с выходом второго элемента 48, вход которого объединен с выходом 30 и подключен к выходу элемента И-НЕ 73, пер- вый вход которого соединен с выходом триггера 63, второй вход элемента И-НЕ 71 подключен к выходу второго элемента 67, выход элемента И-НЕ 71 соединен с вторым входом элемента И-НЕ 72. выход которого подключен к выходу 28, выход инвертора 54 соединен с входом инвертора 55 и вторым входом элемента И-НЕ 73, выход инвертора 55 подключен к входу синхронизации триггера 63, вход установки в единичное состояние которого объединен с выходом 40 и подключен к первому выходу мультивибратора 75, информационный вход триггера

63соединен с корпусом устройства, выход инвертора 46 подключен к объединенным входам установки в нулевое состояние триггеров 57 и 58, вторым входам элементов И-ИЛИ-НЕ 64 и 65 и второму входу элемента И-НЕ 69. выход которого соединен с входами установки в единичное состояние тригге- ров 57 и 58, входы синхронизации которых объединены с входом инвертора 52, выходом 37 и подключены к выходу элемента И-ИЛИ-НЕ 64, третий вход которого соединен с входом 42 а четвертый вход элемента И-ИЛИ-НЕ 64 подключен к второму выходу мультивибратора 75, выход триггера 57 соединен с выходом 41, а информационный вход триггера 57 подключен к первому выходу триггера 58, второй выход которого соединен с третьим входом элемента И- ИЛИ-НЕ 65, четвертый вход которого подключен к выходу элемента И-НЕ 70, первый вход которого объединен с информационным входом триггера 59 и подключен к вы- ходу инвертора 50, вход которого соединен с входом 26, второй вход элемента И-НЕ 70 объединен с выходами 38 и 39 и подключен

к выходу элемента И 68, второй вход которого объединен с входом единичной установки триггера 60 и подключен к первому выходу триггера 61, второй выход которого соединен с выходом 43, выход инвертора 52 подключен к объединенным выходу 35 и входу инвертора 53, выход которого соединен с выходами 32 и 36, выход элемента И-ИЛИ- НЕ 65 подключен к выходу 33, вход единичной установки триггера 61 соединен с выходом триггера 60, информационный вход которого и информационный вход триггера 61 подключены к корпусу устройства, второй вход мультивибратора 75 объеди- нен с входами синхронизации триггеров 59 и 61 и подключен к выходу мультивибратора 74, вход которого соединен с входом 27, выход первого элемента ИЛИ-НЕ 48 соединен с выходом 29, вход 44 подключен к входу инвертора 49, выход которого соединен с информационным входом триггера 58, вы- ход инвертора 47 подключен к входу синхронизации триггера 56.

Датчик 12 двоичных кодов (фиг. 4) содержит входы 76-79 управления, информационный вход 80, первый 81, второй 82 и третий 83 выходы, триггер 84, управляемый инвертор 85. регистр 86 последовательного приближения, блок 87 инверторов, блок 88 шинных формирователей, при этом входы 76-79 управления образуют вход 17 управления датчика, входы 76-78 соединены соответственно с тактовым входом регистра 86 последовательного приближения, входом единичной установки триггера 84, входами управления инвертора 85 и блока 88 шинных формирователей, вход 79 подключен к входу запуска регистра 86 последова тельного приближения, информационный вход которого соединен с выходом управляемого инвертора 85, вход которого подключен к выходу триггера 84, вход синхронизации которого соединен с информационным входом 80, цифровые выходы регистра 86 последовательного приближения подключены в входу блока 87 инверторов-, выход которого соединен с вторым выходом датчика 12 двоичных кодов и входом блока 88 шинных формирователей, выход которого подключен к первому выходу 81, выход сигнала готовности регистров 86 последовательного приближения соединен с третьим выходом 83, информационный вход триггера 84 и вход разрешения работы регистра 86 последовательного приближения подключены к корпусу формирователя.

Запоминающее устройство (фиг 5) содержит вход 89 адреса, первый 90 и второй 91 информационные входы, входы 92-95 управления, первый 96 и второй 97 выходы запоминающего устройства 6, оперативное запоминающее устройство (ОЗУ) 98, регистр 99, инвертор 100, при этом вход 89 адреса подключен к адресному входу ОЗУ 98, информационные входы которого соединены с первым 90 и вторым 91 информационными входами запоминающего устройства в, входы управления: Запись/чтение и стробирование выхода под- ключены соответственно к входу 92 управления (через инвертор 100) и входу 93 запоминающего устройства б, входы 94 и 95 управления которого соединены соответственно с входом синхронизации (С) и управления состоянием выхода (Е2) регистра 99, информационный вход которого подключен к первому выходу ОЗУ 98. второй вы- ход которого соединен с вторым выходом 97 запоминающего устройства 6. первый выход которого подключен к выходу регистра 99.

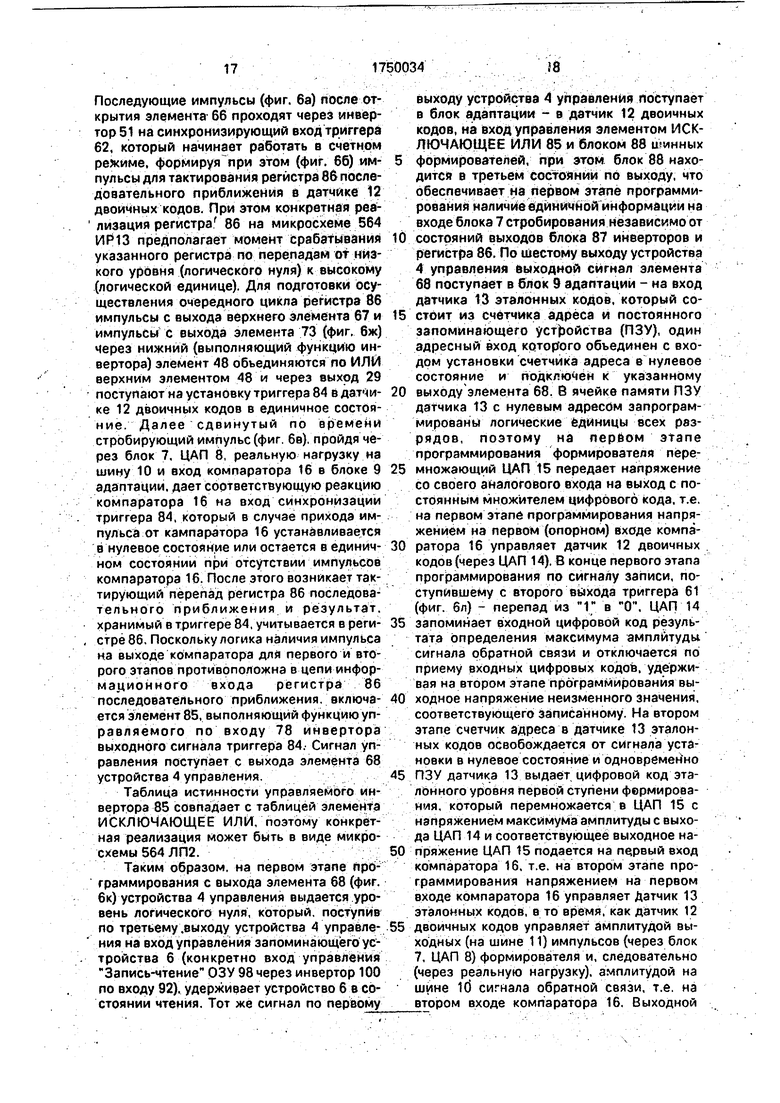

На фиг. 6 изображены диаграммы рабо- ты предлагаемого формирователя, где приняты следующие обозначения: а - сигнал на шине 1 внешнего запуска; б - тактовые импульсы на входе 76 регистра 86 последовательного приближения {в датчике 12 двоичных кодов блока 9): i - сигнал на втором входе блока 7 стробирования: г - сигнал на выходе триггера 57 устройства .4 управления; д - сигнал на выходе триггера 59 устройства 4 управления: е - сигнал на вхо-

де 79 запуска регистра 86 датчика 12 двоичных кодов блока 9 адаптации: ж - сигнал на входе 77 триггера 84 датчика 12 двоичных кодов блока 9 адаптации: з - сигнал готовности на выходе 83 регистра 86 последова- тельного приближения 86 (датчик 12 блока 9): и- выходные импульсы мультивибратора 75 устройства 4 управления; к - сигнал на выходе элемента 68 устройства 4 управления; л - сигнал на втором выходе 43 триггера 61 устройства 4 управления; м - сигнал на шине 2 запуска адаптации.

Генератор 3 тактовых импульсов может быть реализован на интегральной микросхеме 530 ГГ1. имеющей вход управления. При этом схема включения указанной микросхемы типовая, рекомендованная соответствующими техническими условиями изготовителя.

Счетчик 5 реализуется на микросхеме 530ИЕ17, включенной в режиме суммирования тактовых импульсов, прерываемого при записи нулевого состояния всех разрядов. Блок 7 стробирования может быть реализован на логических элементах И-Н Е мик- росхемы 530 ЛАЗ. при этом выход каждого разряда параллельного кода с выхода запоминающего устройства 6 подключен к первому входу соответствующего элемента И-НЕ, имеющего два логических эквивалентных между собой входа, а вторые входы элементов И-НЕ всех разрядов объединены и образуют второй вход блока 7 стробирования. выходом которого являются выходы указанных элементов И-НЕ.

Датчик 13 эталонных кодов может быть реализован как на однократно программируемом запоминающем устройстве (микросхемы серии 556), так и на перепрограммируемых ПЗУ - например, микросхемы 558РРЗ,- 1601РР1, 573РФ6, при этом счетчик адреса в указанном датчике эталонных кодов является суммирующим счетчиком, имеющим счетный вход и вход установки в нулевое состояние, выходы разрядов счетчика подключены на соответствующие адресные входы ПЗУ. При этом один разряд адреса указанного ПЗУ объединен с входом установки счетчика адреса в нулевое состояние, один выходной разряд ПЗУ подключен ко второму выходу датчика 13. а остальные разряды выходов ПЗУ соединяются с первым выходом датчика 13 (и далее на цифровой вход перемножающего ЦАП 15).

Формирователь имеет два режима работы: формирование импульсов (сокращенно - формирование) по находящейся в запоминающем устройстве б программе; программирование запоминающего устройства 6 в соответствии с данными, находящимися в датчике 13 эталонных кодов и фактическими значениями параметров реальной нагрузки (сокращенно - программирование).

Переключение режимов работы осуществляется триггером 59 устройства 4 управления, при этом уровень логического нуля на выходе указанного триггера соответствует режиму формирования, а уровень логической единицы - режиму программирования.

Работа формирователя в режиме формирования заключается в следующем.

Исходным состоянием счетчика 5 является нулевое состояние всех разрядов. При этом элемент И-НЕ 69 открыт по второму входу, а триггеры 57 и 58 находятся в нулевом состоянии, которое (выходным сигналом триггера 57) запрещает работу генератора 3 тактовых импульсов. В регистре 99 запоминающего устройства 6 хранится нулевое состояние всех разрядов, регистр.99 находится в активном состоянии по выходу, а блок 88 шинных формирователей - в состоянии высокого импеданса (третье состояние).

На элементе И-ИЛИ-НЕ 64 разрешен вход 42, подключенный к выходу генератора 3, на элементе 65 разрешено прохождение сигнала с второго выхода триггера 58.

На второй вход (стробирования) блока 7 стробирования с выхода элемента 72 постоянно (в режиме формирования) подается уровень логической единицы - разрешение для управления ЦАП 8 кодами запоминаю- щего устройства 6. При этом нулевой код с выхода запоминающего устройства 6 преобразуется ЦАП 8 в соответствующий исходный выходной 9 уровень напряжения. Блок 9 адаптации в режиме формирования находится в пассивном состоянии (не влияет на форму выходных сигналов на шине 11). С приходом по шине 1 на вход 24 внешнего запуска импульса запуска последний проходит через элементы 45 и 69 на входы уста- новки триггеров 57 и 58 в единичное состояние, которое по выходу триггера 57 поступает на вход разрешения формирования выходных импульсов генератора 3 тактовых импульсов. Импульсы с выхода генератора 3 проходят через элементы 64,52 и 53 на выходы 35,36 и 37 и далее соответственно на вход синхронизации регистра 99, тактовый вход счетчика 5 и вход (СЕ) 93 стробирования ОЗУ 98, находящего- ся постоянно и режиме чтения для режима формирования.

По мере суммирования импульсов счетчиком 5 изменяется его выходной код. задающий адрес ячеек ОЗУ 98. Указанный выходной код ОЗУ 98 записывается в каждом такте (периоде колебаний генератора 3) в регистр 99, выполняющий функцию буферного обеспечения одновременного (по фронту не входе синхронизации регистра 99) появления уровней выходного кода запоминающего устройства 6 и удержания записанного кода в течение каждого такта. Это исключает возможные искажения при преобразовании цифрового кода в ЦАП 8. Последовательно изменяясь, адреса ОЗУ 98 проходят от нулевого до максимального синхронно с импульсами генератора 3 тактовых импульсов, соответствующие выходные коды ОЗУ 98 через регистр 99, постоянно открытый в режиме формирования блок 7 стробирования преобразуются ЦАП 8 в ступенчатое напряжение, аппроксимирующее необходимую форму сигнала. Процесс формирования необходимого сиг- нала завершается с помощью запис анного в одной из ячеек ОЗУ 98 признака окончания, который поступает на второй выход 97 ОЗУ 98 и далее в устройство 4 управления на вход 44 инвертора 49. При этом, поступив на информационный вход триггера 58, сигнал с выхода инвертора 49 в виде уровня логического нуля записывается очередным тактовым импульсом с выхода элемента 64 в указанный триггер. После этого на выходе

элемента 65 логическая единица, разрешавшая счетчику 5 последовательный счет, сменяется на логический нуль, что соответствует записи в счетчик 5 (тип 530ИЕ17) нулевой информации в параллельном коде (постоянно задан подключением входов счетчика к уровню логического нуля - корпуса). Одновременно уровень логического нуля с первого выхода триггера 58 поступает на информационный вход триггера 57 и следующим тактовым импульсом с выхода элемента 64 происходит установка триггера 57 в исходное состояние, что вызывает прекращение работы генератора 3 тактовых импульсов. Одновременно последним тактовым импульсом генератора 3 в счетчик 5 и регистр 99 записывается исходный нулевой код.

Таким образом завершается цикл работы предлагаемого формирователя. Особенностью режима формирования является наличие внешнего запуска устройства по шине 1 (вход 24), при этом длительность импульса запуска выбирается короче процесса формирования полного сигнала предложенным устройством с тем, чтобы схема могла вернуться в исходное состояние.

В следующем цикле формирования описанные процессы повторяются.

Работа формирователя в режиме программирования заключается в следующем.

Исходным состоянием элементов схемы, участвующих в режиме формирования, являются текущие состояния формирования, т.е. до начала работы в режиме про-- граммирования формирователь находится в режиме формирования. При этом триггеры 59-61, 56, 62 и 63 соответственно имеют следующие исходные состояния: триггер 59 - нулевое; триггер 60 - единичное: триггер 61 - нулевое; триггер 56 - нулевое; триггеры 62 и 63 - нулевое.

Исходный уровень логического нуля с выхода триггера 56 запрещает прохождение импульсов с выхода элемента«45 (внешнего запуска по шине 1) через элемент И 66, поэтому исходно на первый выход устройства 4 управления (е составе выходов 29-31) импульсные сигналы управления блоком адаптации не поступают. Мультивибраторы 74 и 75 работают в ждущем режиме, поэтому исходно ими не формируются импульсы выходных сигналов.Элемент И 68 закрыт бла- годаря исходному нулевому состоянию триггера 59, поэтому уровень логического нуля с выхода элемента 68 поступает на выходы 38 и 39 и далее соответственно в запоминающее устройство 6 (вход 92) и датчик 13 эталонных кодов задает режим чтемия ОЗУ 98 и исходное состояние датчика 13 в блоке 9 адаптации.

Исходное состояние блока 9 адаптации до начала программирования является пассивным. При этом, поскольку отсутствуют импульсные сигналы управления по второму и четвертому входам блока 9 адаптации, состояние датчика 12. ЦАП 14 и 15 может быть произвольным. Компаратор 16 также может находиться в произвольном состоянии - соответствующем уровню напряжения на выходе ЦАП 15 и амплитуде импульсов на первом входе блока 9 адаптации. Указанные импульсы на первом входе блока 9 адаптации в предлагаемом устройстве являются сигналом обратной связи при работе в режиме программирования.

Из датчика 13 эталонных кодов в исходном состоянии (в соответствии с поступившим сигналом из устройства 4 управления по третьему входу блока 9 адаптации на вход 18 указанного датчика) выдается на первый выход (на вход ЦАП 15) исходный единичный код всех разрядов, на второй выход 22 и далее через третий выход блока 9 адаптации на второй информационный вход запоминающего устройства б и первый вход устройства 4 управления поступает исходный уровень логического нуля, что обеспечивает исходное состояние инвертора 50, элемента И-НЕ 70. Поскольку исходным для режима программирования является режим формирования, в котором запоминающее устройство б находится в режиме чтения ОЗУ 98, логический уровень на его втором информационном входе 91 не оказывает влияния на работу запоминающего устройства. 6. Так как запоминающий ЦАП 14- в блоке 9 адаптации осуществляет запоминание входной информации по перепаду от уровня логической единицы к уровню логического нуля, в отсутствие таких перепадов напряжение на втором выходе 43 триггера 61 в устройстве 4 управления и соответственно на седьмом выходе устройства 4. четвертом входе блока 9 адаптации и входе записи ЦАП 14 указанный ЦАП 14 находится в режиме преобразования входного значения цифрового кода. В исходном состоянии датчик 12 двоичных кодов и первый выход 20 блока 9 адаптации находятся в третьем состоянии за счет блока 88 шинных формирователей, управляемых сигналом с уровнем логического нуля, поступающим по входу 78. С приходом на шину 2 запуска адаптации импульса запуска (фиг. 6и) устройство 4 управления запрещает по пятому выходу работу генератора 3 тактовых импульсов; в счетчик 5 заносится исходное нулевое состояние всех разрядов; первый выход запоминающего устройства 6 переводится в третье состояние, а первый выход блока адаптации - в активное состояние; в блок 9 адаптации выдаются сигналы управления (с

выходов 1, б и 7 устройства 4 на входы 2-4 соответственно блока 9); на второй вход блока 7 стробирования поступают строби- рующие импульсы (фиг. бе).

Работа устройства в режиме програм0 мирования происходит далее е два этапа: определение цифрового кода максимума амплитуды импульсов обратной связи; поочередное определение цифровых кодов (и их запись в запоминающее устройство 6)

5 для каждого эталонного уровня и соответствующего такта работы режима формирова- ния.

На обоих этапах устройство 4 управления формирует сигналы для счетчика 5, за0 поминающего устройства б, блока 9 адаптации и блока 7 стробирования .синхронные с импульсами, поступающими по шине 1 внешнего запуска (фиг. 6а). В результате на первом этапе из блока 9 адаптации

5 выдается цифровой код по первому выходу соответственно на первый вход блока 7 стробирования с единичными уровнями во всех разрядах, что при открывании по второму (стробирующему) входу блока 7 стро0 бирования. ведет к формированию на выходе ЦАП 8 импульсов максимальной амплитуды. Указанные импульсы поступают в реальную нагрузку, имеющую выход обратной связи, на который выходной сигнал ре5 альной нагрузки передается без искажений (линейно). Поэтому возникающие в реальной нагрузке искажения адекватно отображаются в сигнале на выходе обратной связи, который поступает на шину 10 и первый

0 вход блока 9 адаптации.

В течение первого этапа блоком 9 адаптации осуществляется определение цифрового кода, соответствующего максимуму амплитуды, после чего на четвертый выход

5 блока адаптации выдается признак готовности, который, поступив по второму входу в устройство 4. вызывает переключение выходных сигналов устройства 4 управления в режим второго этапа. На первом этапе запо0 минающее устройство б остается в состоянии чтения, поэтому цифровой код. соответствующий максимуму амплитуды импульсов на шине 10 и поступающий на первый информационный вход запоминаю5 щего устройства 6 не записывается в последнее, а счетчик S при этом не изменяет своего нулевого состояния, т.е. цифровой код максимума амплитуды формируется блоком 9 адаптации, запоминание этого кода происходит также в блоке 9 адаптации по

перепаду, поступающему из устройства 4 управления по седьмому выходу через четвертый вход блока 9. Указанный перепад возникает как ответ устройства 4 управления на появление первого признака готовности, поступающего по второму входу из блока 9 адаптации на первом этапе программирования, т.е. при первом появлении признака готовности на четвертом выходе блока 9 адаптации первый этап заканчивается и начинается второй этап программирования.

При этом работа предлагаемого устройства происходит следующим образом. Блок 9 адаптации поочередно определяет цифровые коды, соответствующие хранимым внутри блока 9 эталонным значениям кодов. Это определение идет путем поочередного задания значений цифровых кодов на первый вход блока 7 стробирования (с первого выхода блока 9) до получения равенства амплитуды импульсов на шине 10 и установленного внутри блока 9 эталонного уровня напряжения, соответствующего эталонному коду блока 9. При получении равенства амплитуды импульсов обратной связ и (на шине 10) из блока 9 адаптации выдается по четвертому выходу признак готовности, который по второму входу поступает в устройство 4 управления. Устройство 4 управления при этом формирует вначале сигналы записи цифрового кода, равного определенному в блоке 9 адаптации, в запоминающее устройство 6 (по первому информационному входу устройства 6).

После записи указанного кода в ячейку с адресом, соответствующим цифровому коду на выходе счетчика 5. устройство 4 управления наращивает адрес путем подачи одного импульса на счетный вход счетчика

5.Кроме того, устройство 4 управления по шестому выходу выдает команду переключения блока 9 адаптации на следующий по порядку эталонный код (уровень напряжения). После этого блок 9 адаптации вновь повторяет цикл определения цифрового кода, соответствующего текущему-эталонному коду, далее вновь формируется признак готовности на четвертом выходе блока 9 и соответственно происходят описанные процессы записи в запоминающее устройство

6.счетчик 5 и т.д. Число таких циклов определяется выбранным числом дискретов по времени режима формирования. После определения и.записи последнего цифрового кода второго этапа программирование из блока 9 адаптации выдается на третий выход признак окончания, который записывается в соответствующую ячейку (с очередным адресом запоминающего устройства б по второму информационному входу), а по первому входу устройства 4 управления указанный признак интерпретируется как условие окончания програм- 5 мирования, после чего устройство 4 управления переключается в режим формирования, соответственно изменяя при этом управляющие сигналы для счетчика 5, запоминающего устройства б, блока 7 стробиро- 0 вания и блока 9 адаптации. После этого вновь начинает работать генератор 3 тактовых импульсов, т.е. происходит процесс формирования импульсов, как было описано, с той разницей, что цифровые коды

5 считываемые на каждом такте из запоминающего устройства, являются теми, которые обеспечивают требуемую форму импульса не на выходе ЦАП 11, а на выходе реальной нагрузки. Этим достигается устранение ис0 кажений формы импульсов за счет реальной нагрузки

Кроме того, при программировании осуществляется по хранимому в памяти блока 9 адаптации эталонному представлению

5 формируемых импульсов в виде последовательности эталонных цифровых кодов получения другой (отличной от эталонной) последовательности цифровых кодов, заносимых в запоминающее устройство 6. Ука0 занное эталонное представление определяется расчетным путем при аппроксимации требуемой формы импульсов, т е. в соответствии с периодом генератора 3 тактовых импульсов определяются значения

5 эталонных цифровых кодов (отсчеты амплитуды в точке начала каждого следующего периода генератора 3) Эти эталонные цифровые коды и заносятся в память блока 9 адаптации, Период генератора 3 эыбирает0 ся обычно, исходя из известной теоремы Котельникова На первом этапе программирования определяется фактическое значение максимальной амплитуды Um импульса. которое далее запоминается в блоке 9 адап5 тации в виде цифрового кода Набор эталон ных цифровых кодов для блока 9 хранится в датчике 13 эталонных кодов в виде относительных значений Поскольку при этом эталонный код датчика 13 в перемножающем

0 ЦАП 15 умножается на величину Um- хранимую в запоминающем ЦАП 14, на выходе ЦАП 15 и первом входе компаратора 16 для каждого отсчета формирования импульса выдается эталонный уровень напряжения с

5 учетом реального максимума амплитуды (Dm). Запоминание Um происходит на первом этапе в ЦАП 14. при этом из датчика 13 эталонных кодов выдается единичный код всех разрядов, т.е при поиске цифрового кода, соответствующего максимуму амплитуды, изменяется с помощью датчика 12 двоичных кодов цифровой код на цифровом входе ЦАП 14 (при неизменном единичном коде на цифровом входе ЦАП 15).

В конце первого этапа программиро- вания перепадом по четвертому входу 19 блока 9 адаптации производится запись-запоминание цифрового кода с входа ЦАП 14 в его внутреннюю память и в дальнейшем на втором этапе программирования этот код хранится в ЦАП 14 и его выходное напряжение сохраняется постоянным в соответствии с указанным кодом.

На втором этапе программирования становится активным первый выход 20 бло- ка 9 адаптации, т.е. датчик 12 двоичных кодов осуществляет поиск уже не через ЦАП 14, как на первом этапе программирования, а через блок 7 стробирования, ЦАП 8 и реальную нагрузку. На втором этапе програм- мирования для каждого значения эталонного цифрового кода, выдаваемого последовательнодатчиком 13 эталонных кодов, по указанной цепи (блок 7, ЦАП 8. реальная нагрузка) прохождения выдаваемых датчиком 12 на первый 20 выход цифровых коДов, по выходному сигналу компаратора 16 находится датчиком 12 цифровой код, давший равенство амплитуд сигналов по первому входу компаратора (эталон) и по второму входу - с шины 10 сигнала обратной связи. После определения кода в датчике 12 через его первый выход (и второй выход 21 блоха 9) этот код передается в запоминающее устройство 6. где заломи- нается в очередной ячейке памяти. Далее датчик 13 эталонных кодов по сигналам управления на третьем входе 18 блока 9 адаптации переходит к выдаче следующего эталонного кода и т.д. Признак окончания (в виде логической единицы в одном из разря- .дов) записан в датчике 13 эталонных кодов блока 9 и далее, поступая на второй информационный вход запоминающего устройства 6 и первый вход устройства 4 управления. соответственно записывается в устройство 6 и запускает устройство 4 на переключение в режим формирования. В процессе программирования датчик 12 двоичных кодов получает от устройства 4 управления через второй вход. 17 блока 9 адаптации необходимые сигналы управления, соответствующим образом синхронизированные с моментами времени стробирования блока 7 стробирования, что обеспечивает правиль- иый результат при считываний его с выхода компаратора 16. Признак готовности выдается на четвертый выход 23 блока 9 адаптации и далее, поступая в устройство 4 управления, вызывает переход к следующему циклу работы (определению след ощего цифрового кода).

Рассмотрим работу устройства при конкретной реализации одного из вариантов устройства 4 управления, счетчика 5, запоминающего устройства 6 и датчика 12 двоичных кодов.

С приходом на шину 2 запуска адаптации импульса запуска (фиг. 6м) триггер 59 устанавливается в состояние логической единицы по выходу (фиг. 6д). Возникший при этом перепад (от низкого уровня к высокому) запускает одновременно триггер 60 и мультивибратор 75. При этом взаимодействие триггеров 60 и 61 приводит к установке (в следующей последовательности: нулевой уровень на выходе триггера 60. нулевой уровень на первом выходе триггера 61, единичный уровень на выходе триггера 60) триггера 61 в единичное состояние, т.е. на первом выходе триггера 61 - логический нуль, а на втором - единица. Поэтому логический нуль с первого выхода триггера 61, поступив на второй вход элемента 68. удерживает его по выходу в исходном состоянии логического нуля, несмотря на поступивший уровень логической единицы - с выхода триггера 59 (фиг. 6д). Выходной сигнал триггера 59 (фиг. бд) открывает по первым входам элементы 64.65.71 и 72 и прекращается удержание в нулевом состоянии триггеров 56. 62 и 63. Пройдя через, инвертор чь, указанный сигнал устанавливает в нулевое состояние триггеры 57 и 58 и закрывает элементы 64 и 65 по вторым входам. При этом процесс формирования выходных импульсов в предлагаемом устройстве прерывается, так как выходной сигнал триггера 57 становится запрещающим для генератора 3 тактовых импульсов, а сигналы управления счетчиком 5, запоминающим устройством 6 (выходы 32-3S) заменяются на сигналы, поступающие через элементы 64 и 65 по четвертым входам, соответственно со второго выхода мультивибратора 75 и элемента И-НЕ 70 который при установке триггера 61 в единичное состояние (описано выше) имеет на выходе уровень логической единицы. Поэтому элемент 65 обеспечивает (в начале режима программирования) на выходе уровень логического нуля, который,поступив на вход счетчика 5. обеспечивает установку последнего в нулевое состояние. Ближайший к моменту установки триггера 59 в единичное состояние из импульсов (фиг. 6а) внешнего запуска (по шине 1). пройдя через элементы 45 и 47 на синхронизирующий вход триггера 56, записывает в него логическую единицу (фиг. бг). Выходной сигнал триггера 56 при этом открывает элемент 66

Последующие импульсы (фиг. 6а) после открытия элемента 66 проходят через инвертор 51 на синхронизирующий вход триггера 62, который начинает работать в счетном режиме, формируя при этом (фиг. 66) импульсы для тактирования регистра 86 последовательного приближения в датчике 12 двоичных кодов. При этом конкретная реализация регистра 86 на микросхеме 564 ИР13 предполагает момент срабатывания указанного регистра по перепадам от низкого уровня (логического нуля) к высокому (логической единице). Для подготовки осуществления очередного цикла регистра 86 импульсы с выхода верхнего элемента 67 и импульсы с выхода элемента 73 (фиг, бж) Через нижний (выполняющий функцию инвертора) элемент 48 объединяются по ИЛИ верхним элементом 48 и через выход 29 поступают на установку триггера 84 в датчике 12 двоичных кодов в единичное состояние. Далее сдвинутый по времени стробирующий импульс (фиг. 6в). пройдя через блок 7, ЦАП 8, реальную нагрузку на шину 10 и вход компаратора 16 в блоке 9 адаптации, дает соответствующую реакцию компаратора 16 на вход синхронизации триггера 84, который в случае прихода импульса от кампаратора 16 устанавливается в нулевое состояние или остается в единичном состоянии при отсутствии импульсов компаратора 16. После этого возникает тактирующий перепад регистра 86 последовательного приближения и результат, хранимый в триггере 84, учитывается в регистре 86. Поскольку логика наличия импульса на выходе компаратора для первого и второго этапов противоположна в цепи инфор- ма.ционного входа регистра 86 последовательного приближения, включается элемент 85, выполняющий функцию уп- равляемого по входу 78 инвертора выходного сигнала триггера 84/ Сигнал управления поступает с выхода элемента 68 устройства 4 управления.

Таблица истинности управляемого инвертора 85 совпадает с таблицей элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, поэтому конкретная реализация может быть в виде микросхемы 564 ЛП2.

Таким образом, на первом этапе программирования с выхода элемента 68 (фиг. 6к) устройства 4 управления выдается уровень логического нуля, который, поступив по третьему .выходу устройства 4 управления на вход управления запоминающего устройства 6 (конкретно вход управления Запись-чтение ОЗУ 98 через инвертор 100 по входу 92). удерживает устройство 6 в состоянии чтения. Тот же сигнал по первому

выходу устройства 4 управления поступает в блок адаптации - в датчик 12 двоичных кодов, на вход управления элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 85 и блоком 88 ионных 5 формирователей, при этом блок 88 находится в третьем состоянии по выходу, что обеспечивает на первом этапе программирования наличие единичной информации на входе блока 7 стробирования независимо от

0 состояний выходов блока 87 инверторов и регистра 86, По шестому выходу устройства 4 управления выходной сигнал элемента 68 поступает в блок 9 адаптации - на вход датчика 13 эталонных кодов, который со5 стоит из счетчика адреса и постоянного запоминающего устройства (ПЗУ), один адресный вход которого объединен с входом установки счетчика адреса в нулевое состояние и подключен к указанному

0 выходу элемента 68. 8 ячейке памяти ПЗУ датчика 13 с нулевым адресом запрограммированы логические единицы всех разрядов, поэтому на первом этапе программирования формирователя пере5 множающий ЦАП 15 передает напряжение со своего аналогового входа на выход с постоянным множителем цифрового кода, т.е. на первом этапе программирования напряжением на первом (опорном) входе компа0 ратора 16 управляет датчик 12 двоичных кодов (через ЦАП 14). В конце первого этапа программирования по сигналу записи, поступившему с второго выхода триггера 61 (фиг. 6л) - перепад из 1 в О, ЦАП 14

5 запоминает входной цифровой код результата определения максимума амплитуды сигнала обратной связи и отключается по приему входных цифровых кодов, удерживая на втором этапе программирования вы0 ходное напряжение неизменного значения, соответствующего записанному. На втором этапе счетчик адреса в датчике 13 эталонных кодов освобождается от сигнала установки в нулевое состояние и одновременно

5 ПЗУ датчика 13 выдает цифровой код эталонного уровня первой ступени формирования, который перемножается в ЦАП 15 с напряжением максимума амплитуды с выхода ЦАП 14 и соответствующее выходное на0 пряжение ЦАП 15 подается на первый вход компаратора 16, т.е. на втором этапе программирования напряжением на первом входе компаратора 16 управляет Датчик 13 эталонных кодов, в то время, как датчик 12

5 двоичных кодов управляет амплитудой выходных (на шине 11) импульсов (через блок 7, ЦАП 8) формирователя и, следовательно (через реальную нагрузку), амплитудой на шине 10 сигнала обратной связи, т.е. на втором входе компаратора 16. Выходной

импульс мультивибратора 75 (фиг. би) формируется при каждом запуске мультивибратора 74 - сигналом с выхода 83 регистра 86 (фиг. 6з) датчика 12 двоичных кодов, который является признаком готовности результата определения датчиком 12 очередного цифрового кода, На втором этапе блок 88 шинных формирователей переводится в активное состояние, что и позволяет передавать цифровые коды из датчика 12 на вход блока 7стробирования. Поскольку для регистра 86 последовательного приближения необходим импульс запуска (фиг. бе), который формируется с помощью триггера 63, элемента 73 в устройстее 4 управления, на время запуска в сигнал управления по входу 77 триггером (фиг. 6ж) замещается с помощью элемента 47 указанный импульс запуска. Это обеспечивает однозначное состояние триггера 84 в датчике 12 в начале каждого цикла работы регистра 86. Выходной импульс мультивибратора 75 поступает также на счетный вход счетчика адреса для ПЗУ датчика 13 эталонных кодов, обеспечивая при этом переключение указанного счетчика адреса и, следовательно, выходного эталонного кода датчика 13 Окончание второго этапа программирования задается првграммой ПЗУ датчика 13 эталонных кодов, при этом в одной из ячеек ПЗУ для отдельного выходного разряда, подключенного1 к третьему выходу 22 блока 9 адаптации, записывается 1, которая далее поступает в запоминающее устройство 6 и устройство 4 управления, где соответственно записывается в ОЗУ 88 и вызывает процесс переключения в режим формирования. При .этом происходит запись нулевого состояния в счетчик 5 и триггер 59 устройства 4 управления.

Таким образом, в предлагаемом форми- . рователе в отличие от известного имеется возможность адаптации программы запоминающего устройства б к параметрам реальной нагрузки, поскольку за счет работы блока 9 адаптации и устройства 4 управления в режиме программирования по эталонному набору цифровых кодов в датчике эталонных кодов определяется соответствующий набор реально необходимых кодов для режима формирования с учетом искажений в реальной нагрузке. Это устраняет необходимость подбора программы запоминающего устройства 6 вручную для каждого экземпляра конкретней нагрузки предлагаемых формирователей, что упрощает их изготбвление, а также обеспечивает поддержание точности формирования в эксплуатации - при изменении параметров реальной нагрузки от воздействия

дестабилизирующих факторов: изменения температуры окружающей среды, старения элементов. Введенные в схему блока адаптации датчик двоичных кодов, датчик

эталонных кодов, запоминающий и перемножающий ЦАП, а также компаратор обеспечивают функцию адаптации предлагаемого формирователя. При этом использование, запоминающего ЦАП,

0 соединенного по выходу с аналоговым входом перемножающего ЦАП, позволяет блоку адаптации отслеживать фактическое значение максимальной амплитуды импульса обратной связи. Это устраняет зависи5 мость цифровых кодов датчика эталонных кодов от указанного значения амплитуды, что исключает регулировочные операции в предлагаемом формирователе и упрощает его изготовление.

0 Программа - набор эталонных кодов в датчике эталонных кодов для неизменной формы выходных импульсов предлагаемого формирователя также является неизменной, не зависит от разброса параметров ре5 альной нагрузки, поскольку в процессе адаптации (программирования запоминающего устройства) учитываются реальные свойства (искажения, вносимые в формирование) реальной нагрузки. Поскольку изме0 нения параметров реальной нагрузки в зависимости от разброса параметров, их изменений от воздействия температуры и старения являются однократными (разброс) или медленнО Меняющимися (от температу5 ры и т.п.), в формирователе достаточно однократной операции адаптации - при включении питания, что однако не исключает имеющейся возможности проведения указанной операции в любой необходимый

0 момент времени.

Достоинством предлагаемого формирователя является учет искажений не только реальной нагрузки, ной погрешностей ЦАП, непосредственно участвующего в преобра5 зовании цифровых кодов - формировании импульсов, т.е. вносимые искажения за счет ЦАП учитываются в сумме с искажениями реальной нагрузки при адаптации. Это значительно снижает требования к точности и

0 стабильности ЦАП, что, в свою очередь, дает возможность использовать в ЦАП наиболее быстродействующие варианты построения схемы, а это дает возможность увеличивать частоту генератора тактовых импульсов,

5 что, в свою очередь, позволяет формировать импульсные сигналы с большей крутизной изменения напряжения, что является важным при использовании предлагаемого формирователя для формирования импульсов микросекундной длительности.

Формула изобретения

1. Адаптивный формирователь импульсов, содержащий генератор тактовых импульсов, счетчик, выход которого соединен с входом запоминающего устройства, цифро- аналоговый преобразователь, выход которого подключен к выходу формирователя, отличающийся тем, что. с целью расширения области применения путем обеспечения автоматической компенсации изменений параметров реальной нагрузки в процессе эксплуатации, в него введены устройство управления, блок адаптации и блок стробирования. первый вход которого соединен с объединенными первыми выходами запоминающего устройства и блока адаптации, второй выход которого подключен к первому информационному входу запоминающего устройства, второй информационный вход которого объединен с первым входом устройства управления и соединен с третьим выходом блока адаптации, первый вход которого подключен к шине сигнала обратной связи, а второй вход соединен с первым выходом устройства управления, второй вход которого подключен к четвертому выходу блока адаптации, второй выход устройства управления соединен с вторым входом блока стробирования, выход которого подключен к входу цифроаналого- вого преобразователя, третий выходустрой- ства управления соединен с входом управления запоминающего устройства, второй выход которого подключен к третьему входу устройства управления, четвертый выход которого соединен с входом счетчика, пятый выход устройства управления подключен к входу генератора тактовых импульсов, выход которого соединен с

четвертым входом устройства управления, пятый и шестой входы которого подключены соответственно к шине сигнала внешнего запуска и шине сигнала запуска адаптации,

а шестой и седьмой выходы устройства уп- раеления соединены соответственно с третьим и четвертым выходами блока адаптации.

2. Формирователь по п. 1, о т л и ч а ющ и и с я тем, что блок адаптации содержит датчик двоичных кодов, запоминающий и перемножающий цифроаналоговые преобразователи, датчик эталонных кодов и компаратор, выход которого соединен с первым

входом датчика двоичных кодов, второй вход которого является входом управления указанного датчика и подключен к второму входу блока адаптации, третий вход которого соединен с входом датчика эталонных

кодов, первый выход которого подключен к цифровому входу перемножающего цифро- аналогового преобразователя, аналоговый вход которого соединен с выходом запоминающего цифроаналогового преобразователя, вход записи которого подключен к четвертому входу блока адаптации, первый выход которого соединен с вторым выходом датчика двоичных кодов, первый выход которого подключен к объединенным цифровому входу запоминающего циф- роаналогового преобразователя и второму выходу блока адаптации, третий выход которого соединен с вторым выходом датчика эталонных кодов, а четвертый выход блока

адаптации подключен к третьему выходу датчика двоичных кодов, выход перемножающего цифроаналогового преобразователя соединен с первым входом компаратора, второй вход которого подключен к первому

входу блока адаптации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2008 |

|

RU2385479C2 |

| Устройство стабилизации частотыКВАРцЕВОгО гЕНЕРАТОРА | 1979 |

|

SU803107A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

Изобретение предназначено для задания формы импульсов путем дискретизации сигнала пи времени и амплитуде. Цель изобретения - расширение области применения путем обеспечения автоматической компенсации изменений параметров реальной нагрузки. Для достижения указанной цели в формирователь импульсов, содержащий генератор 3 тактовых импульсов, счетчик 5, запоминающее устройство б и ЦАП О, введены устройство 4 управления, блок 7 стробировэиия и блок 9 адаптации с соответствующими связями, 1 з.п. ф-лы, 6 ил.

1т,

fbf.

Фиг.З

.. §:

in г

in г

L-.

Ifl

Ш;Ј

| Формирователь напряжения ступенчатой формы | 1980 |

|

SU936403A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Справочник по цифроана- логовым и аналого-цифровым преобразователям | |||

| М.: Радио и связь, 1982, с | |||

| Арматура для железобетонных свай и стоек | 1916 |

|

SU259A1 |

| рис, 4.129. | |||

Авторы

Даты

1992-07-23—Публикация

1990-11-11—Подача