Изобретение относится к измерительной технике и может найти применение в системах автоматического управления, системах автоматизации научных исследований, гибридных вычислительных комплексах.

Цель - повышение быстродействия цифроаналогового преобразования с автоматической коррекцией нелинейности.

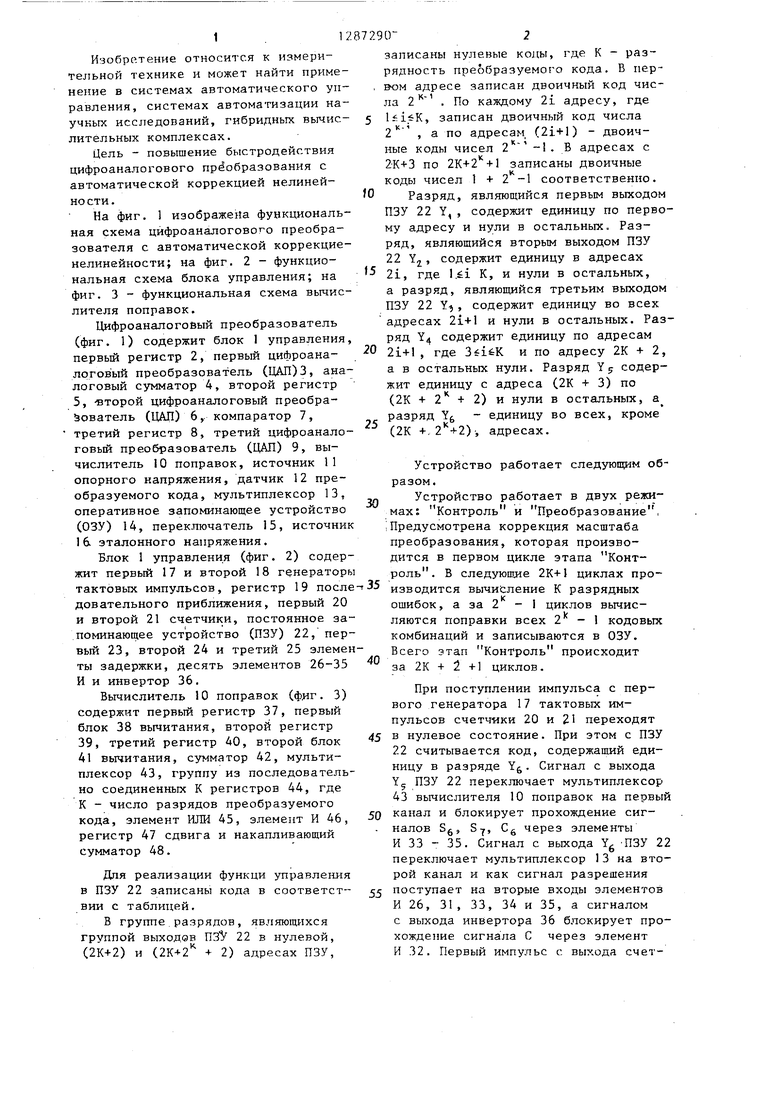

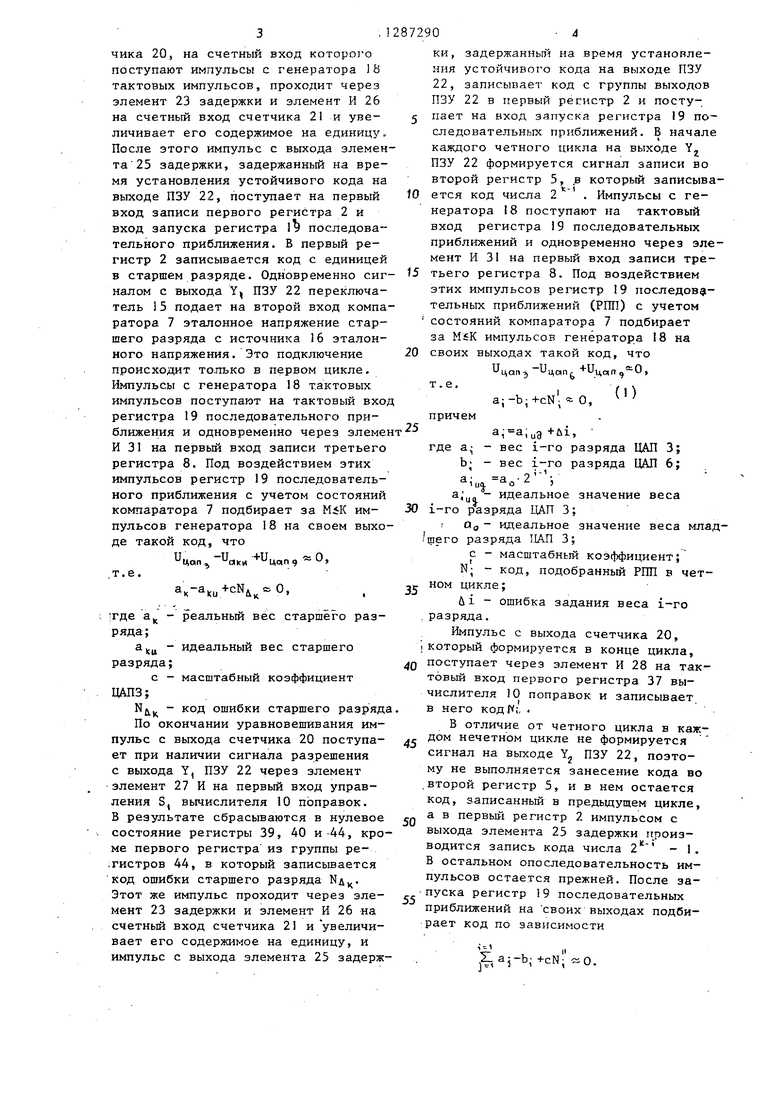

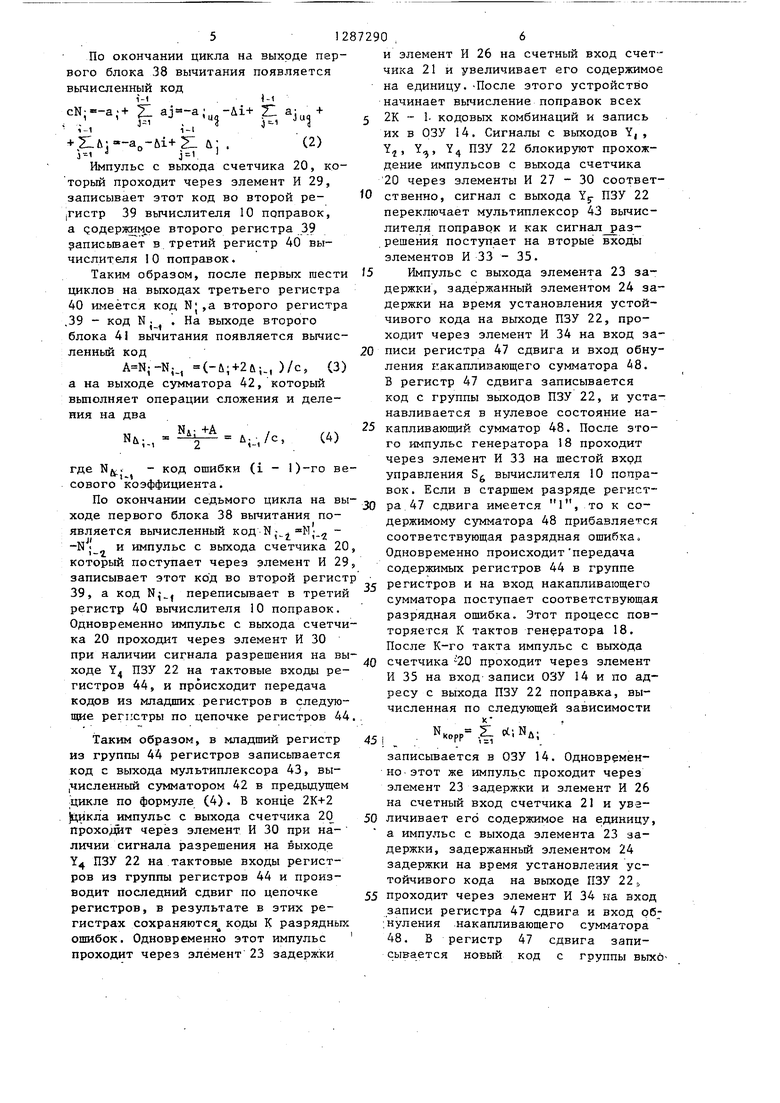

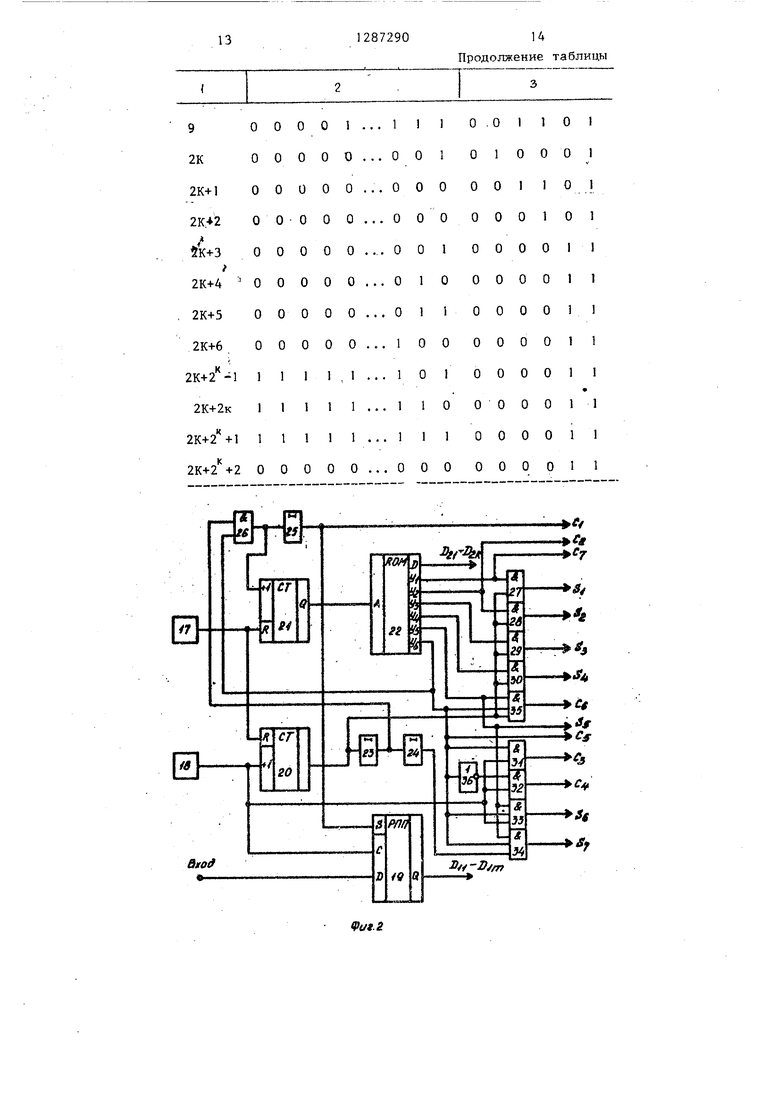

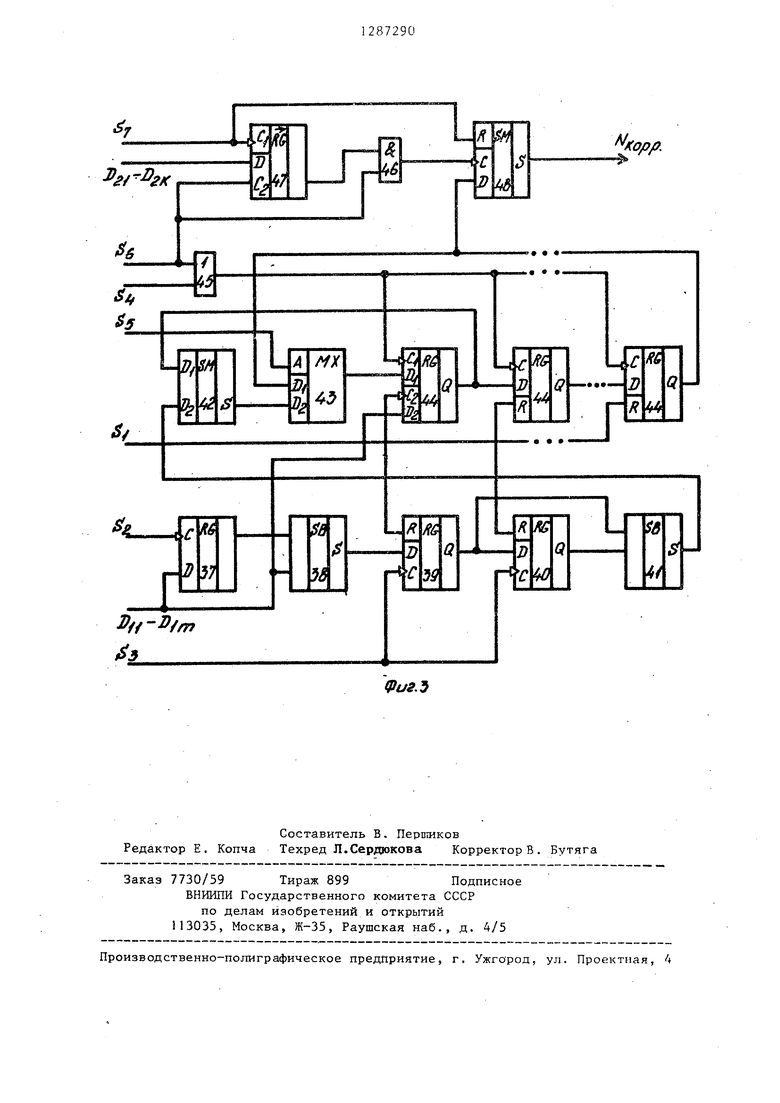

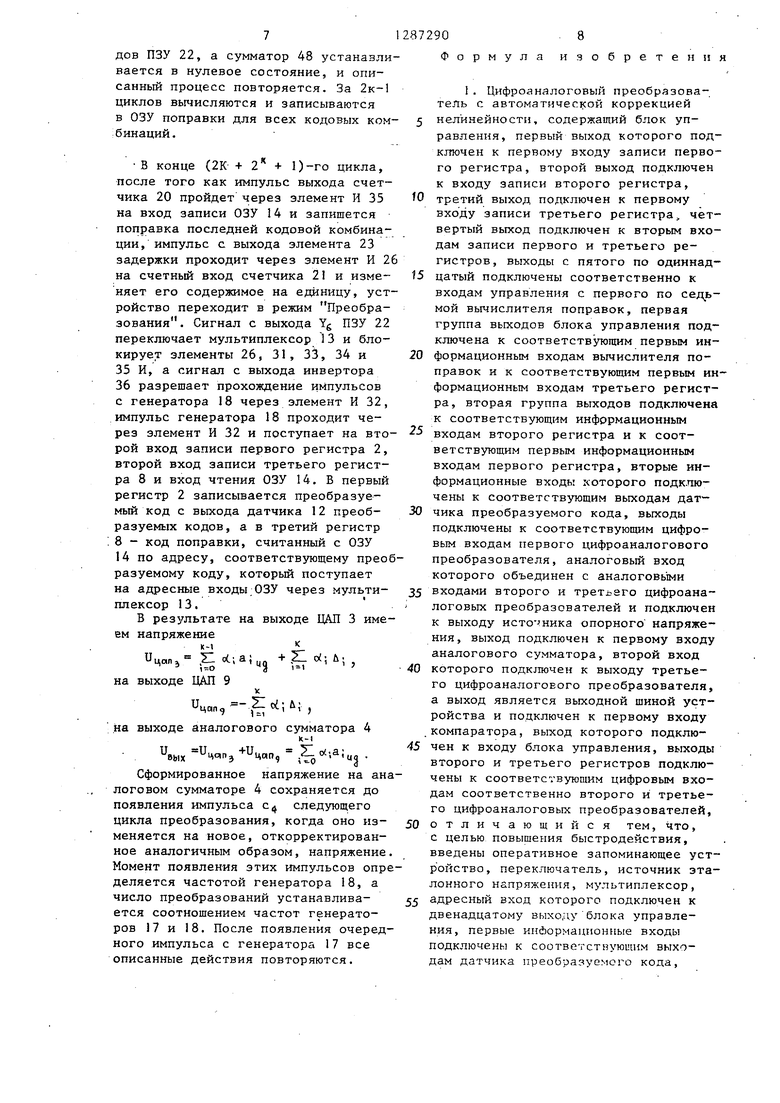

На фиг. 1 изображена функциональная схема цифроаналогового преобразователя с автоматической коррекцие- нелинейности; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема вычислителя поправок.

ЦифроаналогоВый преобразователь (фиг. 1) содержит блок 1 управления первый регистр 2, первый цифроана- логов ый преобразователь (ЦАП)З, аналоговый сумматор 4, второй регистр 5, -второй дифроаналоговый преобразователь (ЦАП) 6, компаратор 7, третий регистр 8, третий цифроанало- говый преобразователь (ЦАП) 9, вычислитель 10 поправок, источник 11 опорного напряжения, датчик 12 преобразуемого кода, мультиплексор 13, оперативное запоминающее устройство (ОЗУ) 14, переключатель 15, источник 16. эталонного напряжения.

Блок 1 управления (фиг. 2) содержит первый 17 и второй 18 генераторы тактовых импульсов, регистр 19 после довательного приближения, первый 20 и второй 21 счетчики, постоянное запоминающее устройство (ПЗУ) 22, первый 23, второй 24 и третий 25 элементы задержки, десять элементов 26-35 И и инвертор 36.

Вычислитель 10 поправок (фиг. 3) содержит первый регистр 37, первый блок 38 вычитания, второй регистр 39, третий регистр 40, второй блок 41 вычитания, сумматор 42, мультиплексор 43, группу из последовательно соединенных К регистров 44, где К - число разрядов преобразуемого кода, элемент ИЛИ 45, элемент И 46, регистр 47 сдвига и накапливающий сумматор 48.

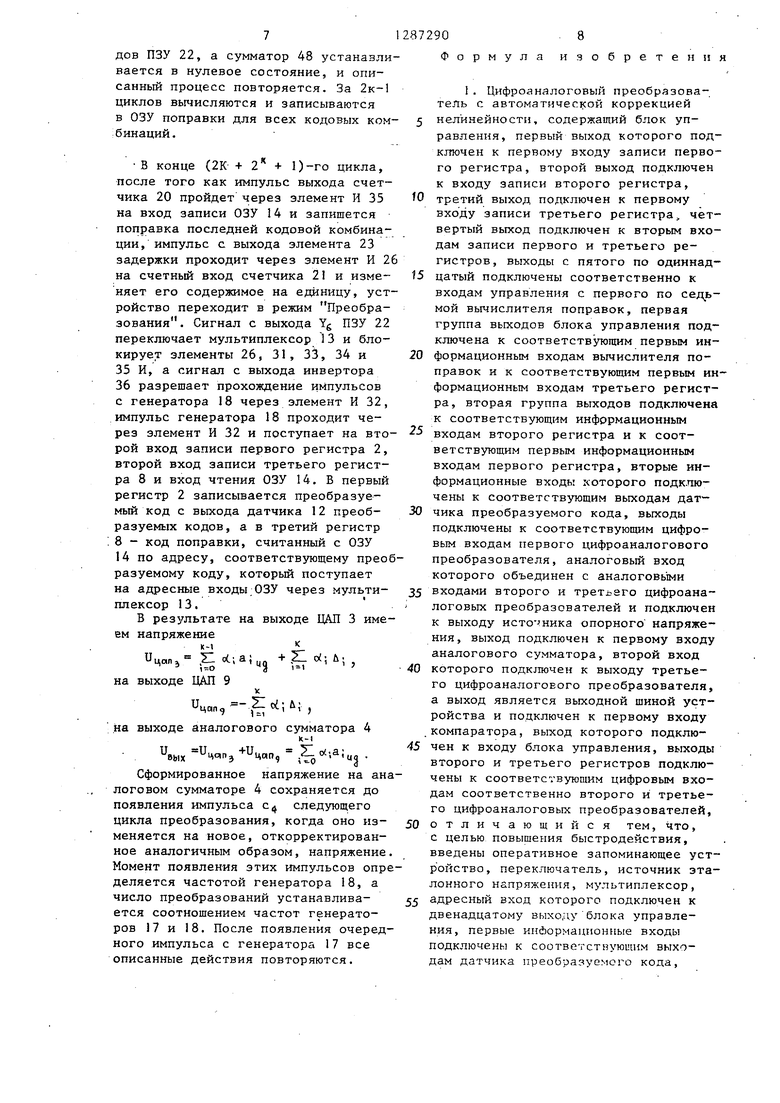

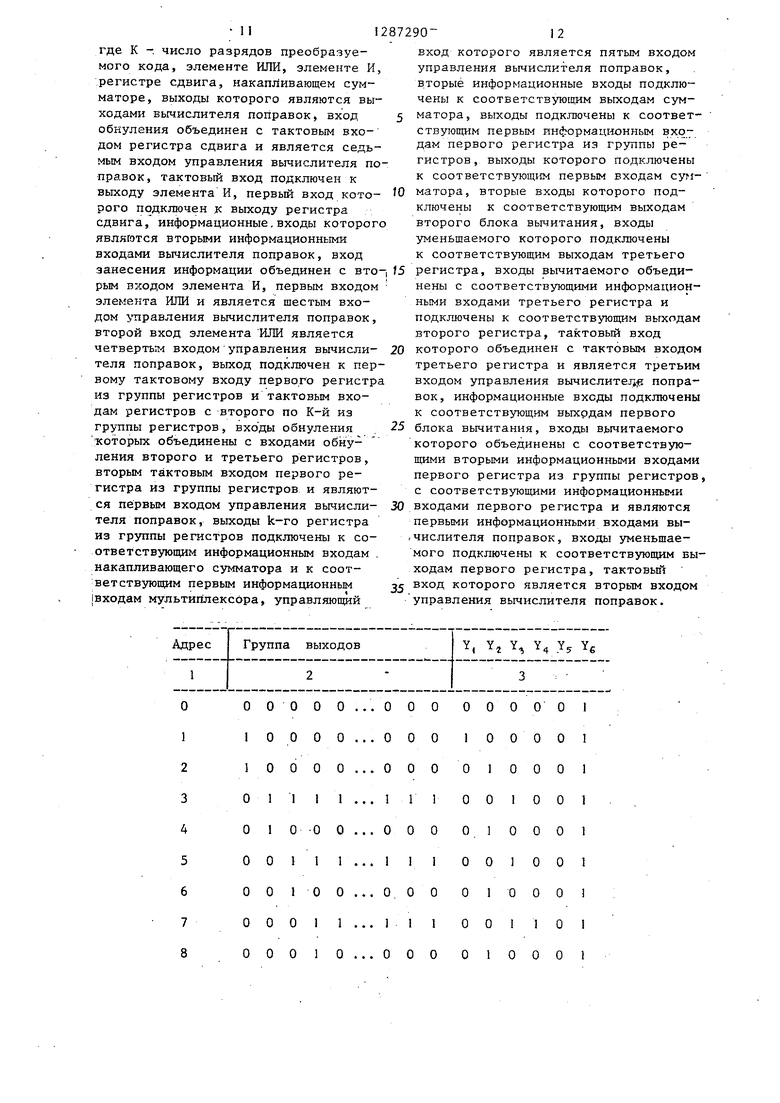

Для реализации функци управления в ПЗУ 22 записаны кода в соответствии с таблицей.

В группе разрядов, являющихся группой выходов ПЗ 22 в нулевой, (2К+2) и (2X42 + 2) адресах ПЗУ,

287291Г2

записаны нулевые коды, где К - разрядность преобразуемого кода. В пер- I вюм адресе записан двоичный код числа . По каждому 21 адресу, где liii. SK, записан двоичный код числа

5

0

а по адресам, (21+1) - двоич- -1. В адресах с

ные коды чисел 2-К+З по 2К+2 + 1

записаны двоичные 2 -1 соответственно.

коды чисел 1 +

Разряд, являющийся первым выходом ПЗУ 22 Y, , содержит единицу по первому адресу и нули в остальных. Разряд, являющийся вторьм выходом ПЗУ 22 YJ, содержит единицу в адресах 21, где l,i К, и нули в остальных, а разряд, являющийся третьим выходом ПЗУ 22 Y, содержит единицу во всех адресах 21+1 и нули в остальных. Разряд Y содержит единицу по адресам 21+1, где и по адресу 2К + 2, а в остальных нули. Разряд Y содер- адреса (2К + 3) по

остальных, а

жит единицу с

(2К + 2 + 2) и нули в

5

0

5

0

5

0

5

- единицу во всех, кроме (2К +, ) ., адресах.

Устройство работает следующим образом.

Устройство работает в двух режимах: Контроль и Преобразование, ;Предусмотрена коррекция масщтаба преобразования, которая производится в первом цикле этапа Контроль. В следующие 2К+1 циклах производится вычисление К разрядных ошибок, а за 2 - I циклов вьиис- ляются поправки всех 2 - 1 кодовьт комбинаций и записываются в ОЗУ. Всего этап Контроль происходит за 2К + 2 +1 циклов.

При поступлении импульса с первого генератора 17 тактовых импульсов счетчики 20 и 21 переходят в нулевое состояние. При этом с ПЗУ 22 считывается код, содержащий единицу в разряде Y. Сигнал с выхода Yj ПЗУ 22 переключает мультиплексор 43 вычислителя 10 поправок на первый канал и блокирует прохождение сигналов Sg, S-J, Cg через элементы И 33 - 35. Сигнал с выхода Y ПЗУ 22 переключает мультиплексор 13 на второй канал и как сигнал разрешения поступает на вторые входы элементов И 26, 31, 33, 34 и 35, а сигналом с выхода инвертора 36 блокирует прохождение сигнала С через элемент И 32. Первый импульс с выхода счетчика 20, на счетный вход которого поступают импульсы с генератора 18 тактовых импульсов, проходит через элемент 23 задержки и элемент И 26 на счетный вход счетчика 21 и увеличивает его содержимое на единицу, После этого импульс с выхода элемента 25 задержки, задержанный на время установления устойчивого кода на выходе ПЗУ 22, поступает на первый вход записи первого регистра 2 и вход запуска регистра 19 последовательного приближения. В первый регистр 2 записывается код с единицей в старшем разряде. Одновременно сигналом с выхода Y, ПЗУ 22 переключатель 15 подает на второй вход компаратора 7 эталонное напряжение старшего разряда с источника 16 эталонного напряжения. Это подключение происходит только в первом цикле. Импульсы с генератора 18 тактовых импульсов поступают на тактовый вход регистра 19 последовательного приближения и одновременно через элемен И 31 на первый вход записи третьего регистра 8. Под воздействием этих импульсов регистр 19 последовательного приближения с учетом состояний компаратора 7 подбирает за импульсов генератора 18 на своем выходе такой код, что

и.,

Цап,

-иа.и- иц,„,«0.

т.е,

-«cN.0,

где а - реальный вес старшего разряда;

Ки

- идеальный вес старшего

разряда;

с - масштабный коэффициент ЦАПЗ;

Nji - код ошибки старшего разряд

По окончании уравновешивания импульс с выхода счетчика 20 поступает при наличии сигнала разрешения с выхода Y, ПЗУ 22 через элемент элемент 27 И на первый вход управления S, вычислителя 10 поправок. В результате сбрасываются в нулевое состояние регистры 39, 40 и-44, кроме первого регистра из группы ре- .гистров 44, в который записывается код ошибки старшего разряда Кд. Этот же импульс проходит через элемент 23 задержки и элемент И 26 на счетный вход счетчика 21 и увеличивает его содержимое на единицу, и импульс с выхода элемента 25 задержки, задержанный на время установления устойчивого кода на выходе ПЗУ 22, записывает код с группы выходов ПЗУ 22 в первый регистр 2 и поступает на вход запуска регистра 19 последовательных приближений. В начале каждого четного цикла на выходе Y ПЗУ 22 формируется сигнал записи во второй регистр 5, в который записывается код числа 2 . Импульсы с генератора 18 поступают на тактовьтй вход регистра 19 последовательных приближений и одновременно через элемент И 31 на первый вход записи третьего регистра 8. Под воздействием этих импульсов регистр 19 последов тельных приближений (РПП) с учетом состояний компаратора 7 подбирает за MiK импульсов генератора 18 на

своих выходах такой код, что

т.е.

цапэ UiOin .

a;-b;+cN; о.

()

причем

где а:

,9+ui,

-вес i-ro разряда ЦАП 3;

-вес i-ro разряда ЦАП 6;

i|j4 а, - идеальное значение веса

1-го разряда ЦАП 3;

Од - идеальное значение веса младшего разряда 1АП 3;

с - масштабный коэффициент; N; - код, подобранный РПП в четном цикле;

ui - ошибка задания веса i-ro , разряда.

Импульс с выхода счетчика 20, Который формируется в конце цикла, поступает через элемент И 28 на тактовый вход первого регистра 37 вычислителя 10 поправок и записывает в него кодГ ; .

В отличие от четного цикла в каж- дом нечетном цикле не формируется сигнал на выходе Y ПЗУ 22, поэтому не выполняется занесение кода во .второй регистр 5, и в нем остается код, записанный в предьщущем цикле, а в первьш регистр 2 импульсом с выхода элемента 25 задержки произ

водится запись кода числа 2

к-;

В остальном опоследовательность импульсов остается прежней. После за- -пуска регистр 19 последовательных приближений на своих выходах подби- :рает код по зависимости

Д- и jZ.aj-b;+cN, .0.

По окончании цикла на выходе первого блока 38 вычитания появляется

вычисленный код 1-1

cNj -а, +

-1

Z: -а+ aj + 1-, 4- 3 (2)

. , 3 4-1

1-1 1-1

+ 21Л;-a -bi+SI и; . Ь Импульс с вькода счетчика 20, ко торый проходит через элемент И 29, записывает этот код во второй ре- |Гистр 39 вычислителя 10 поправок, а додерлммре второго регистра 39 эаписьшает в третий регистр 40 вычислителя 10 поправок.

Таким образом, после первых шести циклов на выходах третьего регистра 40 имеется код Nj,а второго регистра ,39 - код N j . На выходе второго блока 41 вычитания появляется вычис- ленньш код

.., {-й;-«-2й,., )/с, (3) а на выходе сумматора 42, который вьтолняет операции сложения и деления на два

Ni-+А

N.

ui.,/c,

(4)

где N(j. - код ошибки (i - 1)-го весового коэффициента.

По окончании седьмого цикла на выходе первого блока 38 вычитания появляется вычисленный код N,- N; Ji i. А

-N j и импульс с выхода счетчика 20, который поступает через элемент И 29, записывает этот код во второй регистр 39, а код N,, переписывает в третий регистр 40 вычислителя 0 поправок. Одновременно импульс с выхода счетчика 20 проходит через элемент И 30 при наличии сигнала разрешения на вы

ходе Y ПЗУ 22 на тактовые входы регистров 44, и происходит передача кодов из младших регистров в следующие регистры по цепочке регистров 44

Таким образом, в младший регистр из группы 44 регистров записьгоается код с выхода мультиплексора 43, вы- |ЧисленньЕЙ сумматором 42 в предыдущем .цикле по формуле (4). В конце 2К+2 )цИкла импульс с выхода счетчика 2(3 проходат через элемент И 30 при наличии сигнала разрешения на выходе Y ПЗУ 22 на тактовые входы регистров из группы регистров 44 и производит последний сдвиг по цепочке регистров, в результате в этих регистрах сохраняются коды К разрядных ошибок. Одновременно этот импульс проходит через элемент 23 задержки

5

0

0

0

и элемент И 26 на счетный вход счетчика 21 и увеличивает его содержимое на единицу. -После этого устройство начинает вычисление поправок всех 2К - 1. кодовых комбинаций и запись их в ОЗУ 14. Сигналы с выходов Y, , Yj, Y, Y ПЗУ 22 блокируют прохождение импульсов с выхода счетчика 20 через элементы И 27 - 30 соответственно, сигнал с выхода Yj- ПЗУ 22 переключает мультиплексор 43 вычислителя поправок и как сигнал раз- решения поступает на вторые входы элементов И 33 - 35.

Импульс с выхода элемента 23 задержки, задержанный элементом 24 задержки на время установления устойчивого кода на выходе ПЗУ 22, проходит через элемент И 34 на вход записи регистра 47 сдвига и вход обнуления накапливающего сумматора 48. В регистр 47 сдвига записывается код с группы выходов ПЗУ 22, и устанавливается в нулевое состояние на- 5 капливающий сумматор 48. После этого импульс генератора 18 проходит через элемент И 33 на шестой вход управления S вычислителя 10 поправок. Если в старшем разряде регистра 47 сдвига имеется 1, то к содержимому сумматора 48 прибавляется соответствующая разрядная ошибка. Одновременно происходит передача содержимых регистров 44 в группе регистров и на вход накапливающего сумматора поступает соответствующая разрядная ошибка. Этот процесс повторяется К тактов генератора 18. После К-го такта импульс с выхода счетчика 20 проходит через элемент И 35 на вход записи ОЗУ 14 и по адресу с выхода ПЗУ 22 поправка, вычисленная по следующей зависимости

. N,pp.|. .Ыд;

записьшается в ОЗУ 14. Одновременно этот же импульс проходит через элемент 23 задержки и элемент И 26 на счетный вход счетчика 21 и ува0 личивает его содержимое на единицу, а импульс с выхода элемента 23 задержки, задержанный элементом 24 задержки на время установления устойчивого кода на выходе ПЗУ 22.,

5 проходит через элемент И 34 на вход записи регистра 47 сдвига и вход рб- :нуления накапливающего сумматора 48. В регистр 47 сдвига записывается новый код с группы выхй5

ов ПЗУ 22, а сумматор 48 устанавлиается в нулевое состояние, и опианный процесс повторяется. За 2к-1 иклов вычисляются и записываются ОЗУ поправки для всех кодовых коминаций,

В конце (2К + 2 + 1)-го цикла, после того как импульс выхода счетчика 20 пройдет через элемент И 35 на вход записи ОЗУ 14 и запишется поправка последней кодовой комбинации, импульс с выхода элемента 23 задержки проходит через элемент И 26 на счетный вход счетчика 21 и изме- няет его содержимое на единицу, устройство переходит в режим Преобразования. Сигнал с выхода Yg ПЗУ 22 переключает мультиплексор 13 и блокирует элементы 26, 31, 33, 34 и

35И, а сигнал с выхода инвертора

36разрешает прохождение импульсов с генератора 18 через элемент И 32, импульс генератора 18 проходит через элемент И 32 и поступает на второй вход записи первого регистра 2, второй вход записи третьего регистра 8 и вход чтения ОЗУ 14. В первый регистр 2 записывается преобразуемый код с выхода датчика 12 преобразуемых кодов, а в третий регистр

8 - код поправки, считанный с ОЗУ 14 по адресу, соответствзпощему преобразуемому коду, который поступает на адресные входы ОЗУ через мультиплексор 13.

В результате на выходе ЦАП 3 имеем напряжение

иц„пз g ct;aiy +,Z: ,

на выходе ЦАП 9

ицс,п,,о{;й; ,

на выходе аналогового сумматора 4

вых , ,

Сформированное напряжение на аналоговом сумматоре 4 сохраняется до появления импульса с следующего цикла преобразования, когда оно изменяется на новое, откорректированное аналогичным образом, напряжение. Момент появления этих импульсов определяется частотой генератора 18, а число преобразований устанавливается соотношением частот генераторов 17 и 18. После появления очередного импульса с генератора 17 все описанные действия повторяются.

872908

Формула изобретения

1. Цифроаналоговый преобразователь с автоматической коррекцией 5 нелинейности, содержащий блок управления, первый выход которого подключен к первому входу записи первого регистра, второй выход подключен к входу записи второго регистра,

0 третий выход подключен к первому

входу записи третьего регистра, четвертый выход подключен к вторым входам записи первого и третьего регистров , выходы с пятого по одиннадt5 цатый подключены соответственно к входам управления с первого по седьмой вычислителя поправок, первая группа выходов блока управления подключена к соответствующим первым ин20 формационным входам вычислителя поправок и к соответствующим первым информационным входам третьего регистра, вторая группа выходов подключена к соответствующим информационным

5 входам второго регистра и к соответствующим первым информационным входам первого регистра, вторые информационные входы которого подключены к соответствующим выходам дат30 чика преобразуемого кода, выходы подключены к соответствующим цифровым входам первого цифроаналогового преобразователя, аналоговый вход которого объединен с аналоговь ми

35 входами второго и третьего цифроаналоговых преобразователей и подключен к выходу исто- ника опорного напряжения , выход подключен к первому входу аналогового сумматора, второй вход

40 которого подключен к выходу третьего цифроаналогоЕого преобразователя, а выход является выходной шиной устройства и подключен к первому входу компаратора, выход которого подклю45 чен к входу блока управления, выходы второго и третьего регистров подключены к соответсгвуюшим цифровым входам соответственно второго и третьего цифроаналоговых преобразователей,

50 отличающийся тем, что, с целью повышения быстродействия, введены оперативное запоминающее устройство, переключатель, источник эталонного напряжения, мультиплексор,

55 адресный вход которого подключен к двенадцатому выходу блока управления, первые информационные входы подключены к соотвстствуюиим выходам датчика преобразуемого кода.

9-

вторые информационные входы объединены с соответствующими вторыми информационными входами вычислителя поправок и подключены к соответствущим выходам второй группы блока управления, выходы мультиплексора подключены к соответствующим адресным входам оперативного запоминающего устройства, информационные входы которого подключены к соответствующим выходам вычислителя поправок , выходы подключены к соответствующим вторым информационным входам третьего регистра, вход управления считьшанием подключен.к четвертому выходу блока управления, вход управления записью подключен к тринадцатому выходу блока управления, четырнадцатый выход которого подключен к управляющему входу переключателя, первый информационный вход которого подключен к выходу ист очника эталонного напряжения, второй информационный вход подключен к выходу второго цифроаналогового преобразователя, выход подключен к второму входу компаратора.

2. Преобразователь по п. 1, о т 1личаю1цийся тем, что блок .управления выполнен на первом генераторе тактовых импульсов, регистре последовательного приближения, первом и втором счетчиках, постоянном запоминающем устройстве, первом, втором и третьем элементах задержки десяти элементах И, инверторе, втором, генераторе тактовых импульсов, выход которого подключен к счетному входу первого счетчика, к первым входам шестого, седьмого и восьмого элементов И, к тактовому входу регистра последовательного приближения-, информационный вход которого является входом блока управления, а выход являются первой группой выходов блока управления, вход запуска подключен к выходу третьего элемента за- держки и является первым выходом блока управления, вход третьего элемента задержки объединен со счетным входом второго счетчика и подключен к выходу первого элемента И, первый вход которого объединен с входом второго элемента задержки и подключен к выходу первого элемента задержки, выход второго элемента задержки подключен к первому 1входу-девятого элемента И, вход

10

5

0

5

0

5

0

5

первого элемента задержки объединен с первыми входами второго, третьего, четвертого, пятого и десятого элементов И и подключен к выходу первого счетчика, вход обнуления которого объединен с входом обнуления Bi oporo счетчика и подключен к выходу первого генератора тактовых импульсов ,выходы второго счетчика подключены к соответствующим входам постоянного запоминающего устройства, группа выходов которого является второй 1 группой выходов блока управления, первый выход постоянного запоминающего устройст1;а подключен к второму входу второго элемента И и является четырнадцатым выходом блока управления, второй выход постоянного запоминающего устройства подключен к второму входу третьего элемента И и является вторым выходом блока управления, третий выход постоянного запоминающего устройства подключен к второму входу четвертого элемента И, четвертый выход постоянного запоминающего устройства подключен к второму входу пятого элемента И, пятый выход постоянного запоминающегоустройства подключен к вторым входам восьмого, девятого и десятого элементов И, шестой выход постоянного запоминающего устройства подключен к вторым входам первого и шестого элементов И, через инвертор - к второму входу седьмого элемента И, к третьим входам восьмого, девятого и десятого элементов И и является двенадцатым выходом блока управления, выход десятого элемента И является тринадцатью выходом блока управления, выход шестого элемента И является третьим выходом блока управления, выход седьмого элемента И является четвертым выходом блока управления, выходы второго, третьего четвертого, пятого элементов И,

пятый выход постоянного запоминающего устройства, выходы восьмого и девятого элементов И являются соответственно выходами с пятого по одиннадцатый блока управления.

3. Преобразователь по п. 1, от личающийся тем, что вычислитель поправок выполнен на пер- вом регистре, первом блоке вычитания, втором и третьем регистрах, втором блоке вычитания, сумматоре, мультиплексоре, группе из К послеовательно соединенных регистров.

где К -. число разрядов преобразуемого кода, элементе ИЛИ, элементе И регистре сдвига, накапливающем сумматоре, выходы которого являются выходами вычислителя поправок, вход обнуления объединен с тактовым входом регистра сдвига и является седьмым входом управления вычислителя пправок, тактовый вход подключен к выходу элемента И, первый вход кото рого подключен к выходу регистра сдвига, информационные,входы которо являются вторыми информационными входами вычислителя поправок, вход занесения информации объединен с вт рым входом элемента И, первым входо элемента ИЛИ и является шестым входом -правления вычислителя поправок второй вход элемента ИЛИ является четверть: - входом управления вычислителя поправок, выход подключен к певому тактовому входу первого регист из группы регистров и тактовым входам регистров с второго по К-й из группы регистров, входы обнуления :которых объединены с входами обну- ления второго и третьего регистров, вторым тактовым входом первого регистра из группы регистров и являются первым входом управления вычислителя поправок, выходы k-ro регистра из грзшпы регистров подключены к соответствующим информационным входам накапливающего сумматора и к соответствующим первым информационным входам мультиплексора, управляющий

0 матора, 15

вход которого является пятым входом управления вычислителя поправок, в.торые информационные входы подключены к соответствующим выходам сумматора, выходы подключены к соответствующим первым информационным вхо-. дам первого регистра из группы регистров, выходы которого подключены к соответствующим первым входам сум-

вторые входы которого подключены к соответствующим выходам второго блока вычитания, входы уменьшаемого которого подключены к соответствующим выходам третьего регистра, входы вычитаемого объединены с соответствующими информационными входами третьего регистра и подключены к соответствующим выходам второго регистра, тактовый вход которого объединен с тактовым входом третьего регистра и является третьим входом управления вычислите: поправок, информационные входы подключены к соответствующим выходам первого 5 блока вычитания, входы вычитаемого которого объединены с соответствующими вторыми информационными входами первого регистра из группы регистров, с соответствующими информационными входами первого регистра и являются первыми информационными входами вычислителя поправок, входы уменьшаемого подключены к соответствующим выходам первого регистра, тактовьй вход которого является вторым входом

0

0

5,

матора,

управления вычислителя поправок.

00001..

00000..

00000..

000 О О . .

00000..

О О О О О . .

О 00 О О ..

00000. 1 1 1 1,1.

.

,. 10

2К+2 +1 1 1 1 1 1 ... 1 1 1

2К+2 +2 00000...000 00001 1

11 0.01101 001 010001 000 001101 о 000 о о 1 о 1 001 000011 010 000011 01 100001 100 000011 101 00001 1

,9

10 000011 00001 1

1 1 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Устройство для формирования дуг и окружностей на экране телевизионного индикатора | 1990 |

|

SU1800476A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

Изобретение относится к области измерительной техники и может быть использовано в системах автоматического управления и гибридных вычислительных комплексах. Цель - повышение быстродействия цифроаналогового преобразователя с автоматической коррекцией нелинейности - достигается введением в устройство, содержащее блок 1 уп п равления, регистры 2, 5, 8, цифро- аналоговь1е преобразователи 3,6, 9, аналоговый сумматор 4, компаратор 7, вычислитель 10 поправок, источник 11 опорного напряжения, датчик 12 преобразуемого кода, дополнительных блоков: мультиплексора 13, оперативного запоминающего устройства 14, переключателя 15, источника 16 эталонного напряжения. Быстродействие повышено в К раз, где К - число корректируемых разрядов цифроаналогового преобразователя 3. 2 з.п. ф-лы, 3 ил. 1 табл. (Л

ti т

т

5

Составитель В. Перпгиков Редактор Е. Копча Техред Л.Сердюкова Корректор В . Бутяга

Заказ 7730/59 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

.

Фиг,Ъ

| Мажоритарный элемент | 1982 |

|

SU1045399A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микроэлектронные цифроаналоговые и аналого-цифровые преобразователи информации/Под ред | |||

| В.Б | |||

| Смолова | |||

| Л.: Энергия, 1976, с | |||

| Регулятор давления для автоматических тормозов с сжатым воздухом | 1921 |

|

SU195A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1987-01-30—Публикация

1985-02-20—Подача