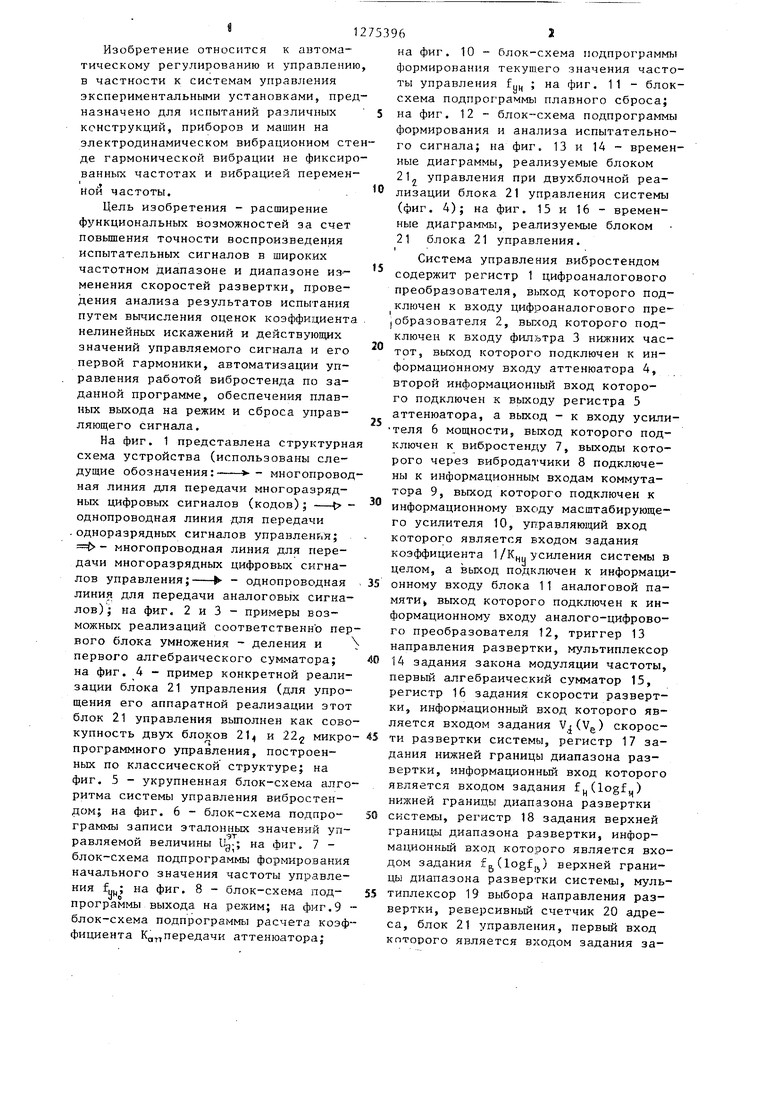

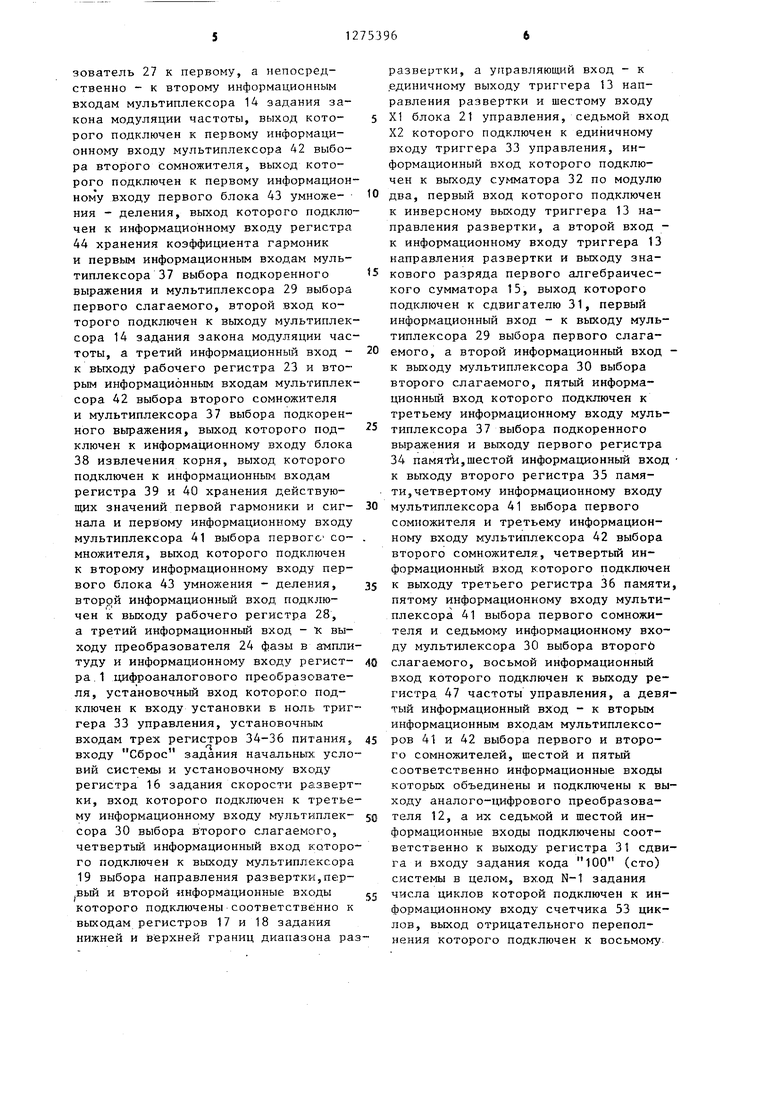

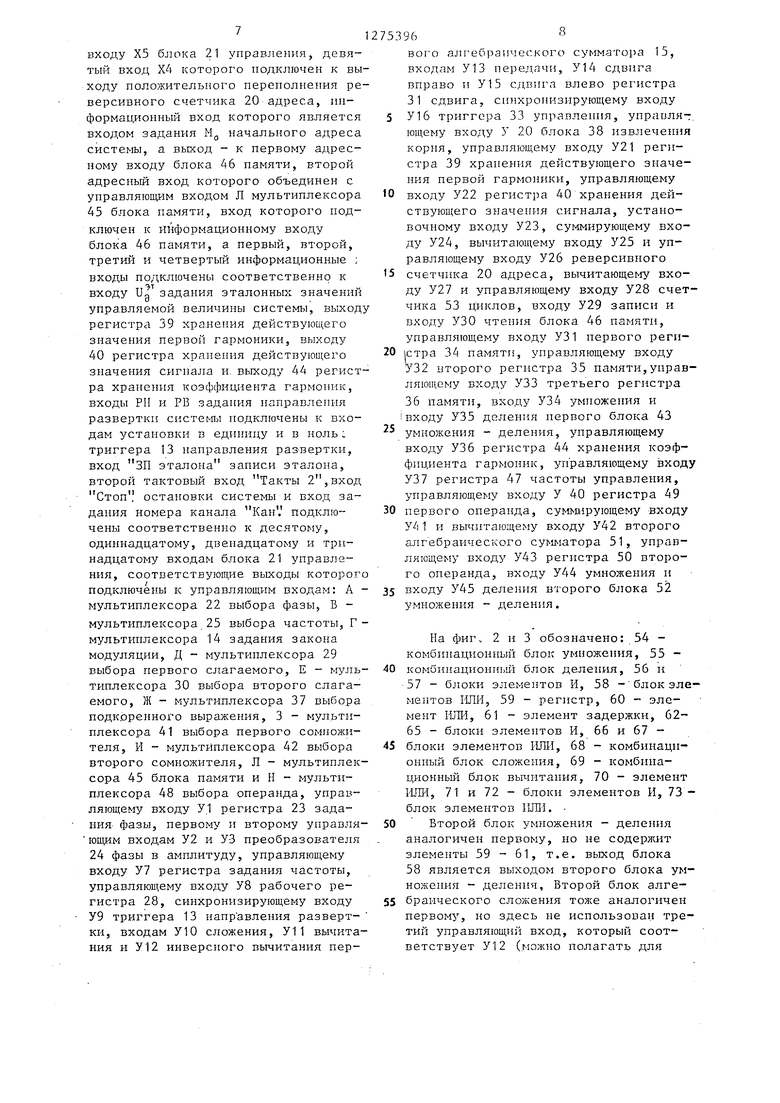

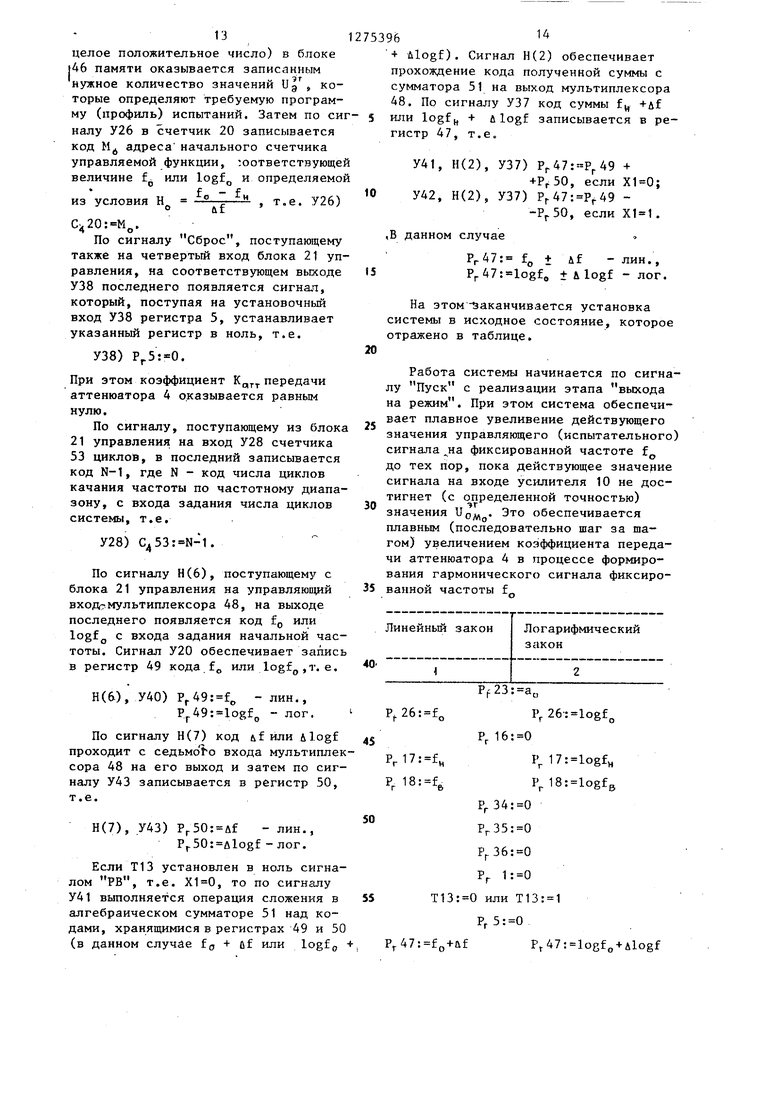

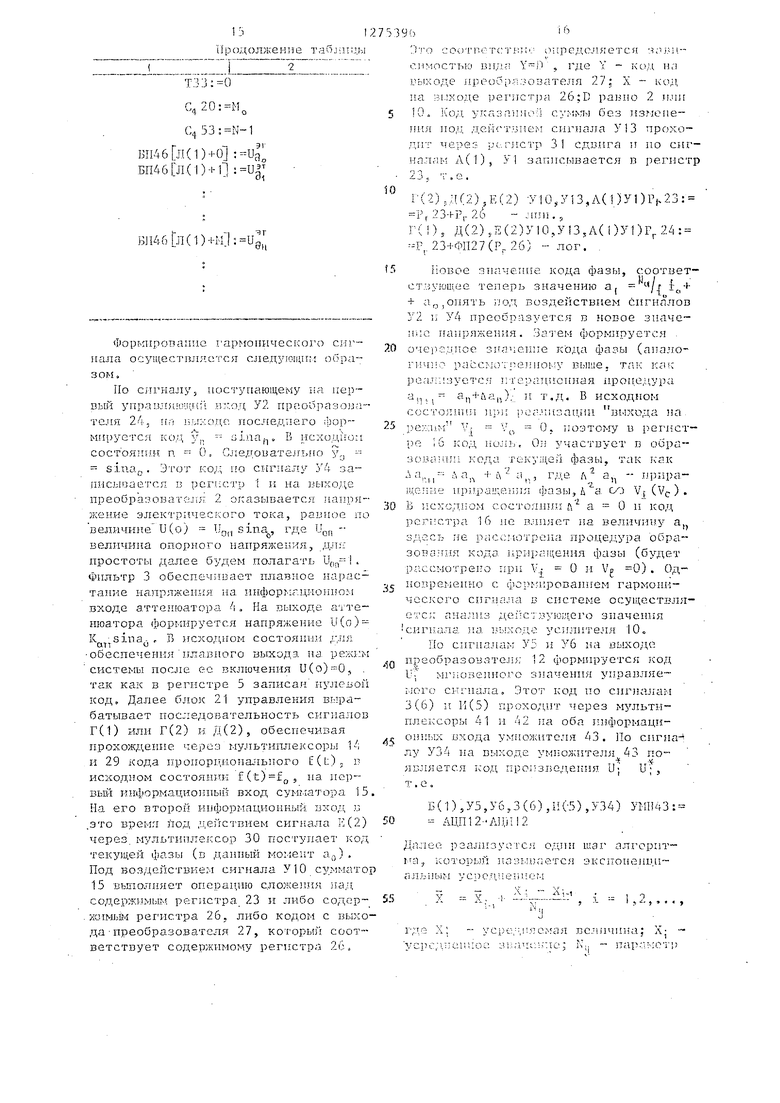

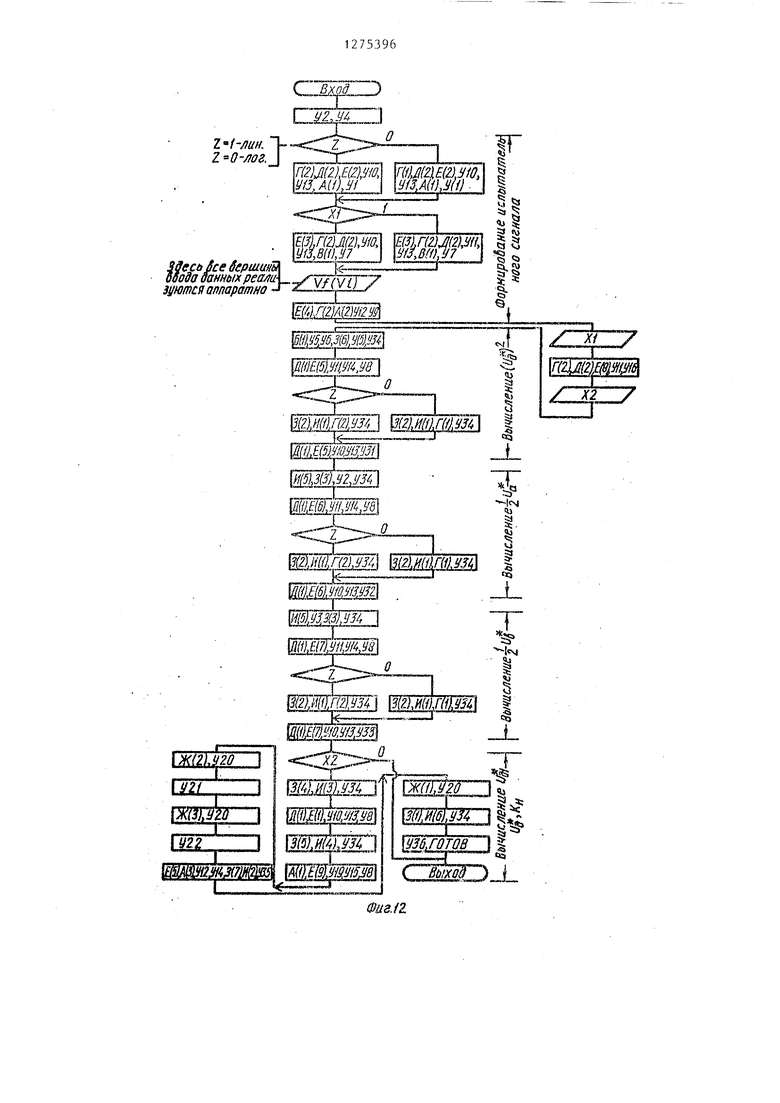

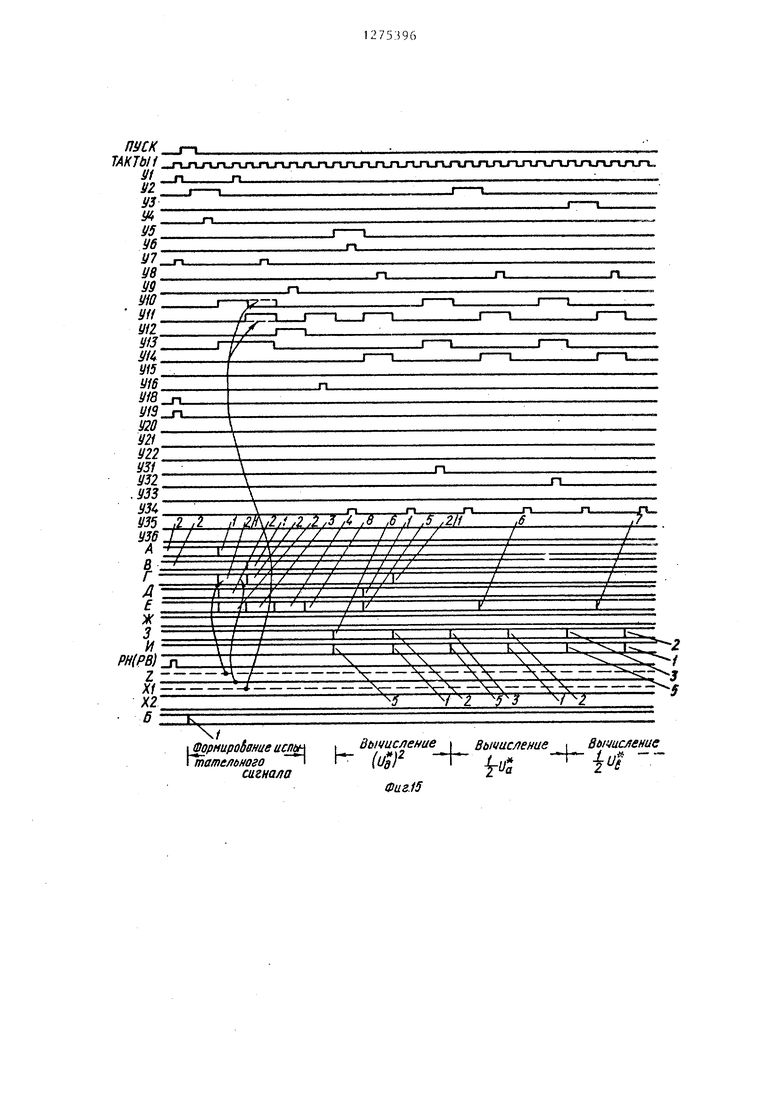

Изобретение относится к автоматическому регулированию и управлению в частности к системам управления экспериментальными установками, пред назначено для испытаний различных конструкций, приборов и машин на электродинамическом вибрационном сте де гармонической вибрации не фиксиро ванных частотах и вибрацией переменной частоты. Цель изобретения - расширение функциональных возможностей за счет повьшения точности воспроизведения испытательных сигналов в широких частотном диапазоне и диапазоне из-менения скоростей развертки, проведения анализа результатов испытания путем вычисления оценок коэффициента нелинейных искажений и действующих значений управляемого сигнала и его первой гармоники, автоматизации управления работой вибростенда по заданной программе, обеспечения плавных выхода на режим и сброса управляющего сигнала. На фиг. 1 представлена структурна схема устройства (использованы следущие обозначения: -- многопровод ная линия для передачи многоразрядных цифровых сигналов (кодов); - однопроводная линия для передачи .одноразрядных сигналов управле.нр1Я; Ф- многопроводная линия для передачи многоразрядных цифровых сигналов управления; - однопроводная линия для передачи аналоговых сигналов); на фиг. 2 и 3 - примеры возможных реализаций соответственно пер вого блока умножения - деления и первого алгебраического сумматора; на фиг. 4 - пример конкретной реализации блока 21 управления (для упрощения его аппаратной реализации этот блок 21 управления вьтолнеи как сово купность двух блоков 21 и 22 микро программного управления, построенных по классической структуре; на фиг. 5 - укрупненная блок-схема алго ритма системы управления вибростендом; на фиг. 6 - блок-схема подпрограммы записи эталонных значений управляемой величины Ug.; на фиг. 7 блок-схема подпрограммы формирования начального значения частоты управления на фиг. 8 - блок-схема подпрограммы выхода на режим; на фиг.9 блок-схема подпрограммы расчета коэф фициента К„.,передачи аттенюатора; на фиг. 10 - блок-схема подпрограммы формирования текущего значения частоты управления f„ц ; на фиг. 11 - блоксхема подпрограммы плавного сброса; на фиг, 12 - блок-схема подпрограммы формирования и анализа испытательного сигнала; на фиг. 13 и 14 - временные диаграммы, реализуемые блоком 21- управления при двухблочной реализации блока 21 управления системы (фиг. 4); на фиг. 15 и 16 - временные диаграммы, реализуемые блоком 21 блока 21 управления. Система управления вибростендом содержит регистр 1 цифроаналогового преобразователя, выход которого подключен к входу цифроаналогового пре0бразователя 2, выход которого подключен к входу фильтра 3 нижних частот, выход которого подключен к информационному входу аттенюатора 4, второй информационный вход которого подключен к выходу регистра 5 аттенюатора, а выход - к входу усилителя 6 мощности, выход которого подключен к вибростенду 7, выходы которого через вибродатчики 8 подключены к информационным входам коммутатора 9, выход которого подключен к информационному входу масштабирующего усилителя 10, угфавляющий вход которого является входом задания коэффициента 1/К. усиления системы в целом, а 1выход подключен к информационному входу блока 11 аналоговой памяти выход которого подключен к информационному входу аналого-цифрового преобразователя 12, триггер 13 направления развертки, мультиплексор 14 задания закона модуляции частоты, первьй алгебраический сумматор 15, регистр 16 задания скорости развертки, информационный вход которого является входом задания V.j(Vg) скорости развертки системы, регистр 17 заДания нижней границы диапазона развертки, информационный вход которого является входом задания fj(logfu) нижней границы диапазона развертки системы, регистр 18 задания верхней границы диапазона развертки, информационный вход которого является входом задания f dogfj,) верхней границы диапазона развертки систеьы, мультиплексор 19 выбора направления развертки, реверсивный счетчик 20 адреса, блок 21 управления, первый вход которого является входом задания закона Z (лин/лог) модуляции частоты системы, второй вход является входом Пуск запуска системы, третий вход является первым тактовым Такты 1

входом системы, а четвертый вход - s входом Сброс задания начальных условий системы, соответствующие входы блока 21 управления подключены к управляющим входам: У4 регистра 1 цифроаналогового преобразователя, Ю УЗ8, У 39 - регистра 5 аттенюатора, Б - коммутатора 9, У5 - блока 11 аналоговой памяти, Уб - аналого-цифрового преобразователя 12, У17 - регистра 16 задания скорости развертки, 15 У18 - регистра 17 зажания нижней границы диапазона развертки, У19 - регистра 18 задания верхней границы диапазона развертки, мультиплексора 22 выбора фазы, регистр 23 задания фазы,20 преобразователь 2А фазы в амплитуду, мультиплексор 25 выбора частоты, регистр 26 задания частоты, функциональный преобразователь 27, рабочий регистр 28, мультиплексор 29 выбора 25 первого слагаемого, мультиплексор 30 выбора второго слагаемого, регистр 31 сдвига, сумматор 32 по модулю два, триггер 33 управления, три регистра 34-36 памяти, мультиплексор 37 выборазо подкоренного выражения, блок 38 извлечения корня, регистр 39 хранения действующего значения первой гармоники, регистр 40 хранения действующего значения сигнала, мультиплексор 41 jj выбора первого сомножителя, мульти-. плексор 42 выбора второго сомножителя, первьй блок 43 умножения - деления, регистр 44 хранения коэффициента гармоник, мультиплексор 45 блока 40 памяти, блок 46 памяти, регистр 47 частоты управления, мультиплексор 48 выбора операнда, регистр 49 первого операнда, регистр 50 второго операнда, второй алгебраический сумматор второй блок 52 умножения - деления, счетчик 53 циклов, причем первый информа1щонный вход второго блока 52 умножения - деления подключен к первому информационному входу мультпплекзо

сора 48 выбора операнда, выходу регистра 49 первого операнда и первому информационному входу второго алгебраического сумматора 51, выход которого подключен к второму информационно-55 му входу мультиплексора 48 выбора операнда, выход знакового разряда втовторого алгебраического сумматора 51

подключен к пятому входу ХЗ блока управления, а второй информационньш вход - к выходу регистра 50 второго операпда и второму информационному входу второго блока 52 умножения - дделения, выход которого подключен к третьему информационному входу мультиплексора 48 выбора операнда, четвертьш информационньш вход которого подключен к выходу блока 46 памяти и информационному выходу системы,а пятый информационньш вход - к вьпсоду регистра 47 частоты управления,информационный вход которого подключен к информационным входам регистра 5 аттенюатора, первого и второго 49 и 50 операндов и выходу мультиплексора 48 выбора операнда, шестой,седьмой, восьмой и девятый информационные входы которого являются соответственно входом f Clogfo) задания начальной частоты, входом uf (ulogf) задания периода дискретности, входом К задания коэффициента пропорциональности закона управления и входом йКд задаппя приращения коэффициента передачи аттенюатора системы, десятый информационный вход - к выходу регистра 5 аттенюатора, одиннадцатый вход является входом U„д,зaдaния кода максимального значения напряжения на вькоде аттенюатора 4 системы, вход о задания нулевого кода которой подключен к первому информационному входу мультиплексора 30 выбора второго слагаемого, второй информационный вход которого подключен к инфopмaциoннo ry входу преобразователя 24 фазы в амплитуду и к выходу регистра 23 задания фазы, информационный вход которого подключен к выходу мультиплексора 22 выбора фазы первьш информационный вход которого подключен к выходу регистра 31 сдвига, первому информационному входу мультиплексора 25 выбора частоты, информационному входу рабочего регистра 28, и трех регистров 34-36 памяти, а второй информационный вход является входом q, задания начальной фазы системы, вход f Clogf) задания начальной частоты которой подключен к второму информационному входу мультиплексора 25 выбора частоты, выход которого подключен к ин-i формационному входу регистра 26 задания частоты, выход которого подключен через функциональный преобразователь 27 к первому, а непосредственно - к второму информационным входам мультиплексора 14 задания закона модуляции частоты, выход которого подключен к первому информационному входу мультиплексора 42 выбора BTOpioro сомножителя, выход которого подключен к первому информационному входу первого блока 43 умноже- ния - деления, выход которого подключен к информационному входу регистра 44 хранения коэффициента гармоник и первым информационным входам мультиплексора 37 выбора подкоренного выражения и мультиплексора 29 выбора первого слагаемого, второй вход которого подключен к выходу мультиплексора 14 задания закона модуляции частоты, а третий информационный вход к выходу рабочего регистра 23 и вторым информационным входам мультиплексора 42 выбора второго сомножителя и мультиплексора 37 выбора подкоренного выражения, выход которого подключей к информационному входу блока 38 извлечения корня, выход которого подключен к информационным входам регистра 39 и 40 хранения действующих значений первой гармоники и сигнала и первому информационному входу мультиплексора 41 выбора первого сомножителя, выход которого подключен к второму информационному входу первого блока 43 умножения - деления, второй информационньш вход подключен к выходу рабочего регистра 28, а третий информационный вход - к выходу преобразователя 24 фазы в амплитуду и информационному входу регистра.1 цифроанапогового преобразователя, установочный вход которого подключен к входу установки в ноль триггера 33 управления, установочным входам трех регистров 34-36 питанияj входу Сброс задания начальные; условий системы и установочному входу регистра 16 задания скорости развертки, вход которого подключен к третьему информационному входу ryльтиплeксора 30 выбора второго слагаемого, четвертьй информационный вход которого подключен к выходу мультиплексора 19 выбора направления развертки,пер|Вый и второй «нформационные входы которого подключены соответственно к выходам регистров 17 и 18 задания нижней и верхней границ диапазона разразвертки, а управляющий вход - к .единичному выходу триггера 13 направления развертки и шестому входу Х1 блока 21 управления, седьмой вход Х2 которого подключен к единичному входу триггера 33 управления, информационный вход которого подключен к выходу сумматора 32 по модулю два, первый вход которого подключен к инверсному выходу триггера 13 направления развертки, а второй вход к информационному входу триггера 13 направления развертки и выходу знакового разряда первого алгебраического сумматора 15, выход которого подключен к сдвигателю 31, первый информационный вход - к выходу мультиплексора 29 выбора первого слагаемого, а второй информационный вход к вьгходу мультиплексора 30 выбора второго слагаемого, пятый информационный вход которого подключен к третьему информационному входу мультиплексора 37 выбора подкоренного выражения и выходу первого регистра 34 памяти,шестой информационный вход к выходу второго регистра 35 памяти, четвертому информационному входу мультиплексора 41 выбора первого сомножителя и третьему информационHONry входу мультиплексора 42 выбора второго сомножителя, четвертый информационный вход которого подключен к выходу третьего регистра 36 памяти пятому информационному входу мультиплексора 41 выбора первого сомножителя и седьмому информационному входу мультилексора 30 выбора второгб слагаемого, восьмой информационный вход которого подключен к выходу регистра 47 частоты управления, а девятый информационный вход - к вторым информационным входам мультиплексоров 41 и 42 выбора первого и второго сомножителей, шестой и пятый соответственно информационные входы которых объединены и подключены к выходу аналого-цифрового преобразователя 12, а их седьмой и шестой информационные входы подключены соответственно к выходу регистра 31 сдвига и входу задания кода 100 (сто) системы в целом, вход N-1 задания числа циклов которой подключен к информационному входу счетчика 53 циклов, выход отрицательного переполнения которого подключен к восьмому

входу Х5 блока 21 управления, девятый вход Х4 которого подключен к выходу положительного переполнения реверсивного 20 адреса, информационньш вход которого является входом задания М начального адреса системы, а выход - к первому адресному входу блока 46 памяти, второй адресный вход которого объединен с управлягощ1- м входом Л мультиплексора А5 блока памяти, вход которого подключен к информационному входу блока 46 памяти, а первый, второй, третий и четвертый информационные ; входы подключены соответственно к входу Ug задания эталонных значений управляемой величины системы, выход регистра 39 хранения действующего значения первой гармоники, выходу 40 регистра хра 1ения действующего значения сигнала и. выходу 44 регистра хранения коэффициента гармошек, входы РП и РВ задания направления развертки систем подключены к входам установки в единицу и в ноль: триггера 13 направления развертки, вход ЗП эталона записи эталона, второй тактовый вход Такты 2,вход Стоп остановки системы и вход задания номера канала Кан. подключены соответственно к десятому, одиннадцатому, двенадцатому и тринадцатому входам блока 21 управления, соответствующие выходы которог подключе1 ы к управляющим входам: А мультиплексора 22 выбора фазы, В мультиплексора 25 выбора частоты, Гмультиплексора 14 задания закона модуляции, Д - мультиплексора 29 выбора первого слагаемого, Е - мультиплексора 30 выбора второго слагаемого, Ж - мультиплексора 37 выбора подкоренного выражения, 3 - мультиплексора 41 выбора первого сомножителя, И - мультиплексора 42 выбора второго сомножителя, Л - мультиплексора 45 блока памяти и Н - мультиплексора 48 выбора операнда, управ-ляющe ry входу У.1 регистра 23 задания фазы, первому и второму управляющим входам У2 и УЗ преобразователя 24 фазы в амплитуду, управляющему входу У7 регистра задания частоты, управляющему входу У8 рабочего регистра 28, синхронизирующему входу У9 триггера 13 направления развертки, входам У10 сложения, У11 вычитания и У12 инверсного вычитания пер5396

вого алгебраического сумматора 15, входам У13 передачи, У14 сдвига вправо и У15 сдвига влево регистра 31 сдвига, синхронизирующему входу 5 У16 триггера 33 управления, упрапля-т, ющему входу У 20 блока 38 извлечения корня, управляющему входу У21 регистра 39 хранения действующего значения первой гармоники, управляющему

О входу У22 регистра 40 хранения действу ощего значения сигнала, установочному входу У23, суммирующему входу У24, вычитающему входу У25 и управляющему входу У26 реверсивного

5 счетчика 20 адреса, вычитающему входу У27 и управляющему входу У28 счетчика 53 Циклов, входу У29 записи и входу УЗО чтения блока 46 памяти, управляющему входу У31 первого реги20 jcTpa 34 памят, управляющему входу У32 второго регистра 35 памяти,управляю1дему входу УЗЗ третьего регистра 36 памяти, входу УЗ4 умпожения и входу У35 деления первого блока 43

умножения - деления, управляющему входу УЗ6 регистра 44 хранения коэффициента гармоник, управляющему входу УЗ7 регистра 47 частоты управления, управляющему входу У 40 регистра 49

30 первого операнда, сум шрующему входу У41 и вычитающему входу У42 второго алгебраического сумматора 51, управляющему входу У43 регистра 50 второго операнда, входу У44 умножения и

5 входу У45 деления второго блока 52 умножения - деления.

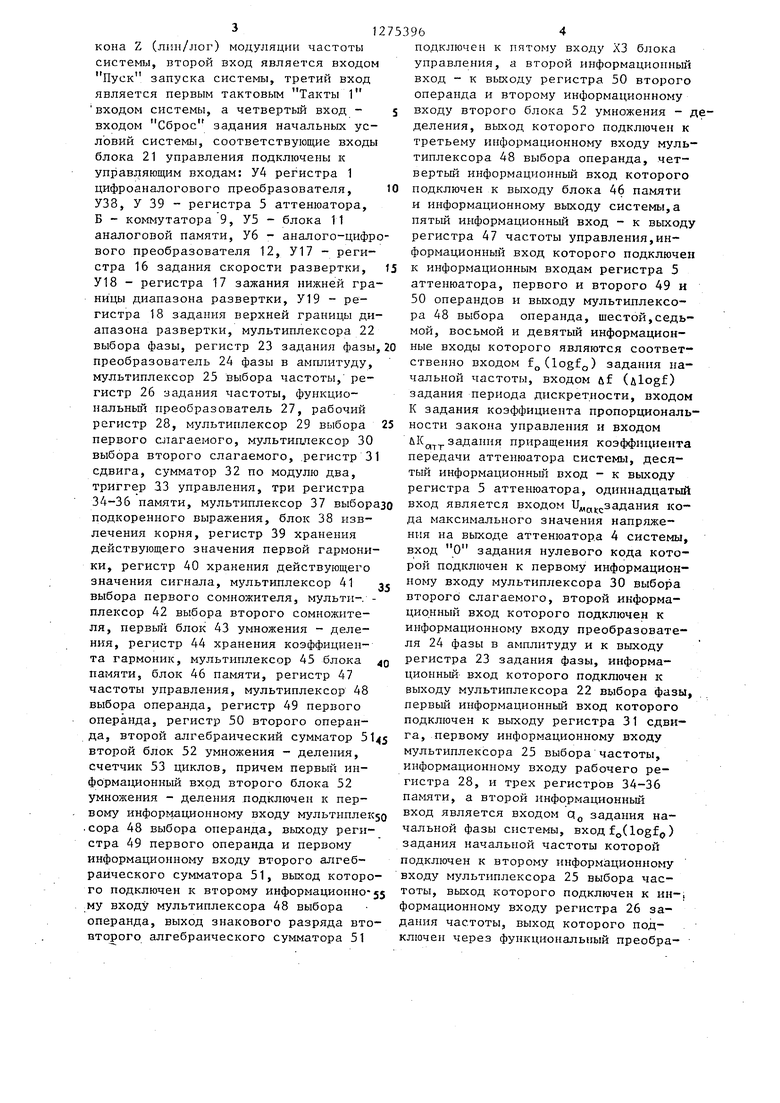

На фиг,. 2 и 3 обозначено: 54 комбинационный блок умножения, 55 40 комбинационньш блок деления, 56 и

57- блоки элементов И, 58 -блок элементов 1ШИ, 59 - регистр, 60 - элемент Ifflli, 61 - элемент задержки, 6265 - блоки элементов И, 66 и 67 -

5 блоки элементов 1-ШИ, 68 - комбинационный блок сложения, 69 - комбинационный блок вычитания, 70 - элемент 1иШ, 71 и 72 - блоки элементов И, 73 блок элементов 1ИШ.

0 Второй блок умножения - деления аналогичен первому, но не содержит элементы 59 - 61, т.е. выход блока

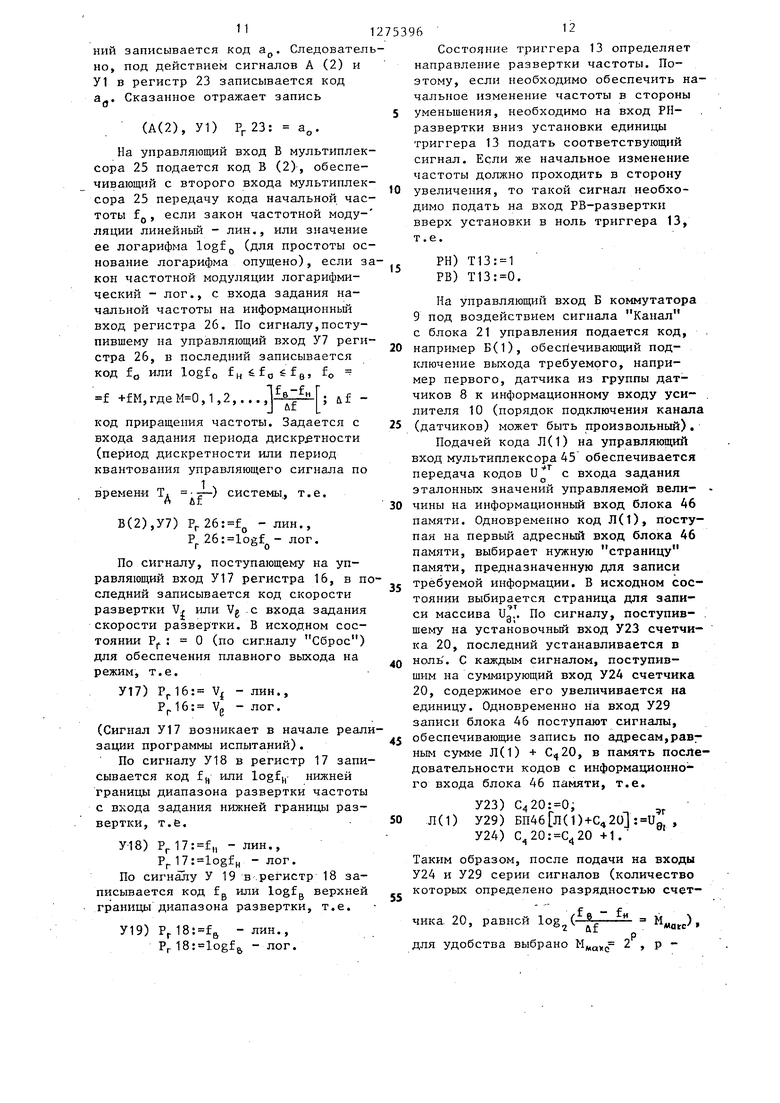

58является выходом второго блока умножения - деления. Второй блок алге5 браического сложения тоже аналогичен первому, но здесь не использован третий управляющий вход, который соответствует У12 (.можно полагать для простоты, что этот сигнал всегда р вен .нулю). Функциями системы управления ви ростендом являются: формирование и пытательного сигнала; анализ выход ного сигнала; управление процессом испытаний по заданной программе. При этом реализуется следующее аналитическое выражение: U(t) U(t) sin (cfCt)), где U(t) - мгновенное значение сигн ла на входе вибростенда; U(t) - текущая амплитуда колеба ний (закон амплитудной м модуляции); Cf(t) - текущая фаза колебаний, q(t)2nj f(C)dr f(t) - текущая частота коле(5ани (закон частотной модуляции) . Причем в формировании цифрового аналога у величины (cf(t)) здесь заключается формирование испытатель ного сигнала УП sin ( ё f; + a)«,oJN,,, о 0 где у,, - п-й дискретный отсчет функ ции у; N - количество значений ар: уме та на периоде; fg - частота дискретизации функ . ции f(t); f- - дискретные отсчеты функ ции f(t) или значение f(t) в конце i-ro шага интегрирования;Nfi - начальная фаза. a.Q ..„,™л.,.. О; О ЧС1 2 Для упрощения реализации вычисле ния аргумента для каждого п+1-го дис кретного отсчета а,, в системе реали зована итерационная процедура N (д + r)f ) . Пр1 реализации линёй 9 ного закона частотной модуляции в системе реализуется выражение fn., - f. -г при реализации логарифмического закона., antlOgj,(logj,f + Vj), где D - основание логарифма (обычно D 2 или D 10); 6 У - скорость изменения значений f (t); Vp - скорость изменения значений логарифма f(t). Анализ выходного сигнала проводится с целью вычисления оценок действующего значения первой гармоники, действующего значения сигнала, коэффициента гармоник и др., которые используются либо непосредственно (документируются) либо для реализации управления. При вьтолнении функции управления осуществляется отработка заданного закона изменения уровня выходного сигнала. Это обеспечивается в результате реализации одного из известных (может быть выбран в значительной степени произвольно в зависимости от араметров объекта управления) закоов управления коэффициентом передаи аттенюгтора, например, вида + К Iilii -l MiL и-- Jмaкc де К , , - коэффициент передачи атте нюатора; К - коэффициент пропорциональности;Ug. - эталонное значение управляемой величины (действующего значения сигнала) в i-й момент дискретизации управляющего сигнала; Ug. - экспериментальное значение управляемой величины в i-M такте дискретизации; макс максимально допустимое (возможное) значение Ug. Большинство функций системойреаизуется на одних и тех же средствах режиме разделения времени. Функционирование системы происхот следзтощим образом. По сигналу Сброс, поступающему вход установки в ноль триггера 33 на установочные входы регистров 16s 34, 35 и 36, триггер 33 уставливается в ноль, а в указанные рестры записывается нулевой код. На управляющий вход А мультиплекра 22 подается код А (2), обеспевающий передачу с второго входа льтиплексора. 22 кода начальной фас входа задания начальной фазы информационный вход регистра 23. сигналу, поступившему на управляий вход У1 регистра 23, в послед 1код а, Следовате записывается А (2) и но, под действием сигналов У1 в регистр 23 записывается код Сказанное отражает запись (А(2), У1) РГ 23: На управляющий вход В мультипле сора 25 подается код В (2), обеспе чивающий с второго входа мультипле сора 25 передачу кода начальной ча тоты fj,, если закон частотной моду ляции линейный - лин., или значени ее логарифма logf (для простоты о нование логарифма опущено), если кон частотной модуляции логарифмический - лог., с входа задания начальной частоты на информациоиньш вход регистра 26. По сигналу,посту пившему на управляющий вход У7 рег стра 26, в последний записывается . код fo или logfo fs-f f ,,1,2,..., код приращения частоты. Задается с входа задания периода дискретности (период дискретности или период квантования управляющего сигнала по времени Т. системы, т.е. В(2),У7) РГ 26; P|. лог. По сигналу, поступающему на управляющий вход У17 регистра 16, в п следний записывается код скорости развертки Vj или Vg с входа задания скорости развертки. В исходном состоянии Р|, : О (по сигналу Сброс) для обеспечения плавного выхода на режим, т.е. У17) V| - ЛИН., (Сигнал У17 возникает в начале реал зации программы испытаний). По сигналу У18 в регистр 17 запи сывается код f или нижней границы диапазона развертки частоты с входа задания нижней границы развертки, Т.Е. У18) - ЛИН., Pf. 17: logfH - лог. По сигналу У 19 в регистр 18 записывается код „ или logfn верхней границы диапазона развертки, т.е. У19) РГ18: fa - ЛИН., РГ18: logfa - лог. 96 Состояние триггера 13 определяет направление развертки частоты. Поэтому, если необходимо обеспечить начальное изменение частоты в стороны уменьшения, необходимо на вход РИ- развертки вниз установки единицы триггера 13 подать соответствующий сигнал. Если же начальное изменение частоты должно проходить в сторону увеличения, то такой сигнал необходимо подать на вход РВ-развертки вверх установки в ноль триггера 13, т.е. РН) РВ) . На управляющий вход Б коммутатора 9 под воздействием сигнала Канал с блока 21 управления подается код, например Б(1), обеспечивающий подключение выхода требуемого, например первого, датчика из группы датчиков 8 к информационному входу усилителя 10 (порядок подключения канала (датчиков) может быть произвольный). Подачей кода Л(1) на управляющий вход мультиплексора 45 обеспечивается передача кодов U с входа задания эталонных значений управляемой вели- чины на информационный вход блока А6 памяти. Одновременно код Л(1), поступая на первый адресньй вход блока 46 памяти, выбирает нужную страницу памяти, предназначенную для записи требуемой информации. В исходном состоянии выбирается страница для записи массива Ug.. По сигналу, поступив- . шему на установочный вход У23 счетчика 20, последний устанавливается в ноль. С каждьм сигналом, поступившим на суммирующий вход У2Д счетчика 20, содержимое его увеличивается на единицу. Одновременно на вход У29 записи блока 46 поступают сигналы, обеспечивающие запись по адресам,рав ным сумме Л(1) + , в память последовательности кодов с информационного входа блока 46 памяти, т.е. У23) C420: 0i . Л(1) У29) (1)+С420 : ид| , Таким образом, после подачи на входы У24 и У29 серии сигналов (количество которых определено разрядностью счетчика 20, равней log ( М«агс). р для удобства выбрано М, 2 Р целое положительное число) в блоке 46 памяти оказывается записанным нужное количество значений U|, которые определяют требуемую программу (профиль) испытаний. Затем по сиг налу У26 в счетчик 20 записывается код М адреса начального счетчика управляемой функции, :оответствующей или logf и определяемой величине f т.е. У26) из условия Н С420: М„. По сигналу Сброс, поступающему также на четвертый вход блока 21 управления, на соответствующем вьпсоде У38 последнего появляется сигнал, который, поступая на установочн1э1й вход У38 регистра 5, устанавливает указанный регистр в ноль, т.е. У38) . При этом коэффициент К передачи аттенюатора 4 оказывается равным нулю. По сигналу, поступающему из блока 21 управления на вход У28 счетчика 53 циклов, в последний записывается код N-1, где N - код числа циклов качания частоты по частотному диапазону, с входа задания числа циклов системы, т.е. Сд53: Н-1. По сигналу Н(6), поступающему с блока 21 управления на управляюпщй вход мультиплексора 48, на выходе последнего появляется код f или logfg с входа задания начальной частоты. Сигнал У20 обеспечивает запись в регистр 49 кода „ или logf,т. е. Н(&), У40) Рг49: „ - лин., P 49: logfg - лог. По сигналу Н(7) код uf или ilogf проходит с седьмо о входа мультиплек сора 48 на его выход и затем по сигналу У43 записывается в регистр 50, т.е. Н(7), У43) Рг50: д - лин., P 50: ulogf - лог. Если Т13 установлен в ноль сигналом РВ, т.е. , то по сигнсшу У41 выполняется операция сложения в алгебраическом сумматоре 51 над кодами, хранящимися в регистрах 49 и 50 (в данном случае fg + fif или logf 6 ulogf) . Сигнал Н(2) обеспечивает прохождение кода полученной суммы с сумматора 51 на выход мультиплексора 48. По сигналу УЗ7 код суммы ц +uf или logf + дlogf записывается в регистр 47, т.е„ У41, Н(2), У37) + +Рг50, если У42, Н(2), У37) Р, , если . ,В данном случае Рг47: fj, t л - лин., Pr47: logfo ± Л logf - лог. На этом-заканчивается установка системы в исходное состояние, которое отражено в таблице. Работа системы начинается по сигналу Пуск с реализации этапа выхода на режим. При этом система обеспечивает плавное увеливение действующего значения управляющего (испытательного) сигнала на фиксированной частоте f, до тех пор, пока действующее значение сигнала на входе усилителя 10 не достигнет (с определенной точностью) значения . Это обеспечивается плавным (последовательно шаг за шагом) увеличением коэффициента передачи аттенюатора 4 в процессе формирования гармонического сигнала фиксированной частоты „ Pf23: a,, Р,17:, Р. РГ Рг35: 0 РГ 0 или РГ Pr47: fp+uf P,47: log o-i-Alog 131 Продолжение .;, Izzinr тз;з: о , C453: N-1 1Я14б л(1)-|-0 ) (1) .П(1) Форкировапис гармонического с.нг-нала осзи|,естпляс1тся следуЮПцтм ofjpaзo, По сигналу5 иостЗг1аю1цему иа первый ynpaiuriiwuinfi 1ПГОД У2 npaoiSpaaojjaтеля 24. пл БЫХОДС; последтшго ;1)ор-М1)уется код у., - aina,, В исходиоа состояли.и п. 0 Сл€.дователь го у,, --- sina. Этот код по сгггналу У4 запнсыоается в регистр 1 и на ,е преобразователя 2 счсазывсАетс.я иатдтяжение электрпчес1;ого тока, раипое по вел.ичнне U(o) Ur,,, sina, где U,,,, - величина опорного напряжения, для простоты далее будем полагать U(,,/-1 . Фильтр 3 oбecпe rивaeт плавное иарастаике напряжения на информационном входе аттенюатора. 4. На БГз1ходе аттенюатора формируется напряжение U(o) К|., - sina. г Б исходном состоянии для обеспечения пла.вного выхода на pe:si;M системы после ее включения U(o)0, . так как в регистре 5 записан нулеБОЙ код. Далее блок 21 управления вь рабатывает последовательность сигналов Г(1) или Г(2) и Д(2), обеспечивая прохождение через мультиплексоры 14 и 29 кода пропорционального L(t); г исходном состоянии (ь)дэ па первый информационны вход сумматора 15 На его второй ипфорг-ациопный иход .и .это время под действием сигнала 1Х2) через мультиплексор 30 поступает код текуш.ей фазы (в данный момент ад). Под воздействием сигнала У10 суммато 15 вьшолняет операн.пю сложения ;чад coдepж Iмы регистра 23 и либо содер. жлмьм регистра 26. либо кодом с выхо да-преобразователя 27, ко1орый соответствует содержимому регистра 26 (,I h сос)тпет( (Мфедсляется riaj iС 1мостью Bi),i),;i Y iV Y - ко,ц на выходе преобразователя 27j X код на выходе ).ierncTi)a 26 ;D painio 2 n.uii 10. Код yKa3aiiiu-:i слммы без т зменепня под дей(твпем сигнала проходит через регистр 31 сдвига и по сигнпл, ЛСП, У1 записывается в регистр 142) ,Д(2).Е(2) У10,,У13,Л(1)У1)Р(.23: Р, 23-И,-2б лип., Г(), Д(2),Е(2)У10,У13,А(|)У1) -Р,. 23+ФП27(Р, 26) - лог. . Новое знггчение кода фазгз, соответствующее теперь значению aj i,-+ а г,, опять :.)од воздействием сигнплов У2 и У4 преобразуется в новое зпачеHi;e ггапряжения. формируется . оче)едное значение кода фазы (апалоГ1;ч ю рассг;огпен11оь у выше, тпк кги: реализуется птератиюнная процедура а,, ,j- a,-i-fia|,).; и т.д. В исходном cocToiunin iipii рц;-л1 зациц выхода на pev:iiM V - , и. поэтому в ретист- ре б код ноль. Оп участвует п образованим кода теку;дей фазы, так как п l 11 РИра1цепие нрираи;е}1ия фазы, Да со Vf (Vj-) . В исходпом состоянии А а О и код рсг1;стра 16 не в.:иьчет на величи у а, здесь не рас{;мотрепа процедура образоваг-гия кода прирч-лг ения фазы (будет рассмотрено при V О и Vj 0). Одповремепно с фср:-;ироваппем гармоничес1сого сигна,; в системе осуществляется дейс; ByioiJiero значения сигнала iia, усилителя 10. По сигналам У5 и У5 на выходе преобразовдтел ; 12 формируется; 1сод Uj г.пновепного ззкпчепия управляемого сигнала. Этот код по сигналаг-i 3(6) и 11(5) проходит через мзльтнплексоры 41 п 42 па оба информационных входа умножителя 43. 1о сигналу УЗ4 па выходе умнолситчзля 43 по™ является код ,1ения U; U; , т. е о Б(1),У5,Уб,3(б),),У34) УШ ;3:- АЦП12-Л1Ц112 Далее p3ajn;3yeTCH один mai алгорпт- га, который называется экспоненциальным ус)е,п, , i-i . I 1 , f текуще .усреднения, Nj; значение частоты управляемого сигнала. При этом блок 21 управления вырабатывает сигналы Д(1), по которому , код с выхода умножителя 43 через мультиплексор 29 поступает на первый информационньй вход сумматора 15; по сигналу Е(5) код с регистра 34 (в ис содном состоянии ноль) через мультиплексор 30 поступает на второй вход сумматора 15, где по сигналу У11 реализуется операция вычитания. Полученный код разности при прохожде нии через регистр 31 сдвига под воздействием сигнала У14 сдвигается на R разрядов вправо (так реализуется операция деления на 2 ). Полученный код с выхода регистра 31 сдвига под действием сигнала У8 записывается в рабочий регистр 28, т.е. Д(1),Е(5).У11,У14,У8) Р 28г (УМН43. -Р,34)-2- Под действием сигнала 3(2) на второй информационный вход умножителя 43 через мультиплексор 41 посту пает ранее полученный код с выхода регистра 28. На первый информацион ный вход умножителя 43 через мультиплексор 42 по сигналу И(1) поступает код через мультиплексор 14, либо с выхода регистра 26,если сформирован сигнал Г(2), либо с выхода преобразователя 27, если сформирован сигнал Г(1). По сигналу У34 в умножителе 43 вьтолняется операция умножения, т.е. 3(2), И(1),Г(2),У34) УМН43: РГ 28-Р 26 - ЛИН., 3(2),Й(1),Г(1),У34) УМН43: Рг28 ФП27(Рг26) - лог. Затем под действием сигналов Д(1), Е(5), У10, У13, У31 реализуется операция сложения кода, хранящегося в регистре 34 (проходит на сумматор 15 через мультиплексор 30), и кода, хранящегося в блоке 43 (проходит на сумматор 15 через мультиплексор 29), результат, сложения, проходя без изменения через регистр сдвига, записьшается в регистр 34. Таким образом в регистре 34 накапливается код (Ug) квадрата действующего значения управляемого сигнала, т.е. Д(1),Е(5),У10,У13,У31) Рг34 + УМН43 6 18 Периодически (по сигналам, поступающим на второй тактовый вход Такты 2 блока управления, период следования которых определяется требуемым временем выходов на режим) блок 21 управления вырабатывает последовательность управляющих сигналов, по которым реализуется сравнение действующего значения управляемого сигнала Ugj,c эталоном Ug Мд..|.на фиксированной частоте. Если при зтом окажется, что Ug Quj система увеличивает коэффициент передачи аттенюатора 4 на фиксированную величину л К реализуется итерационная процедура Коп;,Г с-п-Л Если же U, Ug , то система переходит к реализации основной задачи: отработка программы (профиля) испытаний. Указанное реализуется следующим образом. По сигналу УЗО из ячейки памяти, хранящей эталонное значение Ugj, действующего значения напряжения для частоты f , блока 46 памяти считывается код Ug . Этот код ПО сигналам Н(4) и У43 записывается в регистр 50, т.е. УЗО, Н(4), У43 (1)+Мв. По сигналам Ж(3) и У20 из содержимого регистра 34 извлекается корень квадратный в блоке 38 (код поступает через мультиплексор 37). По сигналу У22 код действующего значения управляемого сигнала переписывается из блока 38 в регистр 40, т.е. Ж(3), У20) БК38: - 1Р 34, У22) . Далее по сигналу Л(3) и У29 (код в счетчике 20 не меняется) в ячейку памяти с адресом .Cn(3)+Mj,записывается код текущей величины действующего значения Ug управляемого сигнала. После этого по сигналам УЗО, Н(4) и У40 код Ug записывается в регистр 49, т.е. Л(3), У29) (3), УЗО,Н(4).У40) Рг49: БП461Л(3)-4-м;. По сигналу У42 в алгебраическом сумматоре 51 реализуется операция вычитания. По знаку разности Р, 49 - Р.50, Т ifг г т.е. определяется выполнение условия . Если UgJ, 0 (знак разности плюс), система переходит к реализации программы испы таний. Если же , то блок 21 управления вырабатывает сигналы, обеспечиваюицш приращение значения По сигналам Н(9), У43 в регистр 50 через мультиплексор 48 заносится код дКд-, а по сигналам Н(10), У40 в регистр 49 из регистра 5 через мультиплексор 48 заносится код , (в исходном состоянии Кд 0), т.е Н(9), У43 Р, 50: лК„,„ Н(10), У40 . По сигналу У41 в сумматоре 51 реали зуется операция сложения. Код полученной суммы по сигналу У43 заносит ся в регистр 50, т.е. У41, У39) + . При этом происходит увеличение К на величину ЛК. . Гармонический си нал той же фиксированной частоты f но большого уровня по сравнению с пр дыдущим циклом, продолжает -поступать на вибростенд. Аналогично описанному в регистре 34 на1 апливается новое значение Ug. которое затем сравнивается с эталоном и т.д. до выполнения условия U8Mo-u|L OПри этом система начинает реализо вать заданную программу испытаний. Блок 21 управления вырабатывает сигнал У17, по которому в регистр 16 заносится код V или Vg. Система продолжает формирование гармонического сигнала. При этом блок 21 управления вырабатывает сигналы У2 и У4, обеспечивая занесение в регистр 1 очередного кода мгновенного значения гармонического сигнала, т.е. У2, У4) PJ. (Рг23); и Г(2) или Г(1), Д(2), Е(2), У10, У13, А(1)у У1, обеспечивая как и ранее реализацию операции сложения,т.е Г(2),Д(2),Е(2),У10, У13,А(1)У1) . + - ЛИН. Г(1),Д(2),Е(23,У10,У13,А(1)У1) Р,.(Р,.26) - лог. Под действием сигнала Е(3) код V ил Vg с вькода регистра 16 через мульти плексср 30 поступает на второй инфор мационный вход сумматора 15. В это же время по сигналам Г(2) и Д(2) на 9620 первый информационный вход сумматора 15 через мультиплексоры 14 и 29 поступает код текущего значения частоты fy или логарифма частоты logf. По сигналу У10 сумматор 15 реализует операцию сложения. Код полученной суммы без изменения по сигналу У13 проходит через регистр 31 сдвига и по сигналам В(1), У7 записывается в регистр 26, т.е. Е(3),Г(2),Д(2),У10,У13,В(1)У7) Рг26: Рг26 + . Очевидно, что содержимое регистра 26 определяет приращение кода фазы, а Содержимое регистра 16 - приращение приращения кода фазы гармонической функции. То есть под действием указанной последовательности управляющих сигналов реализуются две итерационные процедуры вида ап + a, ntl П П Г141 Увеличение содержимого регистра 26 происходит только при условии, когда триггер 13 направления развертки находится в нулевом состоянии. В противом случае (когда триггер 13 в единице) вместо сигнала У10 на сумматор 15 подается сигнал У11. При этом реализуется операция вычитания, т.е. Е(3),Г(2),Д(2),У11,У13,В(1),У7)Рг26: Рг.26 - Рг16. .При такой последовательности управляющих сигналов реализуется развертка частоты гармонического сигнала в сторону уменьшения частоты. Исходное состояние регистра 13 определяется сигналами РН и РВ. Текущее состояние триггера определяется следующим образом. Если предьщущее состояние триггера 13 - ноль, ;то сигнал с единичного выхода триггера обеспечивает прохождение через мультиплексор 19 кода f или logfg в регистре 18. Если предьщущее состояние триггера 13 - единица, то сигнал с его единичного выхода обеспечивает прохождение через мультиплексор 19 кода ff, или logf с регистра 17. По сигналу Е(4) этот код проходит через мультиплексор 30 на второй информационный вход сумматора 15. На первый информационный вход этого сумматора 15 в это время по сигналам Г(2) и Д(2) через мультиплексоры 14 и 29 поступает код с выхода регистра 26. По сигналу У12 на сумматоре 15 реализуе ся операция инверсного вычитания. Выход знакового разряда этого сумматора 15 и определяет текущее состояние триггер 13, в которое он устанав ливается по сигналу У9, т.е. edли , тоЕ(4),Г(2),Д(2),У12,У9 Т13: (Рг-18-Р 26); если , тоЕ(4),Г(2),Д(2),У12,У9 Т13:(Р 17-Р 26). В процессе формирования модулированного по частоте гармонического сигнала системой осуществляется срав нение значений текущей частоты f, и текущей частоты управления fy,. Напом ним,что fijM м здесь М 1,2,3,..., При достижении очередно го значения fy блок 21 вырабатывает сигналы, обеспечивающие вычисление декоторых параметров управляемого сигнала (действующего значения первой гармоники U( , действующего зна чения сигнала Ug, коэффициента гармо ник К) и реализацию функции управления. Отмеченные операции системой реализуются периодически с периодом дискретности Тд T-F . Указанные , А Едействия инициируются единичным соетоянием триггера 33. Как уже отмечалось, его исходное состояние ноль. Текущее состояние определяется соотнош -нием содержимых регистров 26 и 47. Для сравнения указанных величин блок 21 управления вырабатывает сигналы Г(2), Д(2) и Е(8), по которым сигналы с выходов регистров 26 и 47 поступают на информационные входы алгебраического сумматора 15, где по сигналу У11 реализуется операция вычитания. Знак разности с вькода знакового разряда сумматора поступает на второй вход сумматора 32 по модулю два. На его первый вход постоянно подается инверсное значение состояния триггера 13 (триггер 13 в данный момент не меняет свое состояние, так как отсутствует сигнал У9) Результат сложения по модулю два ука занных величин по сигналу У16 записывается в триггер 33, т.е. Г(2),Д(2),Е(8),У11,У16)ТЗЗ: T13®sign (Pj. 26-Рг47), здесь© - знак суммы по модулю два Параллельно с формированием гармонического сигнала, как и ранее,система проводит анализ управляемого сигнала (дискретный эквивалент которого по сигналам У9 снимается с выхода аналого-цифрового преобразователя 12). Процедура вычисления квадрата действующего напряжения уже описана. Поэтому здесь приведем лишь формализованное ее описание: Б(1),У5,У6,3(6),И(5),У34) УМН43: АЦП12;.АЦП12; Д(1),Е(5),У11,У14,У8) (УМН43-Р, 34) 3(2),И(1),Г(2),У34) УМН43: Рг28-Рг26 - ЛИН. 3(2),И(1),Г(1),У34) УМН43: Р 28-ФП27(Рг 26) - лог.; Ц(1),Е(5),У10,У13,У31) Pf34: + УМН43 Далее система вычисляет мнимую ;Ug и действительную Цц составляющие амплитуды первой гармоники. При этом используется преобразование Фурье. При вычислении U системой реализуются следующие операции. По сигналу И(5) код с выхода преобразователя 12 поступает на первый информационный вход умножителя 43. На его второй р1нформационный вход по сигналу 3(3) серез мультиплексор 41 поступает код с выхода преобразователя 24 фазы в амплитуду, который по сигналу У2 вырабатывает код функции sin от аргумента, записанного в регистре 23. По сигналу У34 в умножителе формируется код произведения указанных величин, т.е. И(5),3(3),У2,У34) УМН43: АЦП12-ПФ24 (sin Рг23). Далее, как и ранее, реализуется алгоритм экспоненциального усреднения. По сигналу Д(1) код с выхода умножителя 43 через мультиплексор 29 поступает на первый информационный вход сумматора 15. На его второй информационный вход по сигналу Е(6) через мультиплексор 30 поступает код с регистра 35 (в исходном состоянии ноль). По сигналу У11 реализуется операция вычитания. Полученный код разности при прохождении через регистр 31 сдвига под воздействием сигнала У14 « сдвигается вправо на R разрядов (код 2умножается на 2). Полученный код с выхода регистра 31 сдвига под деист вием сигнала У8 записывается в рабо чий регистр 28, т.е. Д(1), Е(6),У11,У14,У8) (УМП43-Р 35)- 2Под действием сигнала 3(2) на второ информационный вход умножителя 43 через мультиплексор 41 поступает ра нее полученный код с выхода регистр 28. На первый информационный вход умножителя 43 через мультиплексор 42 по сигналу И(1) поступает код че рез ryльтиплeкcop 14, либо с выхода регистра 26, если сформирован сигнал Г(2), либо с выхода преобразователя 27, если сформирован сигнал Г(1). П сигналу У34 в умножителе 43 выполня ется операция умножения, т.е. 3(2),И(1),Г(2),У34 УМН43: Р. - ЛИН. 3(2),И(1),Г(1),У34) УМН43: Р 28--ФП27(Р(26) -лог. Затем под действием сигналов Д(1), Е(6), У 10, У13, У32 реализуется опе рация сложения кода, хранящегося в регистре 35 (проходит на сумматор 15 через мультиплексор 39), и коца хра нящегося в блоке 43 (проходит на сусумматор 15 через мультиплексор 29) результат сложения, проходя без изме нения через регистр 31 сдвига, записывается в регистр 35. Таким образом в регистре 35 накапливается код Ug .мнимой составляющей амплитуды первой гармоники. Д(1),Е(6),У10,У13,У32) Р 35: Р 35+УМН43. Вычисление U осуществляется аналогично рассмотренному вьше с той лишь разницей, что с преобразователя 24 снимается код функции cos, а не sin и что результат накапливается в регистре 36, т.е. И(5),УЗ,3(3),У34) УМН43: / АЦП12 ПФА24 (cos ); Д(1),Е(7),У11,У14,У8) (УМН43-Р.,36) 2 ГЗ(2),И(1),Г(2),У34) I Р,.28.-Рг26 - ЛИН., 3(2),Й(1),Г(1),У34) УМН43: ФП27(Р|.23) - лог.; 96 Д(1),Е(7),У10,У13,УЗЗ) Р, + УМЛ43. Так накапливается код у U. Повторяя указанную последователь-ность операций, система обеспечивает непрерывное формирование испытательного сигнала: гармонический сигнал с линейным или логарифмическим законом частотной модуляции (частньш случай - с фиксированной частотой) и анализ (получение оценок квадрата действующего значения управляемого сигнала, действительной и мнимой составляющей амплитуды первой гармоники). Кроме того, как уже отмечалось, периодически, с периодом дискретности Т. система осуществляет вычисление действующих значений сигнала и его nepBofi гармоники и коэффициента нелинейных искажений, и реализует функцию управления . Это выполняется при сравнении значений текущей частоты f и текущей частоты управления сигналу с триггера 33 управления, поступающему в блок 21 управления. При этом блок 21 управления вырабатывает сигналы 3(4) и И(3), по которым код с регистра 35 через мультиплексоры 41 и 42 поступает на оба информационных входа умножителя 43, где по сигналу У34 реализуется операция умнот.е. жения 3(4),И(3),У34 УМН43: Рр.. Далее по сигналу Д(1) код квадрата мнимой составляющей амплитуды первой гармоники через г-гультиплексор 29 поступает на первый информационный вход сумматора 15. На его второй информационный вход по сигналу Е(1) через мультиплексор 30 поступает код нуля. По сигналу У10 реализуется операция сложения (). По сигналу У13 код полученной суммы проходит без изменений через сдвигатель 31 и по сигналу 18 записывается в ле- гистр 28 (здесь операции, вьшолняеые по сигналам Д(1), Е(1), У10, У13, не имеют самостоятельной функциональной нагрузки. С их помощью лишь обесечивается передача кода с выхода множителя 43 на вход регистра 28), Д(1),Е(1)У10,У13,У8) РГ 28: УМН43. Затем по сигналам 3(5) и И(4) код с выхода регистра 36 через ьгультипле соры 41 и 42 поступает на оба информ ционных входа умножителя 43, где по сигналу У34 реализуется операция умножения , т. е, 3(5),И(4),У34 УМН43: Р;.,.36. По сигналу Д(1) код полученного прризведения с выхода умножителя 43 поступает через мультиплексор 29 на первый информационный вход сумматора 15, На его второй вход по сигналу Е(9) через мультиплексор 30 поступае код с выхода регистра 28. По сигналу У10 сумматор 15 реализует операцию сложения. Полученный код суммы, проходя (по сигналу У15) через регистр 31 сдвига, сдвигается на два ра13ряда влево (умножается на четыре) и по сигналу У8 записывается в регистр 28, т.е. Д(1),Е(9),У10,У15,У8) Pj. Х(РГ 28 + УМН43). Далее по сигналу Ж(2) код с вых:ода регистра 28 поступает через мультиплексор 37 на блок 38 извлечения корня, где по сигналу У20 реализуется функция извлечения корня квадратного, т.е. Ж(2), У20) ВК38: - Р 28. Полученный код действующего значения первой гармоники сигнала (напомним: и,э Ц„/. и,„ (2U,)+(2U6)) с выхода блока 38 по сигналу У21 записьшг,ется в регистр 39, т.е. У21) Рр39: БК38, Действующее значение управляемого сигнала вычисляется под действием следующих сигналов: по сигналу Ж(3) код квадрата действующего значения, накопленный ранее в регистре 34, подается через мультиплексор 37 на вход блока 38, где под действием сиг нала У20 выполняется операция извлечения корня квадратного, т.е. Ж(3), У20) БК38: Р 34. Полученный код действующего значения сигнала с выхода блока 38 по сигналу У22 заносится в регистр 40, т.е. БК38. Коэффициент нелинейных искажений, . .Ги§-и определяемый по формуле К, Н цГ«100, вычисляется под действием следующих управляющих сигналов. По сигналу Е(5) код с регистра 34 поступает на второй информационный вход сумматора 15. На его первый вход подается код с выхода регистра 28 (под действием сигнала Д(3). По сигналу У12 в алгебраическом сумматоре 15 реализуется операция инверсного вычитания (от содержимого регистра 34 отнимается содержимое регистра 28). Код полученной разности проходит через сдвигатель 31 (по сигналу У13) без изменения и по сигналу 3(7) поступает на второй информационный вход умножителя - делителя 43. На его первый вход по сигналу И(2) поступает код с регистра 28. По сигналу У35 реализуется операция деления,т.е. . Е(5),Д(3),У12,У13,3(7)И(2),У35) УМН43: (). Код полученного частного по сигналу Ж(1) поступает через мультиплексор 37 на вход блока 38, где по сигналу У20 реализуется операция извлечения . корня квадратного, т.е. Ж(1), У20) БК38: л|уШ43. По сигналу 3(1) на второй вход умножителя 43 через мультиплексор 41 подается, код с выхода блока 38, а на первый вход - код 100 через мультиплексор 42 по сигналу И(6). По сигналу У34 в умножителе 43 реализуется операция умножения. Код полученного произведения по сигналу У36 записывается в регистр 44, т.е. 3(1), И(6), У34) УМН43: БК38.100; УЗ6) Рр44: УМН43. Каждому значению частоты управления ц поставлен в соответствие код в счетчике 20. При увеличении значения fjjj, на ftf код в счетчике 20 увеличивается на единицу. Это происходит если триггер 13 направления развертки установлен в ноль. Если триггер 13 установлен в единицу,то при уменьшении значения на & f (или logf на ilogfjj) код в счетчике 20 уменьшается на единицу. Такое увеличение кода в счетчике 20 осуществляется по сигналу У24. По сигналу У25 осуществляется уменьшение кода в счетчике 20 на единицу. Следовательно, по сигналам У29 в соответствующие страницы памяти по выбранным адресам могут быть записаны коды с регистров 39, 40 и 44 (это производится без изменения коДа в счетчике 20), т.е. Л(2),У29)БП4бГл(2) : Рг39; Л(3),У29)(3)+С420 Л(4),У29)(4)+С4 44. После получения оценок параметров управляемого сигнала реализуется выбранный алгоритм управления (в каждой точке fu, коэффициентом передачи аттенюатора. По сигналам Л(3 УЗО текущий код Ug. считается из соответствующей ячейки памяти блока 46 По сигналу Н(4) Он поступает через мультиплексор 48 на входы регистров 5, 47,49 и 50. По сигналу У43 указанный код записывается в регистр 50, т.е. Л(3),УЗО,),У43Рг50: БП4б Л(3)+С4 Затем по сигналам Л(1), У24 или У25 и УЗО из соответствующей ячейки памяти блока Дб считывается код эталонного значения f (У25 уменьшает а У24 увеличивает содержимое счетчи ка 20 на единицу). По сигналам Н(4) и У40 этот код через мультиплексор 48 записывается в регистр 49, т.е. Л.(1),У25/У24,УЗО,Н(4),У40) (1) + С420. По сигналу У42 в сумматоре 51 реали зуется операция вьиитания. Код полу ченной разности по сигналу Н(2) про ходит через мультиплексор 48 и по сигналу У40 записывается в регистр 49, т.е. У42,Н(2),У40) Р 49: Р 49-Рг50 . ; Затем по сигналам Н(11) и У43 код .записывается в регистр 50. По сигналу У45 в блоке 52 реализуется операция деления, результат которой по-сигналу И(3) проходит через мультиплексор 48, а по сигналу У43 записывается в регистр 50, т.е. Н(11),У43) Рг50: и„акс У45 Н(3),У43) Рг50: Р 49/Рг50 По сигналу Н(8) код К коэффициента пропорциональности проходит через мультиплексор 48, а по сигналу У40 записывается в регистр 49, т.е. . Н(8), У40) Рг49: К. По сигналу У44 в умножителе 53 peaлизуетСя операция умножения. Код про изведе ия по сигналу Н(3) проходит через мультиплексор 48 и по сигналу У43 записывается в регистр 50, т.е. У44, Н(3),У43) 49«Р(. 50. Далее, по сигналу Н(10) код с выхода регистра 5 проходит через мультиплексор 48, а по сигналу У40 записывается в регистр 49, т.е. Н(10), У40) Р. . Наконец, по сигналу У41 реализуется операция сложения. Полученный код суммы по сигналу Н(2) проходит через мультиплексор 48, а по сигналу У39 записывается в регистр 5, т.е. У41, Н(2),У39 + . Таким образом, реализуется выбранный для примера алгоритм управления вида V - V к эи. - иэ; л.. ™. из--. - из; или К. К„,.+ К (в зависимости от направления развертки частоты). Полученньш код коэффициента . определяет значение коэффициента передачи аттенюатора 4, фиксированное до следующего момента управления, определяемого очередным значением j Очередное значение частоты управления fy, вычисляется следующим образом. По сигналу Н(5) код с выхода регистра 47 проходит мультиплексор 48 и по сигналу У40 записывается в регистр 49,,т.е. Н(5), У40) . По сигналу Н(7) код Af или ulogf проходит через мультиплексор 48 и по сигналу У43 записьшается в регистр 50, Н(7), У43 д - лин., Рг50: Alogf - лог. Затем по сигналу У43 сумматор 51 реализует операцию сложения. Код полученной суммы по сигналу Н(2) проходит мультиплексор 48 и по сигналу УЗ7 записывается в регистр 47, т.е. У41, Н(2), У37) + Р 50 ак реализуется итерационная процедуа вида ум-, ам+ или logfy, logfun,+ ulogf, если триггер 13 установлен в ноль. Если триггер 13 находится в единице, то реализуется процедура fy,,, Цм f. Это происходит аналогично ог1исанно гу, только вместо сигнала У41 на сумматор 51 подается сигнал У42, При этом реализуется операция вычитания, т.е.

У42,И(2),У37) Р 47: Рг49-Рг50.

При проведении испытаний на вибропрочность и на виброустойчивость выбирают необходимое число N полных циклов изменения частоты от f до fg и обратно. При изменении f периодически происходит изменение состояния триггера 13. Сигнал XI о состоянии триггера 13, проходя через блок 21 управления, поступает на вычитающий вход счетчика 53. Этот управляюи ий сигнал У27 уменьшает каждый раз. на единицу содержимое счетчика 53.При поступлении на вычитающий вход счетчика 53N импульсов (сигналов У27) в нем формируется сигнал Х5 отрицательного переполнения,который указывает на то, что программа испытаний завершена.

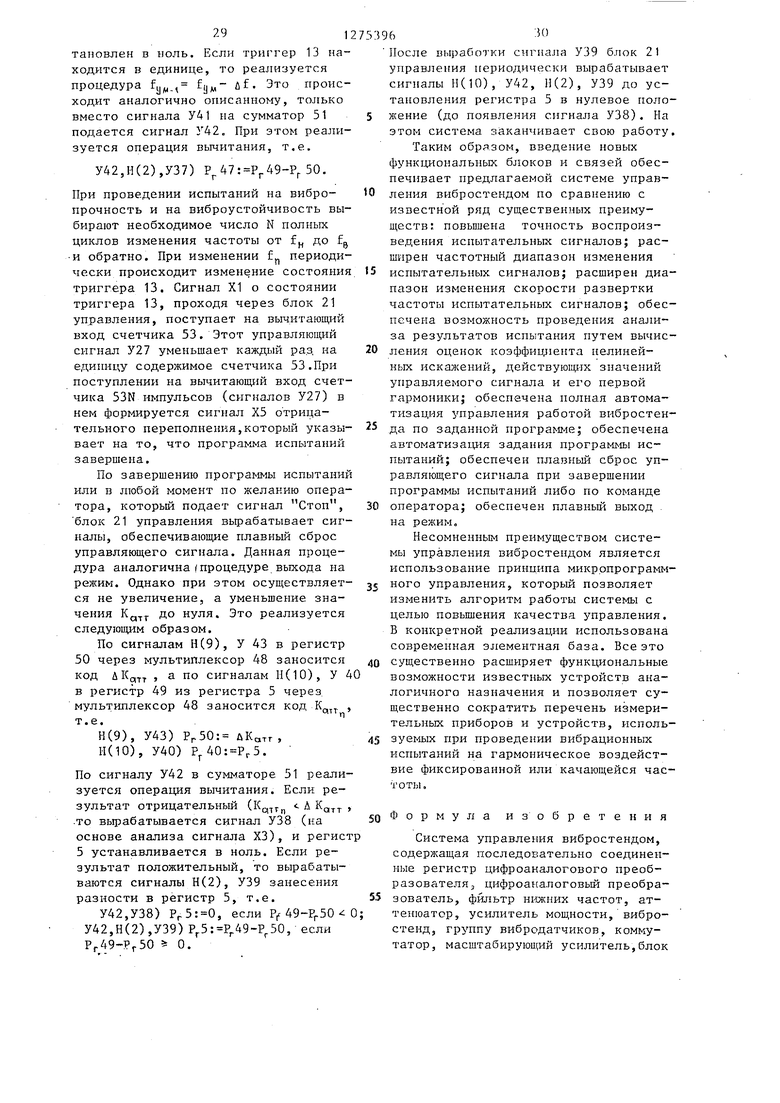

По завершению программы испытаний или в любой момент по желанию оператора, который подает сигнал Стоп, блок 21 управления вьфабатывает сигналы, обеспечивающие плавный сброс управляющего сигнала. Данная процедура аналогична(процедуре выхода на режим. Однако при этом осуществляется не увеличение, а уменьшение значения Кд до нуля. Это реализуется следующим образом.

По сигналам Н(9), У 43 в регистр 50 через мультиплексор 48 заносится код ЛКатт по сигналам И(10), У 4 в регистр 49 из регистра 5 через мультиплексор 48 заносится код К т.е.

Н(9), У43) Рг.50: дКатг ,

П(10), У40) .

По сигналу У42 в сумматоре 51 реализуется операция вычитания. Если результат отрицательный (Коптп Л К ТО вырабатывается сигнал У38 (на основе анализа сигнала ХЗ), и регист 5 устанавливается в ноль. Если результат положительный, то вырабатываются сигналы Н(2), У39 занесения разности в регистр 5, т.е.

У42,У38) , если Р 49-Pf.50У42,Н(2),У39) Р 5: Рг49-Р 50, если

Рг49--Рг50 0.

После выработки сигнала У39 блок 21 управления периодически вырабатывает сигналы Н(10), У42, И(2), У39 до установления регистра 5 в нулевое положение (до появления сигнала У38). На этом система заканчивает свою работу

Таким образом, введение новых функциональньк блоков и связей обеспечивает предлагаемой системе управления вибростендом по сравнению с известной ряд существенных преимуществ; повьпиена точность воспроизведения испытательных сигналов; расШ1фен частотный диапазон изменения испытательных сигналов; расширен диапазон изменения скорости развертки частоты испытательных сигналов; обеспечена возможность проведения анализа результатов испытания путем вычисления оценок коэффищ1ента нелинейных искажений, действующих значений управляемого сигнала и его первой гармоники; обеспечена полная автоматизация управления работой вибростенда по заданной программе; обеспечена автоматиза1щя задания программы испытаний; обеспечен плавиьш сброс управляющего сигнала при завершении программы испытаний либо по команде оператора; обеспечен плавный выход . на режим.

Несомненным преимуществом систеbibi управления вибростендом является использование принципа микропрограммного управления, который позволяет изменить алгоритм работы системы с целью повьш1ения качества управления. В конкретной реализации использована современная элементная база. Все это существенно расширяет функциональные возможности известных устройств аналогичного назначения и позволяет существенно сократить перечень измерительных приборов и устройств, используемых при проведении вибрационных испытаний на гармоническое воздействие фиксированной или качающейся частоты.

Формула изобретения

Система управления вибростендом, содержащая последовательно соединенные регистр цифроаналогового преобразователя j цифроаналоговый преобразователь, фильтр Н1-ШНИХ частот, аттенюатор, усилитель мощности, вибростенд, группу вибродатчиков, коммутатор, масштабирующий усилитель,блок аналоговой памяти, аналого-цифровой преобразователь, а также триггер направления развертки, мультиплексо задания закона модуляции частоты, первый алгебраический сумматор, регистр задания скорости развертки, информационный вход которого является входом задания скорости развертки системы, регистр задания нижней границы диапазона развертки, информационный вход которого является вхо дом задания нижней границы диапазона развертки системы, последовательно соединенные регистр задания верхней границы диапазона развертки информационный вход которого является входом задания верхней границы диапазона развертки системы, и мультиплексор выбора направления разверт ки, а также реверсивный счетчик адре са, регистр аттенюатора, выход которого подключен к второму информацион ному входу аттенюатора, и блок управ ления, первый вход которого является входом задания закона модуляции частоты системы, второй вход - входом запуска системы, третий вход - первым тактовым входом системы, четвертый вход - входом задания начальных условий системы, а выходы блока управления соединены соответственно с управляющими входами регистра цифроаналогового преобразователя, коммутатора, блока аналоговой памяти,аналого-цифрового преобразователя,двумя входами регистра аттенюатора, с входом регистра задания скорости развер ки, с входом регистра задания нижней границы диапазона развертки и с входом регистра задания верхней границы диапазона развертки, отличающаяся тем, что, с целью расширения функциональных возможностей, в систему введены последовательно соединенные мультиплексор выбора фазы, регистр задания фазы и преобра зователь фазы в амплитуду,.последовательно соединенные мультиплексор выбора частоты, регистр задания частоты и функциональный преобразовател последовательно соединенные рабочий регистр и мультиплексор выбора перво го слагаемого, а также мультиплексор выбора второго слагаемого, регистр сдвига, последовательно соединенные. сумматор по модулю два и триггер управления, а также три регистра памяти, последовательно соединенные мультиплексор выбора подкоренного выражения, блок извлечения корня и регистр хранения действующего значения первой гармоники, а также регистр хранения действующего значения сигнала, мультиплексор выбора первого сомножителя, последовательно соединен- ные мультиплексор выбора второго сомножителя, первый блок умножения деления, регистр хранения коэффициента гармоник, мультиплексор блока памяти и блок памяти, последовательно соединенные регистр частоты управления, мультиплексор выбора операнда и регистр первого операнда, последовательно соединенные регистр второго операнда и второй блок умножения - деления, а также второй алгебраический сумматор и счетчик циклов, причем второй информационньш вход второго блока умножения - деления подключен к второму информационному входу мультиплексора выбора операнда, к выходу регистра первого операнда и первому информационному входу второго алгебраического сумматора, выход которого подключен к третьему-информационному входу мультиплексора выбора операнда, выход знакового разряда второго алгебраического сумматора подключен к пятому входу блока управления, а второй информационный вход - к выходу регистра второго операнда, выход второго блока умножения - деления соединен с четвертым информационным входом мультиплексора выбора операнда, пятый информационный вход которого подключен к выходу блока памяти и к информационному выходу системы, информационный вход регистра частоты управления подключен к информационным входам соответственно регистра аттенюатора, регистров второго и первого операндов, шестой, седьмой, восьмой и девятый информационные входы мультиплексора выбора операнда являются соответственно входом задания начальной частотьц входом задания периода дискретности, входом задания коэффициента пропорциональности закона управления и входом задания приращения коэффициента передачи аттенюатора системы, десятый информационный вход подключен к выходу регистра аттенюатора, а одиннадцатый вход является входом задания кода максимальнохо значения напряжения на вьгходе атеннюатоpa системы, вход задания нулевого кода системы подключен к первому информационному входу мультиплексора выбора второго слагаемого, второй информационный вход которого подключен к информационному входу преобразователя фазы в амплитуду, первый информационный вход мультиплексора выбора фазы соединен с выходом регистра сдвига, с первым информационным входом мультиплексора выбора частоты с информационным входом рабочего регистра, с первыми информационными входами трех регистров памяти к с первым информационным входом мультиплексора выбора первого сомножителя, а второй информационньм вход мультиплексора выбора фазы является входом задания начальной фазы системы,вход задания начальной частоты которой соединен с вторым информационным .входом мультиплексора выбора частоты, выход регистра задания частоты соединен с первым входом мультиплексора задания закона модуляции частоты, второй информационньш вход которого соединен с выходом функционального преобразователя, а вькод мультиплексора соединен с вторым информационным входом г/гультиплексора выбора первого слагаемого и с первым информационным входом мультиплексора выбора второго слагаемого, второй ин формционный вход которого соединен с вторым информационным входом мультиплексора выбора первого сомножителя, с первым входом мультиплексора выбора подкоренного выражения, с третьим информационным входом мульти плексора выбора второго слагаемого и с первьгм информационным входом мул типлексора выбора первого слагаемого а также с выходом рабочего регистра, третий вход мультиплексора выбора пе вого слагаемого соединен с вторьм информационным входом мультиплексора выбора подкоренного выражения и с вы ,ходом первого блока умножения - деле ния, второй вход которого соединен с выходом мультиплексора выбора первог сомножителя, третий информационный вход которого соединен с входом реги стра хранения действующего значения сигнала и с выходом блока извлечения корня, четвертый информационный вход мультиплексора выбора первого сомножителя подключен к выходу преобразователя фазы в амплитуду и к информа6ционному входу регистра цифроаналогового преобразователя, установочный вход которого подключен к входу установки в ноль триггера управления, к установочным входам трех регистров памяти, к входу задания начальных условий системы и установочному входу регистра задания скорости развертки, выход которого подключен к четвертому информационному входу мультиплексора выбора второго слагаемого,пятьш вход которого соединен с выходом мультиплексора выбора направления развертки, второй информационный вход которого соединен с выходом регистра задания нижней границы диапазона развертки, а управляющий вход с выходом триггера направления развертки и шестым входом блока управления, седьмой вход которого подключен к единичному выходу трипера управления, первый вход сумматора по модулю два подключен к пулевому выходу триггера направления развертки, второй вход сумматора по модулю два подключен к информационному входу триггера направления развертки и к выходу знакового разряда первого алгебраического су шатора, второй выход которого подключен к .регистру сдвига, первый информационный вход к выходу мультип.пексора выбора первого слагаемого, а второй ипформационный вход - к выходу мультиплексора выбора второго слагаемого, шестой информационный вход которого подключен к третьему информационному входу мультиплексора выбора подкоренного выражения и выходу первого регистра памяти, седьмой информационный входА к выходу- второго регистра памяти, к пятому информационному входу мультиплексора выбора первого сомножителя и третьему информационному входу мультиплексора выбора второго сомножителя, четвертый информационный вход которого подключен к выходу И1нформационному входу мультиплексора выбора первого сомножителя и восьмо- му информационному входу мультиплексора выбора второго слагаемого, девятый информационный вход которого подключен к выходу регистра частоты управления, седьмой и пятый соответственно информационные входы мультиплексоров выбора первого и второго сомножителей объединены и подключены

к ВЫХОДУ аналого-цифрового преобразователя, шестой информаи;ионный вход мультиплексора выбора второго сомножителя подключен к входу задания кода Сто системы, вход задания числа циклов которой подключен к информационному входу счетчика циклов, выход отрицательного переполнения которого подключен к восьмому входу блка управления, девятый вход которого подключен к выходу положительного переполнения реверсивного счетчика адреса, информационный вход которого является входом задания начального адреса системы, а выход - к первому адресному входу блока памяти, второй адресный вход которого объединен с управляюпщм входом мультиплексора блока памяти, второй, третий и чет вертый информационные входы которого подключены соответственно к входу задания эталонных значений управляемой величины системы, к выходу регистра хранения действующего значения первой гармоники и выходу регистра хранения действующего значения сигнала, входы задания направления развертки системы подключены к входам установки в единицу и в ноль триггера направления развертки,вход записи эталона, второй тактовый вход вход остановки системы и вход задания номера канала подключены соответственно к десятому, одиннадцатому, двенадцатому и тринадцатому -входам блока управления, соответствующие выходы которого подключены к управляющим входам мультиплексора выбора фазы, мультиплексора выбора частоты, мультиплексора задания закона модуляции, мультиплексора выбора первого слагаемого, мультиплексора выбора второго слагаемого, мультиплексора выбора подкоренного вьфажения,мультиплексора выбора первого сомножителя

мультиплексора выбора второго сомножителя, мультиплексора блока памяти и мультиплексора выбора операнда, к управляющему входу регистра задания фазы, к первому и второму управляющим входам преобразователя фазы в амплитуду, к управляющему входу регистра задания частоты, к управляющему входу рабочего регистра, к синхронизирующему входу триггера направления развертки, к входам сложения, вычитания и инверсного вычитания ; первого алгебраического сумматора, к входам передачи, сдвига вправо и сдвига влево регистра сдвига, к синхронизирующему входу триггера управления, к управляющему входу блока извлечения корня, к управляющему входу регистра хранения действующего значения первой гармоники, к управляюще му входурегистра хранения действующего значения сигнала, к установочному входу, к суммирующему входу, к вычитающему входу и управляющему входу реверсивного счетчика адреса, к вычитающему входу и управляющему входу счетчика циклов, к входу записи и входу чтения блока памяти, к управляющему входу первого регистра памяти, к управляющему входу второго регистра памяти, к управляющему входу третьего регистра памяти, к входу умножения и входу деления первого блока умножения - деления, к управляющему входу регистра хранения коэффициента гармоник, к управляющему входу регистра частоты управления к управляющему входу регистра первого операнда, к суммирующему входу и вычитающему входу второго алгебраического сумматора, к управляющему входу регистра второго операнда, к входу умножения и входу деления второго блока умножения - деле ния. 4 1ШШ--.,. Щ чj-:0 Г- ; ( M .„-.™I.i./J//; I .,..., , „.. ,.л jj ;,/-, ii K. i -I ..-„dli .dy. -. 1 .,.. -j ,j I 1 . |i.i..l,..l. ««TITi: :: ftj I/7I--Hf If-1-::; -l/L ,.Z,4,1 i ri -i(ii5,}l fi „. I (( OPGCJL, 4 - , Г----П 1 Я..: If ,.Л,, r -d-LcJ Т -fe,A tf 1 is Si LlSfSjiJ f T с -f V i r:-.-J ГI Ц:; {,„„|ч/// .......,.™.bvry ,,, -( Ь ШИйш::,.| i . .;// ;; - i s rfb,.. I/RM| I , . . „ I«:;«, Ffe I Aoffinos f fiomnos l УЗ У39 cKomno3iZ9 т y//Tj 2 Mjy-flf 9; yfOfOl-jB Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство отсечения многоугольника для графического дисплея | 1990 |

|

SU1777151A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для контроля памяти | 1987 |

|

SU1587598A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для усреднения сигналов | 1985 |

|

SU1322316A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

Изобретение относится к автоматическому регулированию и управлению, в частности к системам управления экспериментальными установками,предназначено для испытаний различных конструкций приборов и машин на электродинамическом вибрационном стенде гармонической вибpau eй на фиксированных частотах и вибрацией переменной частоты. Целью изобретения является расширение функциональных возможностей за счет повышения точности воспроизведения испытательных сигналов в широких частотных диапазонах и диапазоне изменения скоростей развертки, проведения анализа результатов испытаний, автоматизация управления работой вибростенда по заданной программе. Система управления вибростендом содержит цифроаналоговый преобразователь, фильтр низких частот, аттенюатор, усилитель мощности, вибростенд, группу вибродатчиков, коммутатор, масштабирующий усилитель, блок аналоговой памяти, аналого-цифровой i преобразователь,17 регистров, 11 мультиплексоров, два триггера, функ Л циональный преобразователь, преобразователь фазы в амплитуду, сумматор по модулю два, два алгебраических сумматора, два блока умножения - деления, блок памяти, блок извлечения корня, реверсивный счетчик и счетчик циклов. Использование принципа микропрограммного управления, введение ел новых функциональных блоков и связей СО О5 существенно расширяют функциональные возможности известных устройств аналогичного назначения. 16 ил, 1 табл.

СТОП

Клин/мд

Ш

Фи.г.и ( Начало -V#/W tt%±i Afivff-f направление разоертни г U/lfc uu/i/u/y (t-y w.налом „СВРОСсформирО cam CQomoemcmoi/fou4Uu Запиог UW сигна/1 PB/PH. Bnpa(Фиг.8) muuHOM слу аеТ13ycmaнаблабается и произдомное состояний (Q/iI при Форнироо/ум включении питанил - {Фиг. 7) Услодно - epacpwecKoe изображение местарастраллелиоания а/ггоритна , Вшоднаре hj l- miMLsJL Форм и р. гарнонагого с иг-. ЮЛ нала,(Фаг.11 т %& Й7Л7/7 Й ---х аЩлтф I

Оосигналу У27 (формируется текущее ,i}реализуется аппаратно 6 „

Услодно-графанес кое изображение L места объединения аморитма а и последующие операторные оершинь ffo/ ffШЛf)Cff yc/JOBHO быпо/гнимшнЦу т. е. ошло/гндются тольно при отсутстбии саанала СТОП. При гшядленаи сигнала стоп любой нонент бремени упраомте. переда- „ ется оерш.ине,.Плаон1)1(2 с&рос ТвходоО а последующие бершинь/ ода даннш)( реа/тзуются аппаратно и пдэшон fioei/m, бьтолнйтсйд бремя 6 реализации алгоритма, иднако резштаты oSada используются о алгоритме иеранее того, момента, котодош cQonwemcmSyem поло /кению оершинб о Улок-схеме алгоритма

С Выход j

) C /L™J

«v

и

i§§§§§§g s§§agl«s|§s5 p5 5 §

ч;.I t tXSr

e

ПУСК ГАКТЬИ

-JT-riyTrxjTJ j4jr rixijTjTJTJTJ4J-unj4Jxruart

Ш ,2 у2 // A/Z// /2 .2.3 ,,8 ,6 ,f .21Г;f

/ / л/// / / / / / / / w/ /fi; IR: -f-Z N : XIШЕ: Формиро ание ucim t Ваи ис/ге/ ие Гтате/гбтго i i ( сигнала

л V 5 J Вд/1 исление Вычисление 1 11

| Устройство для управления вибростендом | 1980 |

|

SU930236A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Вибрация в технике | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| - М.: Машинострдение, 1981, т | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Измерения и испытания | |||

| /Под ред | |||

| М.Д | |||

| Генкина, 1981, с | |||

| Снеговая лыжа для самолетов | 1913 |

|

SU455A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-07—Публикация

1984-12-05—Подача