1

(21)4700568/24 (22) 05.06.89 (46)23.11.91. Бюл. Me 43

(71)Московское приборостроительное .конструкторское бюро Восход

(72)В.А.Ткаченко, С.Н.Ткаченко, Г.Н.Ти- монькин, В.С.Харченко, А.В.Моченков и С.С.Мощицкий

(53)681.3(088.8)

(56) Авторское свидетельство СССР

№ 1343418, кл. G 06 F 11/28, 1987.

Авторское свидетельство СССР № 1361562, кл. G 06 F 11/28, 1987.

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВРЕМЕНИ ВЫПОЛНЕНИЯ ПРОГРАММ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля времени выполнения отдельных сегментов программ при отладке. Цель изобретения - повышение оперативности контроля. Для этого в устройство введены блок задания адреса, блок сравнения, дешифратор режима, коммутатор, два элемента И, второй и третий элементы ИЛИ Оперативность контроля повышается путем сокращения времени фиксации сбоев, которые не позволяют системе перейти к выполнению программы обработки прерываний. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для контроля хода программ | 1983 |

|

SU1101831A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1985 |

|

SU1337901A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для контроля времени выполнения программ | 1985 |

|

SU1312581A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1728864A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для отладки мультипрограммных систем | 1989 |

|

SU1735855A1 |

| Устройство для программного управления | 1990 |

|

SU1784939A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля времени выполнения отдельных сегментов программы при отладке.

Цель изобретения - повышение оперативности контроля за счет сокращения времени фиксации сбоев, блокирующих переход к выполнению программы обработки прерываний.

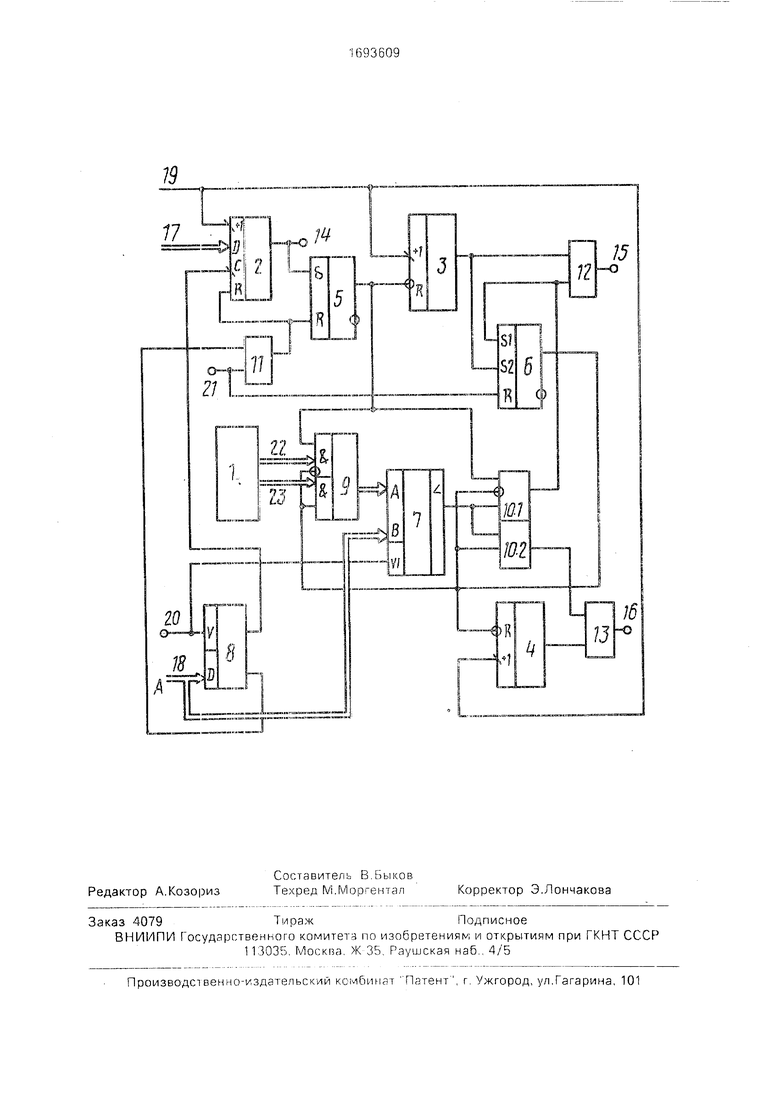

На чертеже показана структурная схема предлагаемого устройства.

Устройство содержит блок 1 задания адреса, счетчик 2 времени, счетчик 3 прерываний, счетчик 4 перезапусков, триггер 5 контроля времени, триггер 6 прерываний, блок 7 сравнения, дешифратор 8 режима, коммутатор 9, два элемента И 10.1 и 10.2, первый 11, второй 12, третий 13 элементы ИЛИ, выход 14 устройства, выход 15 перезапуска программы устройства, выход 16

сброса устройства, вход 17 установки времени выполнения сегмента программы устройства, вход 18 адреса устройства, тактовый вход 19 устройства, вход 20 запуска сегмента программы устройства, вход 21 сброса устройства, первый выход 22 блока задания адреса, второй выход 23 блока 1.

Блок задания адреса предназначен для формирования кодов начального адреса программы обработки прерываний и адреса перехода к контролируемой программе при перезапуске системы (программе обработки Сброс-пуск).

Счетчик 2 времени предназначен для контроля времени выполнения отдельных сегментов контролируемой программы, счетчик 3 прерывания - для контроля реакции контролируемой системы на сигнал запроса прерываний, счетчик 4 перезапусков - для контроля времени реакции системы на

ON Ю СА) О О О

сигнал Сброс-пуск, триггер 5 - для фиксации сигнала переполнения счетчика 2.

Триггер 6 предназначен для фиксации сигнала переполнения счетчика 3. Блок 7 сравнения предназначен для формирования сигналов Стоп-пуск и Отключения системы при несравнении сформированных генератором 1 адресов и кодов адресов, выставляемых микропроцессором на шину адреса и поступающих на вход 18 устройства, Дешифратор 8 режима предназначен для формирования сигналов начала и конца контролируемого сегмента, коммутатор 9 - для осуществления управления выдачей контрольных адресов на входы блока 7 сравнения.

Элементы И 10.1 и 10.2 предназначены для управления выдачей сигналов Стоп- пуск и Отключение системы при наличии управляющих сигналов с выходов триггера 5 и 6 соответственно. Элементы ИЛИ 11 - 13 предназначены для объединения выходов соответствующих элементов устройства.

Выход 14 устройства предназначен для выдачи в систему сигнала Прерывание. Выход 15 устройства -для выдачи в систему сигнала Стоп-пуск, выход 16 устройства - для выдачи в систему сигнала Отключение системы,

Устройство работает следующим образом.

Программа разбивается на контролируемые сегменты, началом которого является программное обращение к счетчику 2 (счетчик 2 является программно-доступным элементом устройства и ему присваивается фиксированный адрес). Конец контролируемого сегмента программы фиксируется в момент появления на шине адреса определенного кода адреса Аз (этот адрес может соответствовать какой-либо команде вывода микропроцессорной системы).

В исходном состоянии все элементы памяти обнулены, в счетчик 3 контроля прерываний занесен код, соответствующий .максимально допустимому времени реакции контролируемой системы на выдаваемый устройством контроля сигнал Прерывание, а в счетчик 4 перезапуска занесен код, соответствующий максимально допустимому времени реакции контролируемой системы на сигнал Сброс-пуск. Триггеры 5 и 6 сигналами низкого уровня на своих выходах удерживают счетчики 3 и 4 в исходном состоянии при поступлении импульсов тактовой частоты на счетные входы счетчиков 2-4.

Микропроцессор (например, К580) выставляет на вход 18 адреса код адреса счетчика 2 контроля программы, этот код будет дешифрован дешифратором 8 режима по приходе управляющего сигнала (метка М1 - пятый разряд слова состояния) на вход 20

устройства. На шину данных микропроцессор выставляет код, идентифицирующий масштаб установки максимально допустимого времени выполнения контролируемого сегмента. Данная информация поступает на

0 вход 17 устройства и запишется в счетчик 2 по полученному сигналу с выхода начала сегмента дешифратора 8.

При нормальном ходе выполнения программы в счетчик 2 периодически будет за5 носиться код временного интервала, который по времени превосходит время выполнения очередного участка программы. Поэтому при правильном ходе выполнения программ переполнения счетчика 2 не про0 исходит, так как по окончании каждого сегмента программы будет приходить неизменный адрес Аз на вход 18, сигнал на втором выходе дешифратора 8 будет восприниматься устройством как сигнал

5 Сброс.

Если происходит нарушение в выполнении программы в результате контролируемый сегмент программы не заканчивается в заданный интервал времени (т.е. неизменя0 емый адрес Аз не поступает на вход 18 устройства), на выходе переполнения счетчика 2 формируется сигнал прерывания. По этому сигналу триггер 5 устанавливается в единичное состояние и разрешает работу

5 счетчика 3. Тактовый импульс, поступающий с входа 19 устройства, увеличивает на 1 значение кода, записанного в счетчик 3, увеличивает на 1.

Если контролируемая система реагиру0 ет на сигнал Прерывание в течение заданного промежутка времени, т.е. сигнал Сброс не поступает на вход 21 устройства за время установки счетчика 3, то на выходе переполнения счетчика 3 формируется сиг5 нал, который поступает на первый вход вто- рэго элемента ИЛИ 12, а затем на выход 15 устройства. Сигнал, вырабатываемый на выходе 15 устройства, является сигналом Сброс-пуск для контролируемой системы.

0 Кроме того, устройство реализует возможность контроля выхода системы на программы обработки прерываний.

Блок 1 задания адреса формирует коды конкретных адресов, например, первой ко5 манды программы обработки прерываний. Микропроцессор контролируемой системы, получив сигнал на прерывание, последний адрес контролируемой программы сохраняет (например, заносит в стек), а на шину адреса выставляет первый адрес команды

программы обработки прерываний. Этот адрес поступит на вход 18, а затем на второй вход блока 7 сравнения. На первый вход блока 7 поступает код адреса с выхода 22 блока 1 задания адреса.-

При несовпадении адресов на выходе блока 7 вырабатывается сигнал Ошибка, который через открытый элемент И 10.1 через элемент ИЛИ 12 поступит на выход 15 устройства как сигнал Сброс-пуск. По сиг- налу Сброс-пуск триггер 6 устанавливается в единичное состояние, разрешая тем самым работу счетчика 4.

Микропроцессорная система, реагируя на сигнал Сброс-пуск, переходит к обработке контролируемой программы вновь с самого начала. На вход 18 поступает код адреса начала программы. Генератор 1 адреса также формирует начальный адрес контролируемой программы. В случае их несравнения на выходе блока 7 вырабатывается сигнал Ошибка, который через открытый элемент И 10.2 и элемент ИЛИ 13 поступит на выход 16 устройства и будет воспринят микропроцессорной системой как Отказ системы.

Если контролируемая система реагирует на сигнал Сброс-пуск, то на вход 21 устройства поступит сигнал Сброс-пуск, по которому устройство переводится в исходное состояние.

Если контролируемая система не реагирует на сигнал Сброс-пуск, в течение установленного времени счетчик 4 перезапуска переполняется, и на его выходе вырабатывается сигнал, поступающий через элемент И 13 на выход 16 устройства как сигнал Отказ системы.

Формула изобретения

Устройство для контроля времени выполнения программ, содержащее первый элемент ИЛИ, первый вход которого является входом сброса устройства, триггер конт- роля времени, триггер прерывания, счетчик прерывания, счетчик перезапусков и счетчик времени, информационный вход которого является входом установки времени выполнения сегмента программы устройст- ва, а выход переполнения является выходом прерываний устройства и соединен с установочным входом триггера контроля времени, выход которого соединен с инверсным входом сброса счетчика прерываний, выход переполнения которого соединен с первым

установочным входом триггера прерываний, выход которого соединен с инверсным входом сброса счетчика перезапусков, выход первого элемента ИЛИ соединен с входами сброса триггера контроля времени и счетчика времени, счетный вход счетчика времени является тактовым входом устройства и соединен с тактовыми входами счетчика прерывания и счетчика перезапусков, отличающееся тем, что, с целью повышения оперативности контроля, в устройство введены блок сравнения, дешифратор режима, коммутатор, два элемента И, второй и третий элементы ИЛИ и блок зада- ния адреса, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен с первым информационным входом блока сравнения, второй информационный вход которого является входом адреса устройства и соединен с информационным входом дешифратора режима, управляющий вход которого является входом запуска сегмента программы устройства и соединен с управляющим входом блока сравнения, а выходы начала сегмента программы и конца сегмента программы дешифратора режима соединены соответственно с тактовым входом записи счетчика контроля времени и вторым вхо-. дом первого элемента ИЛИ, выход переполнения счетчика прерываний соединен с первым входом второго элемента ИЛИ, выход которого является выходом перезапуска программы устройства, а второй вход соединен с выходом первого элемента И и с вторым установочным входом триггера прерывания, вход сброса которого соединен с первым входом первого элемента ИЛИ, выход переполнения счетчика перезапусков соединен с первым входом третьего элемента ИЛИ, выход которого является выходом сброса программы устройства, второй вход соединен с выходом второго элемента И, выход триггера контроля времени соединен с первым управляющим входом коммутатора и первым входом первого элемента И, выход блока сравнения соединен с вторым входом первого элемента И и первым входом второго элемента И, третий инверсный вход первого элемента И соединен с вторым входом второго элемента И, вторым и третьим управляющими входами коммутатора и подключен к выходу триггера прерывания.

Авторы

Даты

1991-11-23—Публикация

1989-06-05—Подача