Изобретение относится к вычислительной технике и может быть использовано для контроля хода программ ЭВМ.

Цель изобретения - повышение достоверности контроля.

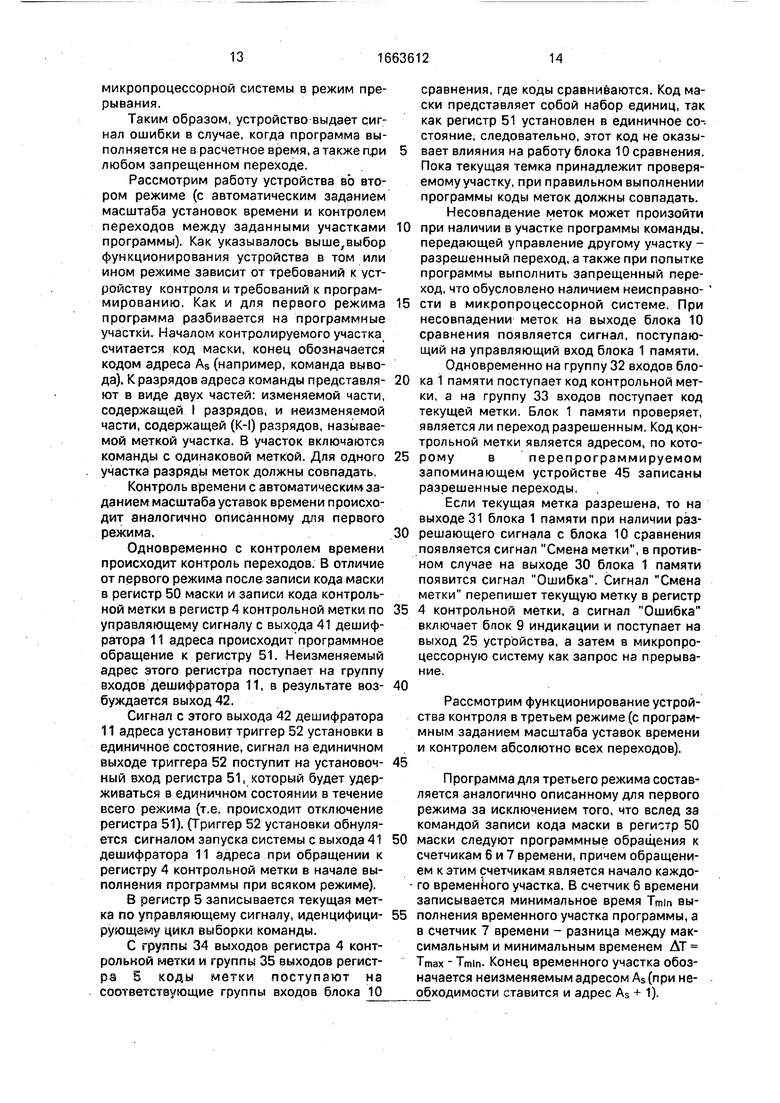

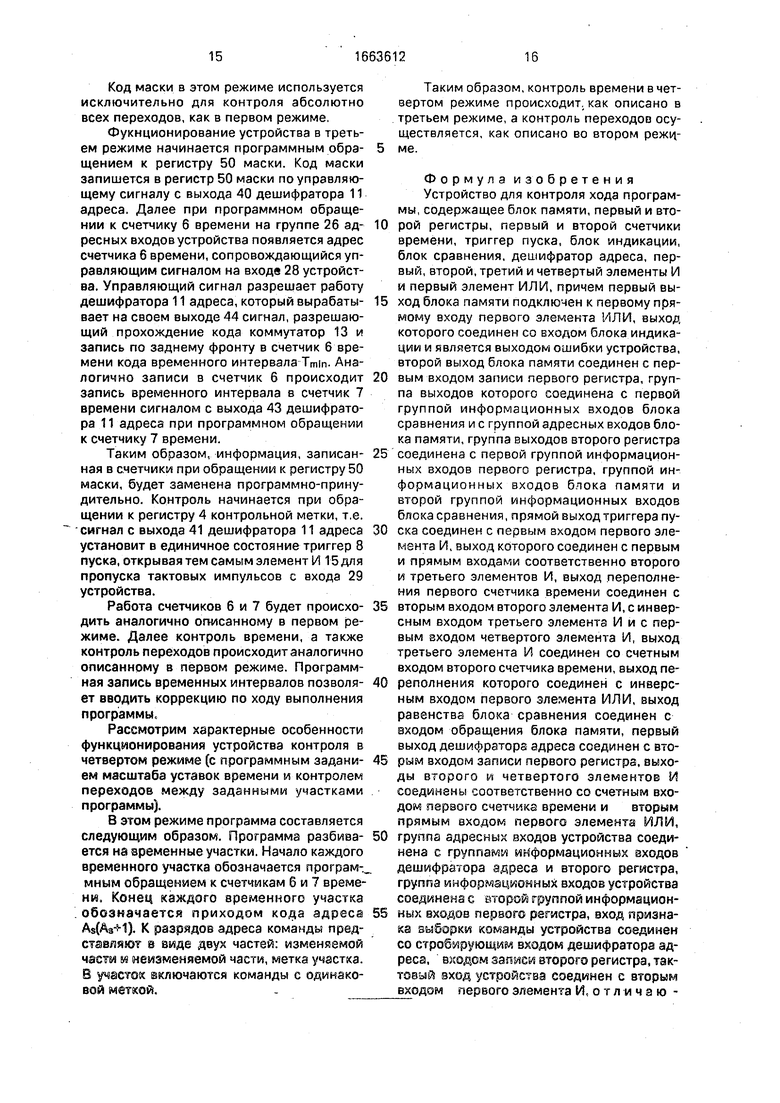

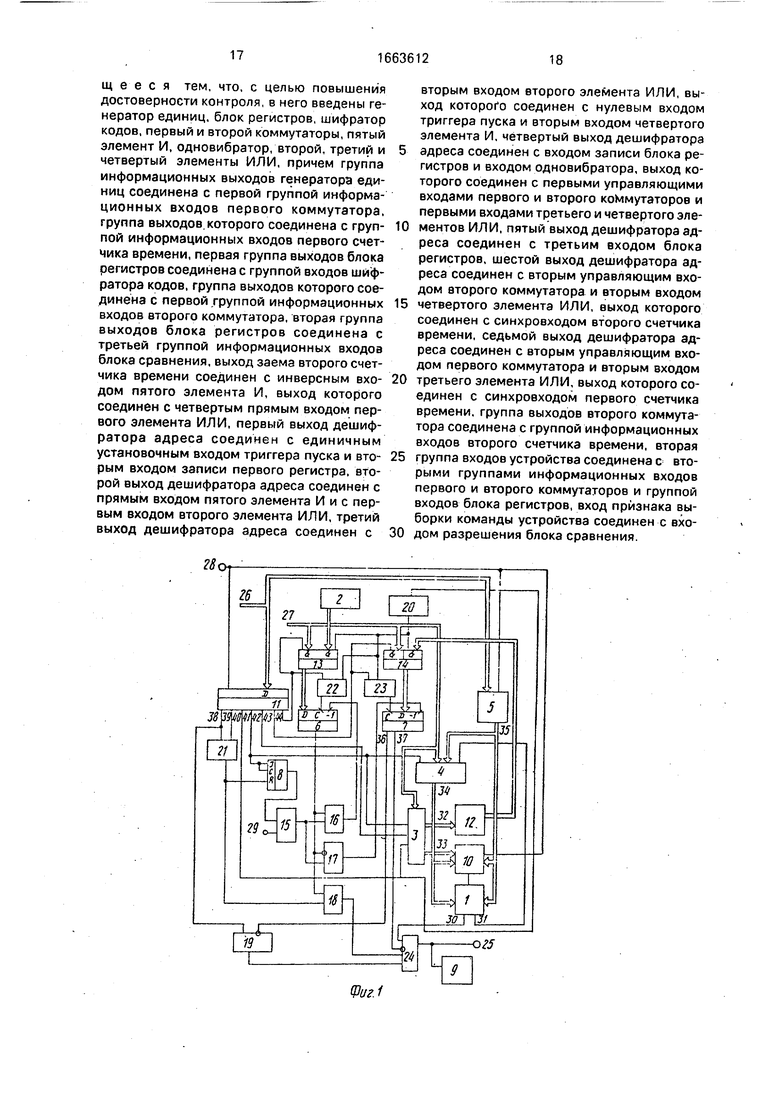

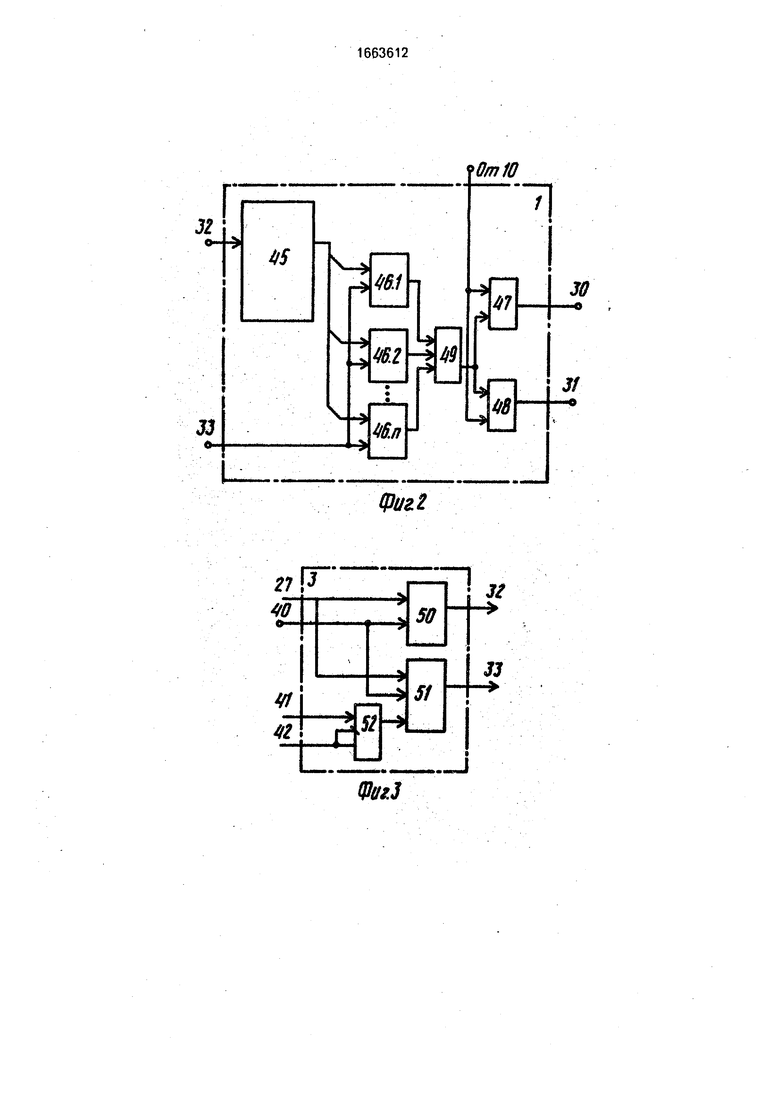

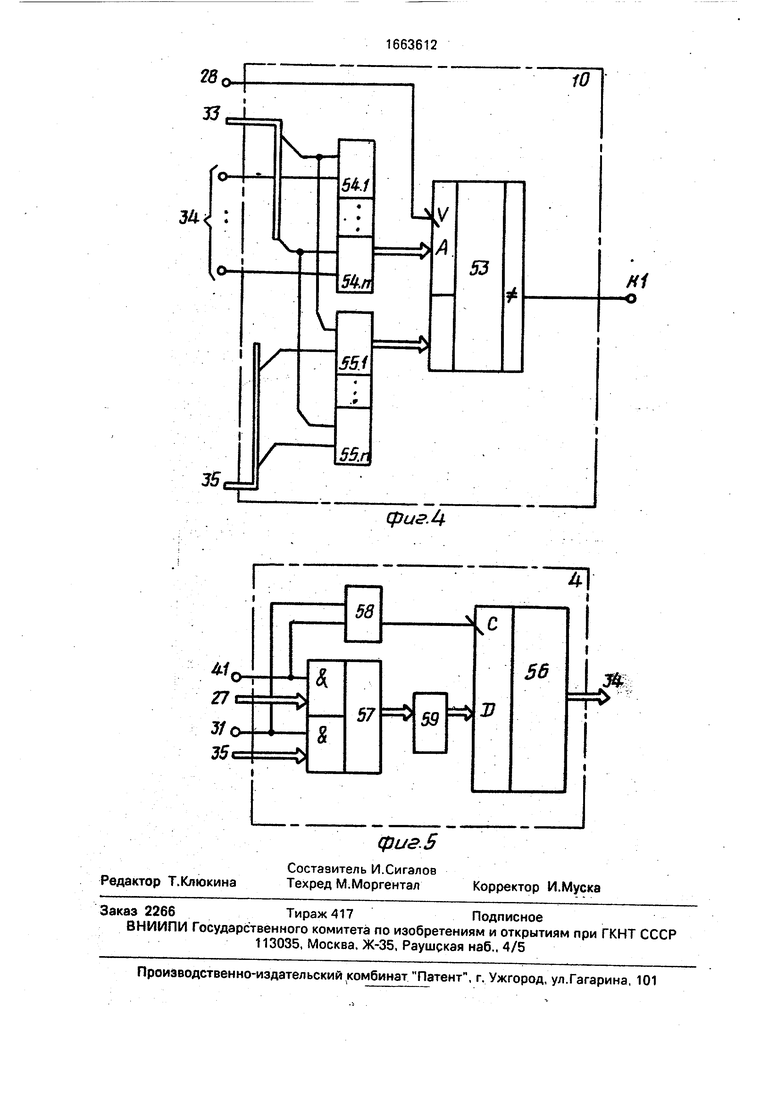

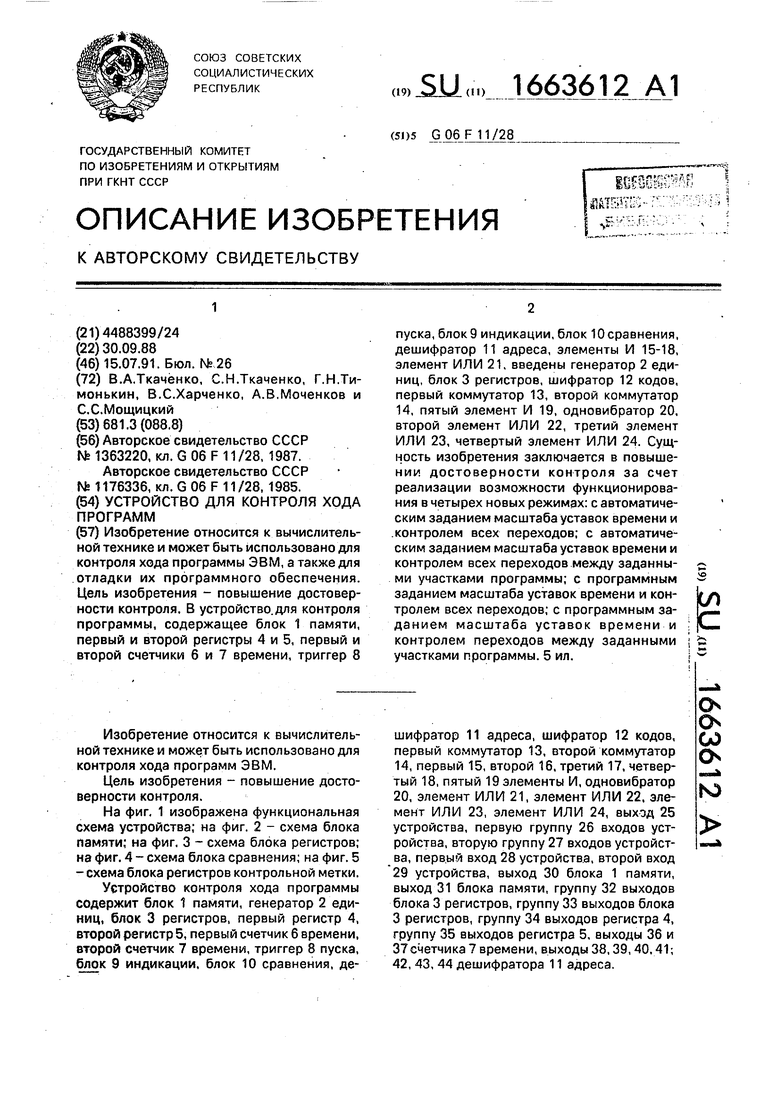

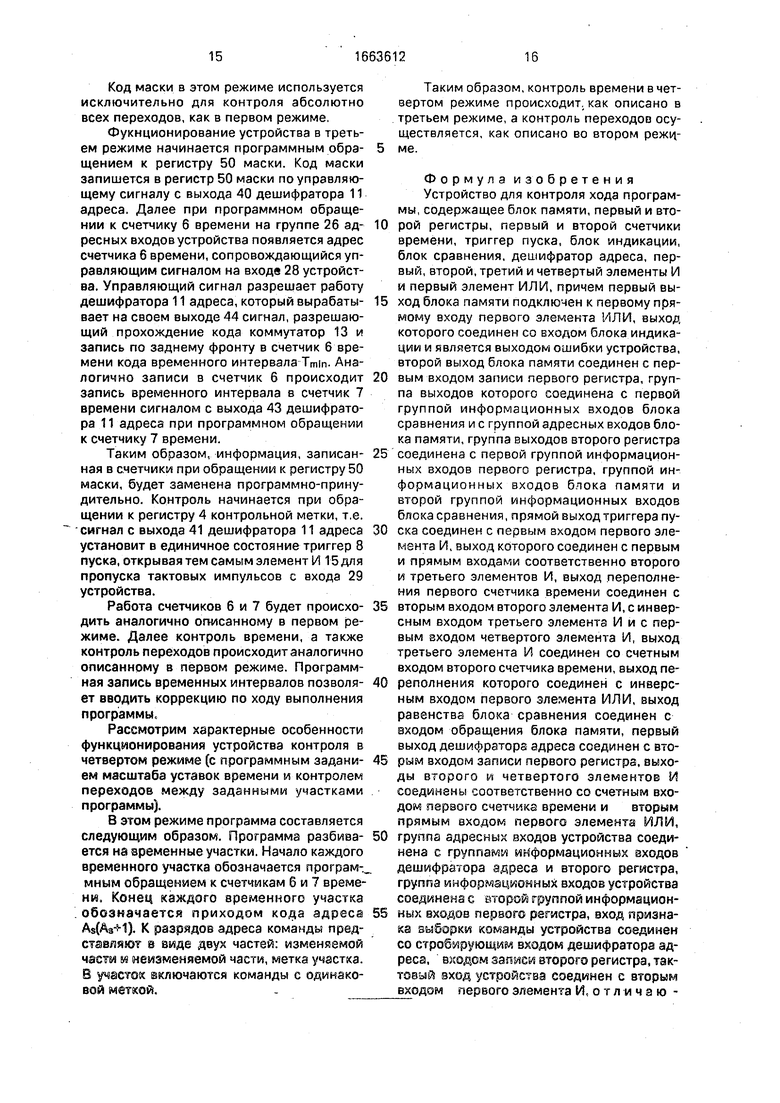

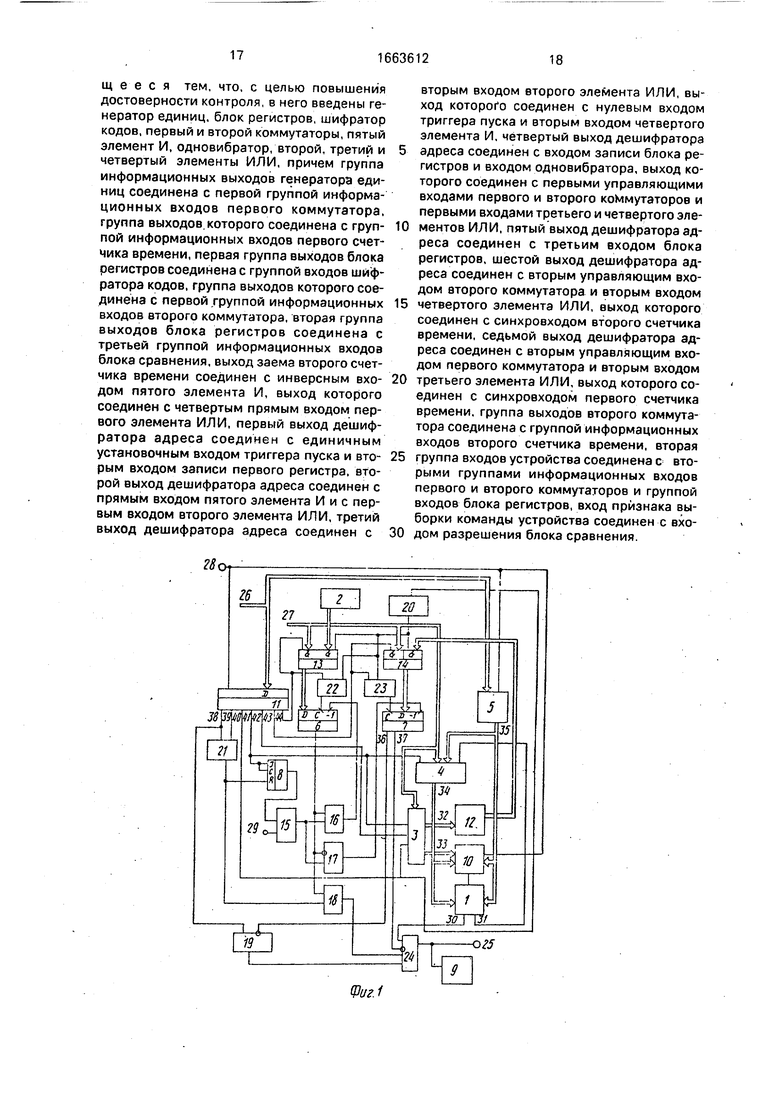

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - схема блока памяти; на фиг. 3 - схема блока регистров; на фиг. 4 - схема блока сравнения; на фиг. 5 -схема блока регистров контрольной метки.

Устройство контроля хода программы содержит блок 1 памяти, генератор 2 единиц, блок 3 регистров, первый регистр 4, второй регистр 5, первый счетчик 6 времени, второй счетчик 7 времени, триггер 8 пуска, блок 9 индикации, блок 10 сравнения, дешифратор 11 адреса, шифратор 12 кодов, первый коммутатор 13, второй коммутатор 14, первый 15, второй 16, третий 17, четвертый 18, пятый 19 элементы И, одновибратор 20, элемент ИЛИ 21, элемент ИЛИ 22. элемент ИЛИ 23, элемент ИЛИ 24, выход 25 устройства, первую группу 26 входов устройства, вторую группу 27 входов устройства, первый вход 28 устройства, второй вход 29 устройства, выход 30 блока 1 памяти, выход 31 блока памяти, группу 32 выходов блока 3 регистров, группу 33 выходов блока 3 регистров, группу 34 выходов регистра 4, группу 35 выходов регистра 5, выходы 36 и 37 счетчика 7 времени, выходы 38,39,40,41; 42, 43, 44 дешифратора 11 адреса.

о.

Os СО О

«яЛ

к

Выход 30 блока 1 памяти подключен к первому входу элемента ИЛИ 24, выход которого подключен к входу блока 9 индикации и выходу 25устройства, Выход 31 блока 1 памяти подключен к первому управляющему входу регистра 4 контрольной метки, группа 34 выходов которого подключена к первой группе входов блока 10 сравнения и группе входов блока 1 памяти. Группа выходов генератора 2 единиц подключена к первой группе входов первого коммутатора 13, группа выходов которого подключена к группе информационных входов счетчика 6 времени.

Группа 32 выходов блока 3 регистров соединена с группой входов шифратора 12, группа выходов которого подключена к первой группе входов второго коммутатора 14, Группа 33 выходов блока 3 регистров подключена к второй группе входов блока 10 сравнения, выход которого подключен к входу блока 1 памяти. Группа 35 выходов регистра 5 соединена С первой группой входов регистра 4 и второй группой входов блока 1 памяти, а также с третьей группой входов блока 10 сравнения.

Выход счетчика 6 времени подключен к первым входам элементов И 16 и 18, а также к инверсному входу элемента И 17, выход которого соединен со счетным входом счетчика 7 времени. Выход 36 счетчика 7 времени подключен к инверсному входу элемента И 19, выход которого подключен к второму входу элемента ИЛИ 24, выход 37 счетчика 7 времени подключен к инверсному входу элемента ИЛИ 24.

Единичный выход триггера 8 пуска подключен к первому входу элемента И 15, выход которого соединен с вторым входом элемента И 16 и прямым входом элемента И 17. Выход 38 дешифратора 11 адреса соединен с первым входом элемента ИЛИ 21 и прямым входом элемента И 19. Выход 39 дешифратора 11 подключен к второму входу элемента ИЛИ 21, выход которого соединен с нулевым входом триггера 8 пуска и вторым входом элемента И 18, выход которого подключен к третьему входу элемента ИЛИ 24, Выход 40 дешифратора 11 адреса подключен к первому управляющему входу блока 3 регистров и входу одновибратора 20, выход которого соединен с первыми управляющими входами коммутаторов 13 и 14, а также с первыми входами элементов ИЛИ 22 и 23. Выход 41 дешифратора 11 адреса подключен к совмещенному установочному входу триггера 8 пуска, второму управляющему входу регистра 4,.а также второму управляющему входу блока 3 регистров.

Выход 42 дешифратора 11 адреса подключен к третьему входу блока 3 регистров, выход 43 дешифратора 11 адреса подключен к второму управляющему входу коммутаюра 14 и второму входу элемента ИЛИ 23, выход которого соединен с синхровходом счетчика 7 времени. Выход 44 дешифратора 11 адреса подключен к второму управляющему входу коммутатора 13 и второму входу

элемента ИЛИ 22. выход которого подключен к синхровходу счетчика 6 времени.

Группа выходов коммутатора 14 подключена к группе информационных входов счетчика 7 времени. Выход элемента И 15

соединен с вторым входом элемента И 16, выход которого подключен к счетному входу счетчика 6 времени, а также к прямому входу элемента И 17. Группа 26 входов устрой- стаа подключена к группе адресных входов

дешифратора 11 адреса, а также отдельными разрядами подключена к группе входов регистра 5. Группа 27 входов устройства подключена к вторым группам входов коммутатора 13 и коммутатора 14, а также отдельными разрядами к второй группе входов регистра 4 и группе входов блока 3 регистров. Вход 23 устройства подключен к управляющему входу дешифратора 11 адреса, управляющему входу регистра 5 и управлягощему входу блока 10 сравнения. Вход 29 устройства подключен к второму входу элемента И 15.

Блок 1 памяти (фиг. 2) содержит перепрограммируемые запоминающие элементы 45 памяти, блок элементов 46.1-46.п сравнения, элемент И 47, элемент И 48, элемент И 49, выход 30, выход 31, группу 32 входов, группу 33 входов, управляющий вход от блока 10 сравнения.

Группа выходов запоминающих элементов 45 отдельными разрядами подключена к первым группам входов элементов 46.1-46.п сравнения соответственно, выходы которых подключены к соответствующим

аходам элемента ИЛИ 49.

Выход элемента И 47 является выходом 30 блока, а выход элемента И 48 является выходом 31 блока. Выход элемента ИЛИ 49 подключен к инверсному входу элемента И

47 и первому входу элемента И 48.

Группа 32 входов подключена к группе входов запоминающего устройства 45. Группа 33 входов блока подключена к вторым группам входов элементов 46.1-46.rt

сравнения. Управляющий вход блока подключен к второму входу элемента И 48 и прямому входу элемента И 47.

Блок 3 регистров (фиг. 3) содержит регистр 50 маски, регистр 51, триггер 52 устанрвки, группу 32 выходов, группу 33

выходов, группу 27 входов, вход 40, вход 41, вход 42.

Группа выходов регистра 50 маски является группой 32 выходов блока. Группа выходов регистра 51 является группой.33 выходов блока. Единичный выход триггера 52 установки подключен к установочному входу регистра 51.

Группа 27 входов блока подключена к группам входов регистра 50 маски и регистра 51, вход 40 подключен к синхровходам регистра 50 маски и регистра 51, вход 41 подключен к нулевому входу триггера 52 установки, вход 42 подключен к совмещенному установочному входу триггера 52 установки.

Блок 10 сравнения (фиг. 4) содержит элемент 53 сравнения, блок элементов И 54.1-54.п, блок элементов И 55.1 -55.п, выход блока на блок 1 памяти, группу 33 входов, группу 34 входов, группу 35 входов, управляющий вход 28.

Выход по несовпадению элемента 53 сравнения является выходом блока.

Группа выходов блока элементов И 54.1-54.п подключена к группе А входов элемента 53 сравнения. Группа выходов блока элементов И 55.1-55.п подключена к группе В входов элемента 53 сравнения.

Группа 33 входов подключена отдельными разрядами к первым входам элементов И 54.1-54,п блока и элементов И 55.1-55.п блока, группа 34 входов блока подключена отдельными разрядами к вторым входам элементов И 54.1-54.п блока соответственно. Группа 35 входов блока подключена отдельными разрядами к вторым входам элементов И 55.1-55.П блока.

Вход 28 блока является управляющим входом элементов 53 сравнения.

Блок 4 регистра контрольной метки (фиг. 5) содержит регистр 56, коммутатор 57, элемент ИЛИ 58, элемент 59 задержки, группу 34 выходов, группу 27 входов, группу 35 входов, входы 41.

Группа выходов регистра 56 является группой 34 выходов блока, группа выходов коммутатора подключена к группе входов элемента 59 задержки, группа выходов которого подключена к группе входов регистра 56, выход элемента ИЛИ 58 подключен к синхровходу регистра 56, группа 27 входов блока подключена к первой группе входов коммутатора 57, группа 35 входов блока подключена к второй группе входов коммутатора, вход 31 блока подключен к первому входу элемента ИЛИ 58 и первому управляющему входу коммутатора 57, вход 41 блока подключен к второму управляющему входу

коммутатора 57 и второму входу элемента ИЛИ 58.

Блок 1 памяти предназначен для хранения и проверки адресов разрешенных переходов. Он представляет собой ассоциативное запоминающее устройство, в котором по адресу данной команды хранятся адреса возможных разрешенных переходов отданной команды к всевозможнымдругим.

0 Перепрограммируемые запоминающие

элементы памяти 45 предназначены для

хранения и выдачи по пришедшему коду

адреса адресов разрешенных переходов.

Блок элементов 46.1-46.п сравнения

5 предназначен для сравнения кодов адресов текущих команд с кодами разрешенных адресов, записанных в перепрограммируемом запоминающем устройстве 45.

Элемент И 47 предназначен для форми0 рования сигнала Ошибка. Элемент И 48 предназначен для формирования сигнала Смена метки. Элемент ИЛ И 49 предназначен для объединения выходов элементов 46.1-46.п сравнения.

5Генератор 2 единиц предназначен для

формирования последовательности сигналов, имеющих потенциал логической единицы.

Блок 3 регистров предназначен для хра0 нения и выдачи кода маски на шифратор 12, блок 10 сравнения в различных режимах работы устройства.

Регистр 50 маски предназначен для получения, хранения и выдачи кода маски.

5 Регистр 51 предназначен для выдачи кода маски на блок 10 сравнения в режимах, когда производится контроль абсолютно всех переходов.

Триггер 52 предназначен для установки

0 и удержания регистра 51 в единичном состоянии при программном обращении к регистру 51.

Регистр 4 контрольной метки предназначен для хранения и выдачи кода контроль5 ной метки. Регистр 5 предназначен для хранения и выдачи кода адреса текущей команды.

Счетчики 6 и 7 времени предназначены для фиксации минимальной и максммаль0 ной границ времени соответственно при контроле времени выполнения контролируемой программы,

Триггер 8 пуска предназначен для формирования сигнала Начало контроля. Блок

5 9 индикации предназначен для световой регистрации наличия ошибки в программе. Блок 10 сравнения предназначен для регистрации наличия переходов, путем сравнения кодов адресов предыдущей команды с последующей.

Элемент 53 сравнения предназначен для выдачи сигнала наличия перехрда на блок 1 памяти при несравнении кодов адресов команд.

Блоки элементов И 54.1-54.п и 55.1-55.ri предназначены для осуществления контроля изменений в разрядах сравниваемых кодов адресов команд с помощью кода маски.

Дешифратор 11 адреса предназначен для выработки сигналов управления программно-доступными блоками схемы, а также выработки сигналов для управления функционированием устройства в соответствии с заданным алгоритмом.

Шифратор 12 кодов предназначен для формирования кодов уставок масштаба времени для автоматической перезаписи в счетчики 6 и 7 времени в соответствии с кодом маски.

Коммутаторы 13 и 14 предназначены для управления записью кодов времени в счетчики 6 и 7 времени либо автоматически с шифратора 12, либо программно.

Элемент И 15 предназначен для пропуска в устройство импульсов тактовой частоты при наличии разрешающего сигнала с выхода триггера 8 пуска.

Элементы И 16, 17, 18 предназначены для осуществления контроля времени обработки участка программы. Элемент И 19 предназначен для контроля времени выполнения контролируемого участка программы, если есть требование строго фиксировать количество обработанных команд в определенный промежуток времени.

Одновибратор 20 предназначен для осуществления синхронизации работы счетчиков 6 и 7 и блока 3 регистров и шифратора 12 кодов при автоматическом задании масштаба уставок времени.

Элемент ИЛИ 21 предназначен для объединения выходов 38 и 39 дешифратора 11 адреса, чтобы сформировать сигнал Конец контролируемого участка.

Элементы ИЛИ 22, 23 предназначены для формирования сигнала синхронизации для управления работой счетчиков 6 и 7 времени.

Элемент ИЛИ 24 предназначен для формирования сигнала Ошибка для блока 9 индикации и запроса на прерывание для микропроцессорной системы.

Устройство работает следующим образом.

Устройство позволяет производить контроль хода выполнения программы как по времени, так и контролировать переходы. Причем контроль по времени возможно реализовать двояким путем (в зависимости от требований к программированию)

с программным заданием интервала времени, в течение которого должны быть обработаны команды данного участка программы;

с автоматическим заданием интервала

времени, причем контролировать выполнение участка программы можно нестрого, в интервале времени Tmin Т Ттах, а также, задаваясь определенным числом команд,

0 которые должны быть обработаны, фиксировать количество выполняемых команд в данный момент времени.

Контроль переходов осуществляется в зависимости от требований к программиро5 ванию, таким образом:

контролируются переходы между участками программы;

контролируются абсолютно все переходы как между участками, так и внутри их.

0 Исходя из изложенного, можно выделить несколько режимов функционирования устройства контроля хода программы:

с автоматическим заданием масштаба уставок времени и контролем абсолютно

5 всех переходов;

с автоматическим заданием масштаба уставок времени и контролем переходов между заданными участками программы; с программным заданием масштаба ус0 тавок времени и контролем абсолютно всех переходов;

с программным заданием масштаба уставок времени и контролем переходов между заданными участками программы.

5 Устройство для микропроцессорной системы является внешним. Связь между устройством и микропроцессорной системой происходит через интерфейсную магистраль.

0

Устройство использует следующие управляющие сигналы микропроцессорной системы; сигнал идентификации машинного цикла Ёыборки команд (метка М1 - пятый

5 разряд слова состояния) - вход 28 устройства; импульсы тактовой частоты, поступающие от генератора микропроцессорной системы, - вход 29 устройства.

В устройстве программно-доступными

0 блоками являются счетчики 6 и 7 времени, регистр 4 контрольной метки, регистр 50 маски, регистр 51 в блоке 3 регистров, каждому блоку соответствует свой программно- неизменяемый номер.

5 В исходном состоянии все элементы памяти обнулены (цепи установки в нуль условно не показаны). При этом в блок 1 памяти, представляющий собой ассоциативное запоминающее устройство, занесе- ны адреса разрешенных переходов.

Рассмотрим функционирование устройства контроля в первом режиме.

Программа составляется с выполнением требований структурности. Программа разбивается на контролируемые участки, причем длина участка (копичество команд)

зависит от длиньГкода маски Nmax 2 - 1, представляющего собой комбинацию 1. обозначающих разряды, которые могут модифицироваться; для каждого контролируе- мого участка эта разрешающая зона может изменяться. Таким образом, фиксируется изменение любого разряда кода адреса. Начало контролируемого участка - код маски, конец обозначается кодом адреса As, идеи- тифицирующим, например, команду вывода OVTPVT.

Микропроцессор (например, К 580) выставляет на шину адреса код адреса регистра 50 маски, а на шину данных код маски.

Адрес регистра 50 маски через группу 26 входов устройства поступает на группу входов дешифратора 11 адреса, а код маски через группу 27 входов устройства поступа ет на группу входов регистра 50 маски блока 3 регистров. Дешифратор 11 адреса расшифровывает адрес регистра 50 маски и на его выходе появляется сигнал, который разрешит запись кода маски в регистр 50 маски. Управляющим сигналом для дешифратора 11 адреса является сигнал идентификации машинного цикла выборки команды (метка Ml - пятый разряд слова состояния) на входе 28 устройства. Код числа с группы 32 выходов регистра 50 маски поступает на шифратор 12, на выходе которого будет сформирован код, обозначающий масштаб времени максимально допустимого выполнения контролируемого участка программы.

Данный код через коммутатор 14 по управляющему сигналу с вь-ходз 40 дешифратора 11 адреса по заднему фронту через одновибратор 20 и через элемент ИЛИ 23 запишется в счетчик 7 максимального вре- мени. Г1о тому же управляющему сигналу с выхода элемента ИЛИ 22 через коммутатор 13 в счетчик 6 минимального времени с группы выходов генератора 2 единиц запишется код, представляющий собой набор логических единиц. Таким образом, в счетчик 6 записан код минимального времени выполнения контролируемого участка, а в счетчик 7 записан код максимального времени выполнения того же участка.

Далее микропроцессор обращается к регистру 4 контрольной метки, т.е.- адрес этого регистра поступает на группу 26 входов устройства и на группу входов дешифратора 11 адреса. По управляющему

сигналу с выхода 41 дешифратора 11 адреса по заднему фронту возбуждается триггер 8 пуска. По сигналу на единичном выходе триггера 3 пуска откроется элемент И 15, тем самым разрешается проход с входа 29 устройства на выход элемента И 15тактовых импульсов.

Сигналы тактовой частоты с выхода элемента И 15 поступают на открытый элемент И 16 и закрытый по инверсному входу элемент И 17. Сигнал с выхода элемента И 16 поступает на счетный вход -1 счетчика 6, содержимое которого уменьшается по мере выполнения команд контролируемого участка программы. Когда счетчик 6 времени обнуляется, сигнал обратного перехода с его выхода закрывает элементы И 16 и 18, а открывает по инверсному входу элемент И 17, через который тактовые импульсы проходят на счетный вход -1 счетчика 7 максимального времени, содержимое которого уменьшается на единицу с приходом каждого тактового импульса. Сигнал Конец конт- роля формируется на выходе 39 дешифратора 11 адреса, по приходу на его группу входов неизменяемого кода адреса As, идентифицирующего команду вывода.

Если дешифратор 11 адреса обнаружит признак конца временного участка раньше, чем обнулится счетчик 6 времени (что соответствует выполнению участка программы за время, меньшее Tmm), то сигнал Конец контроля через открытый элемент И 18, элемент ИЛИ 24 включит блок 9 индикации, поступит на выход 25 устройства и будет воспринят микропроцессорной системой как сигнал ошибки, запрос на прерывание.

Одновременно сигнал Конец контроля переводит триггер 8 пуска в нулевое состояние, закрывая по второму входу элемент И 15. Поступление тактовых импульсов на счетный вход -1 счетчика 6 времени прекращается.

Если дешифратор 11 адреса обнаружит конец проверяемого временного сегмента после обнуления счетчика 6 времени и до обнуления счетчика 7 максимального времени, что соответствует выполнению участка программы за время Т (Tmin Т Ттах). то сигнал Конец контроля переводит в нулевое состояние триггер 8 пуска, закрывает элемент И 15 и прекращает поступление -тактовых импульсов на счетчик 7 максимального времени, так как в этот момент элемент И 18 закрыт, то сигнал Конец контроля не проходит на вход 25 устройства и блок 9 индикации.

Если счетчик 7 максимального времени обнулится до появления кода адреса As (что соответствует выполнению программного

участка за время, большее Ттах), то сигнал обратного переноса с выхода 37 счетчика 7 времени через инверсный вход элемента ИЛИ 24 включит блок 9 индикации, поступит на выход 25 устройства и будет воспринят микропроцессорной системой как запрос на прерывание.

Если необходимо контролировать строго определенное количество команд в заданное время, то программа составляется таким образом, чтобы после адреса As, обозначающего конец контролируемого участка программы, следовал неизменяемый адрес As +1.

При поступлении этого адреса на группу входов дешифратора 11 адреса на выходе 38 дешифратора 11 появится сигнал, который откроет по прямому входу элемент И 19. В этот момент на выходе 36 счетчика 7 времени должен присутствовать сигнал логической единицы, что соответствует тому, что произошла выборка N команд, если же в данный момент будет выбрано больше или меньше, чем N команд, то на выходе 36 счетчика 7 времени будет присутствовать сигнал логического нуля, данный сигнал поступит на инверсный вход элемента И 19, наличие сигнала на выходе которого будет означать присутствие ошибки, что зарегист- рирует блок 9 индикации, а также сигнал ошибки поступит на выход 25 устройства.

Одновременно с контролем времени выполнения программ в устройстве осуществляется контроль переходов. В силу того, что кодом маски можно задавать самые различные зоны изменений разрядов в коде адреса, контролируются абсолютно все переходы.

Контроль переходов осуществляется следующим образом. Как описывалось вы1 ше, регистр 4 контрольной метки является программно-доступным. В регистр 4 контрольной метки программно записывается контрольная метка в начале контроля, т.е. при запуске устройства. В дальнейшем в процессе контроля смеси метки происходит аппаратным путем.

Запись происходит следующим образом. Микропроцессор на шину данных выставляет код контрольной метки, а на шину адреса - код адреса регистра 4. У дешифратора 11 адреса возбуждается выход 41, сигналом с этого выхода информация с группы 27 входов запишется в регистр 4 контрольной метки. В регистр 5 записывается адрес выполняемой текущей команды, который поступает с группы 26 входов устройства, Этот код будет записываться по сигналу, идентифицирующему цикл выборки команды. С групп 34 и 35 выходов регистров 4 и 5

коды поступают на первые и вторые группы входов блока 10 сравнения. Код контрольной метки с выхода 34 регистра 4 поступает на входы блока элементов И 54.1-54.п, а код

текущего адреса поступает на входы блока элементов И 55.1-55.п с группы 35 выходов регистра 5. Код маски с группы 33 выходов регистра 51 поступает на соответствующие входы элементов И 54,1-54.п и 55.1-55.п блоков,

Таким образом, коды на группах выходов элементов И 54.1-54.п и 55.1-55.п будут сформированы в соответствии с законом расстановки 1 и О в коде маски, т.е. любое изменение разрядов в маскируемой зоне в коде адреса, что соответствует переходу, будет зафиксировано в кодах на группах выходов блоков элементов И 54.1- 54.n4i 55.1-55.п. Данные коды поступают на

первую и вторую группы входов блока 53 сравнения соответственно, где по заднему фронту управляющего сигнала с выхода 28 устройства (который идентифицирует выборку команды - метка М1) проходит сравнение этих кодов. Сигнал несовпадения кодов на выходе блока 10 сравнения поступает на управляющий вход блока 1 памяти. Одновременно с поступлением кодов контрольной метки и текущего адреса на блок 10

сравнения, они поступают на соответствующие группы 34 и 35 входов блока 1 памяти, Блок 1 памяти проверяет, является ли совершенный программой переход разрешенным. Код с группы 34 входов блока 1 памяти

является адресом, по которому в перепрограммируемом запоминающем устройстве 45 содержатся адреса всех возможных разрешенных переходов из данного адреса. Считанные коды адресов поступают на первые группы входов соответствующих элементов сравнения 46.1-46,п блока, где они сравниваются с кодом адреса текущей команды.

Если происходит сравнение, т.е. переход разрешен, то на выходе 31 блока 1 памяти появляется сигнал перезаписи кода адреса текущей команды в регистр 4 контрольной метки, где с этого момента дйнный код становится контрольным. В противном

случае на выходе 30 блока 1 памяти появляется сигнал Ошибка.

Следующие коды адресов текущих команд сравниваются с новым контрольным кодом (по существу, кодом адреса предыдущей команды).

В случае запрещенного перехода сигнал Ошибка поступает на вход элемента ИЛИ 24, включает блок 9 индикации и посту- пает на выход 25 устройства для перевода

микропроцессорной системы в режим прерывания.

Таким образом, устройство выдает сигнал ошибки в случае, когда программа выполняется не в расчетное время, а также при любом запрещенном переходе.

Рассмотрим работу устройства во втором режиме (с автоматическим заданием масштаба установок времени и контролем переходов между заданными участками программы). Как указывалось выше/выбор функционирования устройства в том или ином режиме зависит от требований к устройству контроля и требований к программированию. Как и для первого режима программа разбивается на программные участки. Началом контролируемого участка считается код маски, конец обозначается кодом адреса As (например, команда вывода). К разрядов адреса команды представляют в виде двух частей: изменяемой части, содержащей I разрядов, и неизменяемой части, содержащей (К-l) разрядов, называемой меткой участка. В участок включаются команды с одинаковой меткой. Для одного участка разряды меток должны совпадать,

Контроль времени с автоматическим заданием масштаба уставок времени происходит аналогично описанному для первого режима.

Одновременно с контролем времени происходит контроль переходов. В отличие от первого режима после записи кода маски в регистр 50 маски и записи кода контрольной метки в регистр 4 контрольной метки по управляющему сигналу с выхода 41 дешифратора 11 адреса происходит программное обращение к регистру 51. Неизменяемый адрес этого регистра поступает на группу входов дешифратора 11, в результате возбуждается выход 42.

Сигнал с этого выхода 42 дешифратора 11 адреса установит триггер 52 установки в единичное состояние, сигнал на единичном выходе триггера 52 поступит на установочный вход регистра 51, который будет удерживаться в единичном состоянии в течение всего режима (т.е. происходит отключение регистра 51). (Триггер 52 установки обнуляется сигналом запуска системы с выхода 41 дешифратора 11 адреса при обращении к регистру 4 контрольной метки в начале выполнения программы при всяком режиме).

В регистр 5 записывается текущая метка по управляющему сигналу, иденцифици- рующему цикл выборки команды.

С группы 34 выходов регистра 4 контрольной метки и группы 35 выходов регистра 5 коды метки поступают на соответствующие группы входов блока 10

сравнения, где коды сравниваются. Код маски представляет собой набор единиц, так как регистр 51 установлен в единичное состояние, следовательно, этот код не оказывает влияния на работу блока 10 сравнения. Пока текущая темка принадлежит проверяемому участку, при правильном выполнении программы коды меток должны совпадать. Несовпадение меток может произойти

0 при наличии в участке программы команды, передающей управление другому участку - разрешенный переход, а также при попытке программы выполнить запрещенный переход, что обусловлено наличием неисправно5 сти в микропроцессорной системе. При несовпадении меток на выходе блока 10 сравнения появляется сигнал, поступающий на управляющий вход блока 1 памяти. Одновременно на группу 32 входов бло0 ка 1 памяти поступает код контрольной метки, а на группу 33 входов поступает код текущей метки. Блок 1 памяти проверяет, является ли переход разрешенным. Код контрольной метки является адресом, по кото5 рому в перепрограммируемом запоминающем устройстве 45 записаны разрешенные переходы.

Если текущая метка разрешена, то на выходе 31 блока 1 памяти при наличии раз0 решающего сигнала с блока 10 сравнения появляется сигнал Смена метки, в противном случае на выходе 30 блока 1 памяти появится сигнал Ошибка. Сигнал Смена метки перепишет текущую метку в регистр

5 4 контрольной метки, а сигнал Ошибка включает бпок 9 индикации и поступает на выход 25 устройства, а затем в микропроцессорную систему как запрос на прерывание.

0

Рассмотрим функционирование устройства контроля в третьем режиме (с программным заданием масштаба уставок времени и контролем абсолютно всех переходов).

5

Программа для третьего режима составляется аналогично описанному для первого режима за исключением того, что вслед за командой записи кода маски в регистр 50

0 маски следуют программные обращения к счетчикам 6 и 7 времени, причем обращением к этим счетчикам является начало каждо- го временного участка. В счетчик 6 времени записывается минимальное время Tmin вы5 полнения временного участка программы, а в счетчик 7 времени - разница между максимальным и минимальным временем ДТ Ттах - Tmin. Конец временного участка обозначается неизменяемым адресом А8(при необходимости ставится и адрес As + 1).

Код маски в этом режиме используется исключительно для контроля абсолютно всех переходов, как в первом режиме.

Фукнционирование устройства в третьем режиме начинается программным обращением к регистру 50 маски. Код маски запишется в регистр 50 маски по управляющему сигналу с выхода 40 дешифратора 11 адреса. Далее при программном обращении к счетчику 6 времени на группе 26 адресных входов устройства появляется адрес счетчика 6 времени, сопровождающийся управляющим сигналом на входе 28 устройства. Управляющий сигнал разрешает работу дешифратора 11 адреса, который вырабатывает на своем выходе 44 сигнал, разрешающий прохождение кода коммутатор 13 и запись по заднему фронту в счетчик 6 времени кода временного интервала Tmin. Аналогично записи в счетчик 6 происходит запись временного интервала в счетчик 7 времени сигналом с выхода 43 дешифратора 11 адреса при программном обращении к счетчику 7 времени.

Таким образом, информация, записанная в счетчики при обращении к регистру 50 маски, будет заменена программно-принудительно. Контроль начинается при обращении к регистру 4 контрольной метки, т.е. сигнал с выхода 41 дешифратора 11 адреса установит в единичное состояние триггер 8 пуска, открывая тем самым элемент И 15 для пропуска тактовых импульсов с входа 29 устройства.

Работа счетчиков 6 и 7 будет происходить аналогично описанному в первом режиме. Далее контроль времени, а также контроль переходов происходит аналогично описанному в первом режиме. Программная запись временных интервалов позволяет вводить коррекцию по ходу выполнения программы.

Рассмотрим характерные особенности функционирования устройства контроля в четвертом режиме (с программным заданием масштаба уставок времени и контролем переходов между заданными участками программы).

В этом режиме программа составляется следующим образом. Программа разбивается на временные участки. Начало каждого временного участка обозначается программным обращением к счетчикам 6 и 7 времени. Конец каждого временного участка обозначается приходом кода адреса As(). К разрядов адреса команды представляют в виде двух частей: изменяемой части т неизменяемой части, метка участка. В участок включаются команды с одинаковой меткой.

Таким образом, контроль времени в четвертом режиме происходит, как описано в третьем режиме, а контроль переходов осуществляется, как описано во втором режц- ме.

Формула изобретения Устройство для контроля хода программы, содержащее блок памяти, первый и второй регистры, первый и второй счетчики времени, триггер пуска, блок индикации, блок сравнения, дешифратор адреса, первый, второй, третий и четвертый элементы И и первый элемент ИЛИ, причем первый выход блока памяти подключен к первому прямому входу первого элемента ИЛИ, выход которого соединен со входом блока индикации и является выходом ошибки устройства, второй выход блока памяти соединен с первым входом записи первого регистра, группа выходов которого соединена с первой группой информационных входов блока сравнения и с группой адресных входов блока памяти, группа выходов второго регистра

соединена с первой группой информационных входов первого регистра, группой информационных входов блока памяти и второй группой информационных входов блока сравнения, прямой выход триггера пуска соединен с первым входом первого элемента И, выход которого соединен с первым и прямым входами соответственно второго и третьего элементов И, выход переполнения первого счетчика времени соединен с

вторым входом второго элемента И, с инверсным входом третьего элемента И и с первым входом четвертого элемента И, выход третьего элемента И соединен со счетным входом второго счетчика времени, выход переполнения которого соединен с инверсным входом первого элемента ИЛИ, выход равенства блока сравнения соединен с входом обращения блока памяти, первый выход дешифратора адреса соединен с вторым входом записи первого регистра, выходы второго и четвертого элементов И соединены соответственно со счетным входом первого счетчика времени и вторым прямым входом первого элемента ИЛИ,

группа адресных входов устройства соединена с группами информационных входов дешифратора адреса и второго регистра, группа информационных входов устройства соединена с второй группой информационных входов первого регистра, вход признака зыборш команды устройства соединен со етробирующим входом дешифратора адреса, входом записи второго регистра, тактовый вход устройства соединен с вторым входом первого элемента И, отличаю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены генератор единиц, блок регистров, шифратор кодов, первый и второй коммутаторы, пятый элемент И, одновибратор, второй, третий и четвертый элементы ИЛИ, причем группа информационных выходов генератора единиц соединена с первой группой информационных входов первого коммутатора, группа выходов, которого соединена с труп- пой информационных входов первого счетчика времени, первая группа выходов блока регистров соединена с группой входов шифратора кодов, группа выходов которого соединена с первой группой информационных входов второго коммутатора, вторая группа выходов блока регистров соединена с третьей группой информационных входов блока сравнения, выход заема второго счетчика времени соединен с инверсным вхо- дом пятого элемента И, выход которого соединен с четвертым прямым входом первого элемента ИЛИ, первый выход дешифратора адреса соединен с единичным установочным входом триггера пуска и вто- рым входом записи первого регистра, второй выход дешифратора адреса соединен с прямым входом пятого элемента И и с первым входом второго элемента ИЛИ, третий выход дешифратора адреса соединен с

вторым входом второго элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска и вторым входом четвертого элемента И, четвертый выход дешифратора адреса соединен с входом записи блока регистров и входом одновибратора, выход которого соединен с первыми управляющими входами первого и второго коммутаторов и первыми входами третьего и четвертого элементов ИЛИ, пятый выход дешифратора адреса соединен с третьим входом блока регистров, шестой выход дешифратора адреса соединен с вторым управляющим входом второго коммутатора и вторым входом четвертого элемента ИЛИ, выход которого соединен с синхровходом второго счетчика времени, седьмой выход дешифратора адреса соединен с вторым управляющим входом первого коммутатора и вторым входом третьего элемента ИЛИ, выход которого соединен с синхровходом первого счетчика времени, группа выходов второго коммутатора соединена с группой информационных входов второго счетчика времени, вторая группа входов устройства соединена с вторыми группами информационных входов первого и второго коммутаторов и группой входов блока регистров, вход признака выборки команды устройства соединен с входом разрешения блока сравнения.

flfr/J

28, 35

1

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1615726A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля хода программы ЭВМ, а также для отладки их программного обеспечения. Цель изобретения - повышение достоверности контроля. В устройство для контроля программы, содержащее блок 1 памяти, первый и второй регистры 4 и 5, первый и второй счетчики 6 и 7 времени, триггер 8 пуска, блок 9 индикации, блок 10 сравнения, дешифратор 11 адреса, элементы И 15 - 18, элемент ИЛИ 21, введены генератор 2 единиц, блок 3 регистров, шифратор 12 кодов, первый коммутатор 13, второй коммутатор 14, пятый элемент И 19, одновибратор 20, второй элемент ИЛИ 23, четвертый элемент ИЛИ 24. Сущность изобретения заключается в повышении достоверности контроля за счет реализации возможности функционирования в четырех новых режимах: с автоматическим заданием масштаба уставок времени и контролем всех переходов

с автоматическим заданием масштаба уставок времени и контролем всех переходов между заданными участками программы

с программным заданием масштаба уставок времени и контролем всех переходов

с программным заданием масштаба уставок времени и контролем переходов между заданными участками программы. 5 ил.

54/7

3ScL

Составитель И.Сигалов Редактор Т.КлюкинаТехред М.МоргенталКорректор И.Муска

Заказ 2266Тираж 417Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб.. 4/5

Н1

фиг А

фиг. 5

| Устройство для отладки программ | 1986 |

|

SU1363220A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1176336A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-15—Публикация

1988-09-30—Подача