Изобретение относится к вычислительной технике, может быть использовано в цифровых устройствах для контроля арифметических операций и является усовершенствованием изобретения по авт. св. № 1105896.

Известно устройство для формирования остатка по модулю три с пирамидальной сверткой, содержащее п ступеней, каждая из которых содержит сумматоры, n-я ступень свертки содержит сумматор по модулю три, информационные выходы которого являются выходами свертки, ступени свертки с первой по (л-1)-ю содержат сумматоры по модулю 15, выходы переноса каждого сумматора 1-й ступени (,п) свертки соединены с входом переноса этого сумматора, входы нечетных и четных разрядов сумматоров первой ступени свертки являются входами нечетных и четных разрядов контролируемого числа, входы нечетных и четных разрядов сумматоров J-й ступени свертки (,n-1) соединены соответственно с нечетными и четными входами двух смежных сумматоров (п-1)-й ступени свертки, входы нечетных и четных разрядов сумматора по модулю три соединены соответственно с выходами нечетных и четных разрядов сумматора по модулю 15 (п-1)-й ступени.

Недостатком этого устройства является низкая достоверность его функционирования.

сь

Ю

ел

со

о

со

го

Целью изобретения является повышение достоверности функционирования устройства путем обнаружения ошибок.

Указанная цель достигается тем, что в устройство введены группа из N сумматоров по модулю два (N - четное), первый и второй элементы И, элементы И-НЕ, регистр, первый и второй узлы сравнения, элемент ИЛИ и триггер, причем первые входы сумматоров по модулю два группы являются входами устройства, вторые входы объединены между собой, подключены к синхровходам регистра и триггера и являются тактовым входом устройства, а выходы соединены с соот- ветсвтующими входами сумматоров перавой ступени, входы сброса триггера м регистра объединены между собой и подключены к входу начальной установки устройства, выходы сумматора по модулю три подключены к первым входам первого я второго элементов И, а также к первому и второму входам элемента И-НЕ, выход которого подключен к объединенным между собой вторым входам первого и второго элементов И, выходы которых подключены к соответствующим входам регистра, первый и второй выходы которого соединены соответственно с вторым и пер- I вым входами соответственно первого и вто- , рого узлов сравнения, первые и вторые входы которых подключены соответственно к выходам первого и второго элементов И, а выходы подключены к входам элемента ИЛИ, выход которого соединен с информационным входом триггера, выход которого является контрольным выходом устройства,

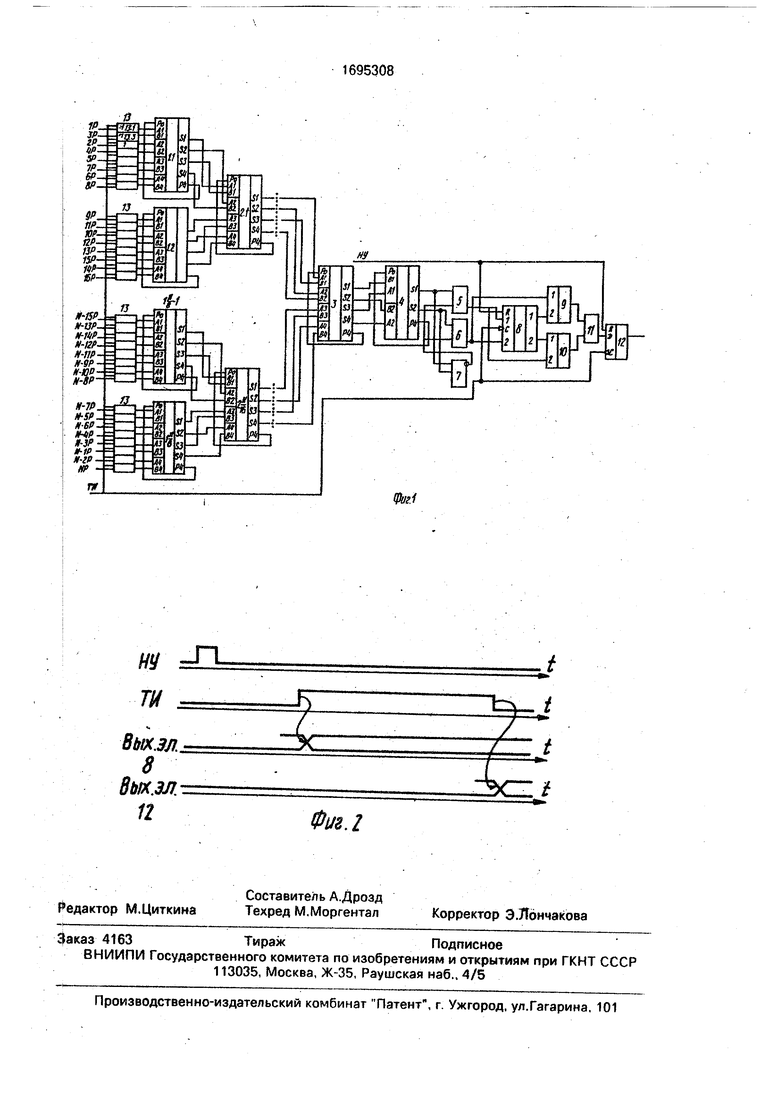

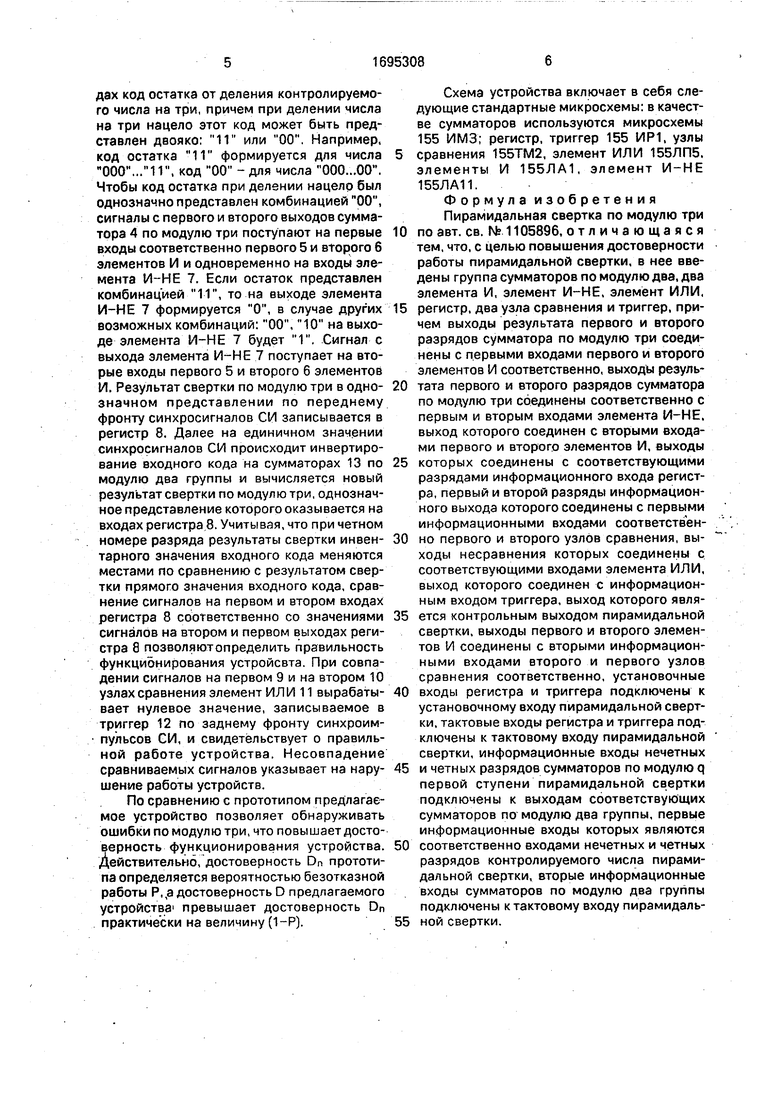

На фиг.1 приведена структурная схема устройства; на фиг.2 - временная диаграмма работы устройства.

Устройство содержит п ступеней, каждая из которых содержит сумматоры 13.1,13.2,...,13.N по модулю даа; сумматоры

1.1,1.2,,,.1.(-g- - 1),1.-g-rro модулю 15 первой

ступени,- сумматоры 2.1,2.2,,,,, 2-щ второй

ступени, сумматор 3 (п-1)-й ступени, сумматор 4 по модулю три n-й ступени, первый 5 и второй б элементы И, элемент И-НЕ 7, регистр 8, первый 9 и второй 10 узлы сравнения, элемент ИЛИ 11, триггер 12, причем

первые входы сумматоров 13.1,13.2(N1},13.М являются входами устройства, вторые входы объединены между собой, подключены к синхровходам регистра 8 и триггера 12 и являются тактовым входом устройства, выходы переноса Каждого сумматора t-й ступени (М,п) свертки соединены с входом переноса сумматора первой ступени, входы нечетных и четных разрядов сумматора j-й ступени ,n-1) соединены

соответственно с нечетными и четными выходами соседних сумматоров (|-1)-й ступени, входы нечетных и четйых разрядов сумматоров 4 по модулю три соединены соответственно с выходами нечетных и четных разрядов сумматора 3 (п-1)-й ступени, а первый и второй выходы сумматора 4 по модулю три соединены с одним из входов первого 5 и второго 6 элементов И соответ0 ственно и одновременно являются входами

элемента И-НЕ 7, выход которого соединен

с остальными входами первого 5 и второго

8 элементов И, выходы которых подключены

к соответствующим входам регистра 8, пер5 вый и второй выходы которого соединены с вторым и первым входами соответственно первого 9 и второго 10 узлов сравнения, первые и вторые входы которых подключены соответственно к выходам первого 5 и второго

0 элементов И, а выходы подключены к входам

элемента ИЛИ 11, выход которого соединен с

информационным входом триггера 12, выход

которого является выходом устройства.

Устройство работает следующим обра5 зом,

В начале работы триггер 12 и регистр 8 устанавливаются по входу сброса в ноль сигналом, поступающим на вход начальной установки устройства. На тактовый вход

0 устройства поступают синхроимпульсы СИ типа Меандр. На первом полутакте синхроимпульсы принимают нулевое значение и входной N-разрядный код (N - четное), поступающий на первые входы сумматоров

5 по модулю два, группы 13 транслируются (при нулевом значении сигнала СИ на вторых входах) и далее на входы сумматоров первой ступени без изменения, причем на входы нечетных разрядов сумматоров

1,1,1.2,...,1.(-g- - 1),1,-g-, подаются нечетные разряды числа, на входы четных разрядов сумматоров -четные разряды числа, сигнал с выхода переноса каждого сумматора i-й ступени

5 ,п) поступает на вход переноса этого же сумматора, в результате чего каждый из сумматоров k-й ступени ( ,n-2) формирует на выходе свертку по модулю 15 подаваемых на его входы разрядов. С выходов нечетных

0 и четных разрядов двух соседних сумматоров k-й ступени ( ,n-2) поступают сигналы на аходы соответственно нечетных и четных разрядов сумматоров (1сИ)-й ступени. Сумматор ()-й ступени 3 формирует на своем

5 выходе свертку по модулю 15 входного.чисяа. С выходов нечетных и четных разрядов этого сумматора 3 сигналы поступают на входы соответственно нечетных и четных разрядов сумматора 4 по модулю три п-й ступени, который формирует на своих выходах код остатка от деления контролируемого числа на три, причем при делении числа на три нацело этот код может быть представлен двояко: 11 или 00. Например, код остатка 11 формируется для числа 000...11, код 00 - для числа 000...00. Чтобы код остатка при делении нацело был однозначно представлен комбинацией 00, сигналы с первого и второго выходов сумматора 4 по модулю три поступают на первые входы соответственно первого 5 и второго б элементов И и одновременно на входы элемента И--НЕ 7. Если остаток представлен комбинацией 11, то на выходе элемента И-НЕ 7 формируется О, в случае других возможных комбинаций: 00, 10 на выходе элемента И-НЕ 7 будет 1. Сигнал с выхода элемента И-НЕ 7 поступает на вторые входы первого 5 и второго 6 элементов И. Результат свертки по модулю три в одно- значном представлении по переднему фронту синхросигналов СИ записывается в регистр 8. Далее на единичном значении синхросигналов СИ происходит инвертирование входного кода на сумматорах 13 по модулю два группы и вычисляется новый результат свертки по модулю три, однозначное представление которого оказывается на входах регистра 8. Учитывая, что при четном номере разряда результаты свертки инвен- тарного значения входного кода меняются местами по сравнению с результатом свертки прямого значения входного кода, сравнение сигналов на первом и втором входах регистра 8 соответственно со значениями сигналов на втором и первом выходах регистра 8 позволяютопределить правильность функционирования устройсвта. При совпадении сигналов на первом 9 и на втором 10 узлах сравнения элемент ИЛИ 11 вырабаты- вает нулевое значение, записываемое в триггер 12 по заднему фронту синхроимпульсов СИ, и свидетельствует о правильной работе устройства. Несовпадение сравниваемых сигналов указывает на нару- шение работы устройств.

По сравнению с прототипом предлагаемое устройство позволяет обнаруживать ошибки по модулю три, что повышает достоверность функционирования устройства. Действительно, достоверность Dn прототипа определяется вероятностью безотказной работы Рча достоверность D предлагаемого устройства1 превышает достоверность Dn практически на величину (1-Р).

Схема устройства включает в себя следующие стандартные микросхемы: в качестве сумматоров используются микросхемы 155 ИМЗ; регистр, триггер 155 ИР1, узлы сравнения 155ТМ2, элемент ИЛИ 155ЛП5. элементы И 155ЛА1, элемент И-НЕ 155ЛА11.

Формула изобретения Пирамидальная свертка по модулю три по авт. св. № 1105896, отличающаяся тем, что, с целью повышения достоверности работы пирамидальной свертки, в нее введены группа сумматоров по модулю два, два элемента И, элемент И-НЕ, элемент ИЛИ, регистр, два узла сравнения и триггер, причем выходы результата первого и второго разрядов сумматора по модулю три соединены с первыми входами первого и второго элементов И соответственно, выходы результата первого и второго разрядов сумматора по модулю три соединены соответственно с первым и вторым входами элемента И-НЕ, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединены с соответствующими разрядами информационного входа регистра, первый и второй разряды информационного выхода которого соединены с первыми информационными входами соответственно первого и второго узлов сравнения, выходы несравнения которых соединены с соответствующими входами элемента ИЛИ, выход которого соединен с информационным входом триггера, выход которого является контрольным выходом пирамидальной свертки, выходы первого и второго элементов И соединены с вторыми информационными входами второго и первого узлов сравнения соответственно, установочные входы регистра и триггера подключены к установочному входу пирамидальной свертки, тактовые входы регистра и триггера подключены к тактовому входу пирамидальной свертки, информационные входы нечетных и четных разрядов сумматоров по модулю q первой ступени пирамидальной свертки подключены к выходам соответствующих сумматоров по модулю два группы, первые информационные входы которых являются соответственно входами нечетных и четных разрядов контролируемого числа пирамидальной свертки, вторые информационные входы сумматоров по модулю два группы подключены к тактовому входу пирамидальной свертки.

L

5

3

Фиг. 2

/

m

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для пирамидальной свертки по модулю три | 1988 |

|

SU1520524A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1987 |

|

SU1425678A1 |

| Пирамидальная свертка по модулю три | 1982 |

|

SU1105896A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Запоминающее устройство с контролем информации | 1986 |

|

SU1437924A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1332321A2 |

Изобретение относится к вычислительной технике и позволяет вычислять и контролировать остаток по модулю три. Цель изобретения - повышение достоверности работы устройства. Устройство содержит п ступеней свертки. Ступени с первой по (п- 1)-ю содержат сумматоры по модулю 15, обеспечивающие вычисление остатка отделения числа на 15. Этот остаток поступает на входы сумматора по модулю три n-й ступени, формирующего код остатка от деления числа на три. Элементы И и И-НЕ преобразуют код остатка к однозначному представлению. Код записывается в регистр. На втором полутакте работы устройства входной код инвертируется на сумматорах по модулю два группы и на входах регистра формируется однозначное представление кода остатка инвеосией входного кода. Узлы сравнения сравнивают значения первого и второго разрядов на входах регистра и второго и первого разрядов на его выходах. При несовпадении хотя бы одной пары сравниваемых сигналов элемент ИЛИ вырабатывает сигнал ошибки, принимаемый триггером 2 ил. w W Ј

| Способ рельефографической записи многоцветного изображения на фототермопластический носитель | 1982 |

|

SU1105856A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-11-09—Подача