§

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для возведения в квадрат | 1987 |

|

SU1451686A1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных и универсальных ЭВМ. Цель изобретения - повышение достоверности функционирования. Устройство содержит регистр 1 операнда, группы 2, 3 элементов И, сумматоры 4, 5, коммутатор 6, регистр 7, сумматор 8 контроля, регистры 9, 10 контроля, триггеры 11, 12, счетчик 13, элемент НЕ 14, мультиплексор 15 с соответствующими связями. 4 ил.

и

СП

СО

Јъ

сд

00

N)

Фиг.1

Изобретение относится к вычислительной технике, может быть использовано в специализированных и универсальных ЭВМ и является усовершенствованием устройства по авт. св. У 1451686.

Цель изобретения - повышение достоверности функционирования.

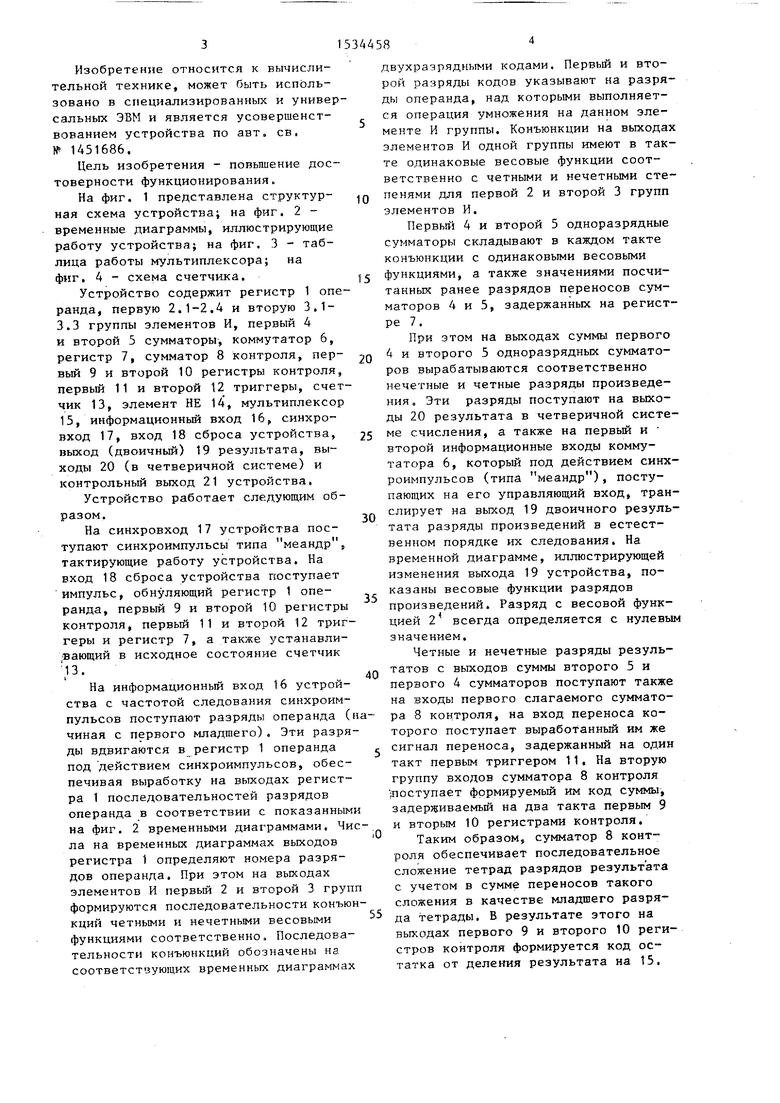

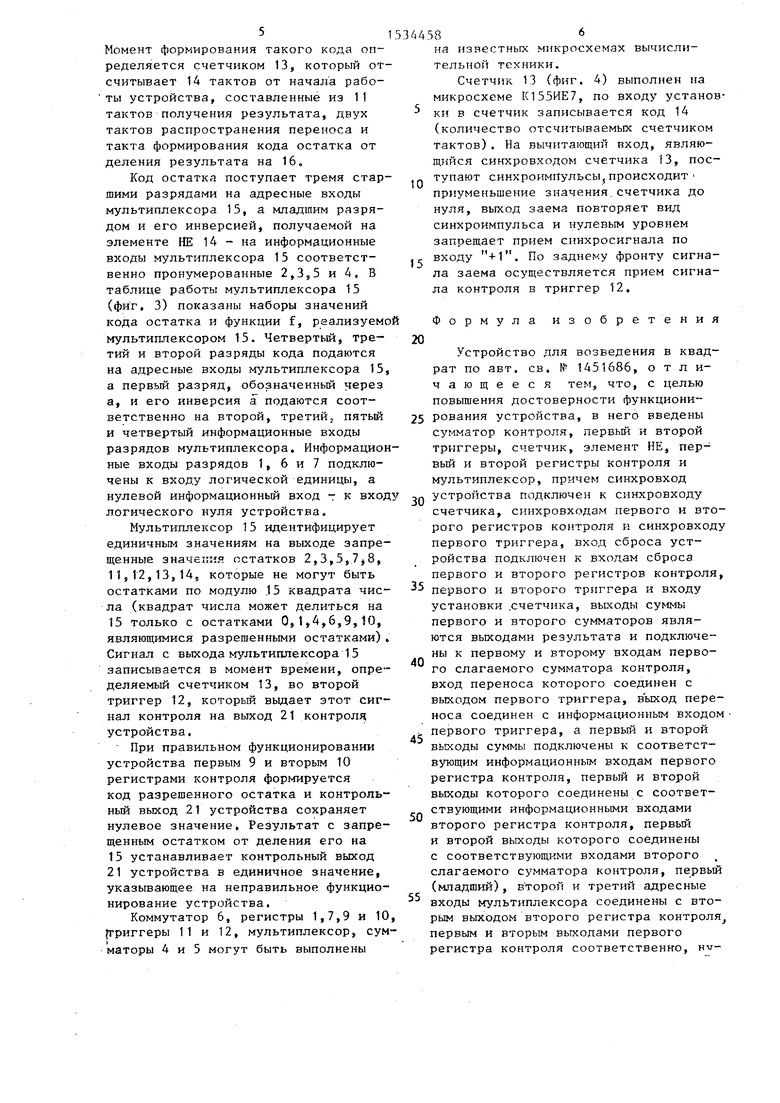

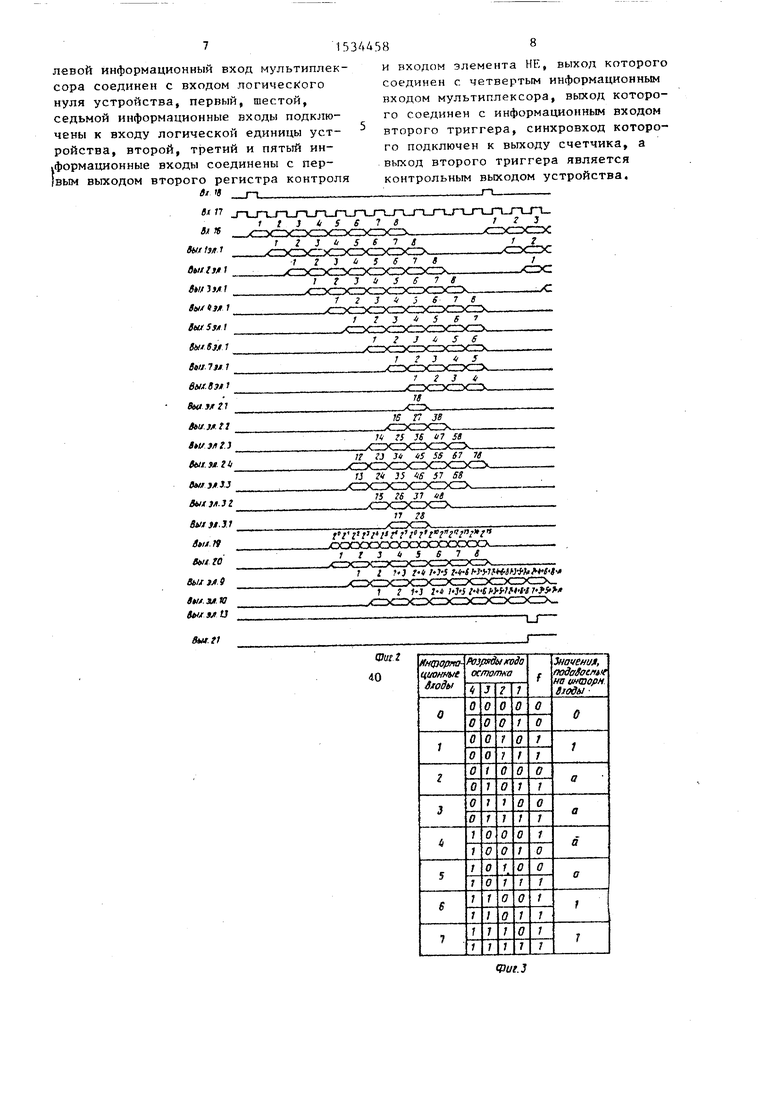

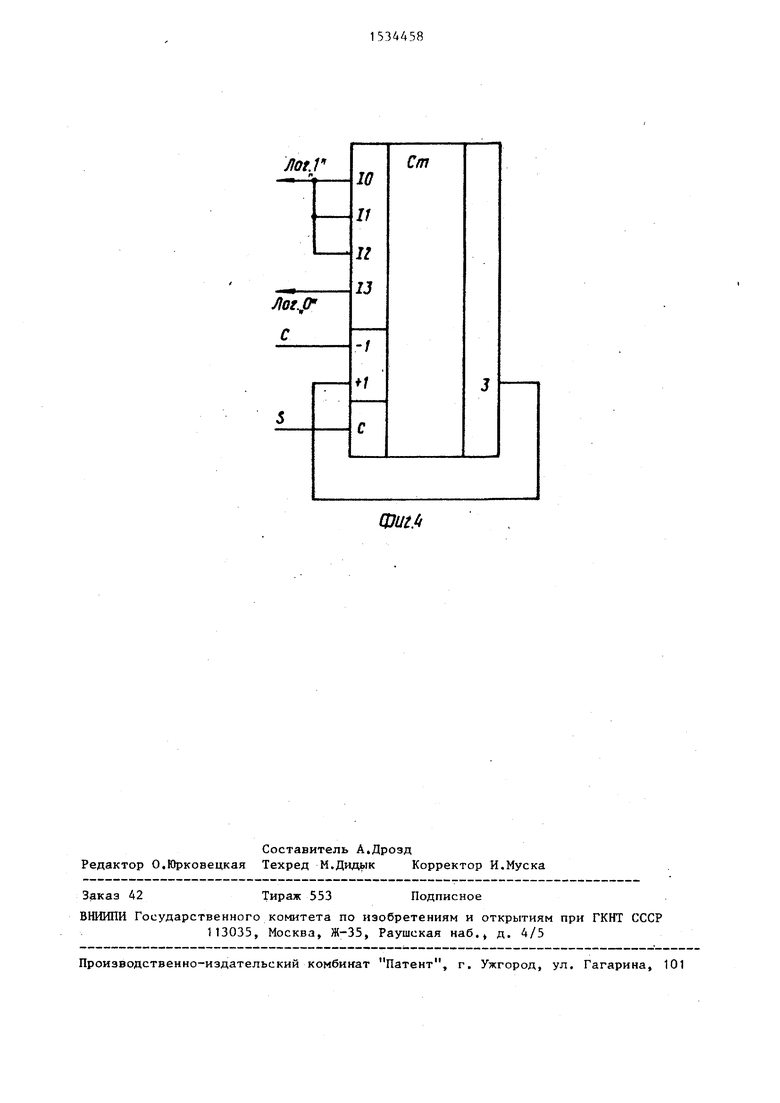

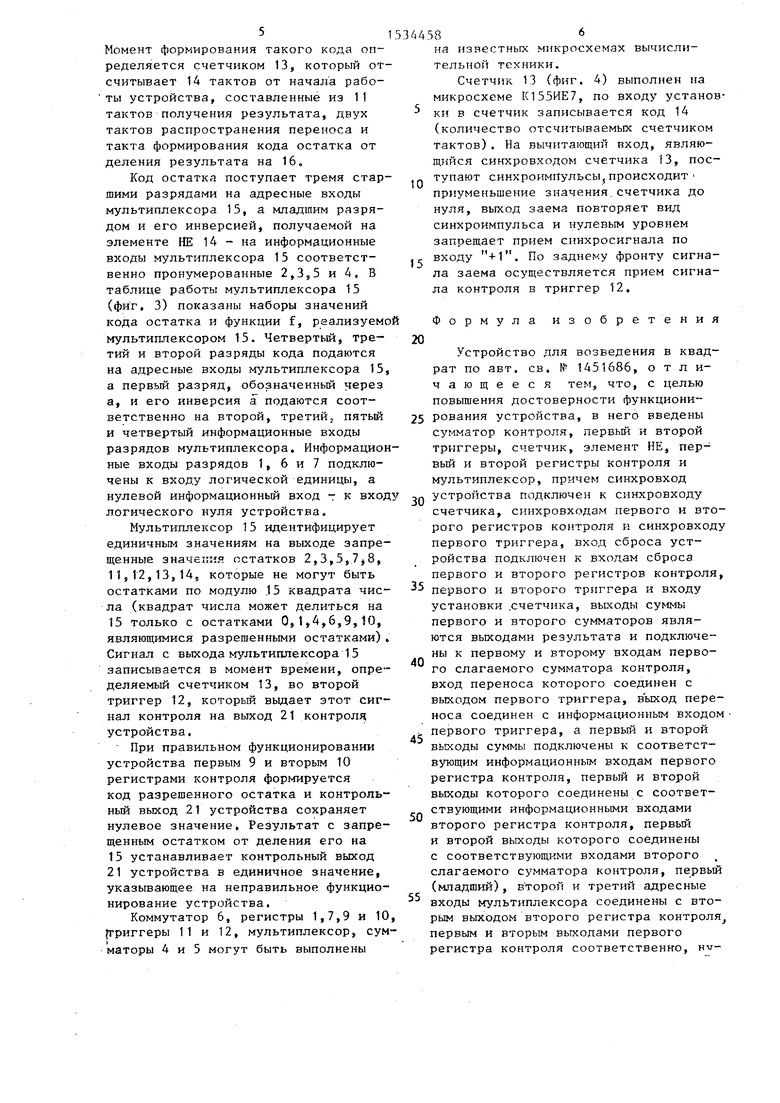

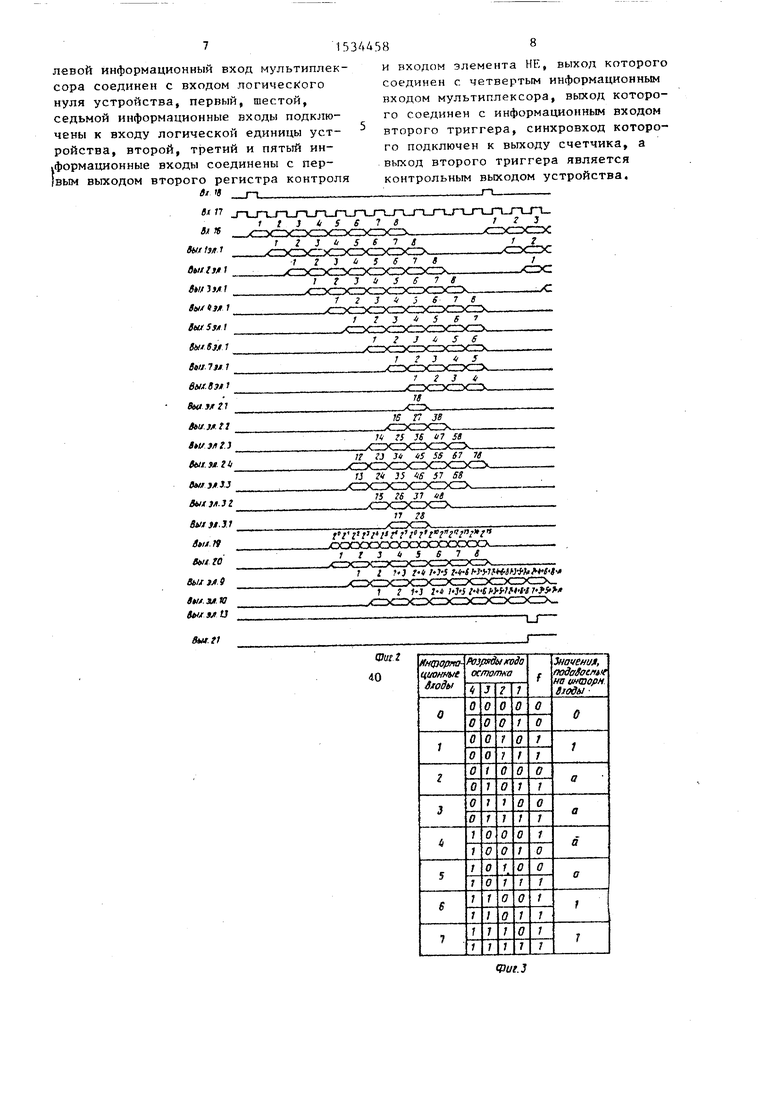

На фиг. 1 представлена структур- ная схема устройства; на фиг. 2 - временные диаграммы, иллюстрирующие работу устройства; на фиг. 3 - таблица работы мультиплексора; на фиг. 4 - схема счетчика.

Устройство содержит регистр 1 операнда, первую 2.1-2.4 и вторую 3.1- 3.3 группы элементов И, первый 4 и второй 5 сумматоры, коммутатор 6, регистр 7, сумматор 8 контроля, пер- вый 9 и второй 10 регистры контроля, первый 11 и второй 12 триггеры, счетчик 13, элемент НЕ 14, мультиплексор 15, информационный вход 16, синхро- вход 17, вход 18 сброса устройства, выход (двоичный) 19 результата, выходы 20 (в четверичной системе) и контрольный выход 21 устройства.

Устройство работает следующим образом.

На синхровход 17 устройства поступают синхроимпульсы типа меандр, тактирующие работу устройства. На вход 18 сброса устройства поступает импульс, обнуляющий регистр 1 операнда, первый 9 и второй 10 регистры контроля, первый 11 и второй 12 триггеры и регистр 7, а также устанавли- вающий в исходное состояние счетчик 13.

На информационный вход 16 устройства с частотой следования синхроимпульсов поступают разряды операнда (нчиная с первого младшего). Эти разряды вдвигаются в регистр 1 операнда под действием синхроимпульсов, обеспечивая выработку на выходах регистра 1 последовательностей разрядов операнда в соответствии с показанными на фиг. 2 временными диаграммами. Числа на временных диаграммах выходов регистра 1 определяют номера разрядов операнда. При этом на выходах элементов И первый 2 и второй 3 групп формируются последовательности конъюнкций четными и нечетными весовыми функциями соответственно. Последовательности конъюнкций обозначены на соответствующих временных диаграммах

5

0

,

5

0

двухрачрядными кодами. Первый и второй рачряды кодов указывают на разряды операнда, над которыми выполняется операция умножения на данном элементе И группы. Конъюнкции на выходах элементов И одной группы имеют в такте одинаковые весовые функции соответственно с четными и нечетными степенями для первой 2 и второй 3 групп элементов И.

Первый 4 и второй 5 одноразрядные сумматоры складывают в каждом такте конъюнкции с одинаковыми весовыми функциями, а также значениями посчитанных ранее разрядов переносов сумматоров 4 и 5, задержанных на регистре 7.

При этом на выходах суммы первого 4 и второго 5 одноразрядных сумматоров вырабатываются соответственно нечетные и четные разряды произведения. Эти разряды поступают на выходы 20 результата в четверичной системе счисления, а также на первый и второй информационные входы коммутатора 6, который под действием синхроимпульсов (типа меандр), поступающих на его управляющий вход, транслирует на выход 19 двоичного результата разряды произведений в естественном порядке их следования, На временной диаграмме, иллюстрирующей изменения выхода 19 устройства, показаны весовые функции разрядов произведений. Разряд с весовой функцией 2 всегда определяется с нулевым значением.

Четные и нечетные разряды результатов с выходов суммы второго 5 и первого 4 сумматоров поступают также на входы первого слагаемого сумматора 8 контроля, на вход переноса которого поступает выработанный им же сигнал переноса, задержанный на один такт первым триггером 11. На вторую группу входов сумматора 8 контроля поступает формируемый им код суммы, задерживаемый на два такта первым 9 и вторым 10 регистрами контроля.

Таким образом, сумматор 8 контроля обеспечивает последовательное сложение тетрад разрядов результата с учетом в сумме переносов такого сложения в качестве младшего разряда тетрады. В результате этого на выходах первого 9 и второго 10 регистров контроля формируется код остатка от деления результата на 15.

Момент формирования такого кода определяется счетчиком 13, который отсчитывает 14 тактов от начала работы устройства, составленные из 11 тактов получения результата, двух тактов распространения переноса и такта формирования кода остатка от деления результата на 16.

Код остатка поступает тремя старшими разрядами на адресные входы мультиплексора 15, а младшим разрядом и его инверсией, получаемой на элементе НЕ 14 - на информационные входы мультиплексора 15 соответственно пронумерованные 2,3,5 и 4. В таблице работы мультиплексора 15 (фиг. 3) показаны наборы значений кода остатка и функции f, реализуемо мультиплексором 15. Четвертый, третий и второй разряды кода подаются на адресные входы мультиплексора 15, а первый разряд, обозначенный через а, и его инверсия а подаются соответственно на второй, третий, пятый и четвертый информационные входы разрядов мультиплексора. Информационные входы разрядов 1, 6 и 7 подключены к входу логической единицы, а нулевой информационный вход - к вход логического нуля устройства.

Мультиплексор 15 идентифицирует единичным значениям на выходе запрещенные значения остатков 2,3,5,7,8, 11,12,13,14, которые не могут быть остатками по модулю 15 квадрата числа (квадрат числа может депнться на 15 только с остатками 0,1,4,6,9,10, являющимися разрешенными остатками). Сигнал с выхода мультиплексора 15 записывается в момент времени, определяемый счетчиком 13, во второй триггер 12, который выдает этот сигнал контроля на выход 21 контроля устройства.

При правильном функционировании устройства первым 9 и вторым 10 регистрами контроля формируется код разрешенного остатка и контрольный выход 21 устройства сохраняет нулевое значение. Результат с запрещенным остатком от деления его на 15 устанавливает контрольный выход 21 устройства в единичное значение, указывающее на неправильно функционирование устройства.

Коммутатор 6, регистры 1,7,9 и 10 триггеры 11 и 12, мультиплексор, сумматоры 4 и 5 могут быть выполнены

0

5

на иэпегтных микросхемах вычислительном техники.

Счетчик 13 (фиг. 4) выполнен на микросхеме К155ИЕ7, по входу установки в счетчик записывается код 14 (количество отсчитываемых счетчиком тактов). На вычитающий пход, являющийся синхровходом счетчика 13, поступают синхроимпульсы,происходит приуменьшение значения счетчика до нуля, выход заема повторяет вид синхроимпульса и нулевым уровнем запрещает прием синхросигнала по входу -И. По заднему фронту сигнала заема осуществляется прием сигнала контроля в триггер 12.

Формула изобретения

0

Устройство для возведения в квадрат по авт. св. If 1451686, отличающееся тем, что, с целью повышения достоверности функциони- 5 рования устройства, в него введены сумматор контроля, первый и второй триггеры, счетчик, элемент НЕ, первый и второй регистры контроля и мультиплексор, причем синхровход устройства подключен к сннхровходу счетчика, синхровходзм первого и второго регистров контроля и синхровходу первого триггера, вход сброса устройства подключен к входам сброса первого и второго регистров контроля, первого и второго триггера и входу установки счетчика, выходы суммы первого и второго сумматоров являются выходами результата и подключены к первому и второму входам первого слагаемого сумматора контроля, вход переноса которого соединен с выходом первого триггера, выход переноса соединен с информационным входом первого триггера, а первый и второй выходы суммы подключены к соответствующим информационным входам первого регистра контроля, первый и второй выходы которого соединены с соответствующими информационными входами второго регистра контроля, первый и второй выходы которого соединены с соответствующими входами второго слагаемого сумматора контроля, первый (младший), второй и третий адресные входы мультиплексора соединены с вторым выходом второго регистра контроля первым и вторым выходами первого регистра контроля соответственно, HV0

5

0

5

0

5

16 Г 31

/ a is ч ft

It гз J IS 55 67 It

1-x-у- x-v-у- -

I /N .1 A f

и г 35 is 57 st

I ft- f

75 IS 37 Ht

СЭСГХ

n t

ttt44 ltltt ltr tel« ttl t 1

СХООСОСХЭООСХЭСЗОСХХХf / 3 5 7 t

г ) /« ЭСЭСЭС1Х1Г СЭС

i г i j г- W

16 Г 31

/ a is ч ft

It гз J IS 55 67 It

1-x-у- x-v-у- -

I /N .1 A f

и г 35 is 57 st

I ft- f

75 IS 37 Ht

СЭСГХ

n t

г ) /« t -i w +i M-M4«-tv ЭСЭСЭС1Х1Г СЭСЭСЭСГХ

i г i j г- W t f

u-

Фшг

40

Составитель А.Дрозд Редактор О.Юрковецкая Техред М.Дидик Корректор И.Муска

Заказ 42

Тираж 553

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб. д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Q)Ut.4

Подписное

| Устройство для возведения в квадрат | 1987 |

|

SU1451686A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-07—Публикация

1988-04-21—Подача