Изобретение относится к цифровой вычислительной технике и предназначено для формирования сигналов кадровой развертки, строчной развертки и коммутации видеосигнала матричного ЖК-экрана,

Цэлыо изобретения является повышение надежности устройства.

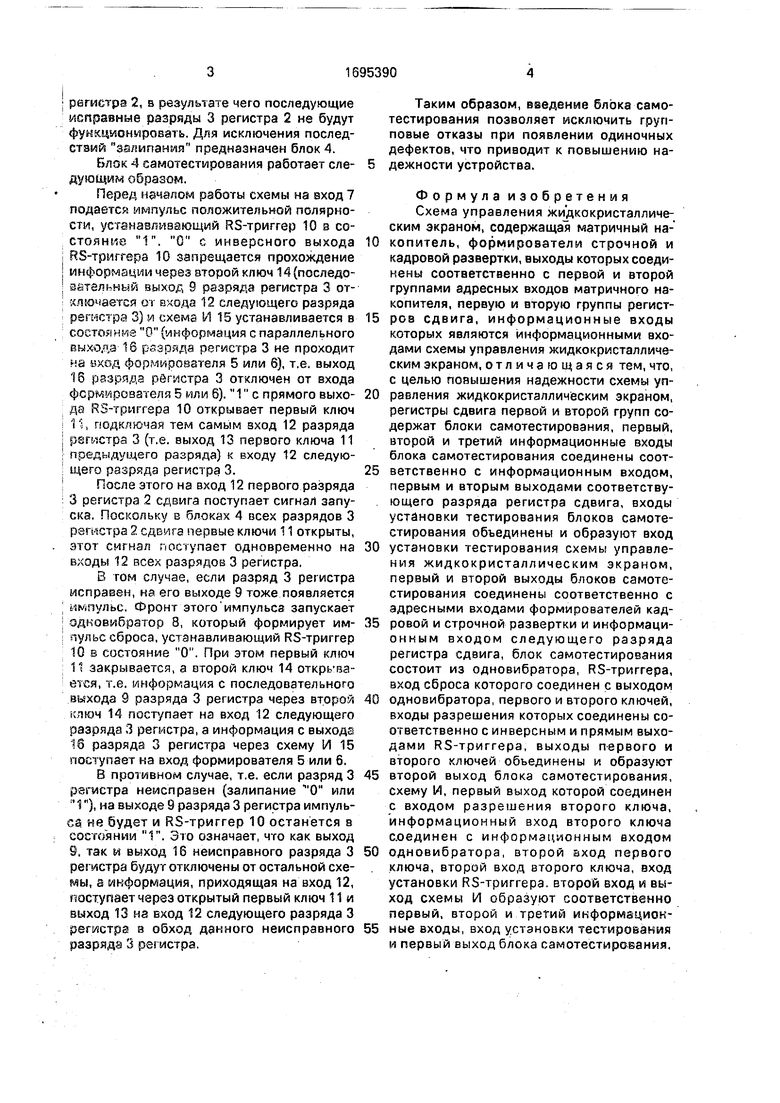

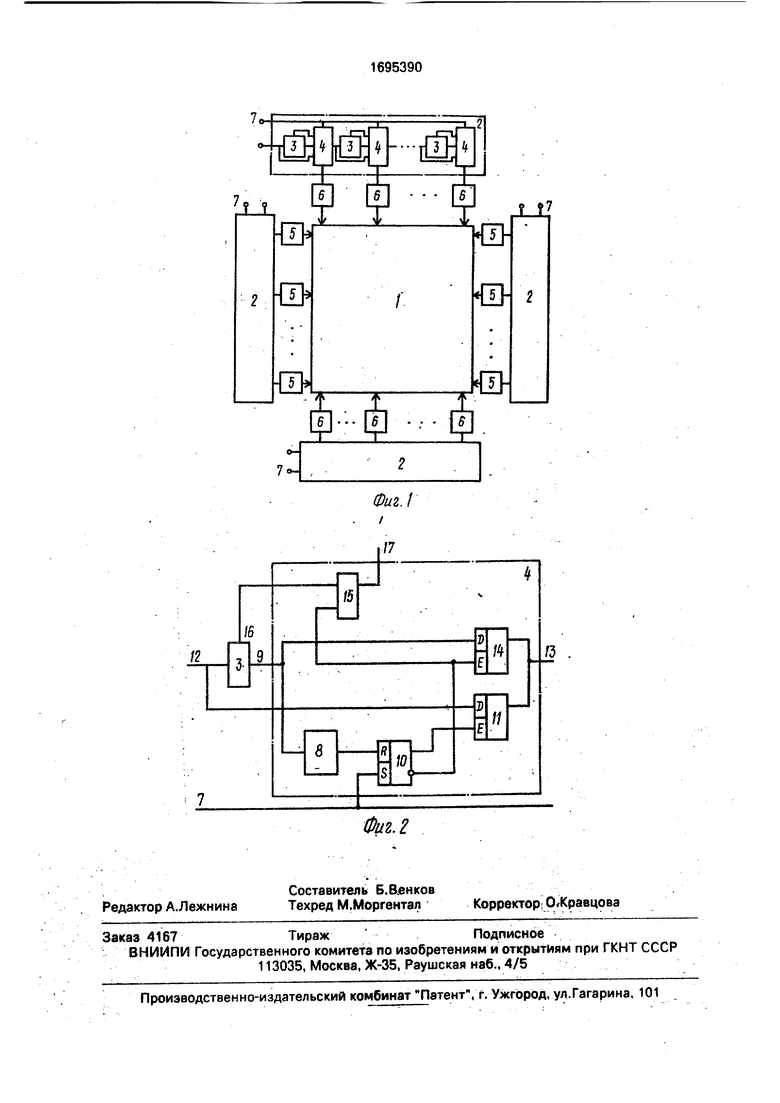

На фиг-.1 и 2 представлены соответственно схема управления экраном .и блок- схема одного разряда регистра сдвига с блоком самотестирования.

Схема управления ЖК-экра ном содержит матричный накопитель 1 в виде запоминающей транзисторной матрицы, регистры 2 сдвига первой и второй групп, состоящие из разрядов 3, блок 4 самотестирования, формирователи 5 кадровой развертки, формирователи 6 строчной развертки, вход 7 разрешения самотестирования, одновибра- тор 8, первый выход 9 разряда регистра 2, RS-триггер 10, первый ключ 11, информационный вход 12 разряда 3, первый выход 13 блока тестирования, второй ключ 14, схему

И 15, второй выход 16 разряда регистра 3, второй выход 17 блока тестирования.

При отсутствии дефектов в разрядах 3 регистра 2 сдвига в исходном состоянии Написаны О. Подачей на ьход 12 а первый разряд 3 регистра 2 записывается 1. При этом уровень 1 появляется на выходе 16 разряда 3 регистра 2, активизируя соответствующие формирователи 5 и 6.

При последующих тактах подачи 1 на вход 12 первого разряда регистра 3 1 будет поочередно появляться на одном из разрядов регистра сдвига. Сканирование вертикальных и горизонтальных регистров 2 сдвига происходит с разной частотой (полное сканирование горизонтального регистра сдвига завершается за один такт сканирования вертикального регистра 2 сдвига. Таким образом осуществляется последовательный перебор всех элементов матричного накопителя 1.

При отсутствии блоков 4 самотестирования возможно появление дефекта залипа- ния О или 1 в одном из разрядов

сл

о ю ел ы ю о

регистра 2, в результате чего последующие исправные разряды 3 регистра 2 не будут функционировать. Для исключения последствий залнпанмп предназначен блок 4.

Блок 4 самотестирования работает следующим образом.

Перед началом работы схемы на вход 7 подается импульс положительной полярности, устанавливающий RS-триггер 10 в состояние 1. О с инверсного выхода RS-триггера 10 запрещается прохождение информации через второй ключ 14 (последовательный выход 9 разряда регистра 3 отключается от входа 12 следующего разряда регистра 3) и схема И 15 устанавливается в состояние О (информация с параллельного выхода 16 разряда регистра 3 не проходит иа вход формирователя 5 или 6), т.е. выход 16 разряда регистра 3 отключен от входа формирователя 5 или 6). 1 с прямого выхода RS-триггера 10 открывает первый ключ 11, подключая тем самым вход 12 разряда регистра 3 (т.е. выход 13 первого ключа 11 предыдущего разряда) к входу 12 следующего разряда регистра 3.

После этого на вход 12 первого разряда 3 регистра 2 сдвига поступает сигнал запуска, Поскольку в блоках 4 всех разрядов 3 регистра 2 сдвига первые ключи 11 открыты, этот сигнал поступает одновременно на входы 12 всех разрядов 3 регистра.

В гом случае, если разряд 3 регистра исправен, на его выходе 9 тоже появляется ьшпульс, Фронт этого импульса запускает эдковибратор 8, который формирует импульс сброса, устанавливающий RS-триггер

10в состояние О. При этом первый ключ

11закрывается, а второй ключ 14 открывается, т.е. информация с последовательного выхода 9 разряда 3 регистра через второй ключ 14 поступает на вход 12 следующего разряда 3 регистра, а информация с выхода 16 разряда 3 регистра через схему И 15 поступает на вход формирователя 5 или 6.

В противном случае, т.е. если разряд 3 регистра неисправен (залипание О или 1), на выходе 9 разряда 3 регистра импульса не будет и RS-триггер 10 останется в состоянии 1. Зю означает, что как выход 9, так и выход 16 неисправного разряда 3 регистра будут отключены от остальной схемы, а информация, приходящая на вход 12, поступает через открытый первый ключ 11 и выход 13 на вход 12 следующего разряда 3 регистра в обход данного неисправного разряда 3 ре истра.

Таким образом, введение блока самотестирования позволяет исключить групповые отказы при появлении одиночных дефектов, что приводит к повышению на- дежности устройства.

Формула изобретения Схема управления жидкокристаллическим экраном, содержащая матричный накопитель, формирователи строчной и кадровой развертки, выходы которых соединены соответственно с первой и второй группами адресных входов матричного накопителя, первую и вторую группы регистров сдвига, информационные входы которых являются информационными входами схемы управления жидкокристаллическим экраном, отличающаяся тем, что, с целью повышения надежности схемы управнения жидкокристаллическим экраном, регистры сдвига первой и второй групп содержат блоки самотестирования, первый, второй и третий информационные входы блока самотестирования соединены соответственно с информационным входом, первым и вторым выходами соответствующего разряда регистра сдвига, входы установки тестирования блоков самотестирования объединены и образуют вход

установки тестирования схемы управления жидкокристаллическим экраном, первый и второй выходы блоков самотестирования соединены соответственно с адресными входами формирователей кадровой и строчной развертки и информаци- онным входом следующего разряда регистра сдвига, блок самотестирования состоит из одновибратора, RS-триггера, вход сброса которого соединен с выходом

одновибратора, первого и второго ключей, входы разрешения которых соединены соответственно с инверсным и прямым выходами RS-триггера, выходы первого и второго ключей объединены и образуют

второй выход блока самотестирования, схему И, первый выход которой соединен с входом разрешения второго ключа, информационный вход второго ключа соединен с информационным входом

одновибратора, второй вход первого ключа, второй вход второго ключа, вход установки RS-триггера. второй вход и выход схемы И образуют соответственно первый, второй и третий информациокные входы, вход установки тестирования и первый выход блока самотестирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ПРОЕКТОР | 2005 |

|

RU2292663C1 |

| ЦИФРОВОЙ МОНИТОР | 2006 |

|

RU2306677C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2006 |

|

RU2310287C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2298297C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2284672C1 |

| ЦИФРОВОЙ ПРОЕКТОР | 2005 |

|

RU2276469C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2304362C2 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1987 |

|

SU1460738A1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2351094C1 |

Изобретение относится к цифровой вычислительной технике и предназначено для формирования сигналов кадровой развертки, строчной развертки и коммутаиии видеосигнала матричного ЖК-экрана Целью изобретения является повышение надежности устройства. Цель достигается тем, что регистры сдвига первой и второй групп содержат блоки самотестирования с соответствующими связями с другими блоками 2 ил.

| SAE Tech, Pap, Ser | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| IEEE Trans, Electron Devices, 1986, ISfe 8, p.p.1218-1221. | |||

Авторы

Даты

1991-11-30—Публикация

1988-04-19—Подача