Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам-делителям с коэффициентом деления на 2,5 и 10, и можег быть применено в устройствах промышленной автоматики и вычислительной техники

Целью изобретения являете, ппчыше ние ремонтопригодности устройства путем включения в его структуру резервного триггера и средств автоматической реконфигу- рации работоспособной структуры

На чертеже приведена структурная схема предлагаемого с етчика-делитетр

Счетчик-делитель содержит основные 1-4 и резервный 5 разряды, первый г и второй 7 элементы И-НЕ трип еры 31-85 разрядов, элементы И/И НЕ 91-94 разрядов, элементы И 101 102, Ю.З и 104 разрядов, вторые 11 1 и 11 2 элемента И соответствующих разрядов, третьи злемен- ты И 12.1- 12 2 соответствующий разрядор, первые 13.1 -13 3 и вторые 14 1 и 14 2 one менты И-ИЛИ соответствуют разрчдоп, элементы И-НЕ 15 1 и 15 2 разрядов элементы ИЛИ-НЕ 16.1 и 16.2 разрядов эле- менты 2И-ИЛИ 171-174 разрядов

Первый синхровход 18 устреисгва сое динен с первым входом элемента И 101 и вторым входом первой структуры И элемс-н- та И-ИЛИ 14.1. Входы 19 и 20 установки о О устройства соединены соответственно с первым и вторым входами элемента И-НЬ 6 устройства. Вход 21 1 разрешение работ и первого разряда соединен с вводами эте- мента И/И-НЕ 9 1 Входы 21 7 21 4 разре- шения работы второго - четвертого разрядов устройства соединены с чторыми входами соответствующих им тл тентов И/И-ИЕ 9.2-9 4 Второй синхр- иод 22 у. тройства соединен с первым входог. второй структуры И элемента И-ИЛИ 14 , вторым входом первой структуры И эли-знтэ И- ИЛИ 14 2, первым входом второй структуры И элемента И-ИЛИ 13 3 и вторым элемента И 10 4 Входы 23 ч 24 ,, жоьч. в

9 устройсi ча соединены соответственно с и втором входами -згемента И-НЕ /

Выход элемента И- НС 6 устройства соединен с R1-входом триггера 8.1, инверс- нчч входом элемента ИЛИ-HL о 1, поррым пхидои элемента И 12.2, инверсным входом .1/1ем«ыа ИЛИ НЕ 16 2 и Rl-в/одом триггера 85 Выход элемента И НЕ 7 уст- роиства соединен с 31-входом rpurtepa 8.5, вюрым входом элемента И НБ 154, инвер- сним входом элемрща И 12 3 вторым входом элемента И 12.2 и инверсными входами ле.снтов И НЕ 15 1, Л 12 1 и SI-входом трип эрч 8 1

Прямой ЕЫХОД элемента И/И-НЕ 9.1 со- одинен с вторым входом элемента И 10.1, торим входом первой структуры И элемен- ia 2И ИЛИ 171, первым входом элемента И

121 и Р2рвым входом элемента И/И-НЕ 9 2 Инверсный выход элемента И/И- НЕ 9.1 соединяй (, первым входом второй структуры И лемйнта 2И ИЛИ 17.1. первым ахо- дом элемента И-НЕ 151, входом первой структуры И элемента И-ИЛИ 13 1 и первым входом первой структуры И элемента И- ИЛИ 14 1. Выход элемента И 10 1 соединен со счетным входом триггера 8.1, прямой выход которою соединен с перьым входом первой структуры И элемента 2И-ИЛИ 17.1.

Прямой выход элемента И/И-НЕ 9.2 соединен с вторым входом первой структуры И элемента 2И-ИЛИ 17.2, первым входом элемента И/И-НЕ 9 3 и вторыми входами ьторых структур И элементов И-И/1И 13.1 и 111. Инверсный выход элемента И/И-НЕ 9 2 соединен с первым входом второй структуры /I эллмен-а 2И- ИЛИ 17,2 первым входом первой структ , И элемента И-ИЛИ

13/ и первым глуод: -1, первой структуры И элемента И-ИЛИ 14,2. Выход олементо И 12.1 (.оедиж и с в орым входом элемента ИПИ-НЕ 16.1. выход которого , оедиьен с Rl-входог, триггера 8.2. Выход зяемечтз И- НЬ 5.1 соединен с S1-входом ip rrepa в 2.

Выход элемента И-ИЛИ 13.1 соединен с 1-входом триггера 8.2, счетный вход которого соединен с выходом элемента И-ИЛИ

14.1.Прямой выход триггера 8.2 соединен с вторым входом второй структуры И элемента 2И-ИЛИ 17.1 и первым входом первой структуры И элемента 2И-ИЛИ 17.2.

Прямой выход элемента И-И-НЕ 9.3 соединен с вторым входом первой структуры И элемента 2И-ИЛИ 17.2, первым входом элемента И/И-НЕ 9.4, входом второй структуры И элемента И-ИЛИ 13.2, вторым входом второй структуры И элемента И-ИЛИ 14.2 и первым входом элемента И-НЕ 15.2 и вторым входом элемента И 10.3. Инверсный выход элемента И/И-НЕ 9.3 соединен с первым входом второй структуры элемента 2И-ИЛИ 17.3, первым входом элемента И 12.3 и первым входом первой структуры И элемента И-ИЛИ 13.4. Выход элемента И-ИЛИ 13.2 соединен с 1-входом триггера 8.3. счетный вход которого соединен с выходом элемента И-ИЛИ 14.2. Выход элемента И 12.2 соединен с Rl-входом триггера 8.3, прямой выход которого соединен с вторым входом второй структуры И элемента 2И- ИЛИ 17.2 и первым входом первой структуры И элемента 2И-ИЛИ 17.3.

Прямой выход элемента И/И-НЕ 9.4 соединен с вторым входом первой структуры И элемента 2И-ИЛИ 17.4, вторым входом второй структуры И элемента И-ИЛИ 13.3 и третьим входом элемента И 11.1. Инверсный выход элемента И/И-НЕ 9.4 соединен с первым входом второй структуры И эле- мента2И-ИЛИ 17.4 и первыми входами элементов И 10.4 и 11.2. Выход элемента И 10.3 соединен с Я2-входом триггера 8.4, счетный вход которого соединен с выходом элемента И-ИЛИ 13.3. Выход элемента И 11,1 соединен с 52-входом триггера 8.4, R1- и 51-входы которого соединены соответственно с выходами элементов ИЛИ-НЕ 16.1 и И-НЕ 15.2. Выход элемента И 12.3 соединен с вторым входом элемента ИЛИ-НЕ

16.2.Прямой выход триггера 8.4 соединен с первым входом первой структуры И элемента 2И-ИЛИ 17.4, вторым входом второй структуры И элемента 2И-ИЛИ 17.3 и первым входом элемента И 10.3.

Выход элемента И 10.4 соединен со счетным входом триггера 8.5, 52-вход которого соединен с выходом элемента И 11.5. Прямой выход триггера 8.5 соединен с вторым входом второй структуры И элемента 2И-ИЛИ 17.4 и Я2-входом триггера 8.5.

Выход элемента 2И-ИЛИ 17.1 является первым информационным выходом 25.1 устройства. Выход элемента 2И-ИЛИ 17.2 является вторым информационным выходом

25.2 устройства и соединен с вторым входом элемента И 11.2, первым входом элемента И 11.1, вторым входом первой структуры И элемента И-ИЛИ 13.3 и первым входом второй структуры И элемента И-ИЛИ 14.2. Выход элемента 2И-ИЛИ 17.3 является третьим информационным выходом 25.3 устройства и соединен с вторым входом элемента И 11.1 и третьим входом элемента И

0 11.2. Прямой выход элемента 2И-ИЛИ 17.4 является четвертым информационным выходом 25.4 устройства. Инверсный выход элемента 2И-ИЛИ 17.4 соединен с первым входом второй структуры И элемента И5 ИЛИ 13.1 и вторым входом первой структуры И элемента И-ИЛИ 13.2

Разряды 1-4 являются основными разрядами счетчика-делителя, реализующими его основное функциональное назначение в

0 устройствах автоматики, телемеханики и вычислительной техники.

Разряд 5 является резервным разрядом счетчика-делителя находящимся в горячем резерве, и предназначен для восста5 новлени.я работоспособности устройства при отказе одного из основных разрядов 1-4.

Элементы И-НЕ 6 и 7 обеспечивают надежность срабатывания устройства при его

0 установке в О и 9 путем выработки соответствующего сигнала при наличии двух одноименных управляющих сигналов и согласования уровня входных сигналов с уровнем логической единицы и логического

5 нуля внутри устройства.

Триггеры 8.1-8.5 являются основными элементами памяти в счетчике-делителе, реализующими функцию накопления информации в соответствии с заданным входной

0 логикой устройства алгоритмов функционирования.

Элементы И/И-НЕ 9.1-9.4 осуществляют выработку сигналов настроечной функции, управляющей работоспособной

5 структурой счетчика-делителя, в зависимости от исправного (неисправного) состояния его разрядов 1-4.

Элемент И 10.1 осуществляет коммутацию тактового импульса с синхровхода

0 18 устройства на счетный вход триггера 8.1 в случае его исправного состояния. При неисправном состоянии разряда 1 элемент И .10.1 закрыт нулевым потенциалом с прямого выхода элемента И/И-НЕ 9.1

5 Элемент И 10.3 пропускает на свой выход сигнал установки в О триггера 8.4 в случае исправного состояния разрядов 1-3 устройства.

Элемент И 10.4 пропускает на свой выход сигнал тактового импульса с синхровхода 22 в случае отказа одного из разрядов 1-4, включая тем самым в работоспособную структуру устройства триггер 8.5.

Элемент И 11.1 пропускает на свой выход сигнал установки в 1 триггера 8.4 в случав исправного состояния разрядор 1--4 устройства.

Элемент И 11.2 пропускает на свой выход сигнал установки в 1 триггера 8.5 в счетном режиме при отказе четвертого раз- ряда устройства

Элемент И 12,1 пропускает на свой вы ход сигнал установки в О трип ера 8.2 при установке устройства в 9 в случае испрлв ного состояния разряда 1 устройства.

Элемент И 12.2 пропускает на свой выход сигнал установки в О триггер R 3 при установке устройства в 9 в случае неисправного состояния триггера 8 1.

Элемент И 12.3 пропускает на свой оы- ход сигнал установки в О триггера 8.4 в случае неисправного состояния одного из разрядов 1-3 при установке устройствп в состояние 9.

Элементы И-ИЛИ 13.1-13.3 разрядов обеспечивают коммутацию сигналов на входы тршгеров 8.2 и 8.3 и на счетный вхсд триггера 8.4 при соответствующей работоспособной структуре устройства,

Элементы И-ИЛЙ И.1 и 14,2 разрядов обеспечивают коммутацию синхросигналов на счетные входы триггеров 8.2 и 8.3 к соответствии с существующей работоспособной структурой устройства.

Элемент И-НЕ 15.1 пропускает на свои выход сигнал установки в I триггера 8.2 в режиме установки устройства в 9 в случае отказа разряда 1.

Элемент И-НЕ 15.2 пропускает иа св. и выход сигнал установки в 1 трип ера 8,4 о режиме установки устройства в состояние 9 в случае исправного состояния разрядов 1-4 устройства.

Элементы ИЛИ-НЕ 16.1 и 1GJ пропускают на свои выходы сигналы установки о Т) соответствующих триггеров 8.2 и 8,4 либо в режиме установки в О устройства либо в режиме сто установки в сосюяние 9.

Элементы 2И-ИЛИ 17.1-17.4 разрядов осуществляют коммутацию сигналов i прямых выходов триггеров 8.1-8.5 на выходы 25.1-25.4 устройства в зависимости or исправного (неисправного) состояктя ссотьот- С1вующего разряда 1-4, или хотя он оц-юго из разрядов 1-4.

Входы 18 и 22 устройства являются соответственно первым и вторым сикхропхо дами устройства.

Входы 19 и 20 являются входами установки о О устройства.

Входы 1.1-21.4 являются управляющими входами разрешения работы соответствующих разрядов устройства. В случае отказа какого-либо из разрядов на соответствующий вход 21 подается сигнал логического нуля.

Входы 23 и 24 являются входами установки в 9 усфойства.

Выходы 25.1-25.4 являются соответствующими первым - четвертым информационными выходами устройства.

Счетчик-делитель работает следующим образом.

Для устлновки счетчика-делителя в ну- повое состояние на входы 19и20одновремен- но подаются CHI налы логический единицы. В этом случае на выходе элемента И-НЕ 6 формируемся сигнал логического нуля, который по входам R1 триггеров 8 1-8.5устанавливает и/. D путовое состояние.

Угпновка счетчи: л-дслителя в состоя- -14с; 9 производится следующим образом. 8 случае исправного-состояния разрядов 1- 4 при одновременном появлении единич- HLU ло ических уровней сигналов на входах 23 и 24 Dединичное состояние устанавлива- IOICH триг рры 8.1, 8.4 и 8.5, а триггеры 8,2 и 8.3 остаются в нулевом состоянии. Это происходит потому, что нулевой логический уровень сигнала, сформированный на выходе элемент,- И НЕ 7, поступает на 31-вход триггера 8 5, на инверсный вход элемента 14 HE 15.2 и дчлее на вход S1 триггера 8.4, HP вход элемента И 12.2 и далее - на Р1-вход триггера 83, на инверсный вход элемента И-НЕ VJ..1 и И 12 1 и на R1-вход триггера 8.2, и ни 81-о,од триггера 8.1. В случае неисправности одного из разрядов происходит перестройка работоспособности структуры счетчикз-дсгцпеля и установка в состояние 9 происходит другим путем. Рассмотрим пример, когда произошел отказ 1 разряда. В этом случае на вход 21.1 подается сигнал нулевого лоа:ческого уровня, который приводит к изменению сигналов на прямых и инвеосипх выходах элементов И/И-НЕ 9.1- 0.4 H.I их прямых выходах будет сформирован сигнал пулевого логического уровня, а на инверсных - высокого логического уровня, i IpV i установка в состояние 9 произойдет следующим образом. Триггеры 8.2 и 8.5 установятся г. состояние логической единицы HU их выходах, а труигеры 8.3 и Ь.4 ь нулииоо логическое состояние, так как нулевой логический уровень сигнала с аиходп эчеменга И-НЕ 7 поступит на S1- вход триггера 8.5. через элемент И 12.3 и ИЛИ-НЕ 16 2 - на R1-вход триггера 8.4. ерез элемент И 12.2 - на Rl-вход триггера 8.3 и через элемент И-НЕ 15.1 - на 51-вход триггера 8 2

Предлагаемый счетчик-делитель может работать в трех режимах: в ре,симе двоично- десятичного счетчика; как счетчик-делитель выходного импульса на 10 со скважностью 2, и как счетчик-делитель на 2 и 5.

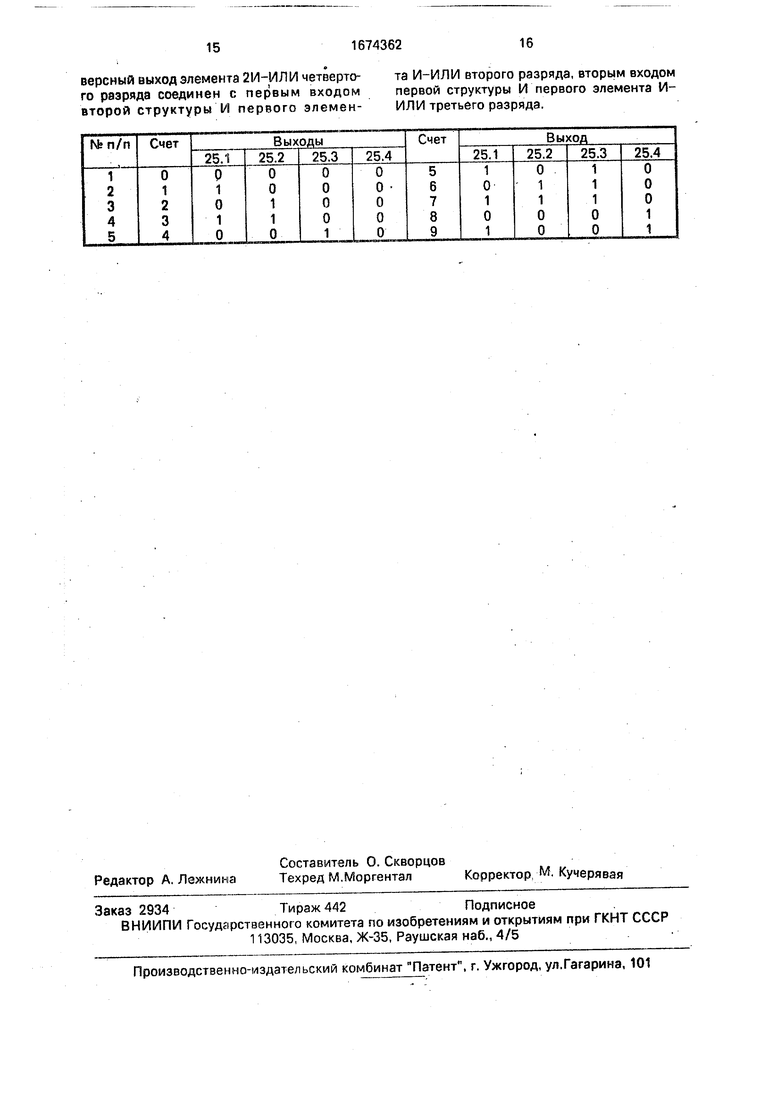

При использовании предлагаемого счетчика-делителя в качестве двоично-десятичного счетчика вход 22 (С2) внешне соединяется с выходом 25.1. На входах 21.1-21.4 при исправном состоянии основных разрядов 1-4 должен присутствовать сигнал логической единицы, а на входах 19, 20 и 23, 24 - сигналы логического нуля. На вход 1Ь (о1) поступают счетные импульсы и счетная последовательность реализуется в соответствии с таблицей истинности.

Логическая ветвь подсчета поступающих импульсов в случае исправного состояния разрядов 1-4 б/дет следующей: с входа 18 устройства через элемент И 10 1 - на счетный вход триггера 8.1, состояние сигнала на прямом выходе триггера 8.1 (и его изменения) через первую структуру И элемента 2 И-И Л И 17.1 поступает на выход 25 1 устройства и через соединение 25.11 22 и вторую группу входов элемента И-ИЛИ 14 1- на счетный вход триггера 3 2; состоянии сигнала (и его изменения) на выходе триггера 8.2 через первую структуру И элемента 2И- ИЛИ 17.2 поступает на выход 25.2 устройства и через вторую структуру И эпемента И-ИЛИ 14.2 на счетный вход триггера 8 3; состояние сигнала (и его изменения) на выходе триггера 8.3 через первую структуру И элемента 2И-ИЛИ 17.3 поступает на выход 25.3 устройства и, через вторую структуру И элемента И-ИЛИ 13.3 на счетный вход триггера 8.4.

В случае отказа какого-либо из основных разрядов 1-4 в предлагаемом счепике- делителе происходит реконфигурация работоспособной структуры. Рассмотрим пример подсчета импульсов при отказе первого разряда. В этом случае на вхсд 21.1 подается сигнал нулевого логического уровня, что приводит к смене состояний сигналов на прямых и инверсных выходах элементов И/И-НЕ 9.1 9.4. В результате этого подсчет импульсов в предлагаемом счетчике-делителе производится по следующей логической ветви, с входа 18 устройства через первую структуру И элемента И-ИЛИ 14.2 - на счетный вход триггера 3.2. Состояние сигнала (и его изменения) с выхода триггера 8.2 через вторую структуру И элемента 2И- ИЛИ 17.1 поступает на выход 25.1 устройства и через соединение 25.1 и22,

перьую стрУ1. гуру И элемент I ИЛИ 14 2 на счетный ьход триггера В 3, состояние сиг нала ..а прямом трип ера 8 3 (и е.о изменения) черег вторуи структуру И элемента 2И-ИЛИ 17 2 лоступгсг на внход25,2 устройство и через «юру,,: структуру И элемента И-ИЛИ 13.3 на счет т)й вход триггера 8 Л состояние сигнилэ н; прямом гыход з три( i s 8 4 (и eru изме сни-0 через йгопуй

0 сгруг гуру И элемента 2И /bV 17.3 пис упч- ет на зь ход 25.3 угтройегРс и через элемент И Ю л на С .слнь й вход трип --ра 8 5: LOCTO яние сигнала на прямом выходе триггера 3.5 (и ото и .менения) вторую cii.KTvpy И

5 зломчнтз -ИЛИ 1 / 4 пепуп г„: чэ вихо/, 25.4 устройства

При использо чнчи it.ч дяaracvого счег ЦкГ-,.г,й/ |И.тела ч режиме .„ ,t- v. вь.хсд нею 1 мпучь я и i j со гкг ..-KI 2 оьг- -д

0 1)( yciponcrBd вм-:и еоед.-нчетоя с нхо- дом 18, а входные ип:г, п.1 -,; () г.оцаю-ч-я на охсд22 устройство. I p Ovovuri сигнал снимается с г-ьхпдз Ь 1 ycTpc icn i П глучгО иснравис о ncroiiiii

5 разочдов 1 -1 ncrns , кая п-м ь , одсчета мм путьсоп буг,ет с едуюь й с пхода 22 уст- рог- стаа 4tpnj второю стр туру И алеме тг, И ИЛИ 14 1 - насчетны BXCV, ipnrreps82. cnihd,- с at хода innr;epa 8 2 черол nrf пую

0 структур, И jneMOt-To 211 ИЛИ 17.2, вторую структуру И элемента И ИПИ1Л2- ia счетный пход триггер 3, сигнал с выходн триггера 8 3 через первую структуру И элемента 2И И ПИ 17 3, вторую струк уру И элемента

5 И-ИЛИ 133 - ьй счетным вход трипера 8 4; сигнял с триггера 8 i первую CTpyi-Typy И элемента 2И ИЛИ 17.4 на выход 25 4 и через сосдин :мие 5 4 и 18, элемент , 10. i - на счетный пход триггера 8.1;

0 си нал /% выхода триггера 8 1 (врез первую структуру И элемента 2 4-ИЛИ 17.1 - на выход 25 1 устройс в :

Ртссмотрим логическую ость подсчета импульсов в этом режиме работы предлэга5 емого счетчика-делителя при отклзе второго разряда. В этом случае на вход 21.2 подается сигнал нулевого логическою уровня, который приводит ксмеме состояний сигналов на прямых и инверсных выходах элементов

0 И/И-НЕ 9 2-9 4. Следовательно, логическая ветзь подсчета имп/льсов будет следу- ЮЩРЙ, с входа 22 устройслвз через первую структуру И элемента И-ИЛИ 14 2 - на счет- нь й вход триггера 8.3; сигнал с выхода триг5 iepa 3 3 через вторую группу входоп элзмснта 2И-ИЛИ ГЛ2 постугпет на виход 2Ь.2 устройства и через перзую структур1, И элемента И-ИЛИ 13 3 на счетный триггера 8.4; сигнал с выхода триггера 8.4 (ерез вторую структуру И элемента 2И-ИЛИ 17.3

поступает на выход 25.3 устройства и через элемент И 10.4 на счетный вход триггера 8.5; сигнал с выхода триггера 8.5 через вторую структуру И элемента 2И-ИЛИ 17.4 поступает на выход 25.4 устройства и через соединение 25.4U18, элемент И 10.1 на счетный вход триггера 8.2; сигнал с выхода триггера 8.1 через первую структуру И элемента 2И- ИЛИ 17.1 поступает на выход 25.1 устройства.

Таким образом, в случае отказа разряда 2 логическая ветвь подсчета импульсов в предлагаемом счетчике-делителе вытесняет из работоспособной структуры неисправный разряд и производит замещение второго разряда третьим, третьего разряда - четвертым и четвертого разряда - резервным, сохраняя при этом свою работоспособность.

При использовании предлагаемого счетчика-делителя в режиме деления на 2 и 5 внешних соединений не требуется. Триггер 8.1 при исправном состоянии разрядов 1-4 используется как двоичный элемент деления на 2, а вход 22(С2) с выходом 25.4 - для деления на 5. Оба счетчика функционируют независимо друг от друга. При отказе третьего разряда логическая ветвь подсчета импульсов будет следующей: с входа 22 через вторую структуру И элемента t/l-VUll/l 14.1 -на счетный вход триггера 8.2; с выхода триггера 8.2 через первую структуру И элемента 2И-ИЛИ 17.2, первую структуру И элемента И-ИЛИ 13.3 - на счетный вход триггера 8.4; с выхода триггера 8.4 через вторую структуру И элемента 2И-ИЛИ 17.3, элемент И 10.4 - на счетный вход триггера 8.5; с выхода триггера 8.5 через вторую структуру И элемента 2И-ИЛИ 17.4 - на выход 25.4 устройства.

Замена отказавшего четвертого разряда производится путем его вытеснения из работоспособной структуры резервным разрядом аналогичным способом.

Таким образом, в предлагаемом счетчике-делителе осуществляется замена отказавшего разряда резервным независимо от места отказа, что предотвращает необходимость перекоммутации входов и выходов устройства.

Формула изобретения Счетчик-делитель, содержащий триггеры разрядов и два элемента И-НЕ, первый и второй входы установки в О устройства соединены соответственно с первым и вторым входами первого элемента И-НЕ устройства, первый и второй входы установки в 9 устройства соединены соответственно с первым и вторым входами второго элемен

та И-НЕ устройства, отличающийся тем, что, с целью повышения ремонтопригодности, он дополнительно содержит резервный разряд с триггером и двумя

элементами И, а первый разряд дополнительно содержит элемент И/И-НЕ, элемент И и элемент 2И-ИЛИ, второй разряд допол- . нительно содержит элемент И/И-НЕ, два элемента И-ИЛИ, элемент И, элемент И0 НЕ, элемент ИЛИ-НЕ и элемент 2И-ИЛИ, третий разряд дополнительно содержит элемент И/И-НЕ, два элемента И-ИЛИ, элемент И и элемент 2И-ИЛИ, четвертый разряд дополнительно содержит элемент

5 И/И-НЕ, три элемента И, элемент И-ИЛИ, элемент И-НЕ, элемент ИЛИ-НЕ и элемент 2И-ИЛИ, причем первый синхровход устройства соединен с входом элемента И первого разряда и вторым входом первой

0 структуры И второго элемента И-ИЛИ второго разряда, второй синхровход устройства соединен с первым входом второй структуры И второго элемента И-ИЛИ второго разряда, вторым входом первой структуры И вто5 рого элемента И-ИЛИ третьего разряда, первым входом второй структуры И элемента И-ИЛИ четвертого разряда и вторым входом первого элемента И резервного разряда, вход разрешения работы первого разряда

0 устройства соединен с первым и вторым входами элемента И/И-НЕ одноименного разряда, прямой выход которого соединен с вторым входом элемента И, вторым входом, первой структуры И элемента 2И-ИЛИ пер5 вого разряда, первым входом элемента И/И-НЕ и первым входом элемента И второго разряда, инверсный выход элемента И/И-НЕ первого разряда соединен с первым входом второй структуры И элемента

0 2И-ИЛИ одноименного разряда, прямым входом элемента И-НЕ, входом первой структуры И первого и первым входом первой структуры И второго элементов И-ИЛИ второго разряда, выход элемента И первого

5 разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с первым входом первой структуры И элемента 2И-ИЛИ первого разряда, выход первого элемента И-НЕ устрой0 ства соединен с Rl-входом триггера первого разряда, первым входом элемента И третьего, с инверсными входами элементов ИЛИ-НЕ второго и четвертого и Rl-входом триггера резервного разрядов, выход второ5 го элемента И-НЕ устройства соединен с S1-входом триггеров первого и резервного разрядов, инверсными входами элементов И и И-НЕ второго разряда, вторым входом элемента И третьего разряда и инверсными входами третьего элемента И-НЕ четвертого разряда, сход разрешения работы вгооо- го разояда соединен с вторым входом мента И/И-НЕ одноименного разряда, прямой вылод которого соединен с вторым входом первой структуры И элемента 2И ИЛИ, вторым входами вторых структур И периого и второго элементов И-ИЛИ второго разряда и первым входом элемента И/И НЕ- третьего разряда, инверсный выход эпемен та И/И-НЕ второго разряда соединен с пер BUM входом второй структура И элемент-) 2И- ИЛИ одноименного и первыми вход.- „ первых структур И первого и рторого зле ментов И-ИЛИ третьем разряда, выход первого элемента И ИЛИ ьторо 0 соединен с 1-входом триггера од оимеы огс , счетный вход которого соединен с выходом второго элемента И-ИЛИ вторе о разряда, выход элемент/ И второго рззряг: соединен с вторым рхо,;ом элемента ИЛИ- НЕ одноименного разряда выход которого соединен с R1 ходом триггера втзрого paj ряда, 51-вход KOTopCi о соединен г РЬ /слом элемента И-HF одной немного разрчдч прямой выходтриггера второго разряду соединен с вторым второй с руктуры И элемента 2И ИЛИ геивогэ и первым входом первой структуры И элемента 2И ИЛИ второго разрядов вход разреши пч работы третьего разряда соединен с вторым входом элемента И/И-НЕ одноименного разряда прямой выход которого соединен с вторым входом первой сгрук туры И элемента 2И-ИЛИ третьего раз- ряда, входом второй структуры И первого и вторым входом второй структуры И второго элементов И-ИЛИ третьего разря да, вторым входом первого элемента И и первым входом элемента И, И-Ht четвертого разряда, а также с первым входом элемента И-НЕ четвертого разряда, инверсный выход элемента И /И НЕ тоът.,е го разряда соединен с первым вводом В10рой структуры И элемента 2И-ИЛИ одноименного разряда, первым входом первой структуры И элемента И-ИЛИ и первым входом третьего элемента И четвертого разряда, выход первого элемента И-ИЛИ третьего разряда соединен с 1-вхо- дом триггера одноименного разряда, счетный вход которого соединен L выходом второго элемента И-ИЛИ третьего разряда, прямой выход триггера третьего разряда соединен с вторым входом второй стр-уктуры И элемента 2И-ИЛИ второго разряда и первым входом первой структуры И элемента 2И-ИЛИ третьего разряда, выход элемента И третьего разряда соединен с Pi-входом триггера одноименного разрядл, выход первого элемент И чет-

верюго оэзрьдч иен с R -входом три, гера одноименного разряда, чётной второго соединс-i1 с вькодом элемента И- И т,1 одноименного ра°ряцз. выход нторого

Э1 емочтс) И четиг ттого pa фядз соединен с 52-Рходом триггера односменною разпр а, Р1 в/од которого сселим.1. ьых дом чле Mtins ИЛИ-НЕ, вы/,д тоатьею эг эмент И чстварто;о разряда ч о динон г торым

0 в-одом элемента ИЛИ-hE од - оимечного f пзочдт, П ЛАОД э И- НЕ че ргргого раз; я а г.о,;инен с S1-nкодом Tj.nrrepa од- но1 эн ioro iiDiMO,i рыхгя тр;..- fp stM ерточ) рччр-д, (.н

5 ВТСИ.Ыг-, ЗХОДОМ iJ OfПрУНгУГ- М И C./IPM°i r,i И-И 1И T.jj.bC O, Tie,. .1

юй И ,1 2И-1 1П.1 и ;.ерч t-/ мерь ri, , , н, а И с IHD nvir разряда, зхом итзре( «ния pihu0 гы чотвеотого pajpstfl-: с ;.)горым t, дом зпрмент- И/И-riL о; onfei iioiu раЗ),Рй;, Г1ямой косоного соединен с вторым ВУОЛОМ перргг структуры Л зг е- мз тч И 1ЛИ, rnopt.-i, xo/.v- .срсй

Ь J. iypw И jnp га и -оетьип второго элемента И четверюго разря/-1, лнзергчыи выход эпемон а И/И- НЕ ei i рр си и госдинен г первым р- /,J,IIM ti орой ;трукгур,,1 И тт ментч И0 МПИ одной, lehf.oro p-jspq/ i, м BSO дом первого и первым входом гториго И резе, н юго ,,а, выход nepRO. о о/.еме а 1-1 разервнс О аяряда со- сдиьон со c.4eTt-biN входог триггер одни

J иенного разряда S2 в-од которою co° AiintH r, выходом второго элемента И р -рвного разряда, промой вы о/ ригге ра резервного разряда соединен с вто- ЬАОДОМ второи стоуктуры И элемента

0 И-И,ГЧ 1 четвертого разряда и го своим R2 и олсм, выход элемента 2И-ИЛИ первого разряда является первым информа- циопным выходом устройстве выход элемента 2И-ИЛИ второго разряда ЯВЛР5 ется вторым информационным выходом ycifойствэ и соединен с первым входом второй структуры И второго элемента И- ИЛИ третьего разряда, вторым входом перьой структуры И элемента И-ИЛИ, пер

0 вым входом второ.о элемента И четвертого с .зряда и вторым входом зторого эпемечта И резервного разряда, выход элемента 2И-ИЛИ .ретьего разряда ется третьим информационным выходом ус5 тройства и соединен с вторым входгг второго элемента И четвертого разряда и третьим входом второю элемента И peat рь- ною разряда, выход элемента 2И-ИЛИ т- вертого разряда является четвертым информационным выходом чтройств.., инверсный выход элемента 2И-ИЛИ четвертого разряда соединен с первым входом второй структуры И первого элемента И-ИЛИ второго разряда, вторым входом первой структуры И первого элемента И- ИЛИ третьего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1985 |

|

SU1272503A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Двоичный счетчик | 1983 |

|

SU1149402A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

Изобретение относится к импульсной и вычислительной технике и может быть использовано в устройствах автоматики, телемеханики, измерительной и вычислительной техники, в узлах и блоках деления частоты на 2, 5 и 10 с повышенной ремонтопригодностью на этапе эксплуатации этих устройств. Устройство отличается тем, что, с целью повышения ремонтопригодности, оно, кроме триггеров 8.1 - 8.4 разрядов и двух элементов И-НЕ 6 и 7, дополнительно содержит резервный разряд с триггером 8.5 и двумя элементами И 10.4 и 11.2, первый разряд дополнительно содержит элемент И/И-НЕ 9.1, элемент И 10.1 и элемент 2И-ИЛИ 17.1, второй разряд дополнительно содержит элемент И-И-НЕ 9.2, два элемента И-ИЛИ 13.1 и 14.1, элемент И 10.2, элемент И-НЕ 15.1, элемент ИЛИ-НЕ 17.1 и элемент 2И-ИЛИ 17.2, третий разряд дополнительно содержит элемент И/И-НЕ 9.3, два элемента И-ИЛИ 13.2 и 14.2, элемент И 12.2 и элемент 2И-ИЛИ 17.3, четвертый разряд дополнительно содержит элемент И/И-НЕ 9.4, три элемента И 10.3, 11.1 и 12.2, элемент И-ИЛИ 13.3, элемент И-НЕ 15.2, элемент ИЛИ-НЕ 16.2 и элемент 2И-ИЛИ 17.4 с соответствующими конструктивными связями. Такое техническое решение позволяет восстановить работоспособность устройства при отказе одного из основных разрядов 1 - 4 путем подачи управляющего нулевого потенциала на соответствующий управляющий вход 21.1 - 21.4. 1 ил., 1 табл.

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник | |||

| Применение интегральных микросхем в электронной вычислительной технике | |||

| / Под ред | |||

| Б | |||

| Н | |||

| Файзулаева, Б | |||

| В | |||

| Тарабрина, М.: Радио и связь, 1987, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-30—Публикация

1989-09-05—Подача