(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1982 |

|

SU1109890A1 |

| Цифровой нерекурсивный фильтр | 1990 |

|

SU1786638A1 |

| Нерекурсивный цифровой фильтрдециматор | 1984 |

|

SU1195420A2 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1171994A1 |

| Нерекурсивный цифровой фильтр нижних частот | 1986 |

|

SU1418750A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Рекурсивный цифровой фильтр | 1985 |

|

SU1264307A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

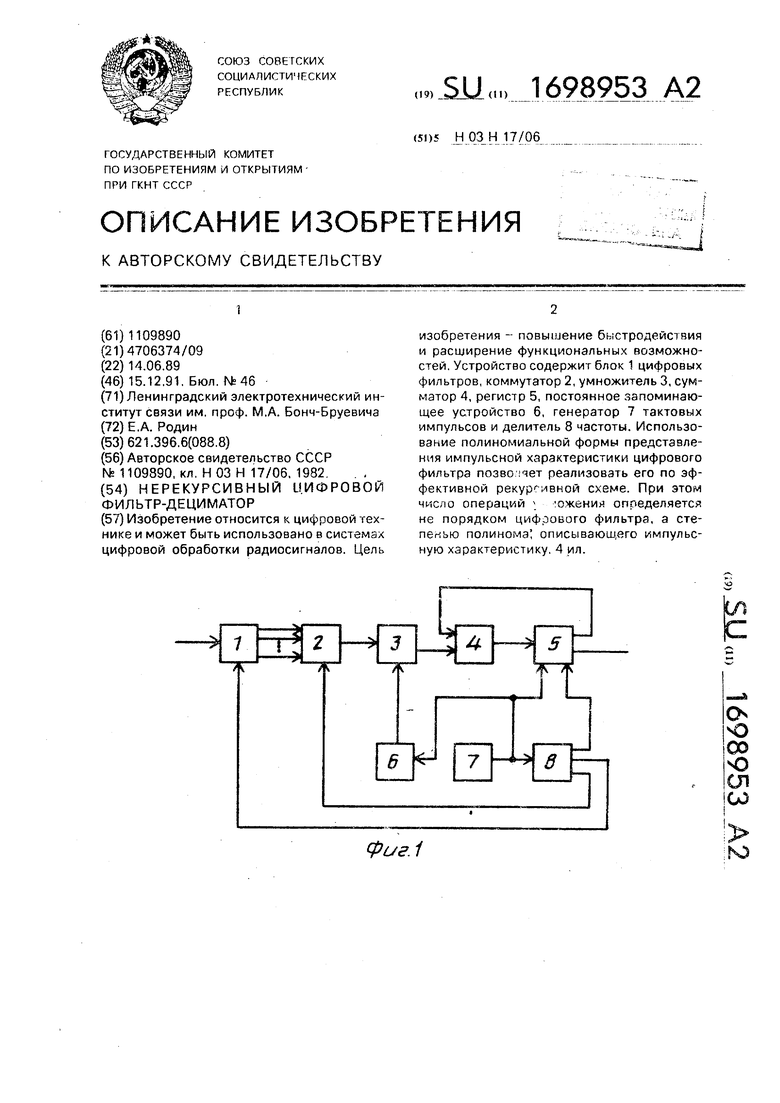

Изобретение относится к цифровой технике и может быть использовано в системах цифровой обработки радиосигналов. Цель изобретения - повышение быстродействия и расширение функциональных возможностей. Устройство содержит блок 1 цифровых фильтров, коммутатор 2, умножитель 3, сумматор 4, регистр 5, постоянное запоминающее устройство 6, генератор 7 тактовых импульсов и делитель 8 частоты. Использование полиномиальной формы представления импульсной характеристики цифрового фильтра позво яет реализовать его по эффективной рекурсивной схеме. При этом число операций ожения определяется не порядком цифрового фильтра, а степенью полинома описывающего импульсную характеристику. 4 ил.

О

о

00

о ся со

фиг.1

ю

Изобретение относится к цифровой технике, может быть использовано в системах цифровой обработки радиосигналов и является усовершенствованием изобретения по авт. св. Мг 1109890.

Цель изобретения - повышение быстродействия и расширение функциональных возможностей путем многовариантной обработки сигнала.

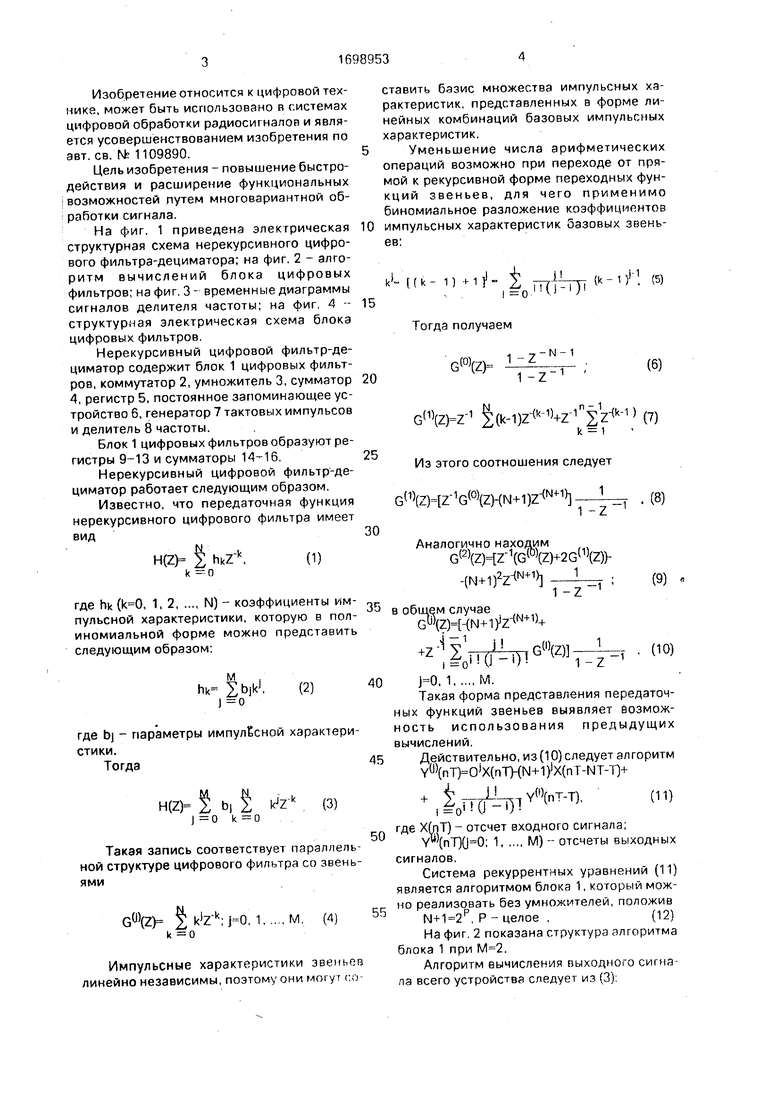

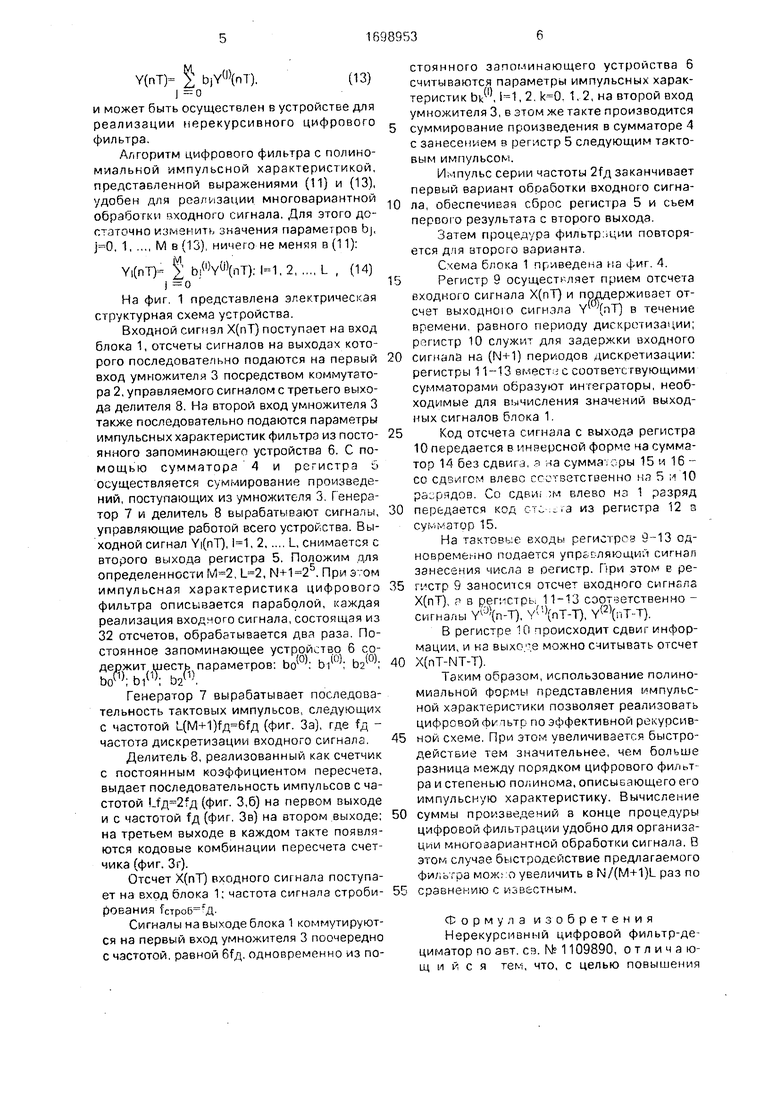

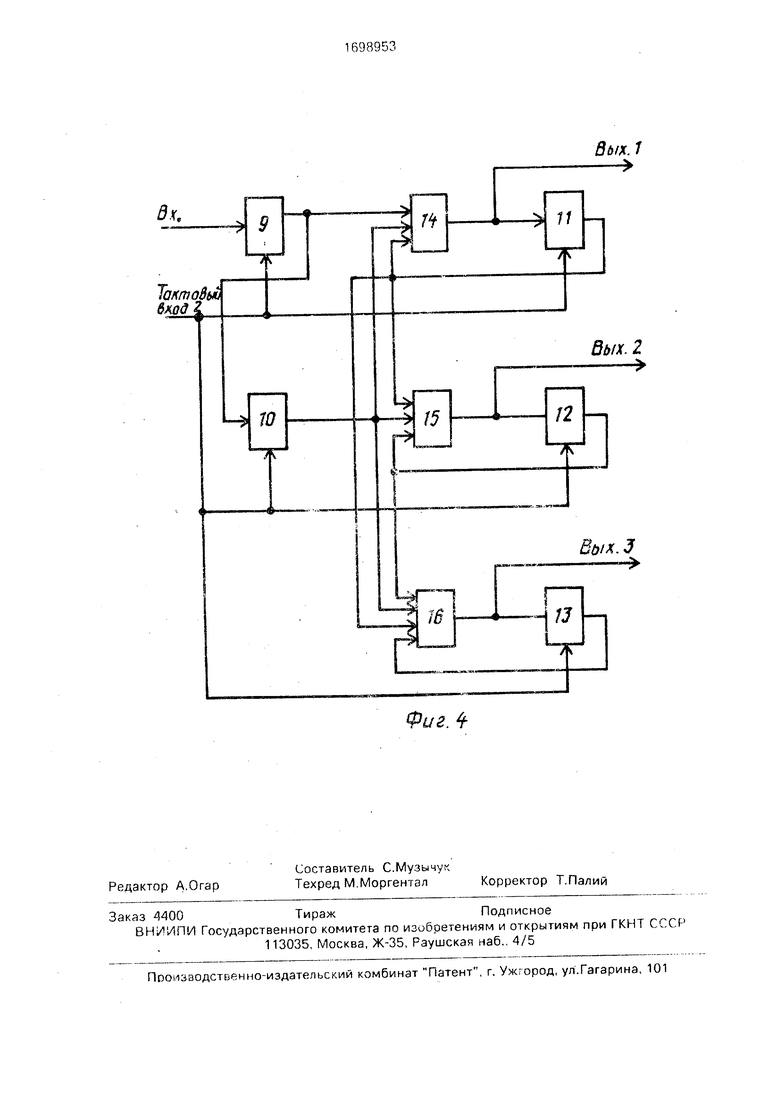

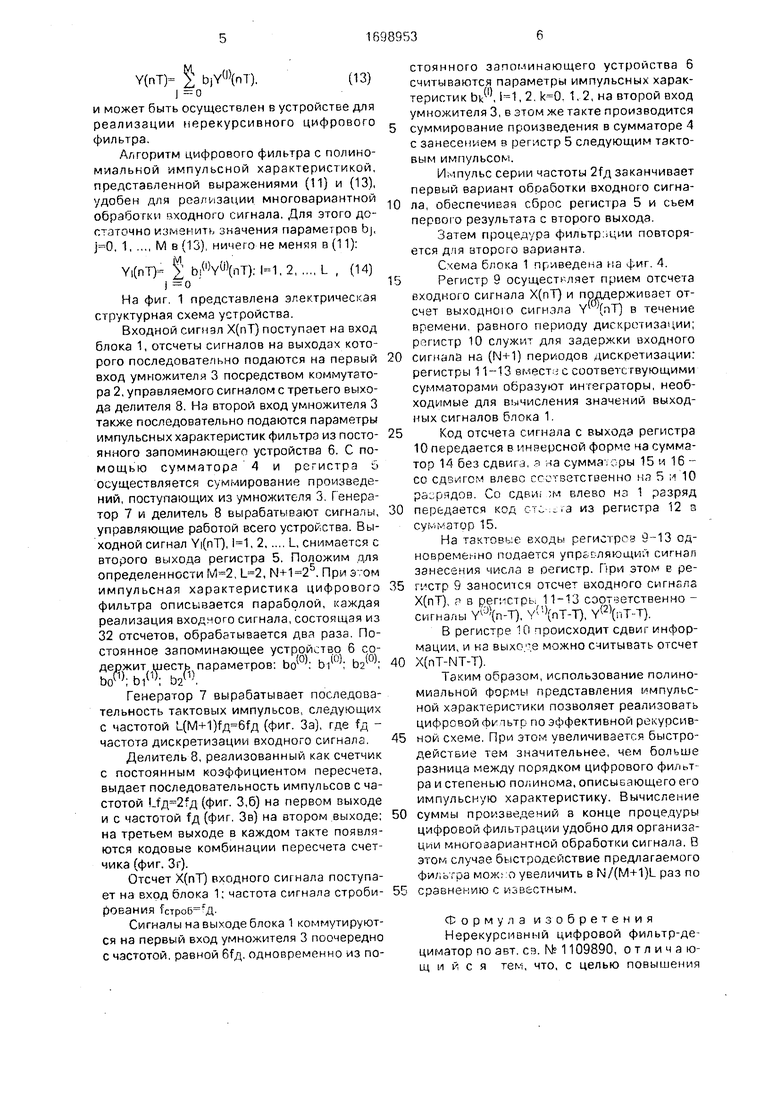

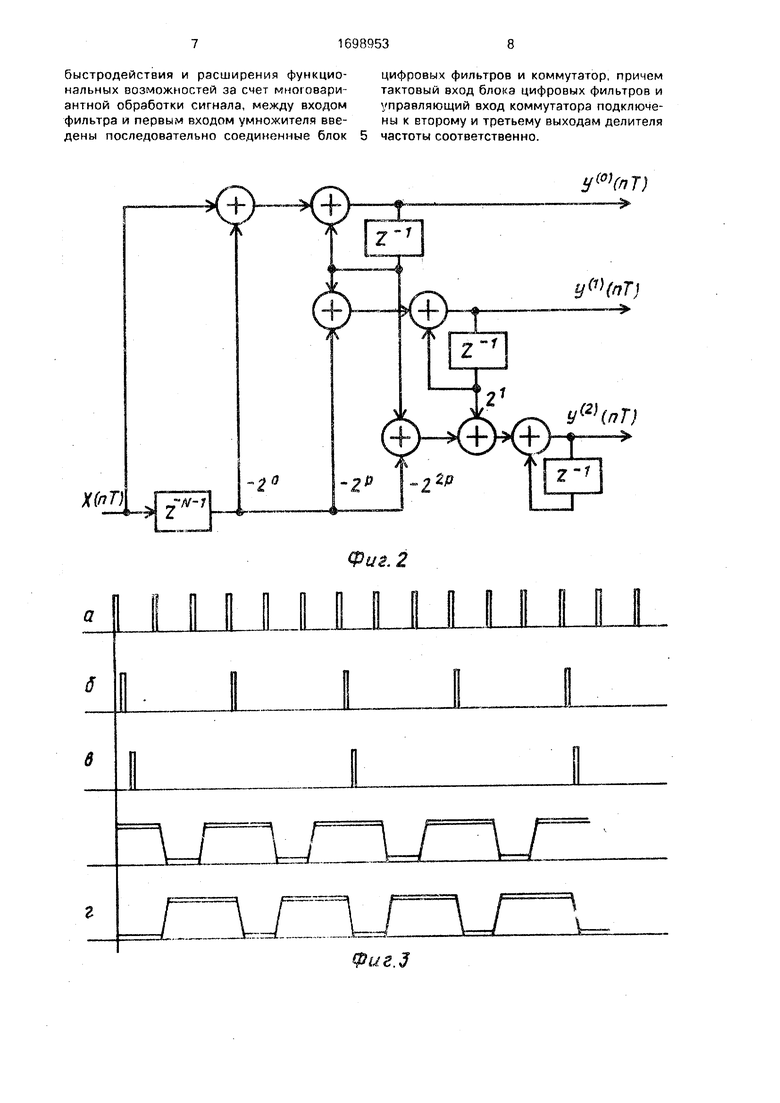

На фиг. 1 приведена электрическая структурная схема нерекурсивного цифрового фильтра-дециматора; на фиг. 2 - алгоритм вычислений блока цифровых фильтров; на фиг. 3 - временные диаграммы сигналов делителя частоты; на фиг. 4 -- структурная электрическая схема блока цифровых фильтров.

Нерекурсивный цифровой фильтр-де- циматор содержит блок 1 цифровых фильтров, коммутатор 2, умножитель 3, сумматор 4, регистр 5, постоянное запоминающее устройство б, генератор 7 тактовых импульсов и делитель 8 частоты.

Блок 1 цифровых фильтров образуют регистры 9-13 и сумматоры 14-16.

Нерекурсивный цифровой фильтр-де- циматор работает следующим образом.

Известно, что передаточная функция нерекурсивного цифрового фильтра имеет вид

Н(2 Ј hkZ

k -О

-k

0)

где hk (, 1,2N) - коэффициенты импульсной характеристики, которую в полиномиальной форме можно представить следующим образом;

м hk Јbjkj,

(2)

где bj - параметры импульсной характеристики. Тогда

H(Z

-Ь,2

) 0 k

Такая запись соответствует параллельной структуре цифрового фильтра со звеньями

§

. 1... .М. (4)

k 0

Импульсные характеристики звеньев линейно независимы, поэтому они могут со

ставить базис множества импульсных характеристик, представленных в форме линейных комбинаций базовых импульсных характеристик.

Уменьшение числа арифметических операций возможно при переходе от прямой к рекурсивной форме переходных функций звеньев, для чего применимо биномиальное разложение коэффициентов импульсных характеристик базовых звеньев;

k1- U- 1) М}1- i (k-lf (5)

Тогда получаем

20

G(0)(Z 1-Z-N 1 (Ь 1-Z

(6)

25

G(1)(Z)Z 1 2(k-1))+Z-inЈZ- k-1) (7)

k 1

Из этого соотношения следует

0

5

G(1)(Z)Z-1G(0)(ZHN+1)Z-(N+1).

1

1 -Z

Аналогично находим

G(2)(Z)(G(0)(Z)+2G(1)(Z))-(N+1) 1

1 -Z

-- I

в общем случае nuWw.

)4

.(8)

(9)

л

+Z

-1 V J1 . R%YI1

(z)irz

0

5

5

, 1М.

Такая форма представления передаточных функций звеньев выявляет возможность использования предыдущих вычислений.

Действительно, из (10) следует алгоритм

Y{J)((nTKN+1)lX(nT-NT-T)+

). ()

где Х(пТ) - отсчет входного сигнала;

Y( 1М) - отсчеты выходных

сигналов.

Система рекуррентных уравнений (11) является алгоритмом блока 1, который можно реализовать без умножителей, положив

, P-целое .(12)

На фиг. 2 показана структура алгоритма блока 1 при .

Алгоритм вычисления выходного сигнала всего устройства следует из (3).

Y(

nT) $

(l)(nU

и может быть осуществлен в устройстве для реализации нерекурсивного цифрового фильтра.

Алгоритм цифрового фильтра с полиномиальной импульсной характеристикой, представленной выражениями (11) и (13), удобен для реализации многовариантной обработки входного сигнала. Для этого достаточно изменить значения параметров bj, , 1М в (13), ничего не меняя в (11):

Yi(nT) b;(VVr),2L , (14)

j o

На фиг. 1 представлена электрическая структурная схема устройства.

Входной сигнал Х(пТ) поступает на вход блока 1, отсчеты сигналов на выходах которого последовательно подаются на первый вход умножителя 3 посредством коммутатора 2, управляемого сигналом с третьего выхода делителя 8. На второй вход умножителя 3 также последовательно подаются параметры импульсных характеристик фильтра из посто- янного запоминающего устройства 6. С помощью сумматора 4 и регистра 5 осуществляется суммирование произведений, поступающих из умножителя 3. Генератор 7 и делитель 8 вырабатывают сигналы, управляющие работой всего устройства. Выходной сигнал Yi(nT), , 2L, снимается с

второго выхода регистра 5. Положим для определенности , , . При этом импульсная характеристика цифрового фильтра описывается параболой, каждая реализация входного сигнала, состоящая из 32 отсчетов, обрабатывается два раза. Постоянное запоминающее устройство 6 содержит шесть параметров: bo 0 : ЬоС1); bi(1); b2(1).

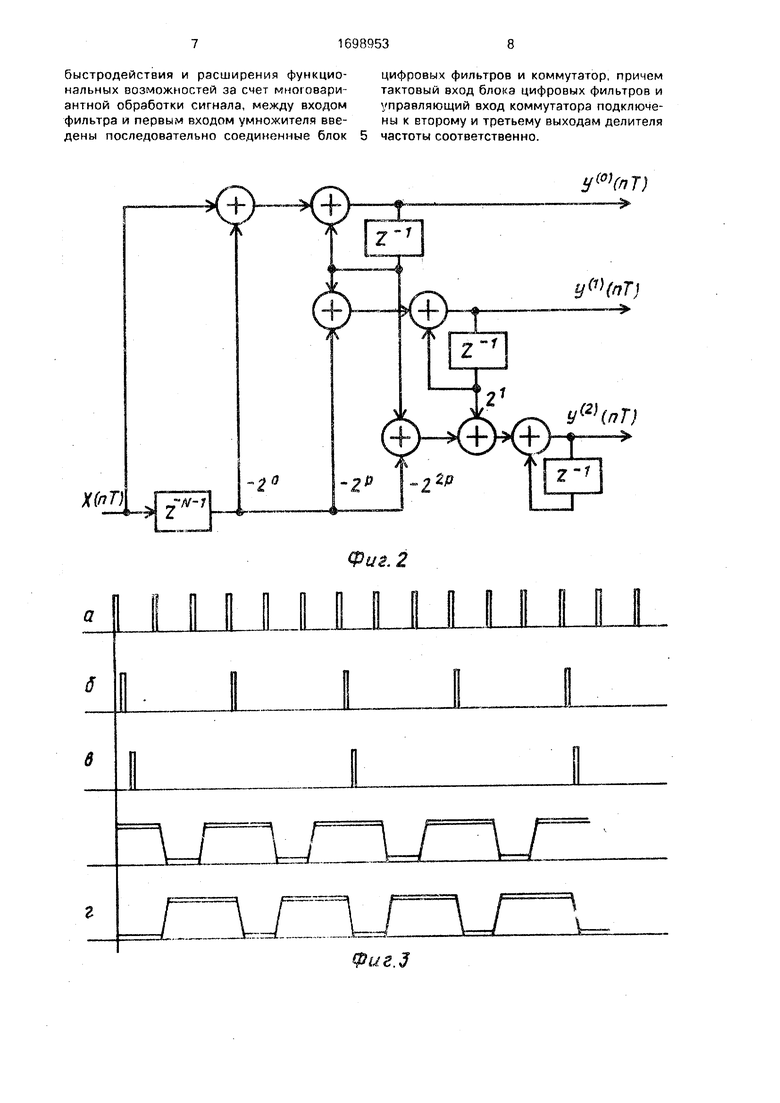

Генератор 7 вырабатывает последовательность тактовых импульсов, следующих с частотой ЦМ+1) (фиг. За), где тд - частота дискретизации входного сигнала.

Делитель 8, реализованный как счетчик с постоянным коэффициентом пересчета, выдает последовательность импульсов с частотой (фиг. 3,6) на первом выходе и с частотой (фиг. Зв) на втором выходе; на третьем выходе в каждом такте появляются кодовые комбинации пересчета счетчика (фиг. Зг).

Отсчет Х(пТ) входного сигнала поступает на вход блока 1; частота сигнала строби- рования fcipo6 ffl.

Сигналы на выходе блока 1 коммутируются на первый вход умножителя 3 поочередно с частотой, равной бтд. одновременно из по

ц

1П

15

2025 30

35 40

45

50 55

стоянного запоминающего устройства 6 считываются параметры импульсных характеристик bk , 1-1, 2, , 1, 2, на второй вход умножителя 3, в зтом же такте производится суммирование произведения в сумматоре 4 с занесением в регистр 5 следующим тактовым импульсом.

Импульс серии частоты 2тд заканчивает первый вариант обработки входного сигнала, обеспечивая сброс регистра 5 и сьем первого результата с второго выхода.

Затем процедура фильтр,ции повторяется для второго варианта.

Схема блока 1 приведена на фиг. 4.

Регистр 9 осуществляет прием отсчета входного сигнала Х(пТ) и поддерживает отсчет выходнот сигнала Y1 (пТ) в течение времени, равного периоду дискретизации; регистр 10 служит для задержки входного сигнала на (N+1) периодов дискретизации; регистры 11-13 вместе: с соответс гвующими сумматорами образуют интеграторы, необходимые для вычисления значений выходных сигналов блока 1.

Код отсчета сигнала с выхода регистра 10 передается в инверсной форме ча сумматор 14 без сдвига, я на суммам еры 15 и 16 - со сдвигом влево соответственно на 5 и 10 разрядов. Со сдви м влево на 1 разряд передается код G -X t.a из регистра 12 в сумматор 15.

На тактовъ.е входы регистров 9-13 одновременно подается упр&с-ляющий сигнал занесения числа в регистр. При зтом в регистр 9 заносится отсчет входного сигнала X(nT), f в регистры 11-13 соответственно - сигналы Y 0)(n-T). Y()(nT-T), Y().

В регистре 10 происходит сдвиг информации, и на выходе можно считывать отсчет X(nT-NT-T).

Таким образом, использование полиномиальной формы представления импульсной характеристики позволяет реализовать цифровойфитьтр поэффективней рекурсивной схеме. При этом увеличивается быстродействие тем значительнее, чем больше разница между порядком цифрового филет- ра и степенью полинома, описывающего его импульсную характеристику. Вычисление суммы произведений в конце процедуры цифровой фильтрации удобно для организации многозариантной обработки сигнала. В этом случае быстродействие предлагаемого фильтра мож: о увеличить в N/(M+1)L раз по сравнению с известным.

Формула изобретения Нерекурсивный цифровой фильтр-де- циматор по авт. сз. № 1109890, отличающийся тем, что, с целью повышения

быстродействия и расширения функциональных возможностей за счет многовариантной обработки сигнала, между входом фильтра и первым входом умножителя введены последовательно соединенные блок

Х(лТ)

цифровых фильтров и коммутатор, причем тактовый вход блока цифровых фильтров и управляющий вход коммутатора подключены к второму и третьему выходам делителя частоты соответственно.

Ут(пТ)

Фиг. 2

Фие.З

. 1

Фиг. 4

| Нерекурсивный цифровой фильтр-дециматор | 1982 |

|

SU1109890A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1991-12-15—Публикация

1989-06-14—Подача