Изобретение относится к импульсной технике и может быть использовано для синхронного двоичного счета импульсных сигналов.

Целью изобретения является упроще- ние синхронного двоичного счетчика импульсов.

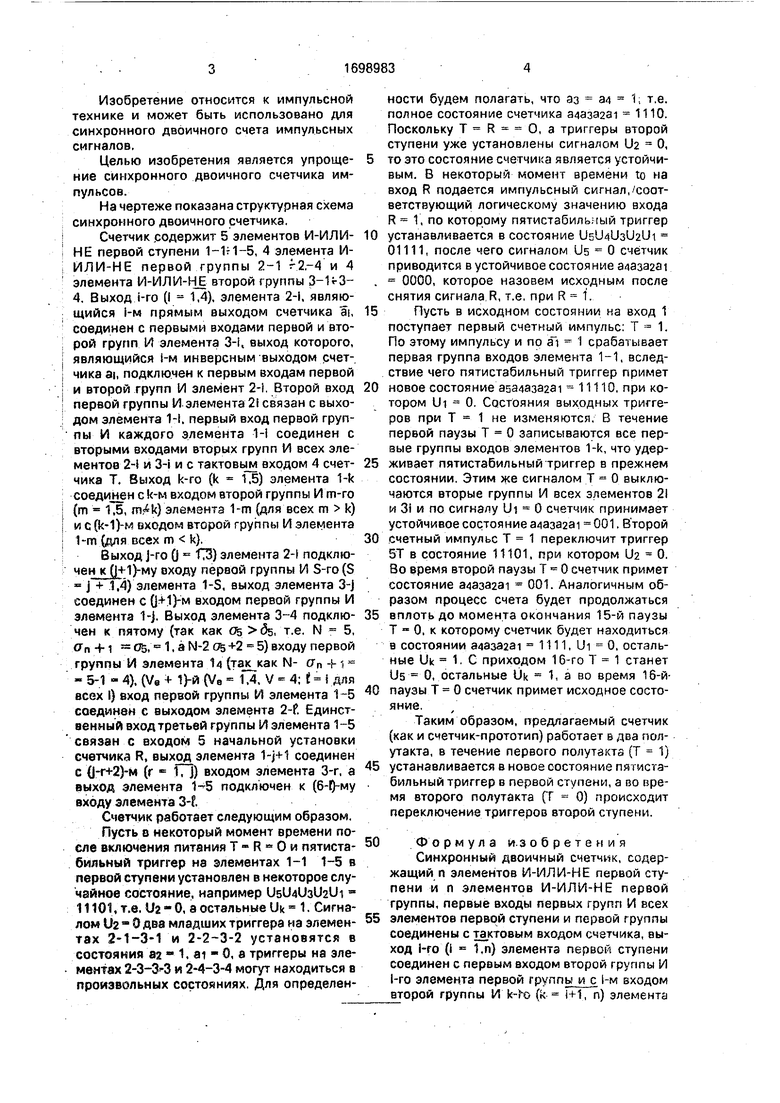

На чертеже показана структурная схема синхронного двоичного счетчика.

Счетчик содержит 5 элементов И-ИЛИ- НЕ первой ступени 1-1М-5, 4 элемента И- ИЛИ-НЕ первой группы 2-1 f2.-4 и 4 элемента И-ИЛИ-НЕ второй группы 3-НЗ- 4. Выход i-ro (I 1.4). элемента 2-i, являющийся f-м прямым выходом счетчика 1й, соединен с первыми входами первой и второй групп И элемента 3-1, выход которого, являющийся 1-м инверсным выходом счетчика Э|, подключен к первым входам первой и второй групп И элемент 2-i. Второй вход первой группы И элемента 21 связан с выходом элемента 1-1. первый вход первой группы И каждого элемента 1-1 соединен с вторыми входами вторых групп И всех элементов 2-1 и З-i и с тактовым входом 4 счет- чика Т. Выход k-ro (k « 1,5) элемента 1-k соединен с k-м входом второй группы И т-го (т 1,5, ) элемента 1-т (для всех т k) и с (k-1)-M входом второй группы И элемента 1-т (для всех т k),

Выход j-ro 0 ГЗ) элемента 2-1 подключен к р+1)-му входу первой группы И S-ro{S j + 1.4) элемента 1-S, выход элемента 3-j соединен с (|+1}-м входом первой группы И элемента 1-}. Выход элемента 3-4 подклю- чен к пятому (так как ОБ 3s, т.е. N 5, оп +1 О5, 1, a N-2 Os +2 5) входу первой группы И элемента 14 ( N- сгп -И - 5-1 - 4). {Ve + 1)-й (Ve - 1,4. V 4; t i для всех I) вход первой группы И элемента 1-5 соединен с выходом элемента 2-Р. Единственный вход третьей группы И элемента 1-5 связан с входом 5 начальной установки счетчика R, выход элемента 1-J+1 соединен с (j-r+2)-M (г - 1, ) входом элемента 3-г, а выход элемента подключен к (6-1)-му входу элемента 3-t

Счетчик работает следующим образом.

Пусть в некоторый момент времени после включения питания Т - R и О и пятиста- бильный триггер на элементах 1-1 1-5 в первой ступени установлен в некоторое случайное состояние, например UslMUal Ut 11101, т.е. Ua- 0, а остальные Uk 1. Сигналом U2 0 два младших триггера на элемен- тах 2-1-3-1 и 2-2-3-2 установятся в состояний 82 1. ai m 0, а триггеры на элементах 2-3-3-3 и 2-4-3-4 могут находиться в произвольных состояниях. Для определенности будем полагать, что аз 34 1, т.е. полное состояние счетчика 34333281 1110. Поскольку Т R О, а триггеры второй ступени уже установлены сигналом 1)2 О, то это состояние счетчика является устойчивым. В некоторый момент времени to на вход R подается импульсный сигнал,/соответствующий логическому значению входа R 1, по которому пятистабильмый триггер устанавливается в состояние LtelMUaUaUi 01111, после чего сигналом Us 0 счетчик приводится в устойчивое состояние апаза2а1 0000, которое назовем исходным после снятия сигнала, т.е. при R .

Пусть в исходном состоянии на вход 1 поступает первый счетный импульс: Т 1. По этому импульсу и по al 1 срабатывает первая группа входов элемента 1-1, вследствие чего пятистабильный триггер примет новое состояние а5а4аза2Э1 11110, при котором Ui 0. Состояния выходных триггеров при Т 1 не изменяются. В течение первой паузы Т 0 записываются все первые группы входов элементов 1-k, что удерживает пятистабильный триггер в прежнем состоянии. Этим же сигналом Т 0 выключаются вторые группы И всех элементов 21 и 3i и по сигналу Ui 0 счетчик принимает устойчивое состояние 34333231 001. Второй счетный импульс Т 1 переключит триггер 5Т в состояние 11101. при котором Lte 0. Во время второй паузы Т 0 счетчик примет состояние 34333231 001. Аналогичным образом процесс счета будет продолжаться вплоть до момента окончания 15-й паузы Т - 0, к которому счетчик будет находиться в состоянии 34333231 1111, Ui 0, остальные Uic 1. С приходом 16-го Т 1 станет Us 0, остальные Uk 1, а во время 16-й- паузы Т 0 счетчик примет исходное состояние.

Таким образом, предлагаемый счетчик (как и счетчик-прототип) работает в два полутакта, в течение первого полутакта (Т 1) устанавливается в новое состояние пятистабильный триггер в первой ступени, а во время второго полутакта (Т 0) происходит переключение триггеров второй ступени.

Формула и.з обретения Синхронный двоичный счетчик, содержащий п элементов И-ИЛИ-НЕ первой ступени и п элементов И-ИЛИ-НЕ первой группы, первые входы первых групп И всех элементов первой ступени и первой группы соединены с тактовым входом счетчика, выход 1-го (I 1,п) элемента первой ступени соединен с первым входом второй группы И i-ro элемента первой группы и с i-м входом второй группы И k-ro (k 1+1, п) элемента

первой ступени, выход которого подключен к (к-1)-му входу второй группы И 1-го элемента первой ступени, отличающийся тем, что, с целью упрощений в него введены п элементов И-ИЛИ-НЕ второй группы и I (п+1)-й элемент И-ИЛИ-НЕ первой ступени, первый вход первой группы И которого подключен к первым входам первых групп И всех элементов второй группы и к тактовому входу счетчика, выход 1-го элемента первой ступени соединен с 1-м входом второй группы И (п+1)-го элемента, единственный вход третьей группы И которого подключен к входу установки счетчика в О, а выход (п+1)-го элемента соединен с n-ми входами вторых

0

5

групп И всех остальных элементов первой ступени, выход 1-го элемента второй группы, являющийся 1-м инверсным выходом счетчика, соединен с (1+1 )-м входом первой группы И 1-го элемента первой ступени и с вторыми входами обеих групп И 1-го элемента первой группы, выход которого, являющийся 1-м прямым выходом счетчика, подключен к второму входу первой группы И и к первому входу второй группы И 1-го элемента второй группы и к (1+1)-му входу первой группы И s-го (s 1+1, п + 1) элемента первой ступени, а выход (М)то элемента первой ступени соединен с (i-r + 2)-м (г - 170 входом второй группы И r-го элемента второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный счетчик | 1989 |

|

SU1688406A1 |

| Двоичный счетчик | 1990 |

|

SU1725390A1 |

| Генератор случайной последовательности | 1983 |

|

SU1275434A1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2749150C1 |

| Многоканальный интерфейс | 1990 |

|

SU1751774A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1310803A1 |

| Счетчик импульсов с управляемым коэффициентом пересчета | 1974 |

|

SU517165A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

Изобретение относится к импульсной технике и может быть использовано для синхронного двоичного счета импульсных сигналов. Цель изобретния - упрощение синхронного двоичного счетчика. Синхронный двоичный счетчик содержит элементы И-ИЛИ-НЕ 1,2 и 3, вход сброса 5 и тактовый вход 4. 1 ил. di СО с о о 00 ю 00 со

| Оберман Р.М.М | |||

| Счет и счетчики, М.: Радио и связь, 1984 | |||

| Букреев И.Н | |||

| и др, Микрозлектронные схемы цифровых устройств | |||

| М.: Советское радио, 1975,, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| & | |||

Авторы

Даты

1991-12-15—Публикация

1989-09-05—Подача