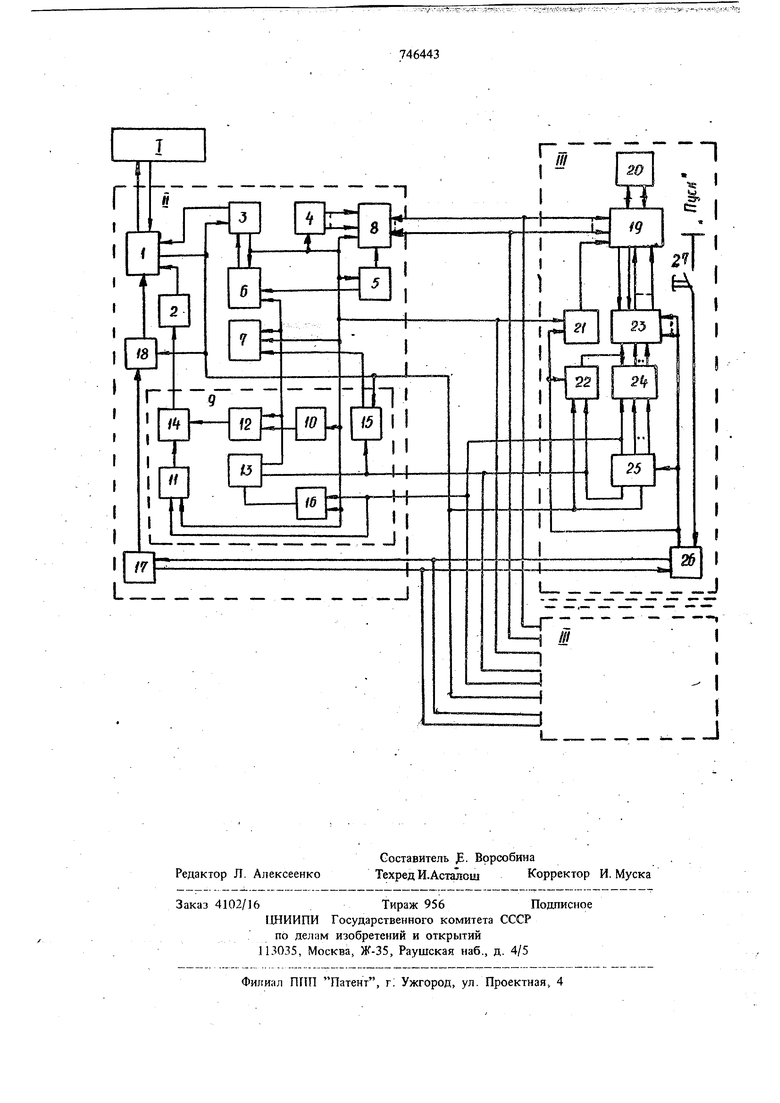

Изобретение относится к контрольно-измерительной технике, в частности, к системам автоматического контроля параметров цифровых интетральных схем (ЦИС), в том числе и больших интегральных схем (БИС) в условиях их массового производства, и может использоваться для автоматического контроля па раметров интегральных схем с функцией памят а также для .контроля параметров любых схем содержащих ячейки, требующие одинаковогорежимного обеспечения и, следовательно, одной программы контроля, таких как многовходовые логические элементы И, НЕ, И-НЕ, ИЛИ, ИЛИ-НЕ и др. Известна система для автоматического конт роля параметров электронных схем, включающая в себя управляюшук вычислительную машину, измерительные станций, рабочие посты, дещифратор измерительных станций и блок прерывания программ 1. Наиболее близкой к преддтагаемой является система совмещенного контроля статических и динамических параметров цифровых интегральных схем и бпльигих интегральных схем. содержащая управляющую вьтчислйтеЛьнуи) машину, измерительную станцшо, состоя1цую из коммутадаонной матрицы, блока программируемых ист очников напряжения и тока, блока измерения, блока сравнения, блока регистров тестовых комбинаций, блока задания временнь1х интервалов сЬгласук)щёт оустрс йства, блока прерывания УВМ, регистра готовности измерительной стан101И, и рабочие посты, содержащие коммутатор выводов, подключенный к контактному устройству для включения испытуемой интегральной схемы, устройство управления коммутатором вьфодов и регистр готовности рабочего поста 2. При переходе от контроля одной ячейки к контролю другой, измерительная ста1гния обращается к управляющей вьпшслительной машине для получения команд на соответствующие переключения в коммутационной матрице. Такой принцип работы возможен при контроле параметров цифровых интегральных схем, состоящих из неодинаковых ячеек, контродь каждой из которых требует своего режимного обеспечения и, следовательно, индиijiJ8tg 4fa- - J -тт- : ЯЯа-t. ,. e,SS .. „. - ,-1- jA lkJ:33b.-assss-ruir .ii С , .«-. s ss-:ru Л5 „-Ь , isf гтроля, заложенной видуапьнои програм в памяти УВМ Недостатками известных систем для кон трбля параметровинтегральных схем являются ограниченные функциональные возможности, низкая производительность и значительный объем используемой памяти УВМ. Цель изобретения - расширение области применения и увеличение быстродействия системы. Поставленная цель достигается тем, что в ибтему автоматического контроля параметров интегральных схем, содержащую управля юи1ую вьГчисяительйуй) Машину, соединенную с измерительным устройством, включающим коммутатор, соединенный первыми входами с выходами блока программируемых источников, вторым входом - со вторым выходом измерения, г tpetbHM входом - с первыми входами блока Сравнения, блока измерения, блока программируемых источнико напряжения и тока бл а адакия временных интервалов И первый выходом блока регистро нервьш вход которого подключен к выходу блока сравнения, а второй вход - к первому входу элемента первому выходу блока согласования, первый вход которого соединен свыходом блока прерывания, второй вход - со вторым выходом блока регистров, а третий 1 ° которого соединен с выходом первого регистр готовности, и несколько автономных каналов измерения состоящих из .последовательно сое.диненных кнопки Пуск, второго регистра готовности, блока управления и второго комм койгрЪго соединены с четверfBiMH входами первого коммутатора, а вторые входьГ являются рабочиШГМодами системы, второй вход блока управления подключен .к выходу блока регистров, а второй регистр го fbBflbctlTtoeflVffierfс рвы регистром готов,. ,. ,.,. ,«. V. (« ч ности, введёнь в измерительное устройство ™ёлёкТ6р режимов, состояидай из элемента НЕ -.,.i--.ir-inr--т-1- -г-:--1.-г,-,- --ill --j- --- w TVrT fH t .:..; двух элементов ИЛИ, трех элементов И и триггера, а в каждый кай1н измерения - .„,..™.,,,.. ..,-,-Ь.,,„„,,,л,«-...-., блок формирователей уровТГеи, дешифратор, формирователь КомШвГ й етчик, выход старш первым вхо дам триггеЪа 11перв6т6элемента И, вторые .J-.«..,,jE«tjW J-..S:4 -- ««4 -J i W fea3 -йхбдьг йоторйх Го;еДи1 Ген|1 с; первым входом блока регистров и вхЩ;ОЙ ;элемента НЕ, вь1 Й1Д kbircpbro подклйадн Через второй элемент ™™ irf1KpiS ffШ элемента ИЛИ, °° 11Тор6ГвШ1ат Ш Шген с вь1хЬдЬм .as,ii..jee..™ib,.,™i.,™,o..,i,ij..-«.-a -it «« iajoa первого элемента И, - со входом aBj«i..- T d8gaE i eitaiaat .aaafl-- EaMateiHaass | ; .V блрка прерыванииТ тахо гтриггера подключен Ш ШГс Г ретьего элемента ЛХ iiMtjSii fc j-.;.- 4j t UJifca6i iijfjV iSivV . .-. -..a.vi5t-| ШЙ 1Гфор1йиТодащ:тГсШ|1НД через .третий элемент И, второй вход кЬторого соединен s:g ig« jaKrt3ar2 i-via;-Kii;«SEa:i te ---.-- - . 3 ,.4 с вторыми входами блока сравнения, второго элемента. И и выходом блока задания времепных интервалов, третий вход которого подключен к выходу третьего элемента ИЛИ, второй вход которого соединен с первым выходом блока согласования и с вторыми входами формирователя команд и счетчика, вь1х6ды которого подютючены через дешифратор к первым входам блока формирователей уровней,соединенного с вторым коммутатором, выход формирователя команд подключен к третьим входам дешифратора и блока формирователей уровней, а третий вход соединен с Четвертыми входами блока формирователей уровней и первым выходом второго регистра готовности. На чертеже показана блок-схема одного измерительного канала. Система содержит управлйюидую вычислительную машину Г, измерительное устройство ГГ и п - индентичных автономных каналов TII измерения: Измерительное устройство tl содержит блок 1 согласования, блок 2 прерывания, блок 3 регистров, блок 4 программируемых источников напряжения и тока, блок 5 измерения, блок 6 сравнения, блок 7 задания временных интервалов, коммутатор 8, селектор 9 режимов, элемент НЕ 10, элемент И 11, элемент И 12, элемент И 13, элемент ИЛИ 14, элемент ИЛИ 15, триггер 16, регистр 17 готовности, элемент ИДИ 18.. Каждый из каналов измерения содержит коммутатор 19, рабочий вход 20 системы, 21 управления, формирователь 22 команд блок 23 формирователей уровней, дешифратор 24, счетчик 25, регистр 26 готовности, кнопку 27. Система работает следующим образом. Измерительное устройство Г Г осзществляет, поочередный (обегающий) опрос регистров 26 готовности, фиксирующих подключение ко входу 20 контролируемой интег.ральной схемы, а управляющая вычислительная машина Т, в свою, очередь, производит опрос готовности измерительного устройства 1 Г, посылая команду опроса через блок 1 согласования на вход элемента ИЛИ 18, который не пропускает эту команду до тех пор, пока не взведен регистр 17 сигналом от регистра 26. Как только контролируемая интегральная схема подключается ко входу 20, оператор, обслуживающий измерительный канал, нажимает кнопку 27 и тем самым взводит регистр 26, который в свою очередь взводит регистр 17. По получении с выхода регистра 17 сигнала готовности элемент ИЛИ 8 пропускает на управляющую вычислительную машину Т через блок I согласоппиия комяплу опроса готовносги измерительного устройства Т Г, поступившую на его первый вход. По получении сигнала готовности измерительного устройства 1Г, управляющая вычислительная маинша I выдает командьт ичерез блок 1 согласования осуществляет распределение информационтюй части команд программы контроля в соответствующие регистры блока 3. Информационная часть команды программы содержит данные, необходимые для выпОлнения программы, контроля параметра, а именно данные 6 величине контрольных и контролируемых сигналов, о величине граничных значений контролируемых параметров, о необходимых переключениях в коммутаторе 8, о времени переходных процессов при контроле параметров, а также данные о режиме работы измерительного устройства II и каналов III измерения.

Из блока 3 цифровая информация в двоимном коде поступает в блок 4, где коды информационной части команд преобразуются в выходные напряжения и токи определенной величины и полярности, в блок 5, в блок 6, в блок 7, преобразующий двоич11ые коды в аналоговые сигналы, в коммутатор 8, на входы элементов НЕ 10, И 11 и триггера 16 селектора 9, а также на вход блока 21, который по получении этого сигнала разрешает подключение выходов блока 23 через коммутатор 19 к адресным входам контролируемой интегральной схемы БИС. Через коммутаторы 8 и 19 соответствующие выходы блока 4 подключаются к требуемым выводам контролируемой интегральной схемы, а также к соответствующим входам блока 23, на выходах которого формируются контрольные сигналы низкого ил высокого уровней О и 1 соответственно. Кроме того, через коммутаторы 19 и 8 соответствующие выводы испытуемой интегральной схемы БИС подключаются ко входу блока 5. После срабатывания коммутатора 8 и коммутатора 19 управляющая вычислительная машина выдает команду Начало контроля, по по.лучении которой измерительное устройство IT отключается от управляющей вычислительной мащины, а команда Начало контроля поступает через элемент ИЛИ 15 на вход блока 7 и в измерительный канал III - на один из входов формирователя22 и вход N - разрядного двоичного счетчика 25. По получении команды Начало контроля блок 7 формирует временной интервал на установление переходных процессов, формирователь 22 вырабатывает команду на подзарядку внутренних емкостей испытуемой интегральной схемы, которая через блок 23 разрешает проведение процесса подзарядки, а счетшк 25 формирует адресный код первой контролируемой ячейки интегральной

схемы, который поступает на дешифратор 24, формирующий адресные Ьигналы для первой контролируемой ячейки. Эти сигналы с выхода дешифратора 24 посредством блока 23 устанавливают на выводах контролируемой схемы необходимые сигналы управления, разрешая тем самым доступ к первой ячейке контроля. Результат контроля с выхода блока 5 поступает на вход блока 6.

По окотиании временного интервала на установление переходных процессов блок 7 форми рует сигнал на разрешение сравнения в блоке 6 цифрового эквивалента измеряемого параметра с его эталонным значением и занесение результата сравнения в блок 3. Одновременно указанный сигнал с выхода блока 7 поступает через элемент И 13 в измерительный канал 111 на входы N-разрядного счетчика 25 и формирователя 22, а также через элемент ИЛИ 15 на вход блока 7.

По получении указанного сигнала счетчиком 25 содержимое последнего увеличивается на единицу, что соответствует установлению кода адреса второй контролируемой ячейки. При этом формирователь 22 вырабатывает сигнал, на проведение подзарядки и запрещает работу дешифратора 24 на время подзарядки. По окончации указанного сигнала блок 7 формирует временной интервал на установление переходных процессов для контроля второй ячейки. Измерение параметров второй и последующих ячеек происходит вышеописанным образом.

Информация о результатах контроля ячеек памяти контролируемой интегральной схемы заносится из блока 6 в регистры блока 3, где хранится до окончания процесса контроля всех ячеек.

, Об окончании контроля параметров последней ячейки интегральной схемы свидетельствует сигнал, установившийся на выходе последнего ..разряда N-разрядного счетчика 25. Этот сигнал поступает на входы триггера 16 и элемент И 11 селектора 9. Триггер 16 при этом взводится и.запрещает тем самым прохождение через элемент И 13 сигналов на повторение контроля, а элемент И 11 пропускает сигнал окончания контроля через элемент ИЛИ 14 в блок 2, посредством которого осуществляется подключение измерительного устройства II к управляющей вычислительной машине Т. При этом вся информация о результатах контроля переписывается иэ блока 3 в управляющую вычислительную мац1ину Г, где осуществляется ее обработка.

Таким образом осуществляется процесс многократного измерения параметров без обращения к управляющей вьпшслительной машине. Аналогично осуществляется контроль параметров любых интегральных схем, состоящих из одинаковых HleeK, требующих одного режимного обеспеченйяй,следовательно, одной программы контроля.

Предложенная система для автоматического ко гтроля параметров ит1тегральных схем более эффектйвна п6 срав||Гёнию с известными. Она обеспечивает высокую производительность контроля за счет исключения многократного рбраЩейий к ;утгравляюшей вычислительной машине при контроле параметров одинаковых элементов интегральных схем, требующих одной программы контроля.

Предложенная система обладает более широкими функциональными возможностями, поскОлъку она обеспечивает контроль схем, требуюшйх команд на подзарядку внутренних емкостей. Кроме того, и предложенной системе при контроле пораметров ИС, состоящих из одинаковых ячеек, используется меньший объем памяти УВМ, поскольку в программе контроля исключены команды на переключения элементов в коммутационной матрице при переходе от контроля одной ячейки к контролю другой.

Формула изобретения

Система для автоматического контроля пара метров интегральных схем, содержащая управляющую вьтислительную мапшну, соединенную с измерительным устройством, включающим коммутатор, соединенньш первыми входами с выходами блока йр6гр аммируемых источ(шков, вторым входом - со BtopbiM вьгходом блока измеретшя, а третьим входом - с первыми входами блока сравнения, блока измерения, блока программируеМШ ГИС ЧНИКОБ напряженйя и тока, 6jroka задания Временных интерваjroB и первым выходом блока регистров, первый вход которого подключен к выходу блока ср;1внёниЯ, а второй вход - к первому входу элемента ИЛИ и первому выходу блока согла со1а1гия7 первый вход которого соединен с , .ходом блока прерывания, второй вход - со Жбрым выходом бчока регистров, а третий вход - с выходом элемента ИЛИ, второй

вход KOTOpofo соединен с выходом первого --регистра готовности, и neCKOJtbKo автономных ка17алов измерения, состояших из последова- feJibHO соедиГгенных кнопки Пуск, второго

64438

регистра ютовности, блока управления и второго ко №тутатора, вьгходы которого соедиче ны с четвертыми входами первого коммутатора, а вторые входы являются рабочими входами J системы, второй вход блока управления подключен к выходу блока регистров, а второй регистр готовности соединен с первым регистром готовности, отличаю щ а я с я тем, что, с целью расширения области примеJO нения и увеличения быстродействия системы, в измерительное устройство введеггы селектор режимов, состоящий из элемента НЕ, двух элементов ИЛИ, трех элементов И и триггера, в каждый канал измерения введены блок

J5 формирователей уровней, деишфратор, формирователь команд и счетчик, выход старшего разряда которого подключен к первым входам триггера и первого элемента И, вторые входы которых соединены с первым выходом блока

20 регистров и входом элемента НЕ, выход которого пoдкJlючe f через второй элемент И к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход - со входом блока пре25 рышнгий, выход триггера подключен к первым входам счетчика, третьего элемента ИЛИ и формирователя команд через третий элемент И, второй вход которого соединен с вторыми входами блока сравнения, второго элемента И и выходом

30 блока задания време1гных интервалов, третий вход которого подключен к выходу третьего элемента ИЛИ, второй вход которого соединен с первым выходом б;гока согласования и с вторыми входами формирователя команд и

35 счетчика, в.ыходы которого подключены через дешифратор к первым входам б;гока формирователей уровней, соединенного с вторым коммутатором, выход формирователя команд подключен к третьим входам дешифратора и ка формирователей уровней, а третий вход соединен с четвертыми входами блока формирователей уровней и первым выходом второго регистра готовности.

Источники информации,

45 принятые во внимание при экспертизе

1.Авторское свидетельс1во СССР N 441532, кл. G 05 В 23/02, 971.

2.Богородицкий Л. А. и др.Многопостовой комплекс Электрон-С.Д. - Электронная промьпнленность, 1975, N 1. с. 24-35 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Система автоматического контроля параметров электронных схем | 1981 |

|

SU985764A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Система контроля параметров интегральных схем | 1977 |

|

SU746437A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Автоматизированная система контроля параметров электронных схем | 1987 |

|

SU1500996A1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-18—Подача