1

Изобретение относится к вычислительной технике и представляет собой систему автоматического контроля параметров полупроводниковых приборов, интегральных схем, БИС, функциональных узлов, субблоков и т.д.

Известно устройство для проверки функционирования логических схем, содержащее блок управления, блок ввода данных, блок входных сигналов, блоки контрольных регистров, коммутатор, блок сравнения и блок индикации 1.

Недостатком этого устройства является то, что контроль параметров осуществляется при проверке только одного объекта контроля, т ое. устройство является однопостовым и производительность его невысока.

Наиболее близкой к предлагаемой является система для автоматического контроля параметров электронных

схем, содержащая управляющую вычислительную машину (УВМ и измерительные станции с рабочими постами для подклочения контролируемых схем, причем каждая измерительная станция состоит из коммутатора рабочих постов, соединенного с рабочими постами, регистром рабочих постов и коммутатором выводов схемы, первые входы кото,0 рого подключены к регистру тестовых комбинаций, вторые входы - к блоку программных источников питания, выходы к измерительному блоку и первому входу первой схемы ИЛИ, второй

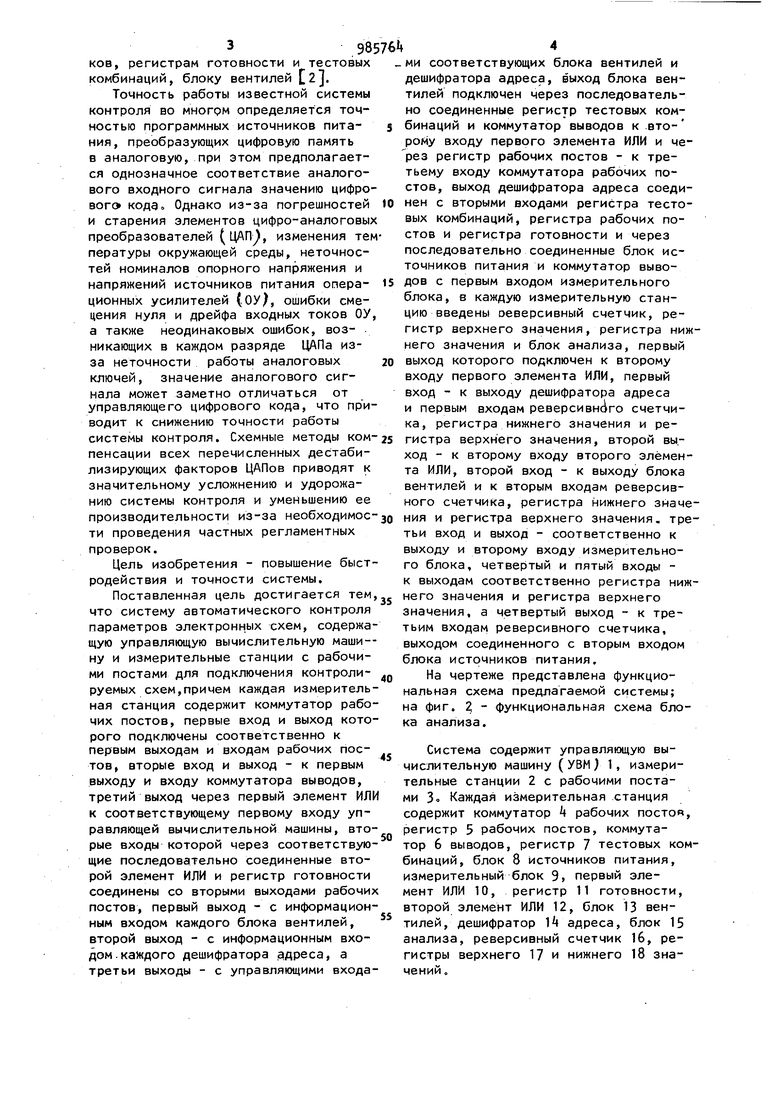

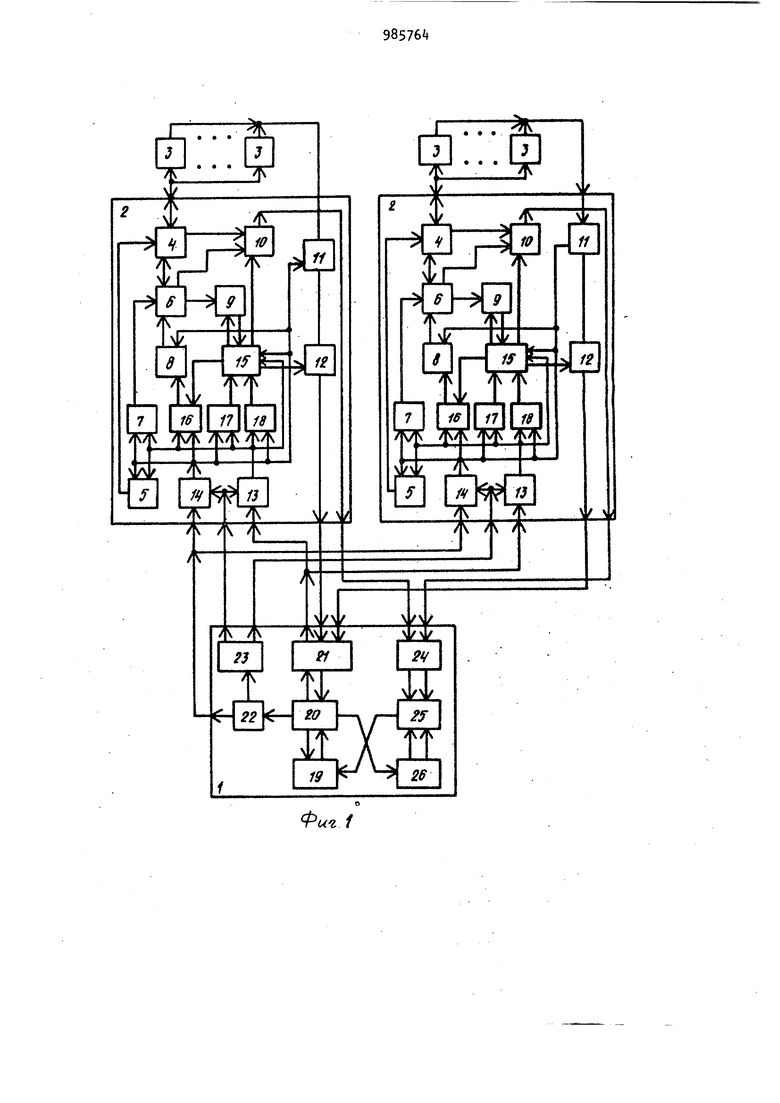

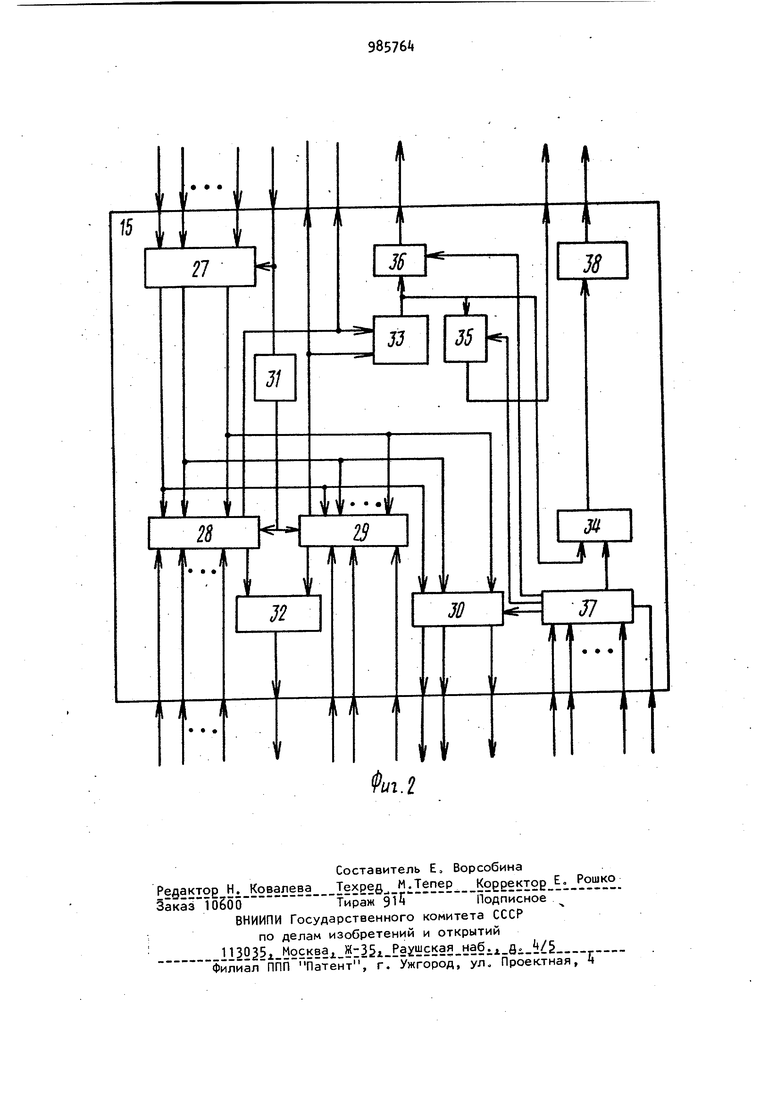

5 вход которой соединен с коммутатором рабочих постов, а выход - с входом прерывания УВМ, регистр готовности рабочих постов, соединенный с рабочими постами, блоком программируемых источников и второй схемой ИЛИ, выход которой подключен к информационным входам УВМ, блок вентилей и дешифратор адресов, подключенный к выходу УВМ, блоку программных источников, регистрам готовности и тестовых комбинаций, блоку вентилей L2J. Точность работы известной системы контроля во многрм определяется точностью программных источников питания, преобразующих цифровую память в аналоговую, при этом предполагается однозначное соответствие аналогового входного сигнала значению цифровогэ кода. Однако из-за погрешностей и старения элементов цифро-аналоговых преобразователей (ЦАП, изменения тем пературы окружающей среды, неточноетей номиналов опорного напряжения и напряжений источников питания операционных усилителей (ОУ), ошибки смецения нуля и дрейфа входных токов ОУ, а также неодинаковых ошибок, возникающих в каждом разряде ЦАПа изза неточности работы аналоговых ключей, значение аналогового сигнала может заметно отличаться от управляющего цифрового кода, что приводит к снижению точности работы системы контроля. Схемные методы компенсации всех перечисленных дестабилизирующих факторов ЦАПов приводят к значительному усложнению и удорожанию системы контроля и уменьшению ее производительности из-за необходимоети проведения частных регламентных проверок. Цель изобретения - повышение быстродействия и точности системы. Поставленная цель достигается тем, ЧТО систему автоматического контроля параметров электронных схем, содержащую управляющую вычислительную маши- ну и измерительные станции с рабочими постами для подключения контролируемых схем,причем каждая измерительная станция содержит коммутатор рабочих постов, первые вход и выход которого подключены соответственно к первым выходам и входам рабочих постов, вторые вход и выход - к первым выходу и входу коммутатора выводов, третий выход через первый элемент ИЛИ к соответствующему первому входу управляющей вычислительной машины, вторые входы которой через соответствующие последовательно соединенные второй элемент ИЛИ и регистр готовности соединены со вторыми выходами рабочих постов, первый выход - с информационным входом каждого блока вентилей, второй выход - с информационным входом, каждого дешифратора адреса, а третьи выходы - с управляющими входами соответствующих блока вентилей и дешифратора адреса, выход блока вентилей подключен через последовательно соединенные регистр тестовых комбинаций и коммутатор выводов к второму входу первого элемента ИЛИ и через регистр рабочих постов - к третьему входу коммутатора рабочих постов, выход дешифратора адреса соединен с вторыми входами регистра тестовых комбинаций, регистра рабочих постов и регистра готовности и через последовательно соединенные блок источников питания и коммутатор выводов с первым входом измерительного блока, в каждую измерительную станцию введены оеверсивный счетчик, регистр верхнего значения, регистра нижнего значения и блок анализа, первый выход которого подключен к второму входу первого элемента ИЛИ, первый вход - к выходу дешифратора адреса и первым входам реверсивного счетчика, регистра нижнего значения и регистра верхнего значения, второй выход - к второму входу второго элёмента ИЛИ, второй вход - к выходу блока вентилей и к вторым входам реверсивного счетчика, регистра нижнего значения и регистра верхнего значения, третьи вход и выход - соответственно к выходу и второму входу измерительного блока, четвертый и пятый входы к выходам соответственно регистра нижнего значения и регистра верхнего значения, а четвертый выход - к третьим входам реверсивного счетчика, выходом соединенного с вторым входом блока источников питания. На чертеже представлена функциональная схема предлагаемой системы; на фиг. 2 - функциональная схема блока анализа. Система содержит управляющую вычислительную машину ( УВМ} 1, измерительные станции 2 с рабочими постами 3 Каждая измерительная станция содержит коммутатор 4 рабочих постоя, регистр 5 рабочих постов, коммутатор 6 выводов, регистр 7 тестовых комбинаций, блок 8 Источников питания, измерительный блок 9, первый элемент ИЛИ 10, регистр 11 готовности, второй элемент ИЛИ 12, блок 13 вентилей, дешифратор Ц адреса, блок 15 анализа, реверсивный счетчик 16, регистры верхнего 17 и нижнего 18 значений. В состав УВМ входят блок 19 управления, блок 20 памяти, регистр 21 обмена, регистр 22 адреса, дешифратор 23 станций, регистр 2 прерывания, блок 25 сравнения и регистр 26 защиты. Блок 15 анализа содержит регистр информации, первый 28 и второй 29 блоки сравнения, блок 30 вентилей, первый элемент 31 задержки, эле.MeHt И 32, первый 33 и второй З эле менты ИЛИ, триггер 35 неисправности, генератор 36 одиночного импульса, ре гистр 37 команд и второй элемент 38 задержки Система работает следующим образом . УВМ через дешифратор станций 23 осуществляет последовательное програ мное сканирование готовности каждой измерительной станции, обеспечивая через дешифратор 1 адреса обегающий опрос регистра готовности и определя первый рабочий пост, готовый к работе в данной измерительной станции Определив пост, готовый к работе, УВМ выдает на станцию первую тестовую комбинацию о значении стимулирующего сигнала, которая в параллельном коде заносится в реверсивный счетчик 16, в регистры 17 и Ш записываются предельные значения аналогового сигнала, который должен отработать ЦАП, а в коммутатор 6 через регистр 7 заносится номер вывода, к которому подключается блок 9. Запись информации в регистры станции осуществляется через регистр 21, блок 13 вентилей под управлением дешифратора 14 адреса После перезаписи информации реверсивного счетчика 1 в соответствующий регистр блока 8 программных источников, УВМ выдает в блок 15 команду на измерение. Блок 15 под управлением регистра 37 работает в трех режимах: отслеживания напряжения ЦАП; контроля измеренного параметра, выдачи в УВМ цифрового кода о величине параметра. В первом режиме регистр 37 через элемент ИЛИ 3, второй элемент 38 задержки выдает сигнал на запуск бло КЗ 9, через интервал времени, необходимый для измерения, блок 9 выдает на информационные входы регистра 27 цифровой код измеренного параметра, а на его управляющий вход - сигнал конца измерения. По этому сигналу информация записывается в регистр 27 и с 98 t некоторой задержкой, необходимой для надежного установления информации на выходе регистра, разрешается сравнение блоками 28 и 29 цифровых кодов регистра 27 и кодов, поступающих с регистров измерительной станции нижнего 17 и верхнего 18 значений. При соответствии измеренного значения допустимым блок 15 анализа по первому управляющему выходу через элемент И 32 запрашивает УВМ на прерывание, в противном случае выдаются соответствующие команды на реверсивный счетчик 16, через элемент ИЛИ 33 и генератор 36 формируется одиночный импульс, а через элемент ИЛИ З и второй элемент 38 задержки вновь запускается блок 9. В первом режиме триггер 35 неисправности блокируется от регистра команд. При поступлении команды на второй режим работы снимается блокировка с триггера 35 и блокируется генератор 36 одиночного импульса. В этом режиме при несоответствии измеренного параметра допустимым значениям через элемент ИЛИ 33 взводится триггер 35 неисправности, выход которого включает световое табло ( не показано}, В третьем режиме работы блока 15 анализа обеспечивается возможность при необходимости считывать информацию из регистра 27 в УВМ для анализа. Работа измерительной станции в целом в первом режиме происходит следующим образом. Приняв команду, блок 15 с кекоторой задержкой t , необходимой ЦАПу блока 8 для отработки цифрового кода, выдает на блок 9 сигнал запуска. Ре-, зультат измерения поступает в блок 15 где происходит его сравнение с предельными значениями сигнала, записанными в регистрах 17 и 18, при этом возможны три комбинации: измеренное значение больше верхнего предельного значения, измеренное значение меньше нижнего предельного значения, измеренное значение находится в заданном интервале допустимых значений о В первом случае блок 15 выдает на управляющий вход реверсивного счетчика 16 сигнал вычитания, а на счетный вход - одиночный импульс, ЦАП отрабатывает новое уменьшенное на 1 значение цифрового кода, затем блок 15 вновь запускает блок 9- Отслеживание аналогового сигнала продолжается до момента, когда измеренное значение станет меньше верхнего предельного значения,, Во втором случае процесс отслеживания аналогичен за исключением того что на управляющий вход реверсивного счетчика выдается сигнал сложения и ЦАП отрабатывает увеличенное на 1 значение цифрового кода. Таким образом осуществляется отслеживание напряжения каждого канала блока 8 и значение аналоговых сигналов по каждому каналу оказывается в заданных пределах допустимых значёНИИ В этом и в третьем случаях, блок 15 анализа через элемент ИЛИ 1 осуществляет запрос на прерывание;и станция готова к получению следующей тестовой комбинации. В следующем интервале, обмена информацией между УВМ и станцией, запр сившей прерывание, считывается состо яние, регистра 1 готовности и УВМ, Определив посты, готовые к работе в данной измерительной станции, последовательно, выдает из регистра 23 чер вентили 13 сигнал включения в регистр 5 который через коммутатор А обеспечивает подключение коммутатора 6 к готовому к работе посту, тем самым обеспечивается последовательное подключение постов внутри станции о Коммутаторы 6 и коммутаторы , также как блок 15, осуществляют запрос прерывания через элемент 10 ИЛИ на вход регистра 24 прерывания УВМ, т.ео во время выполнения команд этими устройствами УВМ свободна для работы с другими станциями. Анализ результатов измерения параметров контролируемой схемы осуществляет блок 1 анализа, сравнивая измеренное значение с предельными, записанными в регистрах 17 и 18, т.ео УВМ освобождае ся на это время для выполнения управляющих функций при работе с измерительными станциями о Использование блока анализа, реверсивного c4eT4ViKa регистров верхнего и нижнего предель ных значении позволяет отследить напряжения блока источников с заданной точностью, которая определяется цифровыми кодами, занесенными в регистры предельных значений. При этом сокращается время, необходимое для проведения регламентных проверок ЦАПов. Точность отслеживания может состав988 лять величину, равную ±1 мл разряда ЦАПа. Кроме того, введенные в систему блоки позволяют вести анализ измеренных значений параметров контролируемой схемы непосредственно в измерительной станции, сранвивая измеренное значение с предельными, записанными в регистрах верхнего и нижнего . предельных значений, тем самым УВМ освобождается от выполнения управляющих функций при работе с большим числом измерительных станций. Формула изобретения Система автоматического контроля параметров электронных схем, содержащая управляющую вычислительную машину и измерительные станции с рабочими постами для подключения контролируемых схем, причем каждая измерительная станция содержит коммутатор рабочих постов, первые вход и выход которого подключены соответственно к первым выходам и входам рабочих постов, вторые вход и выход - к первым выходу и входу коммутатора выводов, третий выход через первый элемент ИЛИ - к соответствующему первому входу управляющей вычислительной машины, вторые входы которой через соответствующие последовательно соединенные второй элемент ИЛИ и регистр готовности соединены с вторыми выходами рабочих постов, первый выход - с информационным входом каждого блока вентилей, второй выход с информационным входом каждого дешифратора .адреса, а третьи выходы - с управляющими входами соответствующих блока вентилей и дешифратора адреса, выход блока вентилей подключен через последовательно соединенные регистр тестовых комбинаций и коммутатор выводов к второму входу первого элемента ИЛИ и через регистр рабочих постов - к третьему входу коммутатора рабочих постов, выход дешифратора адреса соединен с вторыми входами регистра тестовых комбинаций, регистра рабочих постов и регистра готовности и через последовательно соединенные блок источников питания и коммутатор выводов - с первым входом измерительного блока, отличающаяся тем, что, с целью повышен;1я быстродействия и точности системы, в каждую измерительную станцию введены ре версивным счетчик, регистр верхнего значения, регистр нижнего значения и блок анализа, первый выход которого подключен к второму входу первого элемента ИЛИ, первый вход - к выходу дешифратора адреса и первым входам реверсивного счетчика, регистра нижнего значения и регистра верхнего значения, второй выход - к второму входу второго элемента ИЛИ, второй вход - к выходу блока вентилей и к вторым входам реверсивного счетчика, регистра верхнего значения и регистра нижнего значения, третьи вход и выход - соответственно к выходу и 98 второму входу измерительного блока, четвертый и пятый входы - к выходам соответственно регистра нижнего значения и регистра верхнего значения, а четвертый выход - к третьим входам реверсивного счетчика, выходом соединенного с вторым входом блока источников питания. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G Об F 11/00, 1971. 2.Авторское свидетельство СССР № 302717, кл, G Об F 11/00, 1971 (прототип),

Фи11

f5

11

JS

JJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Система для автоматического контроля параметров интегральных схем | 1978 |

|

SU746443A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ | 2003 |

|

RU2248028C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| СИСТЕМА ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ" ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1971 |

|

SU302717A1 |

| Система для контроля электрических параметров логических блоков | 1988 |

|

SU1725230A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Система контроля параметров интегральных схем | 1977 |

|

SU746437A1 |

Авторы

Даты

1982-12-30—Публикация

1981-07-08—Подача