Изобретение относится к автоматике, в частности к устройствам для селекции признаков объектов.

Цель изобретения -- расширение области применения путем реализации обновления информации в реальном времени.

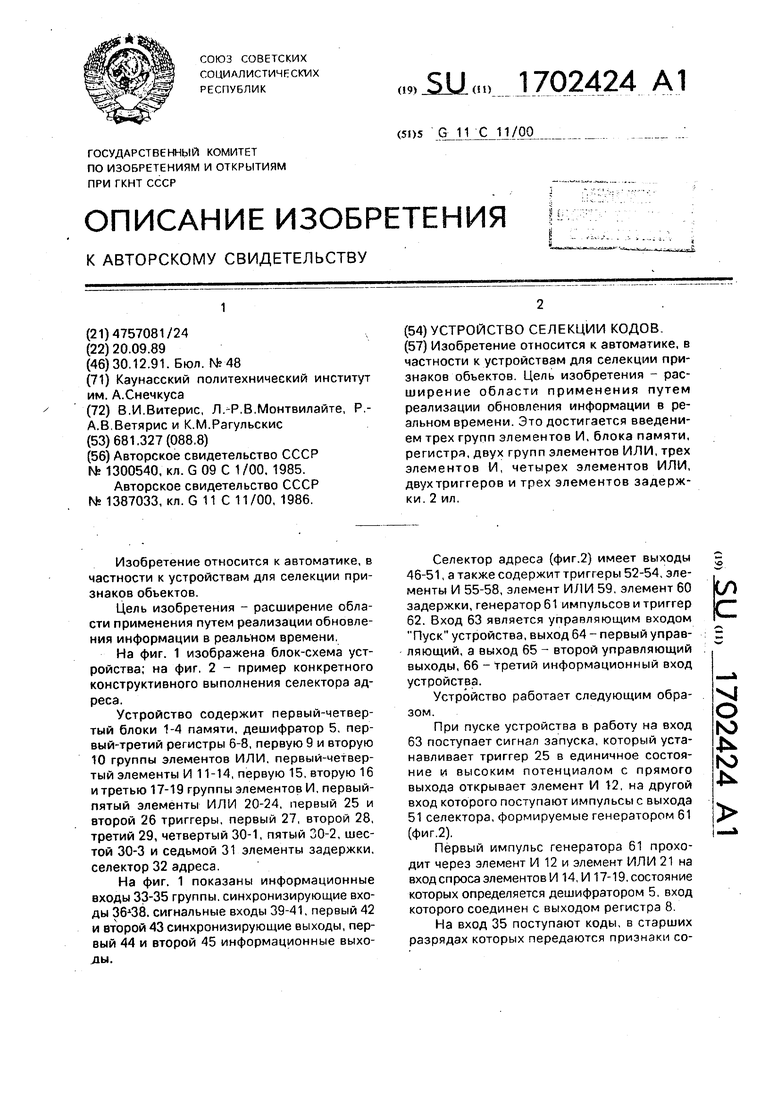

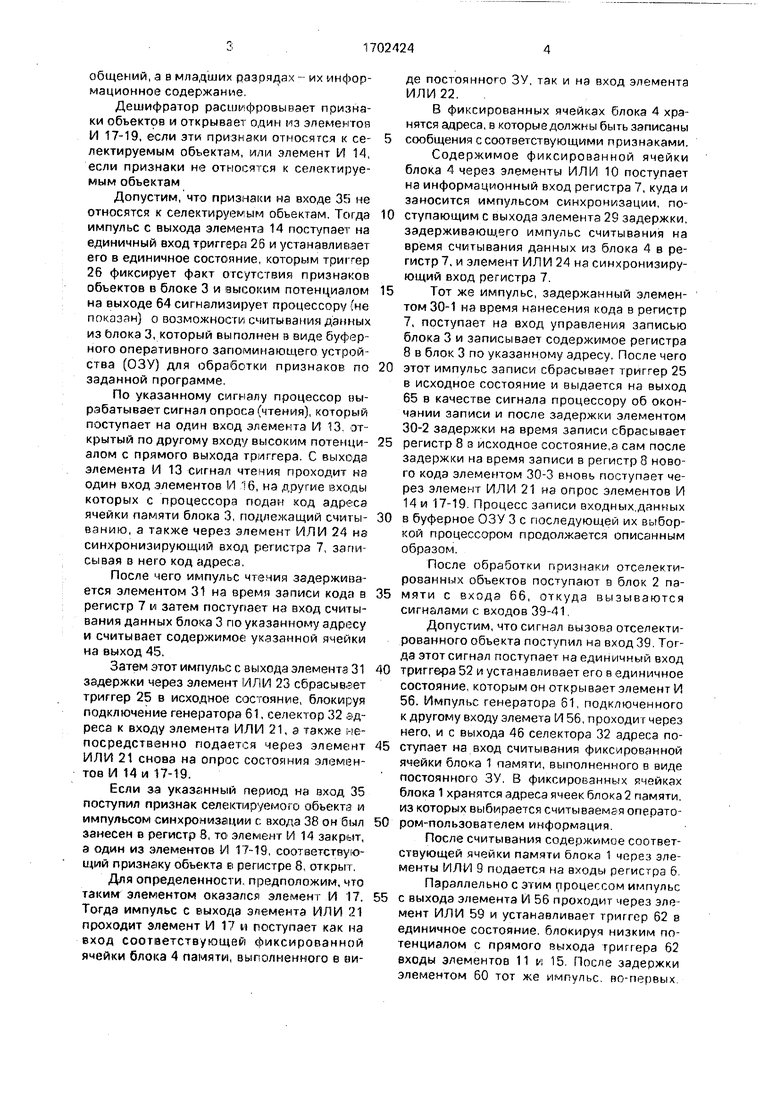

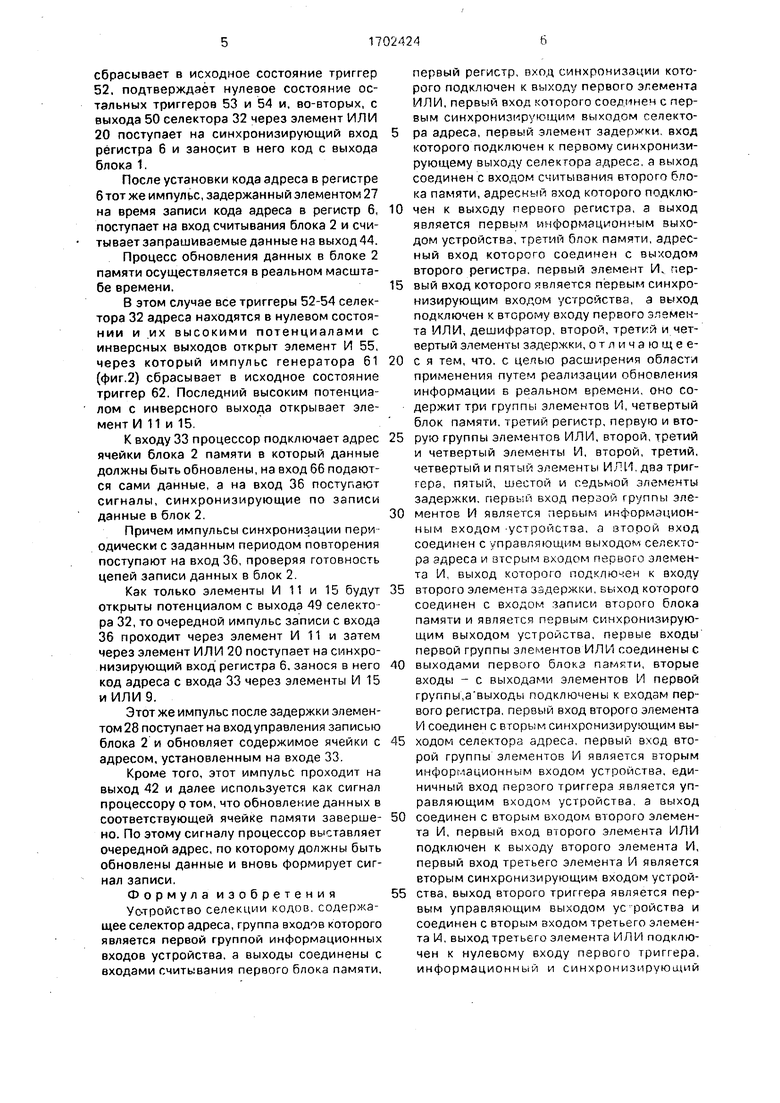

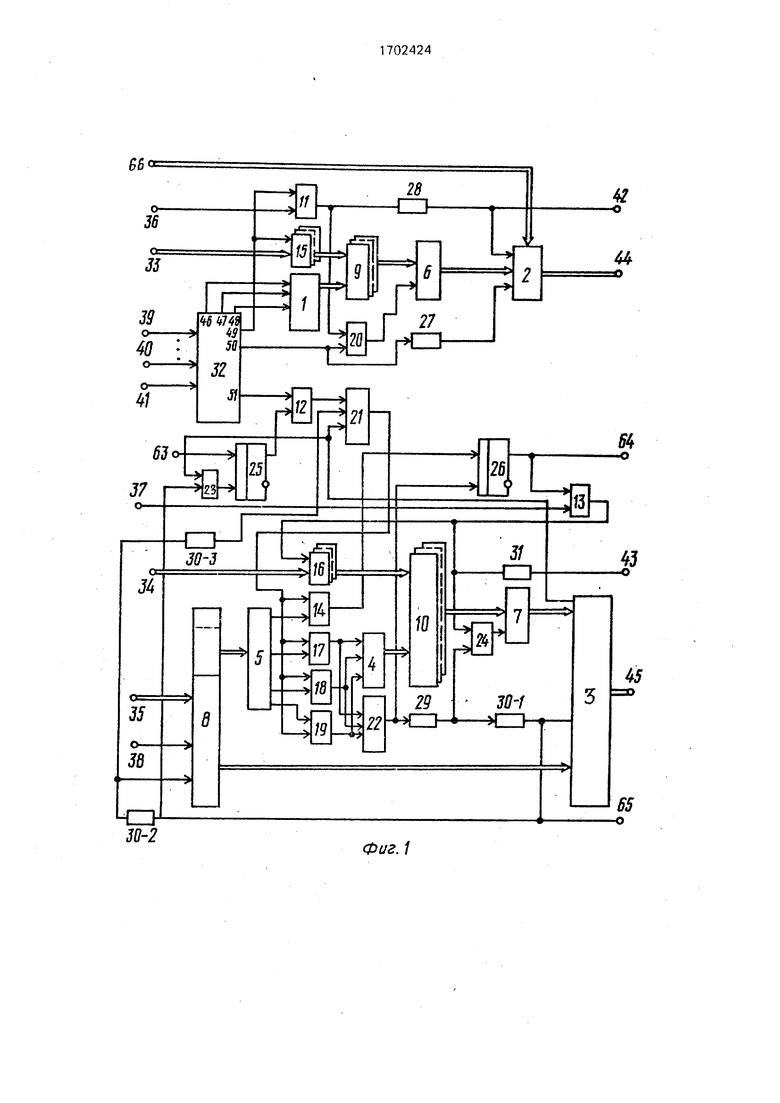

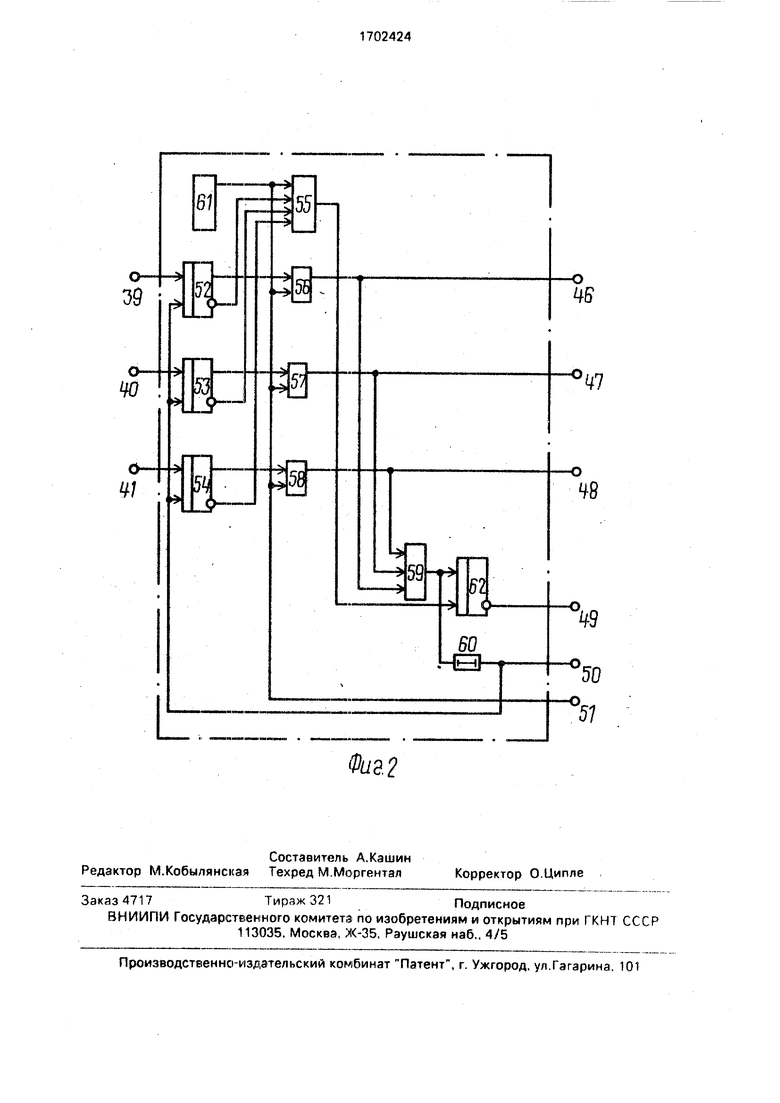

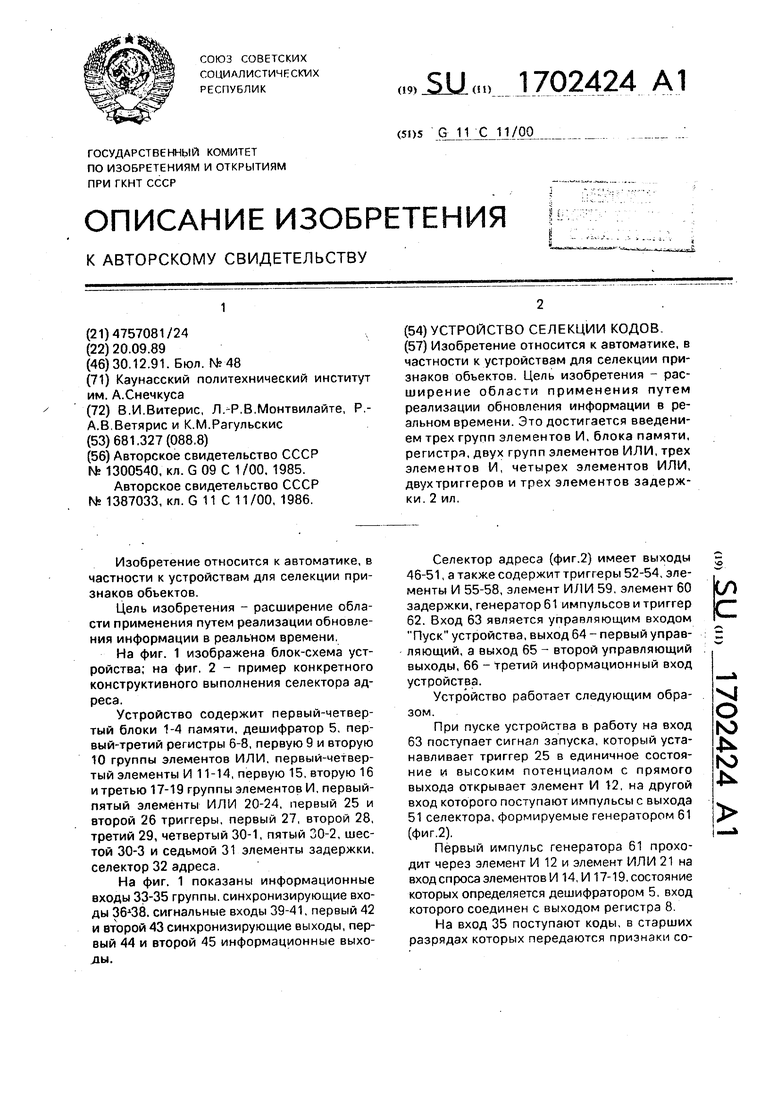

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - пример конкретного конструктивного выполнения селектора адреса.

Устройство содержит первый-четвер- тый блоки 1-4 памяти, дешифратор 5, пер- вый-третий регистры 6-8, первую 9 и вторую 10 группы элементов ИЛИ. первый-четвер- тый элементы И 11-14, первую 15. вторую 16 и третью 17-19 группы элементов И. первый- пятый элементы ИЛИ 20-24. первый 25 и второй 26 триггеры, первый 27, второй 28 третий 29, четвертый 30-1, пятый 30-2, шестой 30-3 и седьмой 31 элементы задержки селектор 32 адреса.

На фиг. 1 показаны информационные входы 33-35 группы, синхронизирующие входы 36J38. сигнальные входы 39-41, первый 42 и второй 43 синхронизирующие выходы, первый 44 и второй 45 информационные выходы.

Селектор адреса (фиг.2) имеет выходы 46-51, а также содержит триггеры 52-54. элементы И 55-58, элемент ИЛИ 59. элемент 60 задержки, генератор 61 импульсов и триггер 62. Вход 63 является управляющим входом Пуск устройства, выход 64 - первый управляющий, а выход 65 - второй управляющий выходы, 66 - третий информационный вход устройства.

Устройство работает следующим образом.

При пуске устройства в работу на вход 63 поступает сигнал запуска, который устанавливает триггер 25 в единичное состояние и высоким потенциалом с прямого выхода открывает элемент И 12, на другой вход которого поступают импульсы с выхода 51 селектора, формируемые генератором 61 (фиг.2).

Первый импульс генератора 61 проходит через элемент И 12 и элемент ИЛИ 21 на вход спроса элементов И 14. И 17-19. состояние которых определяется дешифратором 5. вход которого соединен с выходом регистра 8.

На вход 35 поступают коды, в старших разрядах которых передаются признаки соЁ

VJ

О

ю

ГО

общений, а в младших разрядах - их информационное содержание.

Дешифратор расшифровывает признаки объектов и открывает один из элементов И 17-19, если эти признаки относятся к селектируемым объектам, или элемент И 14, если признаки не относятся к селектируемым объектам

Допустим, что признаки на входе 35 не относятся к селектируемым объектам. Тогда импульс с выхода элемента 14 поступает на единичный вход триггера 26 и устанавливает его в единичное состояние, которым триггер 26 фиксирует факт отсутствия признаков объектов в блоке 3 и высоким потенциалом на выходе 64 сигнализирует процессору (не ) о возможности считывания данных из блока 3, который выполнен в виде буферного оперативного запоминающего устройства (ОЗУ) для обработки признаков по заданной программе.

По указанному сигналу процессор вырабатывает сигнал опроса (чтения), который поступает на один вход элемента И 13, открытый по другому входу высоким потенциалом с прямого выхода триггера. С выхода элемента И 13 сигнал чтения проходит на один вход элементов И 16, на другие входы которых с процессора подан код адреса ячейки памяти блока 3, подлежащий считыванию, а также через элемент ИЛИ 24 на синхронизирующий вход регистра 7, записывая в него код адреса.

После чего импульс чтения задерживается элементом 31 на время записи кода в регистр 7 и затем поступает на вход считывания данных блока 3 по указанному адресу и считывает содержимое указанной ячейки на выход 45.

Затем этот импульс с выхода элемента 31 задержки через элемент ИЛИ 23 сбрасывает триггер 25 в исходное состояние, блокируя подключение генератора 61, селектор 32 адреса к входу элемента ИЛИ 21, а также непосредственно подается через элемент ИЛИ 21 снова на опрос состояния элементов И 14 и 17-19.

Если за указанный период на вход 35 поступил признак селектируемого объекта и импульсом синхронизации с входа 38 он был занесен в регистр 8, то элемент И 14 закрыт, а один из элементов И 17-19, соответствующий признаку объекта в регистре 8, открыт.

Для определенности, предположим, что таким элементом оказался элемент И 17. Тогда импульс с выхода элемента ИЛИ 21 проходит элемент И 17 и поступает как на вход соответствующей фиксированной ячейки блока 4 памяти, выполненного в виде постоянного ЗУ. так и на вход элемента ИЛИ 22.

В фиксированных ячейках блока 4 хранятся адреса, в которые должны быть записаны

сообщения с соответствующими признаками.

Содержимое фиксированной ячейки

блока 4 через элементы ИЛИ 10 поступает

на информационный вход регистра 7, куда и

заносится импульсом синхронизации, по0 ступающим с выхода элемента 29 задержки, задерживающего импульс считывания на время считывания данных из блока 4 в регистр 7, и элемент ИЛИ 24 на синхронизирующий вход регистра 7.

5Тот же импульс, задержанный элементом 30-1 на время нанесения кода в регистр 7, поступает на вход управления записью блока 3 и записывает содержимое регистра 8 в блок 3 по указанному адресу. Посте чего

0 этот импульс записи сбрасывает триггер 25 в исходное состояние и выдается на выход 65 в качестве сигнала процессору об окончании записи и после задержки элементом 30-2 задержки на время записи сбрасывает

5 регистр 8 в исходное состояние,а сам после задержки на время записи в регистр 8 нового кода элементом 30-3 вновь поступает через элемент ИЛИ 21 на опрос элементов И 14 и 17-19. Процесс записи входных данных

0 в буферное ОЗУ 3 с последующей их выборкой процессором продолжается описанным образом.

После обработки признаки отселекти- рованных объектов поступают в блок 2 па5 мяти с входа 66, откуда вызываются сигналами с входов 39-41

Допустим, что сигнал вызова отселекти- рованного объекта поступил на вход 39 Тогда этот сигнал поступает на единичный вход

0 триггера 52 и устанавливает его в единичное состояние, которым он открывает элемент И 56. Импульс генератора 61. подключенного к другому входу элемета И 56. проходит через него, и с выхода 46 селектора 32 адреса по5 ступает на вход считывания фиксированной ячейки блока 1 памяти, выполненного в виде постоянного ЗУ. В фиксированных ячейках блока 1 хранятся адреса ячеек блока 2 памяти, из которых выбирается считываемая оперэто0 ром-пользователем информация

После считывания содержимое соответствующей ячейки памяти блока 1 чорез элементы ИЛИ 9 подается на входы регистра 6 Параллельно с этим процессом импульс

5 с выхода элемента И 56 проходит через элемент ИЛИ 59 и устанавливает триггер 62 в единичное состояние, блокируя низким потенциалом с прямого выхода трипера 62 входы элементов 11 и 15. После задержки элементом 60 тот же импупьс во-первых

сбрасывает в исходное состояние триггер 52, подтверждает нулевое состояние остальных триггеров 53 и 54 и, во-вторых, с выхода 50 селектора 32 через элемент ИЛИ 20 поступает на синхронизирующий вход регистра 6 и заносит в него код с выхода блока 1.

После установки кода адреса в регистре 6 тот же импульс, задержанный элементом 27 на время записи кода адреса в регистр 6, поступает на вход считывания блока 2 и считывает запрашиваемые данные на выход 44.

Процесс обновления данных в блоке 2 памяти осуществляется в реальном масштабе времени.

В этом случае все триггеры 52-54 селектора 32 адреса находятся в нулевом состоянии и их высокими потенциалами с инверсных выходов открыт элемент И 55, через который импульс генератора 61 (фиг.2) сбрасывает в исходное состояние триггер 62. Последний высоким потенциа лом с инверсного выхода открывает элемент И 11 и 15.

К входу 33 процессор подключает адрес ячейки блока 2 памяти в который данные должны быть обновлены, на вход 66 подаются сами данные, а на вход 36 поступают сигналы, синхронизирующие по записи данные в блок 2.

Причем импульсы синхронизации пери одически с заданным периодом повторения поступают на вход 30, проверяя готовность цепей записи данных в блок 2

Как только элементы И 11 и 15 будут открыты потенциалом с выхода 49 селекто ра 32, то очередной импульс записи с входа 36 проходит через элемент И 11 и затем через элемент ИЛИ 20 поступает на синхронизирующий вход регистра 6. занося в него код адреса с входа 33 через элементы И 15 и ИЛИ 9.

Этот же импульс после задержки элементом 28 поступает на вход управления записью блока 2 и обновляет содержимое ячейки с адресом, установленным на входе 33.

Кроме того, этот импульс проходит на выход 42 и далее используется как сигнал процессору о том, что обновление данных в соответствующей ячейке памяти завершено, По этому сигналу процессор выставляет очередной адрес, по которому должны быть обновлены данные и вновь формирует сигнал записи.

Формула изобретения

Ус-тройство селекции ИЛОР одерл а щее селектор адреса, группа входов которого является первой группой информационных входов устройства, а выходы соединены с входами считывания перпого блока памяти

первый регистр, пхоц синхронизации которого подключен к выходу первою элемента ИЛИ, первый вход которси о соединен с первым синхронизирующим выходом -епекто- ра адреса, первый элемент заде ох и вход которого подключен к первому синхронизирующему выходу селектора ргфосг. а выход соединен с входом считывание второго ft пока памяти, адресный вход которого подклю0 чен к выходу первого регистра а выход является первым информационным выходом устройства, третий блок памяти, адресный вход которого соединен с выходом второго регистра, первый элемент И. пер5 вый вход которого является перрым синхронизирующим входом устройства, а выход подключен к второму входу первого элемента ИЛИ, дешифратор, второй третий и четвертый Э Темет ы задержки, о г л и ч а ю щ е е0 с я тем, что, с цепью расширения области применения путем реализации обновления информации в реальном времени оно содержит три группы элементов И. четвертый блок памяти, третий регистр, первую и вто5 рую группы элементов ИЛИ, второй третий и четвертый элементы И, второй, третий, четвертый и пятый элементы ИГИ дна триггера, пяш.1 шестой и г°дьк,пй элементы задержки, верным влод пегкч i группы эле0 ментое И явлчется перьым информационным РХОДОМ устройс па. i ТРОС Ч нход соединен с управляющим селектора адреса s псрым ылодом п-м .jjrr элемента И выход которого HP/V-лю- Сч к входу

5 второго элемента j-здержчи, г.ьход которого соединен с входим записи второю блока памяти и является порг)ым сичтюнизирую- щим выходом устройства, первые входы первой группы элементов ИЛИ соединены с

0 выходами первого блоиэ , вторые входы - с выходами элементов И первой группы.а выходы подключены к гходзм первого регистра, первый вход вгорого элемента И соединен с е горым синхронизирующим вы5 ходом селектора «адреса первый второй группы элементов И является вторым информационным входом устройства, единичный вход первого триггера является управляющим входом /строисгоа а выход

0 соединен с вторым входом вюрого элемента И, первый вход Bioporo элемента ИЛИ подключен к выходу второго элемента И, первый вход трегьегс элемента И является вторым синхронизирующим входом устрой5 ства, выход второю триггера является первым управляющим выходом ус роиства и соединен с вторым входом третье го элемента И, выход третьего элемента ИЛИ подключен к нулевому входу первого триггера, информационный и синхронизирующий

входы третьего регистра являются третьими информационными и синхронизирующими входами устройства, а выходы соединены с входом дешифратора и информационным входом третьего блока памяти, выход которого является вторым информационным выходом устройства, входы четвертого элемента И подключены к выходам дешифратора и второго элемента ИЛИ, а выход соединен с единичным входом второго триггера, входы третьей группы элементов И подключены к выходам дешифратора и второго элемента ИЛИ, входы считывания четвертого блока памяти соединены с выходами соответствующих элементов И третьей группы, первые входы второй группы элементов ИЛИсоеди- нены с выходами четвертого блока памяти, вторые входы - с выходами элементов И второй группы, а выходы подключены к входам второго регистра, входы четвертого элемента ИЛИ соединены с входами элементов И третьей группы, а выход подключен к нулевому входу второго триггера и входу третьего элемента задержки, выход которого соединен с входом четвертого элемента задержки, выход которого является вторым

управляющим выходом устройства и соединен с входом управления записью третьего блока памяти и первым входом третьего элемента ИЛИ, первый вход пятого элемента

ИЛИ подключен к выходу третьего элемента задержки, а выход соединен с синхронизирующим входом второго регистра, вход пятого элемента задержки соединен с выходом четвертого элемента задержки, а

выход подключен к установочному входу третьего регистра, вход шестого элемента задержки соединен с выходом пятого элемента задержки, а выход подключен к второму входу второго элемента ИЛИ, вход

седьмого элемента задержки соединен с выходом третьего элемента И, подключенного к вторым входам пятого элемента ИЛИ и элементов И второй группы, выход седьмого элемента задержки является вторым синхронизирующим выходом устройства и соединен с входом управления третьего блока памяти, вторым входом третьего элемента ИЛИ и третьим входом второго элемента ИЛИ, группа информационных входов второго блока памяти является второй группой информационных входов устройства.

С

W4748 «/ 50

32

-)

27

Г0

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В ИНФОРМАЦИОННОЙ СЕТИ КЛИЕНТ-СЕРВЕР | 2001 |

|

RU2218595C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2276806C1 |

| СИСТЕМА УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В ИНФОРМАЦИОННОЙ СЕТИ ГАС "ВЫБОРЫ" | 2003 |

|

RU2239229C1 |

| УСТРОЙСТВО ДЛЯ РАЗГРАНИЧЕНИЯ ДОСТУПА ПОЛЬЗОВАТЕЛЕЙ К РАЗДЕЛАМ ТЕКСТОВЫХ ДОКУМЕНТОВ | 2001 |

|

RU2239866C2 |

| Устройство для селекции признаков объектов | 1990 |

|

SU1725237A1 |

| Устройство для ввода информации | 1989 |

|

SU1661748A1 |

| СИСТЕМА УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В СЕТИ ИНФОРМАЦИОННО-АНАЛИТИЧЕСКОГО ЦЕНТРА | 2005 |

|

RU2291481C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ПОГРАНИЧНОГО КОНТРОЛЯ | 2006 |

|

RU2316811C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ АВТОМАТИЗИРОВАННОЙ СИСТЕМЫ "ГОСУДАРСТВЕННЫЙ РЕГИСТР НАСЕЛЕНИЯ" | 2003 |

|

RU2246130C2 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫБОРКОЙ И ОБРАБОТКОЙ ДАННЫХ ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2277721C1 |

Изобретение относится к автоматике, в частности к устройствам для селекции признаков объектов. Цель изобретения - расширение области применения путем реализации обновления информации в реальном времени. Это достигается введением трех групп элементов И, блока памяти, регистра, двух групп элементов ИЛИ, трех элементов И, четырех элементов ИЛИ, двух триггеров и трех элементов задержки. 2 ил.

V

Я

12

63 о

37

о-

-Щ-

2J

ULJ

О

J4

/4

/7

/5

JJ

8

/9

ЯМ

64

-о

in

J/ -шь

43

ю

45

J/7-/ С

5У

Фиг. 1

Фиг2

| Устройство для управления вызовом информации | 1985 |

|

SU1300540A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для выборки информации из блока памяти | 1986 |

|

SU1387033A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-12-30—Публикация

1989-09-20—Подача