Изобретение относится к трансляторам импульсно-кодовой модуляции для преобразования входного импульсно-кодо-моду- лированного слова в компандированное импульсно-кодо-модулированное слово, содержащее 3-битовый сегментный код и 4- битовый код ступени.

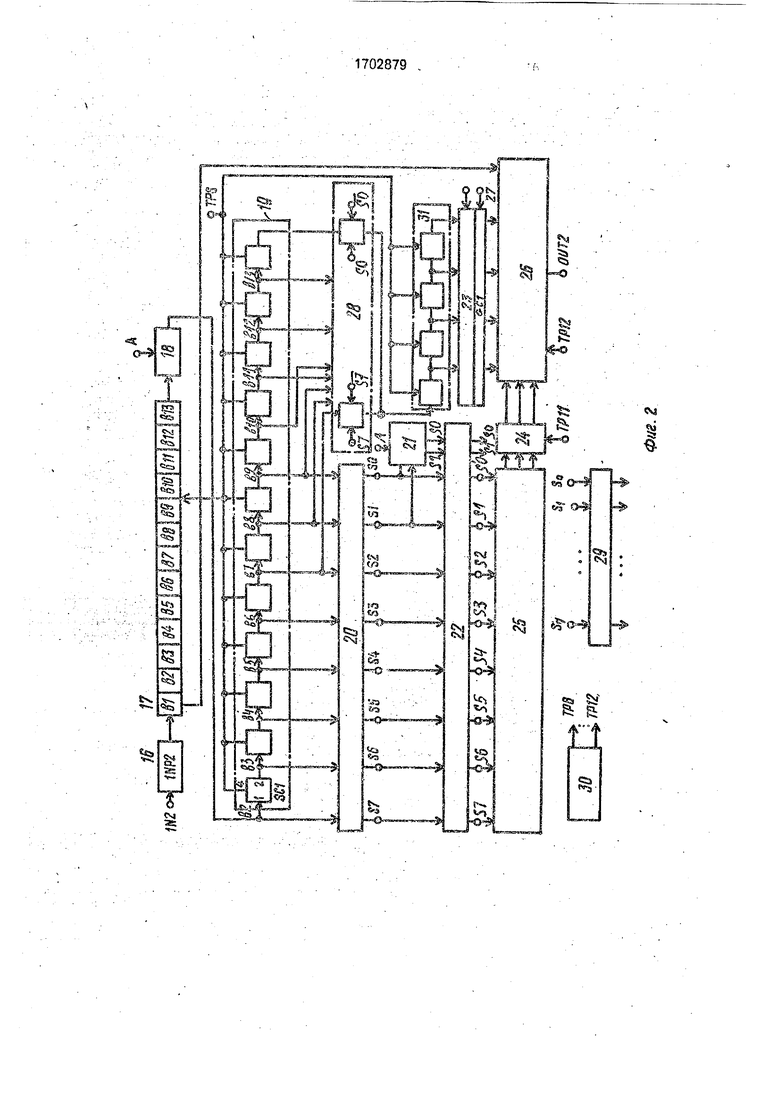

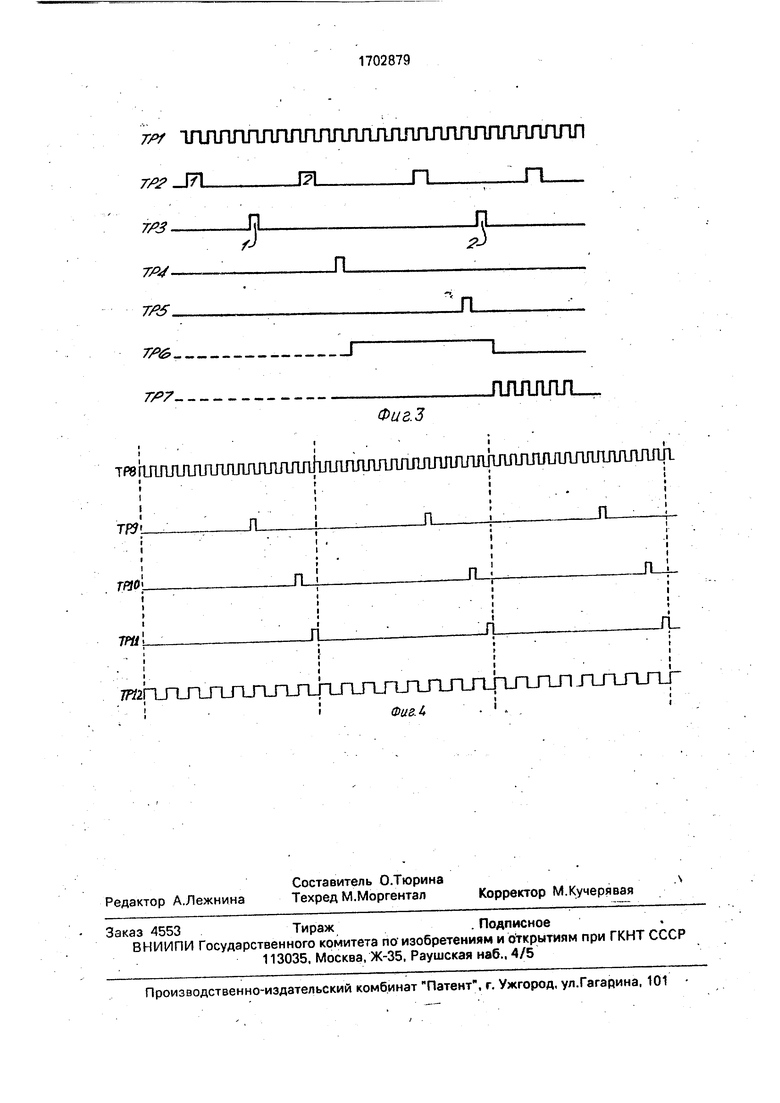

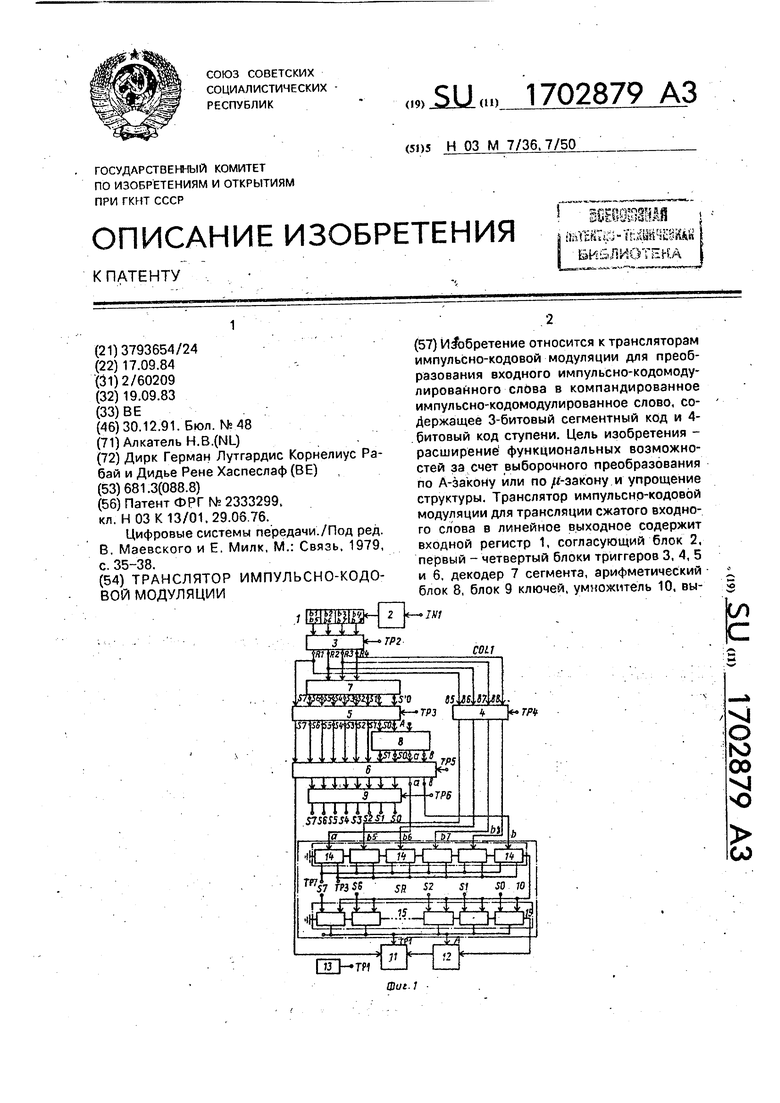

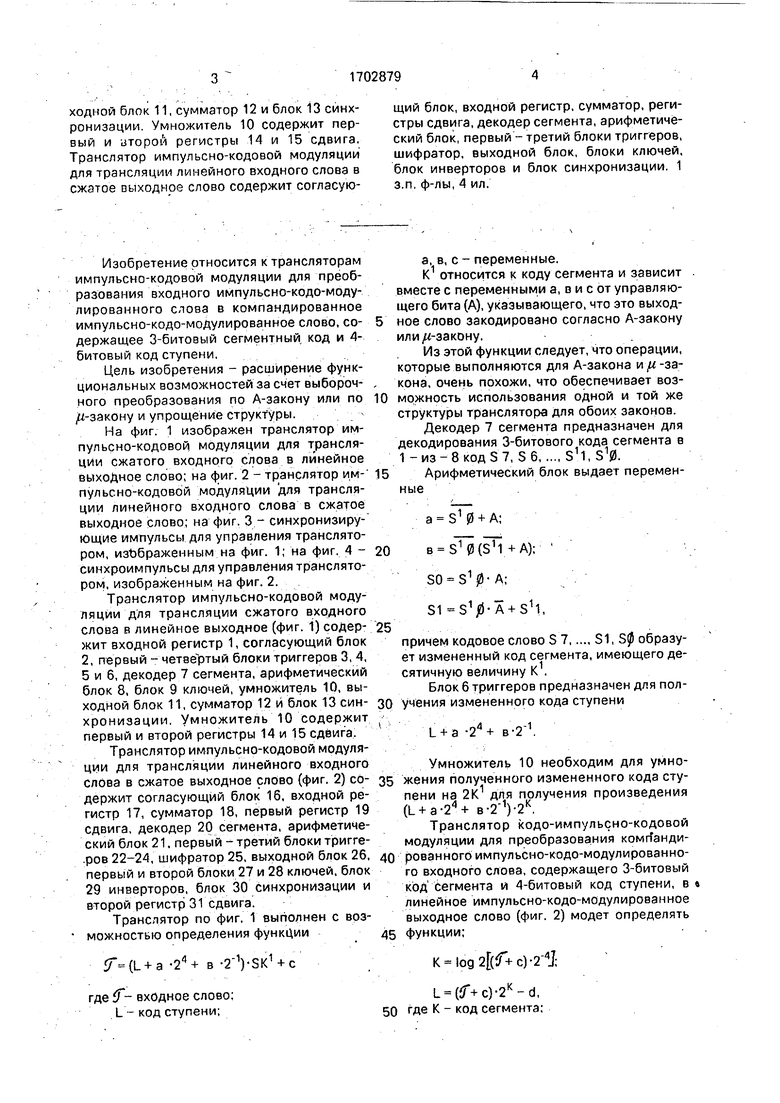

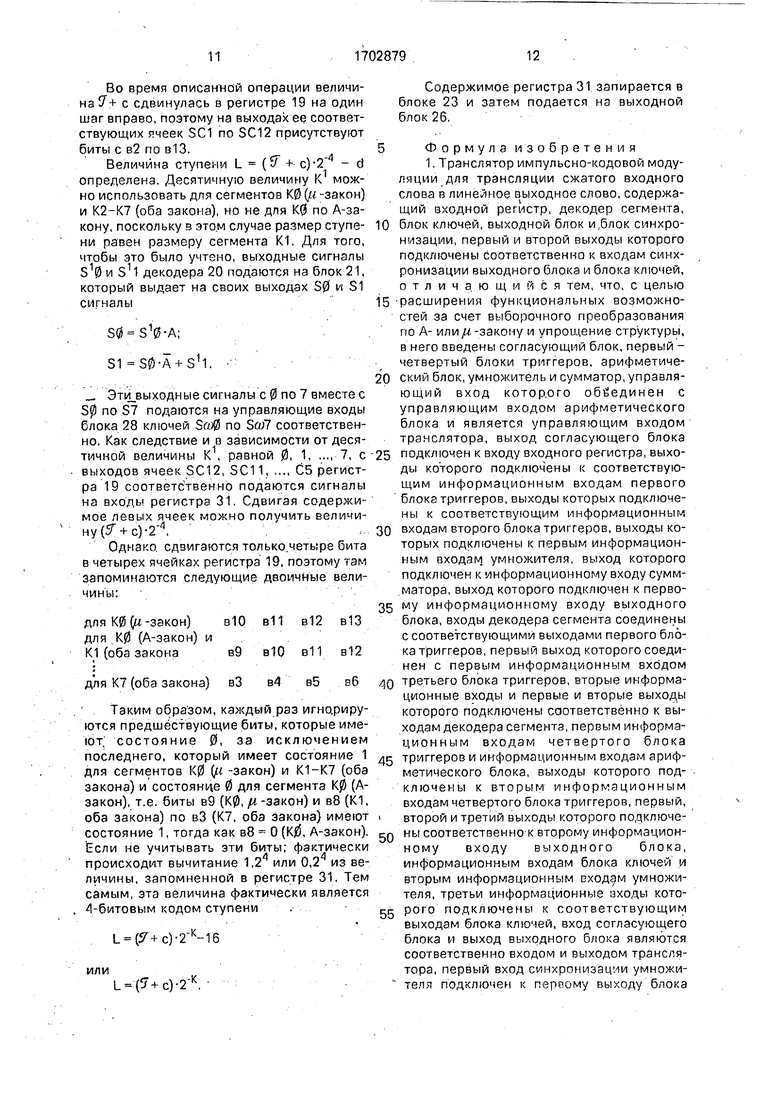

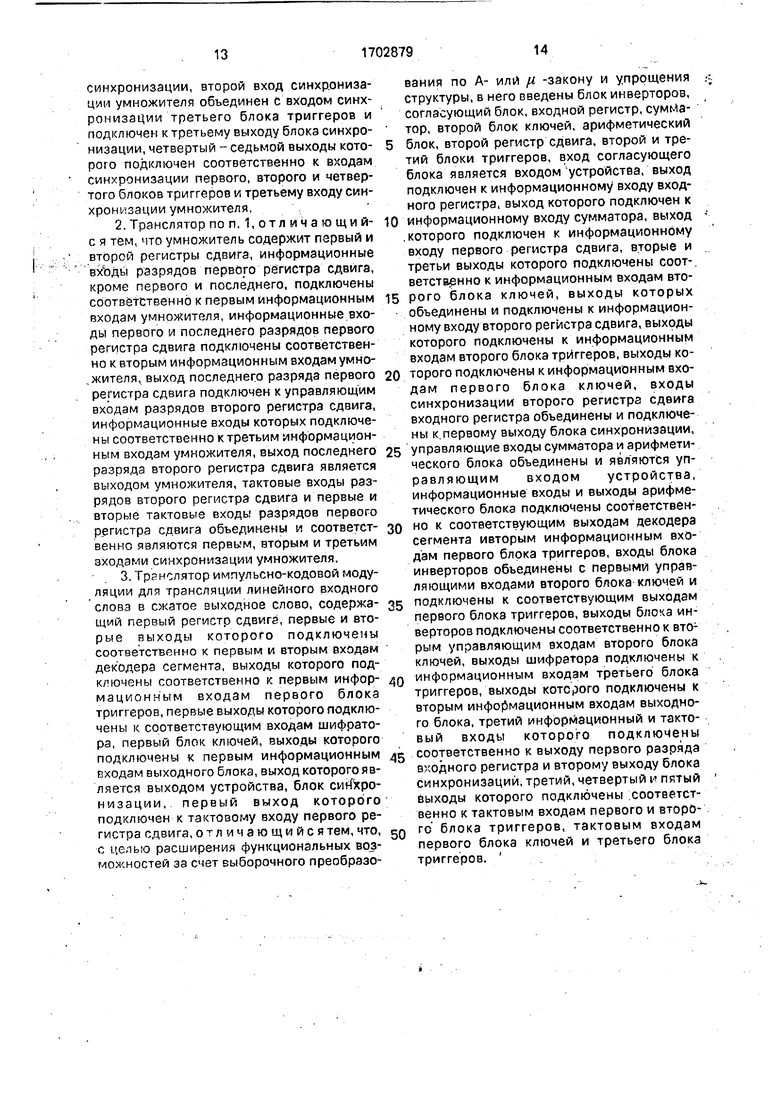

Цель изобретения - расширение функциональных возможностей за счет выборочного преобразования по А-закону или по jU-закону и упрощение структуры.На фиг. 1 изображен транслятор импульсно-кодовой модуляции для трансляции сжатого входного слова в линейное выходное слово; на фиг. 2 - транслятор им- пульсно-кодовой модуляции для трансляции линейного входного слова в сжатое выходное слово; на фиг. 3 - синхронизирующие импульсы для управления транслятором, изЪбраженным на фиг. 1; на фиг. 4 - синхроимпульсы для управления транслятором, изображенным на фиг. 2.

Транслятор импульсно-кодовой модуляции для трансляции сжатого входного слова в линейное выходное (фиг. 1) содержит входной регистр 1, согласующий блок 2, первый - четвёртый блоки триггеров 3, 4, 5 и б, декодер 7 сегмента, арифметический блок 8, блок 9 ключей, умножитель 10, выходной блок 11, сумматор 12 и блок 13 синхронизации, Умножитель 10 содержит первый и второй регистры 14 и 15 сдвига.

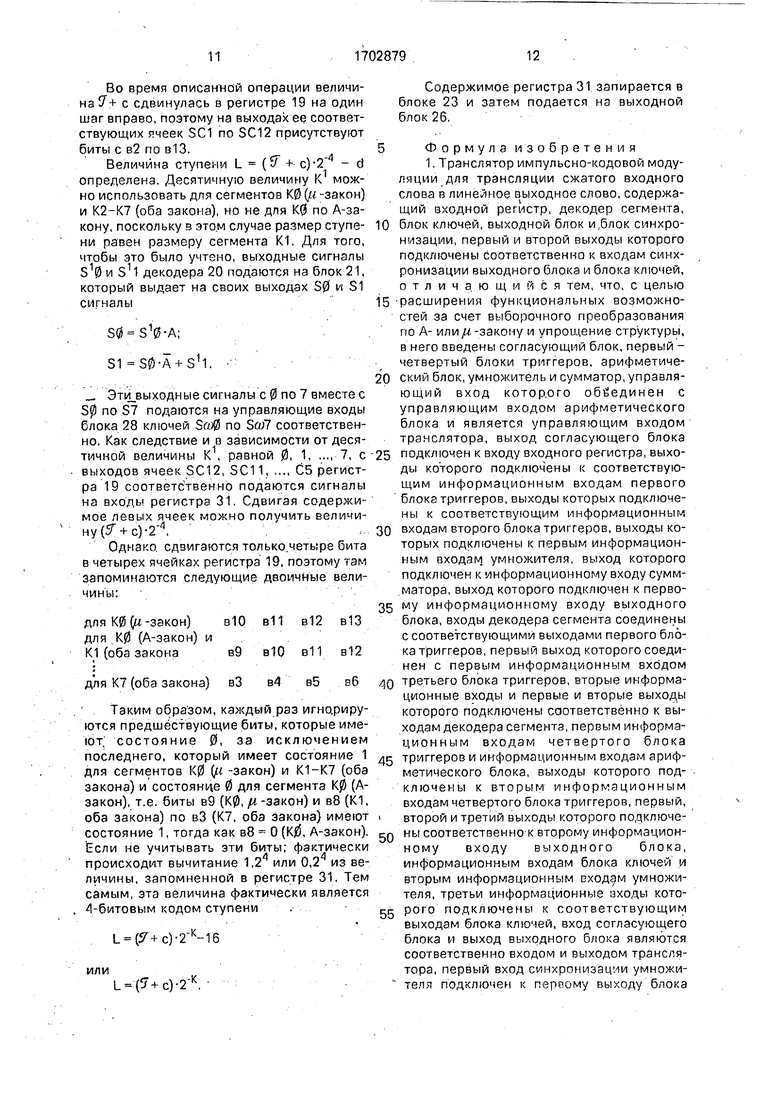

Транслятор импульсно-кодовой модуляции для трансляции линейного входного слова в сжатое выходное слово (фиг, 2) содержит согласующий блок 16, входной регистр 17, сумматор 18, первый регистр 19 сдвига, декодер 20 сегмента, арифметический блок 21, первый третий блоки тригге- .ров 22-24, шифратор 25, выходной блок 26, первый и второй блоки 27 и 28 ключей, блок 29 инверторов, блок 30 синхронизации и второй регистр 31 сдвига.

Транслятор по фиг. 1 выполнен с возможностью определения функции

T(L+a -24+ в )-5К1 + с

где if- входное слово; L - код ступени;

а, в, с - переменные. К1 относится к коду сегмента и зависит . вместе с переменными а, в и с от управляющего бита (А), указывающего, что это выход- ное слово закодировано согласно А-закону или,м-закону.

Из этой функции следует, что операции, которые выполняются для А-закона и/г-за- кона, очень похожи, что обеспечивает воз- можность использования одной и той же структуры транслятора для обоих законов. Декодер 7 сегмента предназначен для декодирования 3-битового кода сегмента в 1 -из-8код87, S6,...,S11,S10. Арифметический блок выдает переменные.

а S1 0 + А;

в S1 0 (ГГП + А); SO S10-А;

S1 S1J0- A + S11,

причем кодовое слово S 7,..., S1, S0 образует измененный код сегмента, имеющего десятичную величину К1.

Блок 6 триггеров предназначен для пол- учения измененного кода ступени

L + a -24+ .

Умножитель 10 необходим для умно- жения полученного измененного кода ступени на 2К для получения произведения 0 + а-24+ )-2к.

Транслятор кодо-импульсно-кодовой модуляции для преобразования комгГанди- рованногб импульсно-кодо-модулированно- го входного слова, содержащего 3-битовый код Сегмента и 4-битовый код ступени, в линейное импульсно-кодо-модулированное выходное слово (фиг. 2) модет определять функции;

K og2(f+c)-2-4J;

L (fT+c)-2K-d, где К - код сегмента;

L-код ступени;

с и d - переменные.

К относится к коду сегмента и зависит так же, как и переменные си d, от управля- ющего бита (А), указывающего, что входное слово закодировано согласно А-закону или согласно -закону.

Транслятор (фиг. 2) содержит сумматор, управляемый управляющим битом А для суммирования переменной с с входным словом для получения измененного входного слова + с и запоминания его в сдвиговом регистре 19, декодер 20, соединенный со сдвиговым регистром 19 для декодирования 8 старших разрядов измененного входного слова7 + с в код 1-из-8, шифратор 25, выдающий переменные:

50 S10-A;

51 S1p-A + S11,

причем кодовое слово имеет десятичную величину К1, арифметический блок 21, блок 28 ключей и регистр 31 сдвига для умножения измененного входного слова Ј/ + с на и суммирования переменной -de полученным произведением для получения кода ступени L.

Умножитель 10 необходим для умножения двоичного слова, хранящегося в первом сдвиговом регистре 14 на 2х, где х 0, ..., К, сдвигая это слово через х ступеней этого сдвигового регистра.

Кодо-импульсно-модулированный сигнал закодирован согласно сегментированному логарифмическому А-закону или ,и-закону, каждый из которых содержит 8 сегментов для каждой из величин знака S закодированного битом в1. Три бита в2-в4 определяют один сегмент К среди 8 возможных сегментов Кб, ..., К7, а биты в5 - в8 определяют одну ступень L среди 16 воз- можных равных ступеней в сегменте. Согласно /г -закону относительные величины размеров ступеней в сегментах К0, ..., К7 равны 2°,..., 27 соответственно, тогда как по А-закону они равны соответственно 2,2,2 , .,., 2 . Это значит, что размер ступени в сегменте К0 по закону А вдвое больше размера ступени в сегменте Щ по закону/4. Компэн- дирОЕЭнный кодо-импульсно модулированный сигнал , например, принимается и передается в такой форме, где все биты, за исключением знакового, инвертированы (а-закон) или где только четные биты инвертированы (А-закон).. .

Можно показать, что соответствующий алгоритм для транскодировакия 8-битового

5

10 15

0

компандированного кодо-импульсно-моду- лированного слова, содержащего биты в1- в8 со знаковым битом S в1, сегментным кодом К в2вЗв4 и кодом ступени L в5, вб, в7, в8 в 13-битовое линейное кодо-импульс- но-модулировзнное слово определяется по формуле

ЈT 2K(L + a-24 + в-2 1) + с или

,

где с 0 для А-закона и с -16 для ,«-ззкона;

К1 0 - 7 для сегментов К0 - К7, за исключением сегмента Кф по А-закону, величина которого равна 1, а не 0;

а в 1 для сегментов К2 - К7 для обоих законов и для К1 по//-закону, поэтому

(L + 24 + 21);

-а 1 и в 0 для сегмента К$ (и -закон) и К1 (А-закон), поэтому

+ 24);

-а в 0, а К1 1 для сегмента К0 (А-закон), поэтому

Транслятор по фиг. 1 может вычислять этот алгоритм следующим образом,

Компандированный кодо-импульсно- модулированный сигнал, подаваемый,на вход блока 2, причем самый старший бит идет первым и трансформируется в согласу- ющем блоке 2, и пoлyчe чый 8-битовый ком- пандированный сигнал, содержащий биты в1 - в8 (фиг/ 1) и определяющий S, К и L, последовательно вводится в регистр 1 двумя последовательными пакетами по четыре бита в1 - в4 и в5 - в8.

Четыре бита в1 - в4 запираются в блоке 3 триггеров под управлением первого синхронизирующего импульса ТР2 (фиг. 3). Бит „знака S в1 подается в выходной блок 11, тогда как 3-битовый сегментный код К в2 -вЗ в4 подается на сегментный декодер, где декодируется в 1-из-8-сегментный код, образованный битами:

S7,-S6,/S5, S4.S3, S2.S1.S0

на одноименных выходах декодера 7, Этот код определяет сегменты Kj3 по К7 следующим образом:

76 54 3 2 1 о Десятичное, значе . j К

К(Э0 .000; :0И0 1#

К10Ч 0бИ0И1 DV V

К71.00.. 0ра# 0i 7

Таким образом, каждый из выходов S1j0, S11. ..., S7 декодера 7 активируется для соответствующего одного из сегментов К0, К1, К2, ,,., К7 и для этих сегментов выделены десятичные величины К1 0, 2, .... G, 7. Однако, согласно вышеприведенному алгорит: му это неправильно для сегмента Kj3 по закону А поскольку величина К должна быть равна Та нё$.

Под управлением синхронизирующего импульса ТРЗ бит в1 и выходной код S10, S11, .,., S7 декодера 7 запирается в блоке 3 триггеров так, что бит в1 и S2-S7 подаются на блок 6 триггеров, тогда кгк биты S 0 и S1 подаются на арифметический блок 8, который используется для вычислений величин а и в и для вычисления правильной величины К для сегмента К0 по закону А. На своих- выходах а, в, S0 и S1 блок 8 создает одноименные сигналы: :л/ . ,

- .. /

a S10-(-A; ,. /- л : .

V V .: . . ...,.,

B S10(S11 +A): -.. . . ..

S0-S10;A; . , v .

S1 SVA + S4.

Из этих отношений следует, что как тре- бует вышеуказзнный алгоритм: а в 1 для сегментов К2-К7 по обоим законам А и /и, отличающимся тем, что А 0 и А 1 соответственно. :

а 1 и в.- О для сегмента К0 (w -закон) и К1 (А - закон); а в 0 для сегмента К0 (А-закон), поэтому приведенные выше сегментные коды меняются,и дают следующие измененные сегментные коды:

S7S6S5S4S352S1S0

К0Чи) - яу#уasл 1 :

К0(А)пК1 t Яд .Э-IS1ff

К7 . 1ST& в-Ув&Я . :

.- Таким образом, десятичной величине К1 1 придано К0 по А-закону, что и требуется,

Второй пакет битов в5 вб в7 в8, определяющий код ступени L, вводится в регистр 1. Эти биты запираются в блоке 3 под управлением второго синхронизирующего импульса ТР2 и после этого запираются в

блоке 4 синхронизирующим импульсом ТР4. Вследствие этого, эти биты в5-в8 подаются на информационные входы умножителя 10..

Под воздействием последующего синхронизирующего импульса ТР5 биты в{, 0, 31, S2-S7, а также а, в на выходах блока 3 и блока 8 запираются в блоке 6 триггеров, в результате чего бит в1 подается на блок 11,

S-биты подаются на блок 9 ключей и биты а

и в подаются на информационные входы

умножителя 10. Измененный код ступени,

образованный битами а, в5, вб, в7, в8 и в,

теперь вводится в регистр 14 под управлениём синхронизирующего импульса ТРС, инвертируется в этой цепи и подается на выходы ячеек этого регистра. Таким обра- зом,на (зыходах регистра 14 присутствует,

в5, вб, в7, в8 и в.

Так, измененный код ступени

L + a

.24 +

т1

с инвертированными разрядами запоминается в ячейках РСТ по РС6 регистра 14, которым даны величины с 24 по соответственно. Как следует из алгоритма, эту величину теперь следует умножить на 2К для того, чтобы получить величину5г.

Посредством отрицательно направленного синхронизирующего импульса ТРб также биты S0, S1 и S2-SJ, подаются на управляющие входы соответствующих ячеек РС11 по РС18 регистра .15. Таким образо.м устанавливается соединение между выходом регистра 14 и вторым выходом ячейки РС11 регистра 15 через числ.о ячеек, равное величине К1.

Под управлением шести синхронизм-

рующих импульсов ТР7, поданных на управляющий вход регистра 14, и синхронизирующих импульсов ТР1, подан- ных на упр авляюш,ий вход регистра 15, биты в, в8, в7, вб, в5 и а сдвигаются по последовательно соединенным ячейкам регистров 14 и 15 и в .первой используемой ячейке регистра 15 происходит инвертирование. Таким образом, величина, запомненная в регистре 14 инвертируется и умножается на

множитель, равный 2 , поэтому на выходе регистра 15 появляется двоичное число ,

Согласно указанному алгоритму для

получения желаемой величины ЈГ к величине необходммо прибавить величинус 0для

А-закона, либо величину С -16 -закона. Это выполняется сумматором 12, который управляется тем же управляющим входом А, что и блок 8. После этого, результат и бит знака ц объединяются в выходном блоке 11 и;

рансформируются перед подачей на выод.

На фиг. 2 показан транслятор, выполненный с возможностью транскоди- рования 13-битового линейного 5 кодо-импульсно-модулированного слова в 8-битовое компандированное кодо-импульсно-модулированное слово.

Соответствующий алгоритм для транскодирования 13-битового линейного кодо- 10 импульсно-модулйрова иного слова, содержащего разряды с в1 по в13, где бит знака s в1, а величина 1Гопределена битами с в2 по в13, в 8-битовое компандированное кодо-импульсно-модулированное слово со знаковым/битом S, сегментом К и сту- пенью задается посредством

К log2 ( с) -2 4 L (tT+c)-2 K-d,

ь

где с 0 для А-закона;

с 16 для// -закона;

и при К от 0 до 7 и d 16 сегментов с Щ по 25 К7, за исключением сегмента КО для А-закона, для которого эта величина равна 1. а не (5, и для которого также d 0. Для К вычисляется нижний предел.

Транслятор (фиг. 2) может вычислять 30 этот алгоритм следующим образом.

Линейное кодо-импульсно-модулированное слово подается на вход блока 16, причем младший бит подается первым и трансформируется в согласующем блоке 16, 35 а полученное 13-битовое линейное кодо- импульсно-модулированное слово, содержащее биты с в1 по в13 со знаковым битом S в1 и величиной5 в2, ..., в13, запоминается в регистре 17. Знаковый бит в1 пода- 40 ется на выходной блок26, а битые в2 по в13, определяющие величину 3 , последовательно вводятся в регистр 19 под воздействием синхронизирующих импульсов ТР8 и проходят чер ез сумматор 18, в котором к 45 величине У прибавляется с 0 или с 16, в зависимости от преобразования по А-за- кону или JLI -закону (что задается управляющим входом А). Таким образом, слово, запомненное в регистре 19, представляет 50 собой измененное входное слово + с. Поскольку бит в13 является младшим битом и имеет весовую функцию 2 , восемь битов в2 - в9 определяют величину ( + с)%2 .которая теперь используется для определения55

15

20

K log2(7+c) .

. Это делается путем определения только наивысшей степени для 2. в выражении (17+ с) . Наивысшая степень определяет нижний предел сегмента.

С этой целью входы с в2 по в9 ячеек SC1 по SC8 регистра 19 соединяются с декодером 20 сегмента, который трансформирует следующие 8-битовые двоичные входные коды:

10

15

где X имеет произвольную величину, в сле- 20 дующие 1-ИЗ-8 сегментные коды, появляющиеся на одноименных выходах декодера 20:

Декодер 20, например, содержит множество тактированных вентилей И, определяющих булеву функцию в2; в2.вЗ; в2в3.в4; ...в 2вЗв4в5в6в7в8. Выход каждого из этих вентилей соединен с соответствующим одним из выходов S7, .... S непосредственно и через блок 29 инерторов с остальными.

Эти последние выходные клеммы S 0, S11,.... S7 декодера 20 связаны с соответствующими сегментами K(f, К1,.... К7, которым придаются указанные десятичные величины

Декодер 20 фактически определяет первую 1. в последовательности разрядов в2- в9, за исключением К0, и игнорирует последующие двоичные величины в этой последовательности. Это означает, что она определяет наивысшие ступени для 2 и не учитываеть более низкие степени. Поэтому каждый из сегментов определяется по его нижнему пределу. К.0 определяется, если все биты в2-в8 являются 0, независимо от в9, поскольку есть уверенность, что речь идет о сегменте 0.

Упомянутые выходы S 0, S 1,..., S7 подаются н-а блок 22 триггеров и оттуда на шифратор 25, который транслирует 1-из-8 сегментные коды в 3-битные сегментные коды, которые подаются через блок 24 триггеров на выходной блок 26.

Во время описанной операции величина У+ с сдвинулась в регистре 19 на один шаг вправо, поэтому на выходах ее соответствующих ячеек SCI no SC12 присутствуют биты с в2 по в13.

Величина ступени L (5 + с)-2 - d определена. Десятичную величину К можно использовать для сегментов К0 (/.I -закон) и К2-К7 (оба закона), но не для К0 по А-за- кону, поскольку в этом случае размер ступени равен размеру сегмента К1. Для того, чтобы это было учтено, выходные сигналы S10 и 311 декодера 20 подаются на блок 21, который выдает на своих выходах S0 и S1 сигналы

50 S10-A;.

51 S0-A + S11. ,

Эти выходные сигналы с 0 по 7 вместе с S$ no S7 подаются на управляющие входы блока 28 ключей Sft)0 no Soft соответственно. Как следствие и в зависимости от десятичной величины К1, равной 0, 1, ..,,7, с

выходов ячеек SC12, SC11, ,.., С5 регистра 19 соответственно подаются сигналы на входы регистра 31, Сдвигая содержимое левых ячеек можно получить величину(5 + с)-2.. ,..

Однако, сдвигаются только.четыре бита

в четырех ячейках регистра 19, поэтому там

запоминаются следующие двоичные величины: для К0 (и-закон)в10

для ,К0 (А-закон)и

К1 (оба законав9

для К7 (оба закона) вЗ в4 в5 вб

Таким обра зом, каждый раз игнорируются предшествующие биты, которые имеют. состояние 0, за исключением последнего, который имеет состояние 1 для сегментов К0 (и -закон) и К1-К7 (оба закона) и состояние 0 для сегмента К0 (А- закон), т.е. биты в9 (К0, 4 -закон) и в8 (К1, оба закона) по вЗ (К7, оба закона) имеют состояние 1, тогда как в8 О (К$, А-закон). Если не учитывать эти биты; фактически происходит вычитание 1,2 или 0,2 из величины, запомненной в регистре 31. Тем самым, эта величина фактически является 4-битовым кодом ступени .

-к

1.-(У+с)

или

L (54c)-2

-К

Содержимое регистра 31 запирается в блоке 23 и затем подается на выходной блок 26.

Формула из обретения

1. Транслятор импульсно-кодовой модуляции для трансляции сжатого входного слова в линейное выходное слово, содержащий входной регистр, декодер сегмента,

блок ключей, выходной блок и,блок синхронизации, первый и второй выходы которого подключены соответственно к входам синхронизации выходного блока и блока ключей, отличающийся тем, что, с целью

расширения функциональных возможностей за счет выборочного преобразования по А- -закону и упрощение структуры, в него введены согласующий блок, первый - четвертый блоки триггеров, арифметический блок, умножитель и сумматор, управляющий вход которого объединен с управляющим входом арифметического блока и является управляющим входом транслятора, выход согласующего блока

подключен к входу входного регистра, выходы которого подключены к соответствующим информационным входам первого блока триггеров, выходы которых подключены к соответствующим информационным

входам второго блока триггеров, выходы которых подключены к первым информационным входам, умножителя, выход которого подключен к информационному входу сумм- матора, выход которого подключен к первому информационному входу выходного блока, входы декодера сегмента соединены с соответствующими выходами первого блока триггеров, первый выход которого соединен с первым информационным входом

третьего блока триггеров, вторые информационные входы и первые и вторые выходы которого подключены соответственно к выходам декодера сегмента, первым информа- ционным входам четвертого блока

триггеров и информационным входам арифметического блока, выходы которого подключены к вторым информационным входам четвертого блока триггеров, первый,

второй и третий выходы которого подключены соответственно к второму информационному входу выходного блока, информационным входам блока ключей и вторым информационным входам умножителя, третьи информационные аходы которого подключены к соответствующим выходам блока ключей, вход согласующего блока и выход выходного блока являются соответственно входом и выходом транслятора, первый вход синхронизации умножи- теля подключен к первому выходу блока

синхронизации, второй вход синхронизации умножителя объединен с входом синхронизации третьего блока триггеров и подключен к третьему выходу блока синхро- низации, четвертый - седьмой выходы кото- рого подключен соответственно к входам синхронизации первого, второго и четвертого блоков триггеров и третьему входу синхронизации умножителя,.

2. Транслятор по п. 1, отл ич а ю щи й- с я тем, что умножитель содержит первый и второй регистры сдвига, информационные вхЪды разрядов первого регистра сдвига, кроме первого и последнего, подключены соответственно к первым информационным входам умножителя, информационные входы первого и последнего разрядов первого регистра сдвига подключены соответственно к вторым информационным входам умно- , жителя, выход последнего разряда первого регистра сдвига подключен к управляющим входам разрядов второго регистра сдвига, информационные входы которых подключены соответственно к третьим информационным входам умножителя, выход последнего разряда второго регистра сдвига является выходом умножителя, тактовые входы разрядов второго регистра сдвига и первые и вторые тактовые входы разрядов первого регистра сдвига объединены и соответст- венно являются первым, вторым и третьим входами синхронизации умножителя.

3. Транслятор импульсно-кодовой модуляции для трансляции линейного входного слова в сжатое выходное слово, содержа- щий первый регистр сдвига, первые и вторые выходы которого подключены соответственно к первым и вторым входам декодера сегмента, выходы которого подключены соответственно к первым инфор- мационным входам первого блока триггеров, первые выходы которого подключены к соответствующим входам шифратора, первый блок ключей, выходы которого подключены к первым информационным сходам выходного блока, выход которого является выходом устройства, блок синхронизации, первый выход которого подключен к тактовому входу первого регистра сдвига, отличающийся тем, что, с целью расширения функциональных возможностей за счет выборочного преобразования по А- или fi -закону и упрощения структуры, в него введены блок инверторов, согласующий блок, входной регистр, сумматор, второй блок ключей, арифметический блок, второй регистр сдвига, второй и третий блоки триггеров, вход согласующего блока является входом устройства, выход подключен к информационному входу входного регистра, выход которого подключен к информационному входу сумматора, выход .которого подключен к информационнбму входу первого регистра сдвига, вторые и третьи выходы которого подключены соот-. ветств нно к информационным входам второго блока ключей, выходы которых объединены и подключены к информационному входу второго регистра сдвига, выходы которого подключены к информационным входам второго блока триггеров, выходы которого подключены к информационным входам первого блока ключей, входы синхронизации второго регистра сдвига входного регистра объединены и подключены к. первому выходу блока синхронизации, управляющие входы сумматора и арифметического блока объединены и являются управляющим входом устройства, информационные входы и выходы арифметического блока подключены соответственно к соответствующим выходам декодера сегмента ивторым информационным входам первого блока триггеров, входы блока инверторов объединены с первыми управляющими входами второго блока ключей и подключены к соответствующим выходам первого блока триггеров, выходы блока инверторов подключены соответственно к вто1 рым управляющим входам второго блока ключей, выходы шифратора подключены к информационным входам третьего блока триггеров, выходы которого подключены к вторым информационным входам выходного блока, третий информационный и тактовый входы которого подключены соответственно к выходу первого разряда входного регистра и второму выходу блока синхронизации, третий, четвертый и пятый выходы которого подключены .соответственно к тактовым входам первого и второго блока триггеров, тактовым входам первого блока ключей и третьего блока триггеров.

шо

К

з:

1JS

J J . .

к

er

%

с- «5.

SWr.yf.MUi ,S-W ieiWC(ei

°Ґwl Ф га.. к

is

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| Устройство для обмена информацией между абонентами телефонной сети | 1978 |

|

SU1482540A3 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| СПОСОБ ЗАПИСИ ЦИФРОВОЙ ИНФОРМАЦИИ НА НОСИТЕЛЕ И УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ С НОСИТЕЛЯ ЗАПИСИ | 1991 |

|

RU2037888C1 |

| ДЕШИФРАТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2089045C1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для определения достоверности цифровой информации | 1989 |

|

SU1674211A2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ЗАЩИТОЙ ОТ ОШИБОК, СПОСОБ ПРИЕМА ИНФОРМАЦИИ С ЗАЩИТОЙ ОТ ОШИБОК И ПЕРЕДАЮЩАЯ СИСТЕМА ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ | 1996 |

|

RU2186459C2 |

| ТРАССИРОВОЧНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ КОММУТАЦИОННОГО ЭЛЕМЕНТА | 1991 |

|

RU2105424C1 |

И&бретение относится к трансляторам импульсно-кодовой модуляции для преобразования входного импульсно-кодомоду- лированного слова в компандированное импульсно-кодомодулированное слово, со- Держащее 3-битовый сегментный код и 4- . битовый код ступени. Цель изобретения - расширение функциональных возможностей за счет выборочного преобразования по А-закону или по / -закону и упрощение структуры. Транслятор импульсно-кодовой модуляции для трансляции сжатого входного слова в линейное выходное содержит входной регистр 1, согласующий блок 2, первый - четвертый блоки триггеров 3, 4, 5 и 6, декодер 7 сегмента, арифметический блок 8, блок 9 ключей, умножитель 10, вы-.ш ТР2

О)

г со см о гjЈ2 J Јj; g V J.

К«гм

/

TPf 1ЛЛПЛЛЛГиТЛЛ11Г1ШШ

J2

TP7.

тге шпгшшяштги

JK

А

mo

л

ТРИ

Л

TranjnjijTJTjajTJ JiJ

n

ЛЛШ1ШТ

Фиг.З

JL

JI

Л

л

R

| УСТРОЙСТВО ДЛЯ МИКРОДУГОВОГО ОКСИДИРОВАНИЯ МЕТАЛЛОВ И ИХ СПЛАВОВ | 2007 |

|

RU2333299C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Солесос | 1922 |

|

SU29A1 |

| Цифровые системы передачи./Под ред | |||

| В, Мэевского и Е | |||

| Милк, М.: Связь, 1979, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

Авторы

Даты

1991-12-30—Публикация

1984-09-17—Подача