Изобретение относится к цифровым системам передачи информации и может быть использовано для оперативного контроля достоверности передаваемой информации и состояния канала передачи, например, в радиотелеметрии, и является усовершенствованием известного устройства по авт. ев № 1368905

Цель изобретения - повышение точности работы устройства за счет обнаружения ошибок во всем непрерывно передаваемом потоке цифровой информации

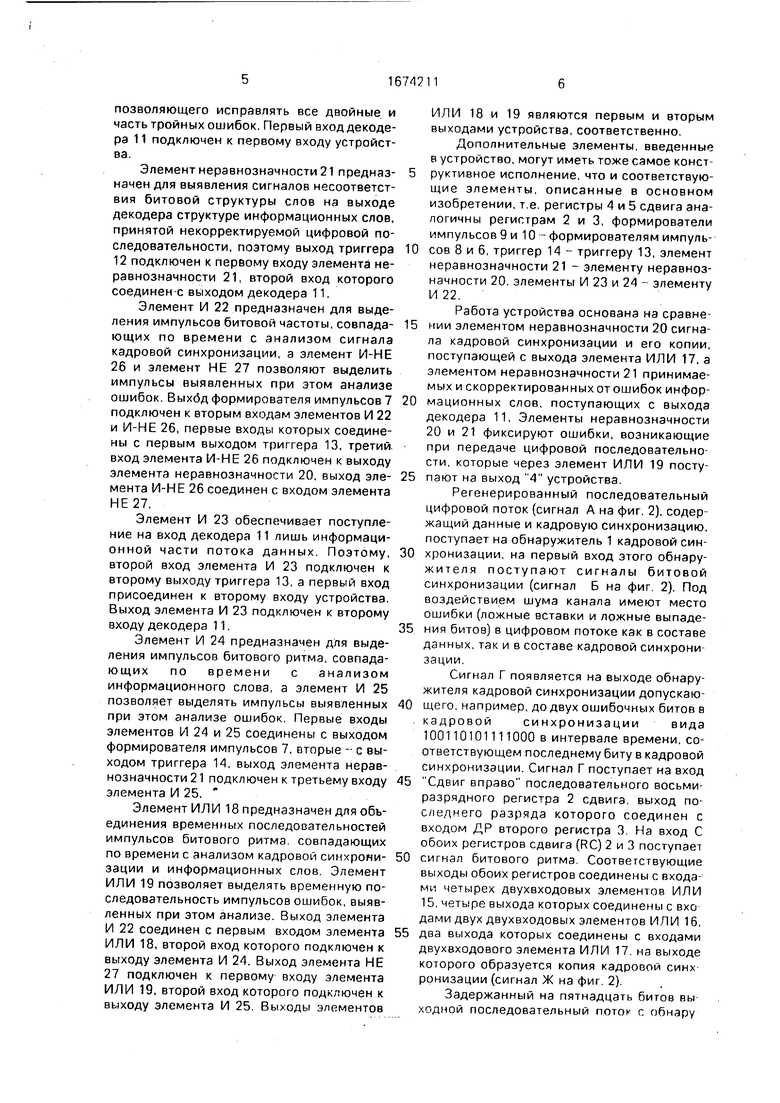

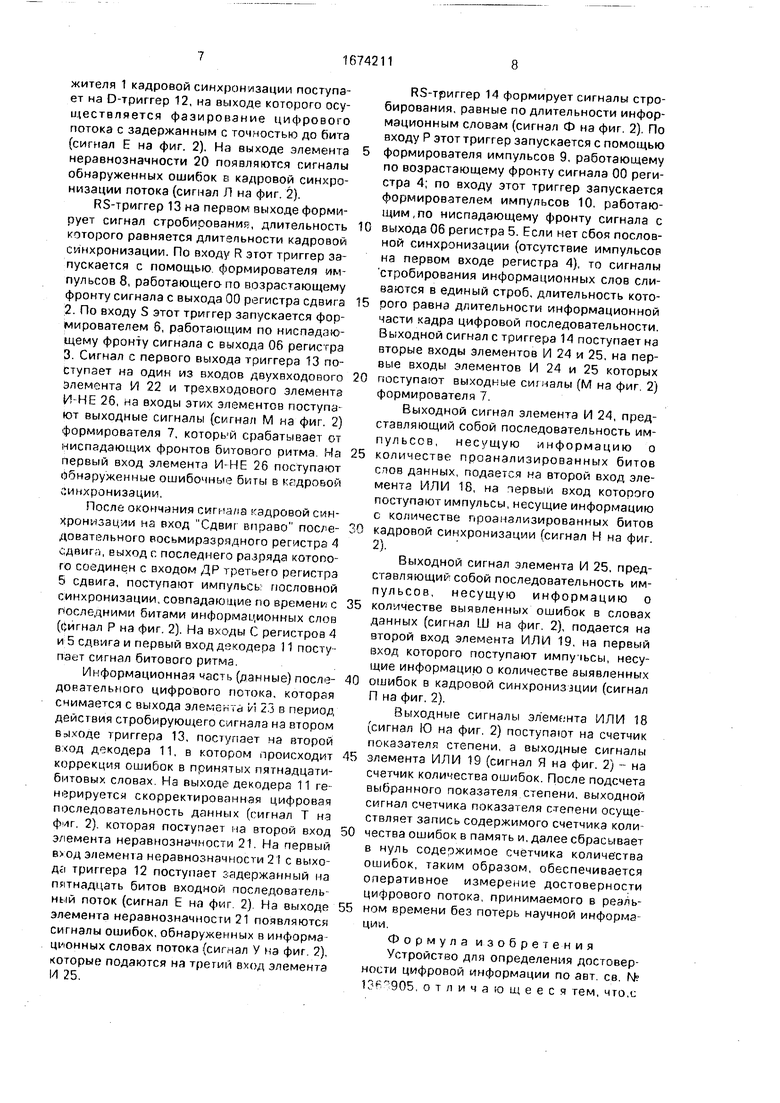

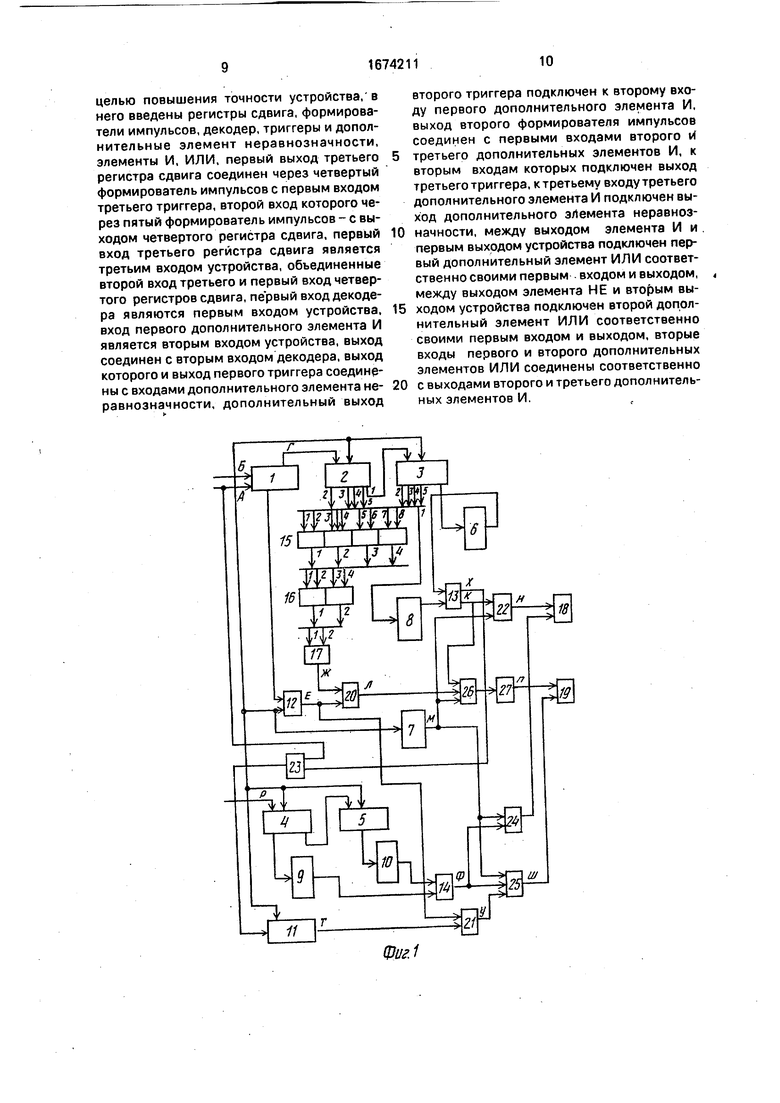

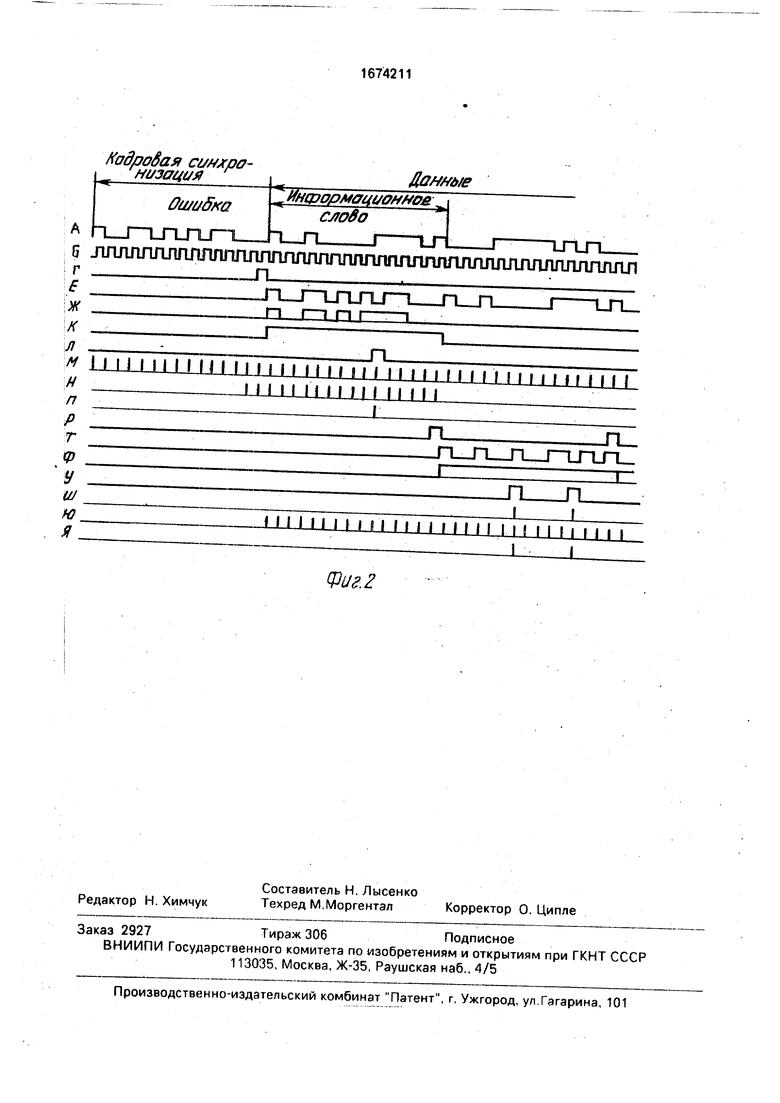

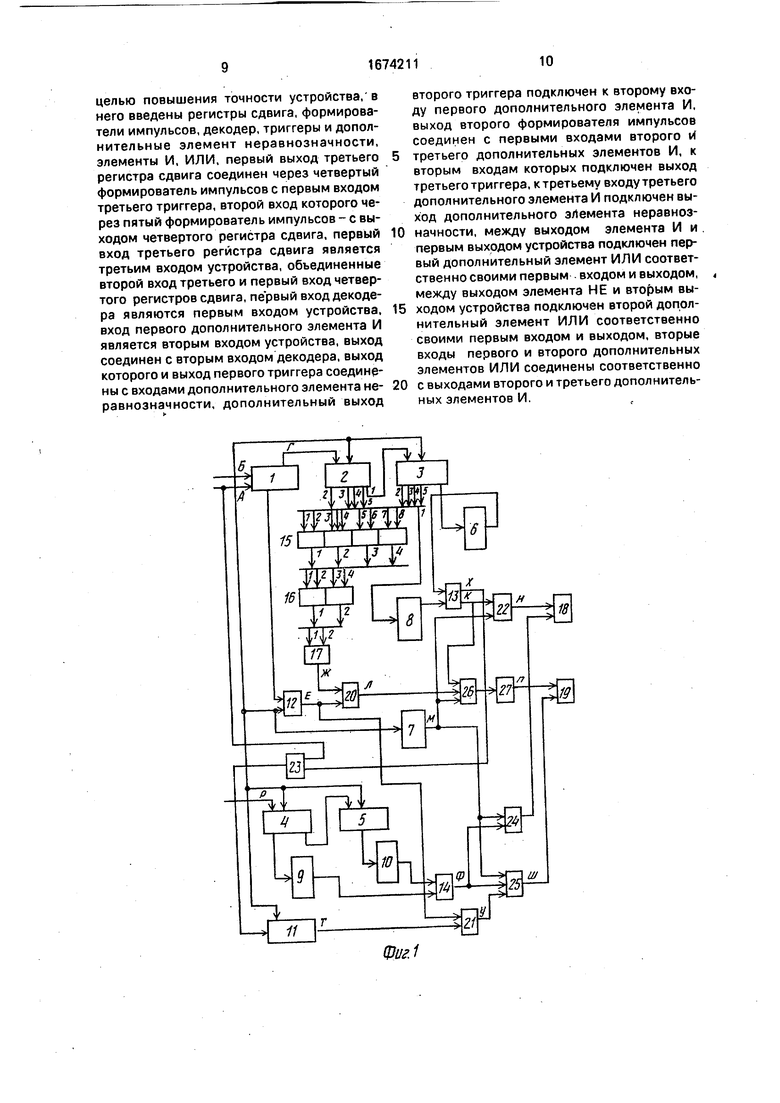

На фиг. 1 приведена функциональная схема устройства, на фиг. 2 временная диаграмма работы устройства

Устройство содержит обнаружитель 1 кадровой синхронизации, первый 2, второй 3, третий 4 и четвертый 5 регистры сдвига первый 6, второй 7, третий 8, четвертый 9 и пятый 10 формирователи импульсов, декодер 11, первый 12, второй 13 и третий 14 триггеры, первую 15 и вторую 16 группы элементов ИЛИ, элемент ИЛИ 17, первый и второй дополнительные элементы ИЛИ 18 и 19, элементы неравнозначности 20 и 21, элемент И 22, первый, второй и третий дополо

х

Јь Ю

нительные элементы И 23-25, элемент И-НЕ 26 и элемент НЕ 27.

Обнаружитель 1 кадровой синхронизации служит для формирования импульса, совпадающего по времени с последним битом сигнала кадровой синхронизации, а также для обеспечения задержки на пятнадцать битов входного последовательного потока. Входы обнаружителя 1 кадровой синхронизации являются, соответственно, первым и вторым входами устройства.

Регистры 2 и 3 сдвига предназначены для последовательного сдвига импульса, получаемого на первом выходе обнаружителя 1 кадровой синхронизации, и совместно с первой 15, второй 16 группами элементов ИЛИ и элементом ИЛИ 17 для получения копии последовательности кадровой синхронизации. Для этого первый выход обнаружителя 1 кадровой синхронизации соединен с первым входом регистра 2, а первый (07) выход регистра 2 соединен с первым входом регистра 3, вторрй (00) и третий (03), четвертый (04) и пятый (06) выходы регистра 2, второй (00) и третий (01), четвертый (02) и пятый (03) выходы регистра 3 соединены, соответственно, с первыми и вторыми входами соответствующих элементов первой 15 группы элементов ИЛИ. первый и второй, третий и четвертый выходы которых соединены, соответственно, с первыми и вторыми ьходами соответствующих элементов второй 16 группы элементов ИЛИ, первый и второй выходы которых соединены, соответственно, с первым и вторым входами элемента ИЛИ 17.

Регистры 2 и 3 совместно с формирователями импульсов 6 и 8 и RS-триггером 13 обеспечивают формирование сигнала стро- бирования на период анализа последовательности битов кадровой синхронизации. Для этого второй выход регистра 2 подключен к входу формирователя импульсов 8, а первый выход регистра 3 соединен с входом формирователя импульсов 6. Выходы формирователей импульсов 6 и 8 подключены, соответственно, к второму (S) и первому (R) входам RS-триггера 13. D-триггер 12 предназначен для обеспечения фазирования входного последовательного цифрового потока с задержанным с точностью до бита. Первый вход триггера 12 соединен с вторым выходом обнаружителя 1 кадровой синхронизации, а второй вход подключен к второму входу устройства.

Формирователь импульсов 7 предназначен для преобразования сигналов битового ритма в короткие по длительности импульсы, обеспечивающие возможность их счета, поэтому вход формирователя импульсов 7 соединен с первым входом устройства.

Элемент неравнозначности 20 предназначен для выявления сигналов несоответствия (ошибок) принятой последовательности кадровой синхронизации с копией, получаемой на выходе элемента ИЛИ 17. Выход элемента ИЛИ 17 соединение первым входом элемента неравнозначности 20, второй

0 вход которого соединен с выходом триггера 12.

Регистры 4 и 5 сдвига обеспечивают задержку канального синхроимпульса на длину слова (15 бит) и совместно с

5 формирователями импульсов 9 и 10. а также R-триггером 14 обеспечивают формирование стробирующего сигнала на период анализа информационного слова. Для этого первый (07) выход регистра 4 соединен с

0 первым входом регистра 5, вторые входы регистров 2-5 являются первым входом устройства. Второй выход (00) регистра 4 соединен с входом формирователя импульсов 9, а выход регистра 5 - с входом формиро5 вэтеля импульсов 10. Выходы формирователей импульсов 9 и 10 соединены, соответственно, с первым (R) и вторым (S) входами триггера 14. Первый вход (ДР) регистра 4 является третьим входом устройст0 ва На него подается сигнал пословной синхронизации (канальный синхроимпульс), получение которого является прере- гативой приемного устройства и не входит в функцию предлагаемого. Выделение сигна5 лов пословной синхронизации при наличии кадровой синхронизации не представляет серьезных трудностей и может быть реализовано обычным умножением частоты следования кадров.

0 Декодер 11 предназначен для исправления случайных ошибок в информационных словах. Его структура определяется сложностью корректирующего кода, который используется при кодировании переда5 ваемой информации. Разнообразие возможных применяемых кодов позволяет в каждом конкретном случае выбирать структуру декодера в соответствии с задачами, на которые ориентирована процедура декоди0 рования. Принципы построения и схемы декодеров широко представлены в современной научно-технической литературе. Если предположить, что в соответствии с прототипом структура кадра определяется

5 пятнадцатибитовым сигналом кадровой синхронизации и информационными словами, а обнаружитель кадровой синхронизации допускает до двух ошибочных битов в кадровой синхронизации, то целесообразно применение, например (15.7) кода ЬЧХ.

позволяющего исправлять все двойные и часть тройных ошибок. Первый вход декодера 11 подключен к первому входу устройства.

Элемент неравнозначности 21 предназ- начен для выявления сигналов несоответствия битовой структуры слов на выходе декодера структуре информационных слов, принятой некорректируемой цифровой последовательности, поэтому выход триггера 12 подключен к первому входу элемента неравнозначности 21, второй вход которого соединен с выходом декодера 11.

Элемент И 22 предназначен для выделения импульсов битовой частоты, совпада- ющих по времени с анализом сигнала кадровой синхронизации, а элемент И-НЕ

26и элемент НЕ 27 позволяют выделить импульсы выявленных при этом анализе ошибок. Выхбд формирователя импульсов 7 подключен к вторым входам элементов И 22

и И-НЕ 26, первые входы которых соединены с первым выходом триггера 13. третий вход элемента И-НЕ 26 подключен к выходу элемента неравнозначности 20, выход эле- мента И-НЕ 26 соединен с входом элемента НЕ 27.

Элемент И 23 обеспечивает поступление на вход декодера 11 лишь информационной части потока данных. Поэтому, второй вход элемента И 23 подключен к второму выходу триггера 13, а первьй вход присоединен к второму входу устройства. Выход элемента И 23 подключен к второму входу декодера 11.

Элемент И 24 предназначен для выделения импульсов битового ритма, совпадающих по времени с анализом информационного слова, а элемент И 25 позволяет выделять импульсы выявленных при этом анализе ошибок. Первые входы элементов И 24 и 25 соединены с выходом формирователя импульсов 7. вторые с выходом триггера 14, выход элемента неравнозначности 21 подключен к третьему входу элемента И 25.

Элемент ИЛИ 18 предназначен для обь- единения временных последовательностей импульсов битового ритма, совпадающих по времени с анализом кадровой синхрони- зации и информационных слов Элемент ИЛИ 19 позволяет выделять временную последовательность импульсов ошибок, выявленных при этом анализе. Выход элемента И 22 соединен с первым входом элемента ИЛИ 18, второй вход которого подключен к выходу элемента И 24. Выход элемента НЕ

27подключен к первому входу элемента ИЛИ 19, второй вход которого подключен к выходу элемента И 25 элементов

ИЛИ 18 и 19 являются первым и вторым выходами устройства, соответственно.

Дополнительные элементы, введенные в устройство, могут иметь тоже самое конст руктивное исполнение, что и соответствующие элементы, описанные в основном изобретении, т.е. регистры 4 и 5 сдвига аналогичны регистрам 2 и 3. формирователи импульсов 9 и 10 формирователям импульсов 8 и 6, триггер 14 триггеру 13. элемент неравнозначности 21 - элементу неравнозначности 20,элементы И 23 и 24 элементу И 22.

Работа устройства основана на сравне нии элементом неравнозначности 20 сигнала кадровой синхронизации и его копии, поступающей с выхода элемента ИЛИ 17. а элементом неравнозначности 21 принимаемых и скорректированных от ошибок информационных слов, поступающих с выхода декодера 11. Элементы неравнозначности 20 и 21 фиксируют ошибки, возникающие при передаче цифровой последовательно сти, которые через элемент ИЛИ 19 посту пают на выход 4 устройства.

Регенерированный последовательный цифровой поток (сигнал А на фиг. 2), содер жащий данные и кадровую синхронизацию, поступает на обнаружитель 1 кадровой син хронизации, на первый вход этого обнаружителя поступают сигналы битовой синхронизации (сигнал Б на фиг 2). Под воздействием шума канала имеют место ошибки (ложные вставки и ложные выпадения битов) в цифровом потоке как в составе данных, так и в составе кадровой синхрони зации.

Сигнал Г появляется на выходе обнару жителя кадровой синхронизации допускающего, например, до двух ошибочных битов в кадровой синхронизации вида 100110101111000 в интервале времени, соответствующем последнему биту в кадровой синхронизации. Сигнал Г поступает на вход Сдвиг вправо последовательною восьмиразрядного регистра 2 сдвига выход последнего разряда которого соединен с входом ДР второго регистра 3 На вход С обоих регистров сдвига (RC) 2 и 3 поступает сигнал битового ритма Соответствующие выходы обоих регистров соединены с входами четырех двухвходовых элементов ИЛИ 15, четыре выхода которых соединены с вхо дами двух двухвходовых элементов И ПИ 16. два выхода которых соединены с входами двухвходового элемента ИЛИ 17 на выходе которого образуется копия кадровой син ронизации (сигнал Ж на фиг. 2)

Задержанный на пятнадцать битов вы /.одной последовательный поток с обнару

жителя 1 кадровой синхронизации поступает на D-триггер 12, на выходе которого осуществляется фазирование цифрового потока с задержанным с точностью до бита (сигнал Е на фиг. 2). На выходе элемента неравнозначности 20 появляются сигналы обнаруженных ошибок в кадровой синхронизации потока (сигнал Л на фиг. 2).

RS-триггер 13 на первом выходе формирует сигнал стробирования, длительность которого равняется длительности кадровой синхронизации. По входу R этот триггер запускается с помощью формирователя импульсов 8, работающего по возрастающему фронту сигнала с выхода 00 регистра сдвига

2.По входу S этот триггер запускается формирователем 6, работающим по ниспадающему фронту сигнала с выхода Об регистра

3,Сигнал с первого выхода триггера 13 поступает на один из входов двухвходового элемента И 22 и трехвходового элемента И-НЕ 26, на входы этих элементов поступают выходные сигналы (сигнал М на фиг. 2) формирователя 7, который срабатывает от ниспадающих фронтов битового ритма На первый вход элемента И-НЕ 26 поступают обнаруженные ошибочные биты в крдровой синхронизации.

После окончания сигнала кадровой синхронизации на вход Сдвиг вправо последовательного еосьмиразрядного регистра 4 сдвиг;, выход с последнего разряда котопо- го соединен с входом ДР третьего регистра 5 сдвига, поступают импульсы пословной синхронизации, совпадающие по времени с последними битами информационных слов (сигнал Р на фиг. 2). На входы С регистров 4 и 5 сдвига и первый вход декодера 11 посту пает сигнал битового ритма

Информационная часть (данные) последовательного цифрового потока, которая снимается с выхода элементе И 23 в период действия стробирующего сигнала на втором выводе триггера 13, поступает на второй вход декодера 11, в котором происходит коррекция ошибок в принятых пятнадцатибитовых словах На выходе декодера 11 ге нерируется скорректированная цифровая последовательность данных (сигнал Т на фиг. 2). которая поступает на второй вход элемента неравнозначности 21. На первый вход элемента неравнозначности 2 1 с выхода триггера 12 поступает задержанный на пятнадцать битов входной последователь ный поток (сигнал Е на фиг. 2). На выходе элемента неравнозначности 21 появляются сигналы ошибок, обнаруженных в информэ ционных словах потока (сигнал V на фиг 2), которые подаются на третий вход элемента И 25.

RS-триггер 14 формирует сигналы стробирования, равные по длительности информационным словам (сигнал Ф на фиг. 2). По входу Р этот триггер запускается с помощью

формирователя импульсов 9, работающему по возрастающему фронту сигнала 00 регистра 4; по входу этот триггер запускается формирователем импульсов 10, работающим, по ниспадающему фронту сигнала с

0 выхода 06 регистра 5. Если нет сбоя пословной синхронизации (отсутствие импульсор на первом входе регистра 4), то сигналы стробирования информационных слов сливаются в единый строб, длительность кото5 рого равна длительности информационной части кадра цифровой последовательности. Выходной сигнал с триггера 14 поступает на вторые входы элементов И 24 и 25. на первые входы элементов И 24 и 25 которых

0 поступают выходные cm налы (М на фиг 2) формирователя 7.

Выходной сигнал элемента И 24, представляющий собой последовательность им- пульссв, несущую информацию о

5 количестве проанализированных битов спов данных, подается на второй вход элемента ИЛИ 18, на первый вход КОТОРОГО поступают импульсы, несущие информацию о количество проанализированных битов

0 кадровой синхронизации (сигнал Н на фиг. 2).

Выходной сигнал элемента И 25, представляющий собой последовательность импульсов, несущую информацию о

5 количестве выявленных ошибок в словах данных (сигнал Ш на фиг. 2), подается на второй вход элемента ИЛИ 19, на первый вход которого поступают импу 1ьсы. несущие информацию о количестве выявленных

0 ошибок в кадровой синхронизации (сигнал П на фиг. 2),

Выходные сигналы элемента ИЛИ 18 (сигнал Ю на фиг. 2) поступают на счетчик показателя степени, а выходные сигналы

5 элемента ИЛИ 19 (сигнал Я на фиг. 2) - на счетчик количества ошибок. После подсчета выбранного показателя степени, выходной сигнал счетчика показателя степени осуице ствляет запись содержимого счетчика коли

0 чества ошибок в память и. далее сбрасывает в нуль содержимое счетчика количества ошибок, таким образом обеспечивается оперативное измерение достоверности цифрового потока, принимаемого в реаль5 ном времени без потерь научной информэ ции

Формула изобретения Устройство для определения достоверности цифровой информации по авт. св. № отличающееся тем. чго.с

целью повышения точности устройства, в него введены регистры сдвига, формирователи импульсов, декодер, триггеры и дополнительные элемент неравнозначности, элементы И, ИЛИ, первый выход третьего регистра сдвига соединен через четвертый формирователь импульсов с первым входом третьего триггера, второй вход которого через пятый формирователь импульсов - с выходом четвертого регистра сдвига, первый вход третьего регистра сдвига является третьим входом устройства, объединенные второй вход третьего и первый вход четвертого регистров сдвига, первый вход декодера являются первым входом устройства, вход первого дополнительного элемента И является вторым входом устройства, выход соединен с вторым входом декодера, выход которого и выход первого триггера соединены с входами дополнительного элемента не- равнозначности, дополнительный выход

второго триггера подключен к второму входу первого дополнительного элемента И, выход второго формирователя импульсов соединен с первыми входами второго и третьего дополнительных элементов И, к вторым входам которых подключен выход третьего триггера, к третьему входу третьего дополнительного элемента И подключен выход дополнительного элемента неравнозначности, между выходом элемента И и первым выходом устройства подключен первый дополнительный элемент ИЛИ соответственно своими первым входом и выходом, между выходом элемента НЕ и вторым выходом устройства подключен второй дополнительный элемент ИЛИ соответственно своими первым входом и выходом, вторые входы первого и второго дополнительных элементов ИЛИ соединены соответственно с выходами второго и третьего дополнительных элементов И.

Кадровая синхронизация

Данные

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения достоверности цифровой информации | 1986 |

|

SU1368905A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

Изобретение относится к цифровым системам передачи и может быть использовано для оперативного контроля достоверности в телеметрических потоках информации. Целью изобретения является повышение точности устройства путем обнаружения ошибок во всем непрерывно передаваемом потоке цифровой информации. Устройство содержит обнаружитель кадровой синхронизации. В состав устройства входят четыре регистра сдвига, обнаружитель кадровой синхронизации, пять формирователей импульсов, декодер, три триггера, два элемента неравнозначности, две группы элементов ИЛИ, три элемента ИЛИ, элемент И - НЕ, элемент НЕ и четыре элемента И. Работа устройства основана на сравнении первым элементом неравнозначности сигнала кадровой синхронизации и копии, поступающей с выхода первого элемента ИЛИ, а вторым элементом неравнозначности - принимаемых и скорректированных от ошибок информационных слов, поступающих с выхода декодера. Элементы неравнозначности фиксируют ошибки, возникающие при передаче цифровой последовательности, которые через второй элемент ИЛИ поступают на выход устройства. 2 ил.

. информационное слой о

манная J i-H

с Jшлллnлflлnлru flллппллnn

,:

м I i11 I11IIIII 11 Ii11 11iмiI 11 i i i 11 i i i i 11 i м i t 11 I

н п

р т

ф

У ш ю я

I I I I I I I И I I I I I I I

I

п.

л

п

л

I

I

НИ III М II И I I I I И М М t I II И I I

±

X

Фиг. 2

ионное

манная i J i-Hп.

л

п

л

I

I

±

X

| Устройство для определения достоверности цифровой информации | 1986 |

|

SU1368905A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-08-30—Публикация

1989-07-12—Подача