Изобретение относится к вычислительной технике и может найти применение в многопроцессорных системах для распределения нагрузки между процессорами.

Цель изобретения - расширение области применения устройства за счет учета директивных сроков обслуживания заявок.

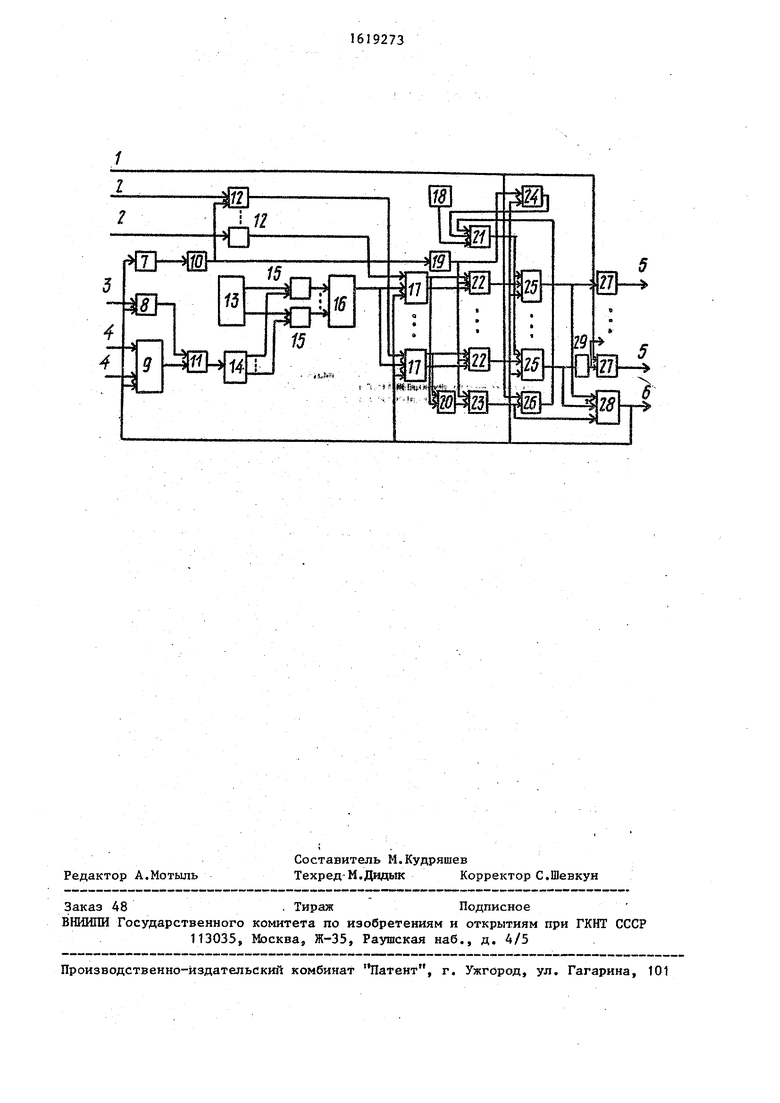

На чертеже приведена структурная схема устройства.

Устройство содержит сигнальный вход устройства 1, группы информационных входов 2 устройства, вход 3 запроса устройства, входы 4 кода запрашиваемой функции устройства, информационные выходы 5 устройства, сигнальный выход 6 устройства, формирователь 7 импульсов, триггер 8, регистр 9, элемент 10 задержки, блок элементов И 11, группу блоков элементов И 12, блок 13 регистров, дешифратор 14, группу блоков элементов И 15, блок элементов ИЛИ 16, группу сумматоров 17, генератор 18 импульсов, элемент 19 задержки,элемент ИЛИ-НЕ20, элемент И 21, группу блоков элементов И 22, элемент И 23, триггер 24, группу счетчиков 25, триггер 26, группу выходных триггеров 27, элемент ИЛИ 28, блок элементов И 29.

Устройство работает следующим образом.

В исходном состоянии все триггеры, счетчики и сумматоры устройства и регистр 9 обнулены. Блок 13 регистров содержит коды, соответствующие допустимому времени ожидания запраши05

CD tsD J

СО

баемых функций в зависимости от директивных сроков и времени их выполнения процессором (все лроцессоры, входящие в многопроцессорную систему, имеют одинаковую производительность) t представленные в ббратном ко де времена ожидания рассчитываются заранее.

Запросы на обслуживание поступают от одного источника с минимальным допущенным интервалом между двумя соседними запросами больше, чем максимально возможное время работы устрогства (под временем работы устройства здесь принимается цикл выбора запроса от момента поступления сигнала запроса на вход 3 до момента поступления сигнала на вход 1, устанавливающего устройство в исходное состояние).

Код запрашиваемой функции поступает по входам 4 в регистр 9. Одновременно на входе 3 появляется сигна

запроса на выполнение запрашиваемой функции, которым устанавливается триггер 8 в единичное состояние, и подается на формирование 7 импульсов на выходе которого появляется импульс, поступающий на элемент 1-0 задержки. Сигнал с единичного выхода триггера 8 открывает блок элементов И 1 1 и разрешает прохождение кода запрашиваемой функции с регистра 9 на дешифратор 14. Ча выходе дешифратора 14, соответствующем коду запрашиваемой функции, появляется сигн :л, открывающий соответствующий блок элементов И 15, Код допустимого времени ожидания запрашиваемой Функции через блок элементов И 15 и блок i элементов ИЛИ 16 поступает на соответст вуюшче входы блока сумматоров 17. По информационным входам устройства 2 через блоки элементов И 12, открывав мие по второму входу задержанным сигналом с выхода элемента 10 задержки на соответствующие сумматоры 17, поступают коды суммарного времени до- обслуживания всех гаявок в соответствующих процессорах. Таким образом, в сумматорах 17 производится операция вычитания из кода обслуживания залвок в соответствующем процессоре кода допустимого времени ожидания запрашиваемой функции.

Импульс, поступивший с элемента 10 задержки на элемент 19 задержки, задерживаясь в последнем, посту

5

0

0

5

0

5

0

5

пает на единичный вход триггера 24, на первый вход элемента И 23 и первые входы блоков элементов И 22. Результат операции вычитания, полученный в сумматоре 17, поступает на соответствующий счетчик 25 только в том случае, когда на знаковом выходе этого сумматора 17 присутствует единичный сигнал, открывающий соответствующий блок элементов 22 при поступлении на него импульса с выхода элемента 19 Задержки. Одновременно сигналы со знаковых выходов сумматора 17 через элемент ИЛИ-НЕ 20 поступают на второй вход элемента И 23.

При поступлении импульса с элемента 19 задержки на первый вход элемента И 23 на его выходе появляется единичный сигнал только в случае, когда все знаковые разряды сумматоров 17 имеют нулевое значение, т.е. запрашиваемая функция ни на одном процессоре не может быть выполнена без нарушения директивного срока,, Импульс с выхода элемента И 23, проходя через элемент ИЛИ 28, поступает на выход 6 устройства, а также устанавливает триггер 26 в единичное состояние, сигнал с инверсного выхода которого подается на вход элемента И 21, закрывая его и тем самым запрещая прохождение импульсов с генерато ра 18 на счетчики 25. Высокий потенциал с прямого выхода триггера 24 поступает на вход элемента И 21 ив случае, когда с инверсного выхода триггера 26 на вход элемента И 21 поступает единичный сигнал, разреша- ет поступление импульсов с генератора 18 на счетные входы счетчиков 25. На выходе переполнения того счетчика 5 появляется импульс, код в котором максимален. Импульс переполнения устанавливает соответствующий триггер 27 в единицу и через элемент ИЛИ 28 поступает на сигнальный выход 6 устройстве и устанавливает в нулевое состояние триггер 8, регистр 9, сумматоры 17, счетчики 25 и триггер 24. При наличии-сигнала на выходе переполнения двух и- более счетчиков 25 в единичное состояние устанавливается тот триггер 27, номер которого меньше, так как соответствующие элементы И 29 с большими номерами запираются сигналом с выхода счетчика 25 с наименьшим номером. Тем самым достигается однозначный выбор

процессора для назначения. С выхода соответствующего триггера 27 на выход устройства 5 поступает единичный сигнал, определяющий процессор, которому назначается на обслуживание запрашиваемая функция. Если на выходе 6 устройства появляется импульс, означающий окончание цикла выбора процессора, и ни на одном из выходов 5 устройства нет единичного сигнала, то запрос на выполнение запрашиваемой функции не принимается к обслуживанию. По окончании цикла выбора система посылает импульс по входу J устройства, устанавливающий триггеры 26, 27 в исходное состояние.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее первый блок элементов И, группу счетчиков, блок регистров, отличающееся тем, что, с целью расширения области применения устройства за счет учета директивных сроков обслуживания заявок, в него введены формирователь импульсов, регистр, три триггера, два элемента задержки, второй блок элементов И, три группы блоков элементов И, дешифратор,блок элементов ИЛИ, группа сумматоров, генератор импульсов, элемент ИЛИ-НЕ, два элемента И, группа выходных триггеров, элемент ИЛИ, причем вход запроса устройства подключен к единичному входу первого триггера и к входу формирователя импульсов, выход которого подключен к входу первого элемента задержки, группы информационных входов устройства подключены к информационным входам соответствующих блоков элементов И первой группы, управляющие входы которых подключены к выходу первого элемента задержки,сигнальный вход устройства подключен к нулевому входу второго тиггера и к нулевым входам триггеров группы, входы запрашиваемой функции устройства подключены к информационным входам регистра, выгоды которого подключены к информационным входам первого блока элементов И, управляющий вход которого подключен к выходу первого триггера, выходы первого блока элементов И подключены к входам дешифратора, вы-f

0

5

0

5

ходы блока регистров подключены к информационным входам соответствующих блоков элементов К второй группы, управляющие входы которых подключены к соответствующим выходам дешифратора, выходы блоков элементов И второй группы подключены к входам блока элементов ИЛИ, выходы которого подключены к первым информационным входам сумматоров группы,вторые информационные входы которых подключены к выходам соответствующих блоков элементов И первой группы, выход генератора импульсов подключен к первому входу первого элемента И, второй вход кото- го подключен к выходу второго триггера, третий вход первого элемента И подключен к выходу третьего триггера, единичный вход второго триггера подключен к выходу второго элемента И и к первому входу элемента ИЛИ, первый вход второго элемента И подключен к выходу второго элемента задержки и к первым управляющим входам блоков элементов И третьей группы, знаковые выходы сумматоров группы подключены к вторым управляющим входам блоков элементов И третьей группы и к входам

Q элемента ИЛИ-НЕ, выход которого подключен к второму входу второго эле мента И, разрядные выходы сумматоров , группы подключены к информационным входам блоков элементов И третьей группы, выходы которых подключены к информационным входам соответствующих счетчиков группы, счетные входы которых подключены к выходу первого элемента И, выход переполнения первого счетчика подключен к единичному входу первого триггера группы, а также к соответствующему входу элемента ИЛИ, выход которого является сигнальным выходом устройства и подключен к входам обнуления регистра первого и третьего триггеров, сумматоров группы и счетчиков группы, выход второго элемента задержки подключен к единичному входу третьего триггера, выходы группы выходных триггеров являю ся информационными выходами устройства, выход переполнения каждого счет-чика группы подключен к соответствующему инверсному входу второго блока элементов И, выходы которого

подключены к единичным входам соответствующих триггеров группы.

5

0

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий в неоднородной вычислительной среде | 1990 |

|

SU1725220A1 |

| Устройство для распределения заданий процессором | 1990 |

|

SU1705827A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| АВТОМАТИЗИРОВАННАЯ ИНФОРМАЦИОННАЯ СИСТЕМА СУДЕБНОГО ДЕЛОПРОИЗВОДСТВА | 2005 |

|

RU2291480C1 |

| Устройство для ввода информации | 1989 |

|

SU1661748A1 |

| Устройство для управления запуском программ | 1989 |

|

SU1621031A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА СБОРА И ОБРАБОТКИ ДАННЫХ ТЕРРИТОРИАЛЬНО-РАСПРЕДЕЛЕННЫХ ОБЪЕКТОВ | 2005 |

|

RU2289159C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СЛЕЖЕНИЯ ЗА ХОДОМ ГОЛОСОВАНИЯ ИЗБИРАТЕЛЕЙ | 2005 |

|

RU2293370C1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для селекции признаков объектов | 1990 |

|

SU1725237A1 |

Изобретение относится к вычислительной технике и может найти применение в многопроцессорных системах для распределения нагрузки между процессорами. Целью изобретения является расширение области применения устройства за счет учета директивных сроков обслуживания заявок. В устройство введены формирователь импульсов, регистр, три триггера, два элемента задержки, три группы блоков элементов И, второй блок элементов И, дешифратор , блок элементов ИЛИ, группа сумматоров, генератор импульсов, элемент ИЛИ-НЕ,два элемента И, группа выходных триггеров, элемент ИЛИ. 1 ил.

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1205144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1989-02-20—Подача