1

Изобретение относится к вьиислитель- ной технике и мсвкет быть HcnonbaojeaHo для формирования испытательных последовательностей в устройствах проверен логических схем.

Известен генератор двоичных последовательностей, формирующий псевдослучайную последовательность максимальной длины, содержащий генератор тактовых импульсов, блок хранения последователь ности в виде регистра, выходы которого являются выходами генератора, и сумматор по модулю два, входы которого прям либо через некоторую коммутирующую схему соединены с некоторыми выходами регистра, а соединен с входами регистра Cl3 .

Однако таксЛ генератор обладает малой гибкостью и может изменять свою конфигурацию (число разрядов, номера и количество разрядов, подключаемых к . входам сумматора и т.п.) лишь в ограниченных пределах.

Наиболее бпизким является генератор, у которого блок хранения выполнен в виде накопителя ЗУПВ объемом N слов, каждое слово которого имити1 ет разряд N разрядного регистра сдвига. В этом случае в состав генератора включается генератор инструкций - датчик програм мы и устройство для модификации адреса накопителя - сумматора, поскольку для имитации сдвига влево исполнительный адрес накопителя в очередном такте - должен увеличиваться на 2 по сравнению, с тем же адресом в предыдущем такте, причем суммирование выполняется по N.

При этом генератор формирует псевдослучайную последовательность о програм.мируемым соединением разрядов с входами сумматора по модулю два t . .

Для известньк генераторов характерны следующие недостатки, за- рудняющие их использование в качестве датчиков испытательных последовательностей:

39913974

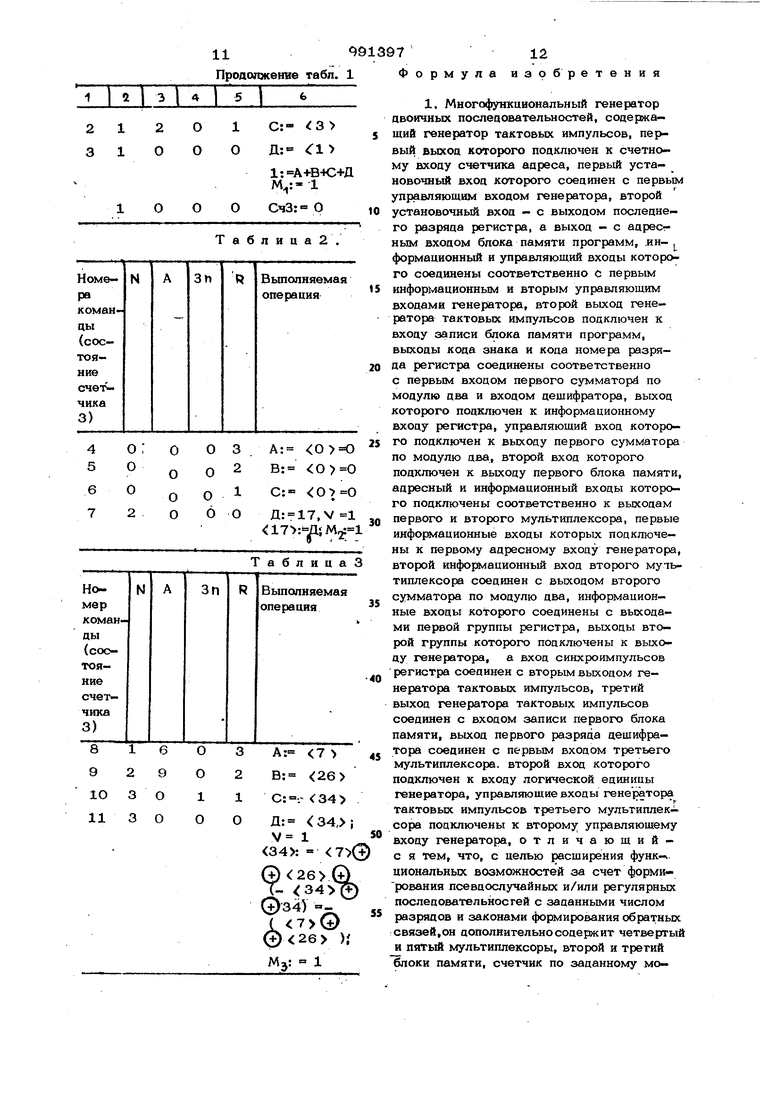

- невозможность без дополнительного соединен с вторым выходом генератора оборудования получения нескольких раз-тактовых импульсов, третий выход генеличных генераторов псевдослучайных и/ил регулярных последовательностей с заданными числами разрядов и заданными законами формирования обратных связей; - невозможность без дополнительного оборудования получения нескольких зависимых генераторов вышеуказанных последовательностей . .Целью изобретения является расширение функциональных возможностей за сче разбиения накопителя на ряд участков, имитирующих требуемое число регистров сдвига. При этом для правильной модификации адреса необходимо иметь данные об адресах первых разрядов, о числе разрядов и о текущем значении модификации адресов разрядов имитируемых регистров сдвига. Поставленная цель достиг ается тем, что в многофункциональный генератор двоичных последовательностей, содержащий генератор тактовых импульсов, первы выход которого подключен к счетному входу счетчика адреса, первый установоч ный вход которого соединен с первым управляющим входом генератора, второй установочный вход - с выходом последне го разряда регистра, а-выход - с адресным входом блока памяти программ, информационный и управляющий входы которого соединены соответственно с первым информационным и вторым управляющим входами генератора, ;второй выход генера тора тактовых импульсов подключен к входу записи блока памяти программ, выходы кода знака и кода номера разряда регистра со0динены соответственно с первым входом первого сумматора по модулю два и уходом дешифратора, выход которого подключен к информационному входу регистра, управляющий вход которого подключен к выходу первого сумматора по 1 1одулю два, второй вход которого подключен к выходу первого блока памяти, адресный и информационный входы которого подключены соответ венно к выхода(М первого и второго муль типлексоров, пфрвые информационные вхо ды которых подключены к первому адрес ному входу rei epaTQpa, второй информационный вход второго мультиплексора соединен с второго сумматора по модулю два информационные входы .которого соединены с выходами первой группы регистр, выходы второй группы к уторого подключены к вькоду генератора, а вход синхроимпульсов регистра ратора тактовых импульсов соединен с входом записи первого блока памяти, вы- ход первого разряда дешифратора соединен с первым входом третьего мультиплексора, второй вход которого подключен к входу логической единицы генератора, управляющие входы генератора тактовых имйульсов третьего мультиплексора подключены к второму управляющему входу генератора, дополнительно введены чет- вертьй и пятый мультиплексоры, второй и третий блоки памяти, счетчик по задан У модулю и формирователь адреса, причем управляющие входы третьего и четвертого мультиплексоров и третьего блока памяти подключены к второму управляющему входу гене{5атора, выход кода номера имитирующего регистра блока памяти программ подключен к первому информационному входу четвертого мультиплексора, второй информационный вы- . ход которого соединен с вторым адресным одом генератора, вход логического У генератора соединен с первым информационным входом пятого мультиплексора, второй инфориационный вход которого соединен с выходом счетчика по модулю, установочный вход которого соединен с первым входом формирователя адреса и выходом третьего блока памяти, информационный вход которого соединен с выходом пятого мультиплексора, адресный вход - с адресным входом второго блока памяти и выходом четвертого мультиплексора, управляющий вход третьего блока памяти соединен с счетным входом счетчика по заданному модулю, с управляющим входом первого блока памяти и выходом третьего мультиплексора, выход кода относительного адреса подключен к второму входу формирователя адреса, третий вход которого соединен с входом модуля счетчика по заданному модулю и с выходом кода числа разрядов второго блока памяти, выход кода адреса первых разрядов которого подключен к четвертому входу формирователя адреса, выход которого соединен с вторым информационным входом первого мультиплексора, информационный вход второго блока памяти соединен с вторым информационным входом генерато ра, входы записи второго и третьего блоков памяти и синхровход счётчика по заданному модулю соединены соответственно с первым, четвертым и вторым вы- .ходами генератора тактовых импульсов. :(

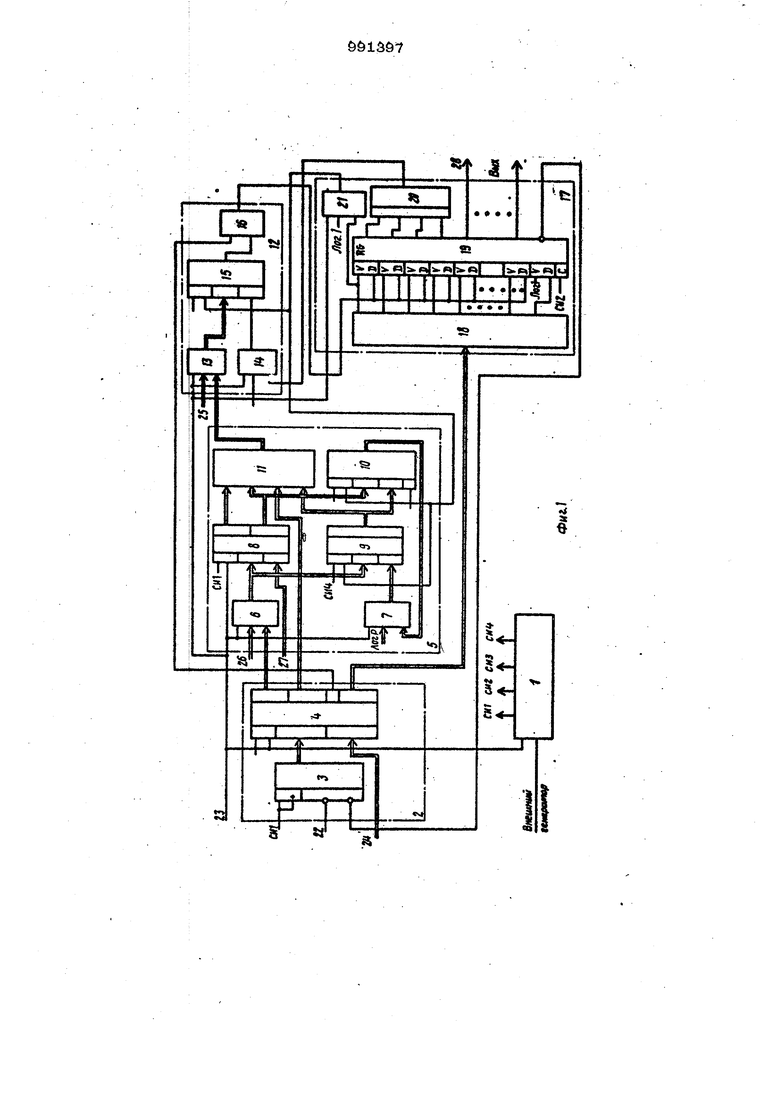

При этом формирователь апреса со- цермсит три сумматора и мультиплексор, выхоа которого соединен с первым вхо дом первого сумматора, вгорой вхоц которого соединен с четвертым входом формирователя, а выход - с выходом формирователя, выход второго сумматора соединен с первым информационным входом мультиплексора, вторсй информационный BXCNI которого соединен с первым входом второго сумматора и выходом третьего сумматора, первый и второй входы которого соединены с первым и вторым входами формирователя, третий вход которого соединен с вторым входом второго сумматора, выход переноса когорого подключен к управляющему входу мультиплексора.

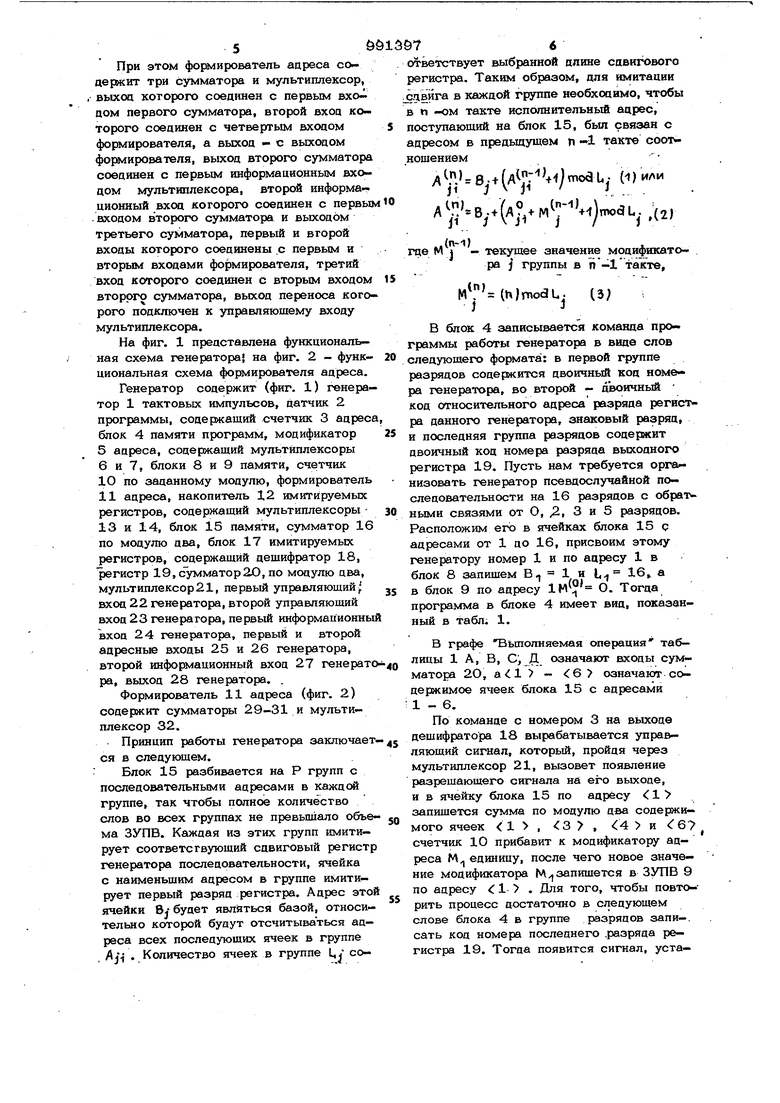

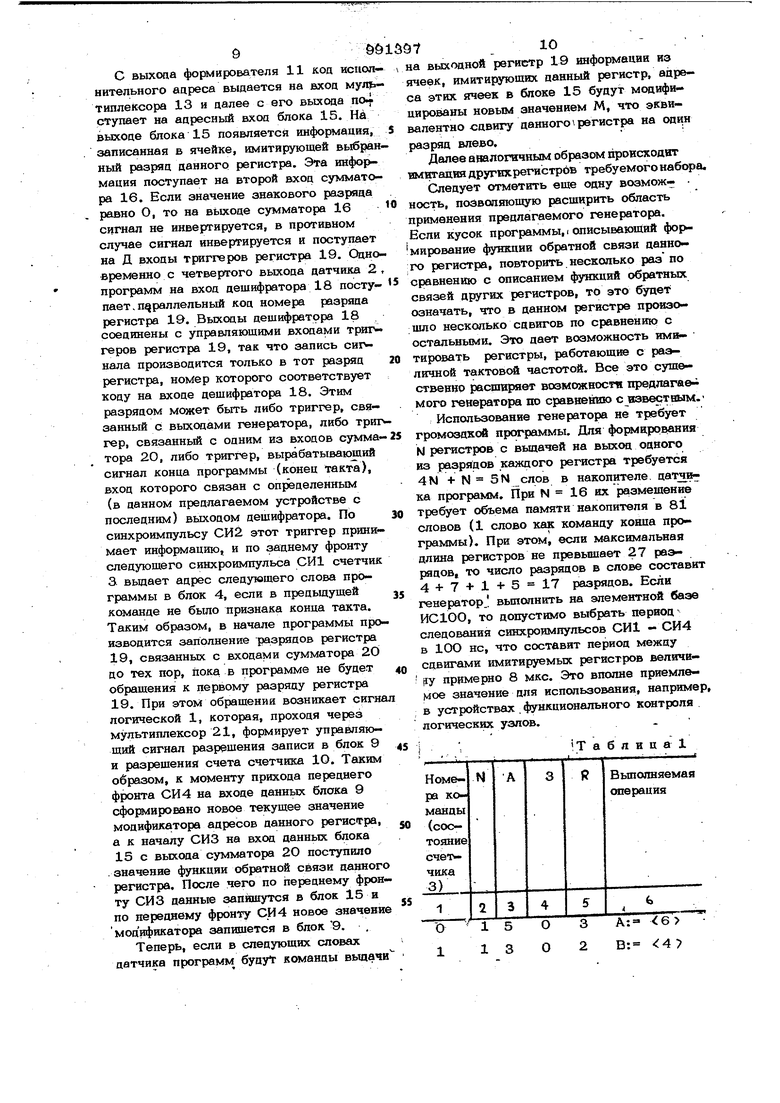

На фиг. 1 представлена функциональная схема генератора} на фиг. 2 - функциональная схема формирователя адреса.

Генератор содержит (фиг. 1) генератор 1 тактовых импульсов, датчик 2 программы, содержащий счетчик 3 адреса блок 4 памяти программ, модификатор

5адреса, содержащий мультиплексоры

6и 7, блоки 8 и 9 памяти, счетчик

10по заданному модулю, формирователь

11адреса, накопитель 12 имитируемых регистров, содержащий мультиплексоры 13 и 14, блок 15 памяти, сумматор 16

по модулю два, блок 17 имитируемых регистров, содержащий дешифратор 18, регистр 19,сумматор2О,по модулю два, мультиплексор21, первый управляющий/ вход 22 генератора, второй управляющий вход 23 генератора, первый информационный вход 24 генератора, первый и второй адресные входы 25 и 26 генератора, второй информационный вход 27 генерато ра, выход 28 генератора. .

Формирователь 11 адреса (фиг. 2) содержит сумматоры 29-31 и мультиплексор 32.

. Принцип работы генератора заключает- ся в следующем.

Блок 15 разбивается на Р групп с последовательньоули адресами в каждсй группе, так чтобы полное количество слов во всех группах не превьпцало объема ЗУПВ. Каждая из этих групп имитирует соответствующий сдвиговый регистр генератора последовательности, ячейка с наименьшим адресом в группе имитирует первый разряд регистра. Адрес этой ячейки 8 будет являться базой, относительно которой будут отсчитываться адреса всех последующих ячеек в группе

Аj . Количество ячеек в группе L.- соответствует выбранной длине сдвигового регистра. Таким образом, для имитации .сдвига в каждой группе необходимо, чтобы в п -ом такте исполнительный адрес, поступающий на блок 15, бьш связан с адресом в предыдущем п -1 такте соотношением

А Г. 8у t () Ьу (i) или

гИ

;.)nx,dL.;(2,

.(n-1)

где М у -текущее значение модифшсато ра j группы в п-1такте,

(h)modU; (Ъ)

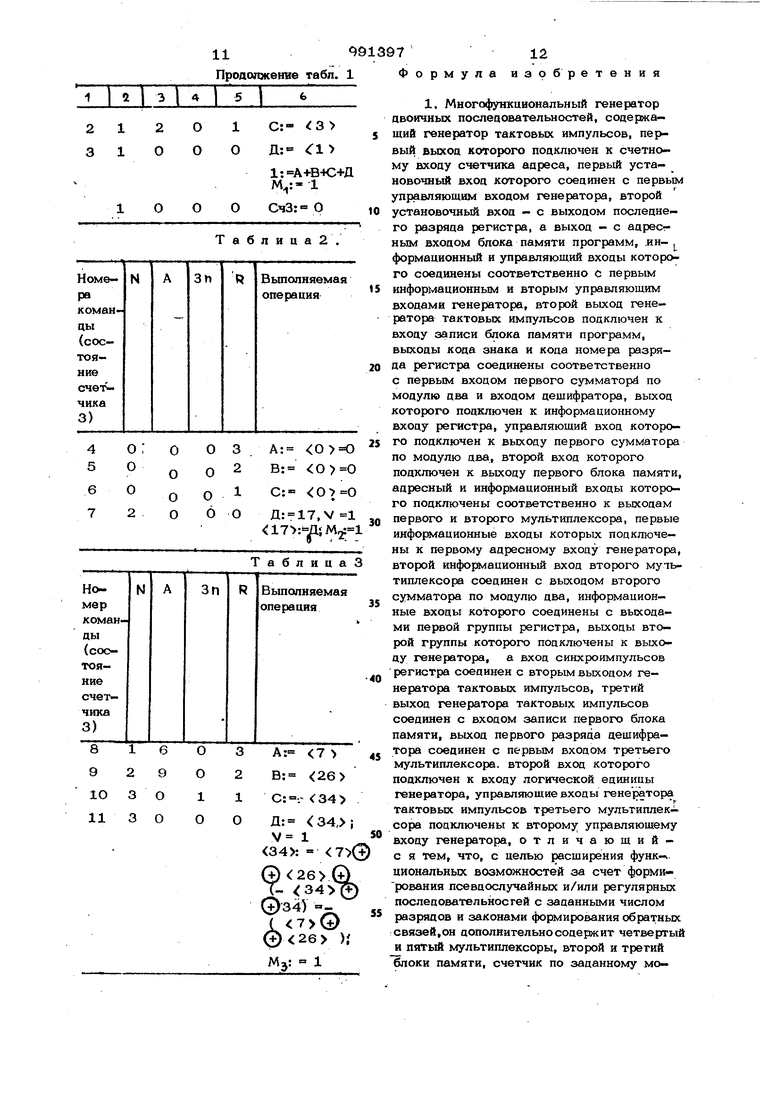

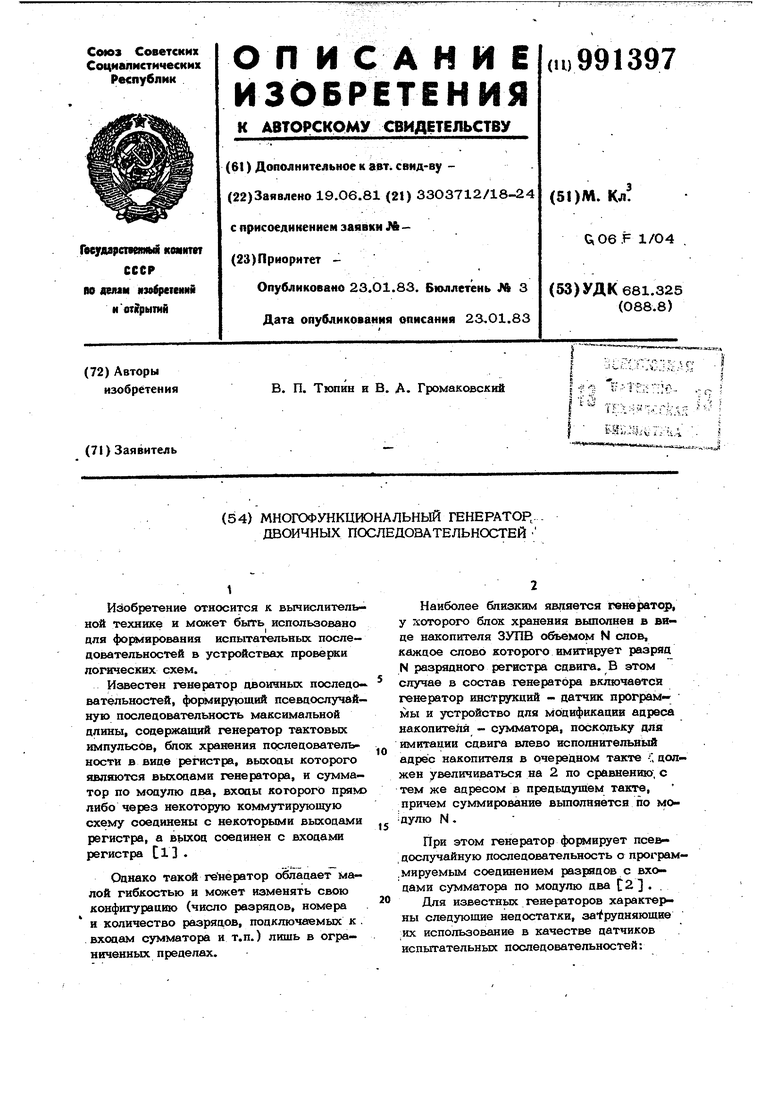

В блок 4 записывается команда программы работы генератора в виде слов следующего формата: в первой группе разрядов содержится двоичный код номера генератора, во второй - двоичный код относительного адреса разряда регистра данного генератора, знаковый разряд, и последняя группа разрядов содержит двоичный код номера разряда выходного регистра 19. Пусть нам требуется орга низовать генератор псевдослучайной последовательности на 16 разрядов с обрат ными связями от О, , 3 и 5 разрядов. Расположим его в ячейках блока 15 с адресами от 1 до 16, присвоим этому генератору номер 1 и по адресу 1 в блок 8 запишем В 1 и t 16,. а в блок 9 по адресу О. Тогда программа в блоке 4 имеет вид, показанный в табл; 1.

В графе Выполняемая операция таблицы 1 А, В, С, Д означают входы сумматора 2О, - 6 означают содержимое ячеек блока 15 с адресами 1-6.

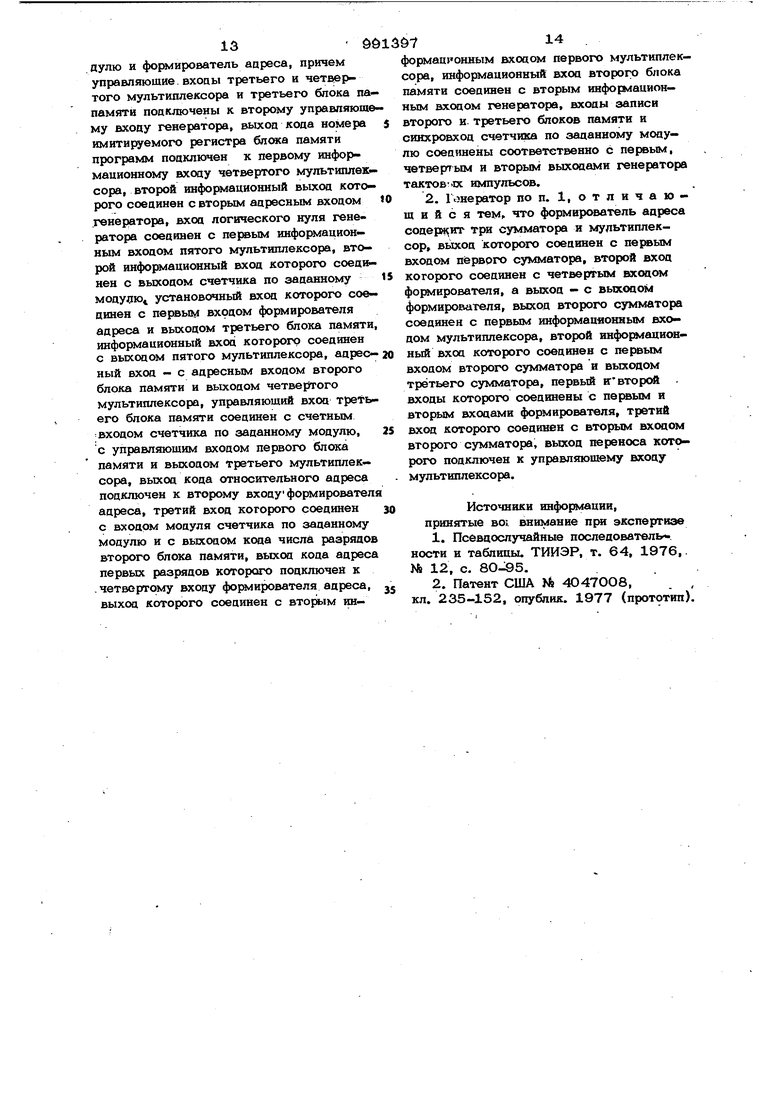

По команде с номером 3 на выходе дешифратора 18 вырабатывается управляющий сигнал, который, пройдя через мультиплексор 21, вызовет появление разрешающего сигнала на его выходе, и в ячейку блока 15 по адресу 1 запишется сумма по модулю два соде реки- мого ячеек 1 , 3 , 4 и f67 счетчик 10 прибавит к модификатору ад- реса М единицу, после чего новое значение модификатора запишется в ЗУПВ 9 по адресу 1 . Для того, чтобы повторить процесс достаточно в следующем слове блока 4 в группе разрядов запи-. сать код номера последнего .разряда регистра 19. Тогда появится сигнал, уста- 7Q9 навливающий счетчик 3 в О, и процесс будет циклически повторяться. Данный сигнал является признаком конца такта генератора, и при необходимости подсчета числа тактов его можно использовать в качестве вхоцнохх) для счетчика тактов. Для того, чтобы входы сумматора 2О можно было устанавливать в определён ное положение, в ячейку 07 блока 15 и в нулевое слово блока 8 при начальном заполнении записывается О. Эта ячейка не должна использоваться при формироваНИИ регистров генераторов, поэтому все генераторы иметь номера /1. Аналогичным образом можно организовать кольцевой регистр сдвига, счетчик Джонсона и т;п. регистровые схемы, Так, для реализации дополнительно к nei вому регистру сольцевого регистра сдв№га с бегушей единицей, расположенного в блоке 15 в ячейках с ад -есами 17 - 33, присвоим этому генератора номер 2, по адресу 2 в блоке 8 запишем 82 17 и L2 I в блок 9 - О. В качестве начальной установки регистра в ячейки 17 - 2 запишем О, в ячейку 33-1. Тогда, после программы работы первого регистра в блоке 4 будет програм ма работы регистра, приведенная в табл. 2 Для организации счетчика Джонсона вместо кольцевого регистра в последней команде прёдыдуцей таблицы достаточно в знаковьй разряд записать 1. При необходимости с помошью программы можно организовать ряд зависи- . мых регистров. Так, например, если мы хотим дополнительно к первым двум регистрам организовать 20-разрядный регистр сдвига, вход которого должен быть равен проинвентированной сумме по модулю два, 6 -го разряда генератора номер 1 и 9-го разряда генератора номер 2, то присвоим этому регистру номер 3 и разместим его в ячейках 34 - 53 блока 15, а По адресу 3 в блок 8 запитем Вз 34, U3 2О, в блок 9 - О. Тогда продолжение программы в бло ке 4 будет иметь вид, приведенный в табл. 3. Аналогичньш образом реализуются и другие вышеу)помянутые возможности генератора. Схшдует фметить, что использование для гене paTojpa функций обратных связей суммато по модулю два не является принципиа|пьным, и для организации нелинейных обратных связей могут быть 78 выбраны другие подходящие комбинацион ные схемы. Таким образом, генератор имеет цва режима работы. В первом режиме производится запись программы в блок 4 я начальных данных в блоки 8, 9 и 15. Для этого на вход 23 подается управляющий сигнал, который разрешает запись в блоки 4 и 8, подкшочает адресные входы блоков 8 и 9 через мультиплексор 6, а адресные входы бло;ка 15 через мультиплексор 13. При этом одновременно мультиплексор 21 вырабатывает сигнал разрешения записи в , блок 9, а мультиплексор 21 вырабатывает сигнал разрешения записи в блок 9, а мультиплексоры 7 и 14 подключают входы данных блоков 9 и 15 к входам логического О и адреса соответственно. С внешних устройств производится синхронизация записи программы в 6rtoK 4, при этом по входу 22 подается сигнал запуск, а по входу 24 поступают данные. Одновременно поступают адреса и данные для заполнения блоков 8, 9 и 15 соот ветственно. По окончании записи во все накопите- ли, генератор переводится в рабочий режим. Для этого управляющий сигнал с 23 снимается, по входу 22 подается сигнал запуска и из датчика 2 программ задается первая команаа. Первая группа разрядов слова команды выдает тсод номера регистра на вход мультиплексора 6 и на адресные входы блоков 8 и 9. По данному номеру первая группа разрядов блока 8 выдает код с адреса базовой ячейки данного регистра В на первый вход формирователя 11, вторая, группа разрядов выдает код числа разрядов данного регистра L, на второй вход и на вход приема модуля счета счетчика Ю. На третий вход формировате«я 11 поступает код относительного адреса выбираемого разряда в данном генераторе АОТН. а на четвертый вход и вход поразрядной установки счетчика 1О поступает код значения модификатора адресов данного регистра М в данном такте, т.е. все О. Фо{ лирователь 11 формирует исполнительный адрес для ЗУПВ 15 в соответствии с выражением (2), т.е. АИСП 2 АОТН+ М при М U + ( М) -(, при + М L, нительного адреса выдается на вход мул типлексора 13 и далее с его выхода по ступает на адресный вхоа блока 15. Ш выходе блока 15 появляется информация, записанная в ячейке, имитирующей выбра ный разряд данного регистра. Эта информация поступает на второй вход суммато ра 16, Если значение знакового ре1зряаа равно О, то на выходе сумматора 16 сигнал не инвертируется, в противном случае сигнал инвертируется и поступает на Д входы триггеров регистра 19. Одно временно с четвертого выхода датчика 2 программ на вход дешифратора 18 поступает. параллельный код номера разряда регистра 19. Выходы дешифратора 18 соединены с управляющими входами триггеров регистра 19, так что запись сиг нала производится только в тот разряд регистра, номер которого соответствует коду на входе дешифратора 18. Этим разрядом может быть либо триггер, связанный с выходами генератора, либо триг гер, связанньй с одним из входов сумматора 2О, либо триггер, вырабатывающий сигнал конца программы (конец такта), вход которого связан с опр)еделеннь1М (в данном предлагаемом устройстве с последним) выходом дешифратора. По синхроимпульсу СИ2 этот триггер принимает информацию, и по заднему фронту следующего синхроимпульса СИ1 счетчик 3 вьщает адрес следующего слова программы в блок 4, если в предьщущей команде не было признака конца такта. Таким образом, в начале программы производится заполнение разрядов регистра 19, связанных с входами сумматора 20 до тех пор, пока в программе не будет обращения к первому разряду регистра 19. При этом обращении возникает сигнал логической 1, которая, проходя через мультиплексор 21, формирует управляющий сигнал разрешения записи в блок 9 и разрешения счета счетчика 1О. Таким образом, к моменту прихода переднего фронта СИ 4 на входе данных блока 9 сформировано новое текущее значение модификатора адресов данного регистра, а к началу СИЗ на вход данных блока 15 с выхода сумматора 2О поступило .значение функции обратной связи данного регистра. После чего по переднему фронту СИЗ данные запишутся в блок 15 и по переднему фронту СИ 4 новое значение модификатора запишется в блок 9. Теперь, если в следующих словах датчика программ будут команды вьщачи ячеек, имитирующих данный регистр, адреса этих ячеек в блоке 15 будут модифицированы новым значением М, что эквивалентно сдвигу данного регистра на один разряд влево. Далее аналогвчным образом происходит вмитадвя других регистров требуемого набора. Следует отметить еще одну возмож- ность, позвоптошую расширить область применения предлагаемого генератора. Если кусок программы, i описывающий фо(мирование функции обратной связи данного регистра, повторить несколько раз по сравнению с описанием функций обратных связей других регистров, то это будет означать, что в данном регистре произошло несколько сдвигов по сравнению с остбшьными. Это дает возможность имитировать регистры, работающие с различной тактовой частотой. Все это сушественно расширяет возможности преалагав1 мого генератор по сравнешоо с взвеет вым. Использование генератора не требует громоздкой пр01Т)аммы. Для формирования N регистров с вьщачей на одного из разрядов каждого регистра требуется 4N + N 5N слов в накопителе, датдика программ. При N 16 их размещение требует объема памяти накопителя в 81 словов (1 слово как команду конца программы). При этом, если максимальная длина регистров не превышает 27 разрядов, то число разрядов в слове составит 4 + 7 + 1+5 17 разрядов. Если генератор 1 выполнить на элементной базе ИС10О, то допустимо выбрать период следования синхроимпульсов СИ1 - СИ4 в 10О НС, что составит период между сдвигами имитируемых регистров величиf.y примерно 8 МКС. Это вполне приемлемое значение для использования, например, в устройствах функционального контроля логических узлов. Таблица П Формула изобретения 1. Многофункциональный генератор авоичных последовательностей, содержащий генератор тактовых импульсов, первый выход которого подключен к счетному входу счетчика адреса, первый установочный вход которого соединен с первым управляющим входом генератора, второй установочный вход - с выходом последнего разряда регистра, а выход - с адресным входом блока памяти программ, .ниформационный и управляющий входы которого соединены соответственно с первым информационным и вторым управляющим входами генератора, второй выход генератора тактовых импульсов подключен к входу записи блока памяти программ, выходы кода знака и кода номера разряда регистра соединены соответственно с первь0 1 входом первого сумматор по модулю два и входом дещифратора, выход которого подключен к информационному входу регистра, управляющий вход которого подключен к выходу первого сумматора по модулю два, второй вход которого подключен к выходу первого блока памяти, адресный и информационный входы которого подключены соответственно к выходам первого и второго мультиплексора, первые информационные входы которых подключены к первому адресному входу генератор, второй информационный вход второго мультиплексора соединен с выходом второго сумматора по модулю два, информационные входы которого соединены с выходами первой группы регистра, выходы второй группы которого подключены к выходу генератора, а вход синхроимпульсов регистра соединен с вторым выходом генератора тактовых импульсов, третий выход генератора тактовых импульсов соединен с входом записи первого блока памяти, выход первого разряда дешифратора соединен с первым входом третьего мультиплексора, второй вход которого подключен к входу логической единицы генератора, управл$пощие входы генератора тактовых импульсов третьего мультиплексора подключены к второму управляющему входу генератора, отличающий - с я тем, что, с целью расщирения функ-. циональных возможностей за счет форми рования псевдослучайных и/или регулярных последовательностей с заданными числом разрядов и законами формирования обратных связей,он дополнительно содержит четвертый и пятый мультиплексоры, второй и третий блоки памяти, счетчик по заданному модулю и фо1 лирователь ацреса, причем управляюшие. входы третьего и четвертого мультиплексора и третьего блока па- памяти подключены к второму управляющему входу генератора, выход кода номера имитируемого регистра блока памяти программ подключен к первому информационному входу четвертого мультиплексора, второй информационный выход которого соединен с вторым адресным входом генератора, вход логического нуля генератора соединен с первым информационным входом пятого мультиплексора, второй информационный вход которого соединен с выходом счетчика по заданному модулю установочный вход которого соединен с первым входом формирователя адреса и выходом третьего блока памяти, информационный вход когорогр соединен с выходом пятого мультиплексора, адресный вход - с адресным входом второго блока памяти и выходом четвертого мультиплексора, управляющий вход третьего блока пам$1Ти соединен с счетным : входом счетчика по заданному модулю, с управляющим входом первого блока памяти и выходом третьего мультиплексора, выход кода относительного адреса подключен к второму входу формирователя адреса, третий вход когорого соединен с входом модуля счетчика по заданному модулю и с выходом кода числа разрядов второго блока памяти, выход кода адреса первых разрядов которого подключен к .четвортрму входу фор« ирователя адреса, выход которого соединен с вторым информационным входом первого мультиплексора, информационный вход второго блока памяти соединен с вторым информационным входом генератора, входы записи второго и третьего блоков памяти и синхровход счетчика по заданному модулю соединены соответственно с первым, четвертым и вторык выходами генератора тактов-.DC импульсов.

2. Гонератор по п. 1, отличающий с я тем, что формирователь адреса содерн ит три сумматора и мультиплексор, вь1ход которого соединен с пергаым входом первого сумматора, второй вход когорого соединен с четвертым входом формирователя, а выход - с выходом формирователя, выход второго сумматора соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с первьп 4 входом второго сумматора и выходом третьего сумматора, первый и второй входы которого соединены с первым и вто{и 1м входами формирователя, третий вход которого соединен с вторым входом второго сумматора, выход переноса которого подключен к управляющему входу мультиплексора.

Источники информации, принятые BOi внимание при экспертизе

1.Псевдослучайные последователь ности и таблицы. ТИИЭР, т. 64, 1976,. № 12, с. 8О-95.

2.Патент США rit 4О470О8,

кл. 235-152, опублик. 1977 (прототип)

0ut.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

Авторы

Даты

1983-01-23—Публикация

1981-06-19—Подача