Изобретение относится к вычислительной технике и может быть использовано в системах передачи информации.

Целью изобретения является упрощение шифратора при обеспечении диалогового режима работы.

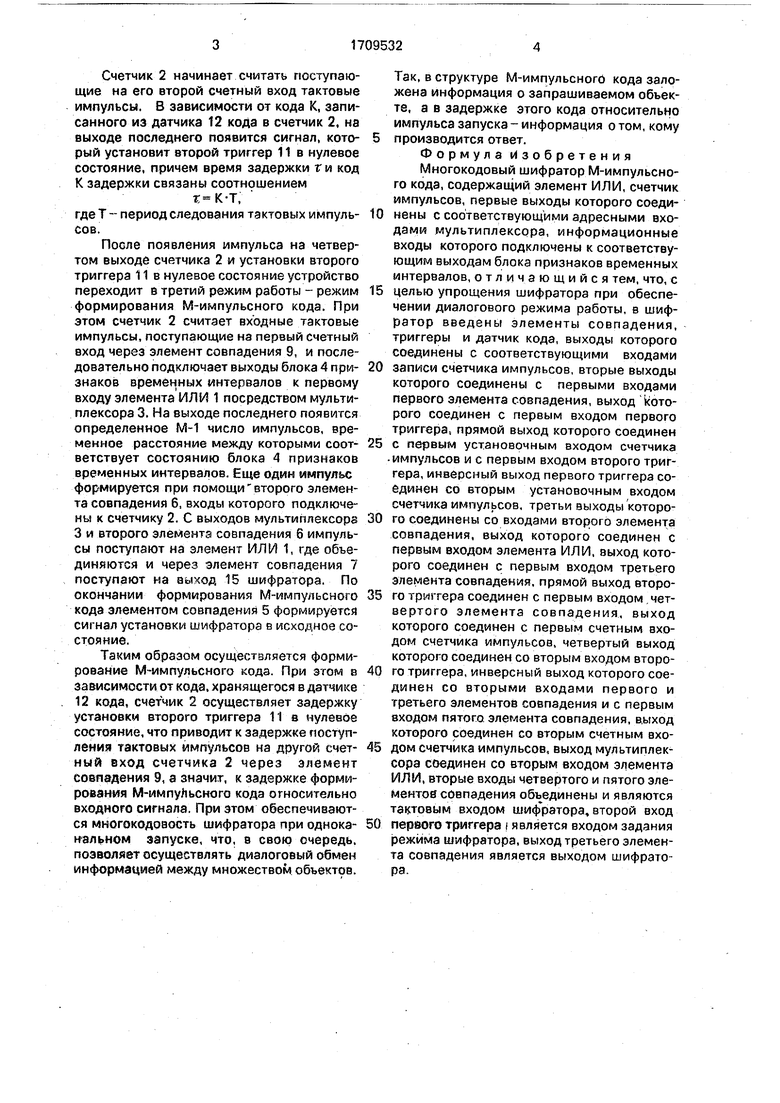

На чертеже представлена функциональная блок-схема шифратора.

Шифратор содержит элемент ИЛИ It счетчик 2 импульсов, мультиплексор 3, блок 4 признаков временных интервалов, первый - пятый элементы 5-9 совпадения, первый и второй триггеры 10 и 11 и датчик 12 кода, тактовый вход 13 и вход 14 задания режима шифратора, выход 15.

Шифратор работает следующим образом.

Шифратор может работать в трех режимах. В первом (исходном) режиме (состоянии) первый и второй триггеры 10 и 11 и счетчик 2 находятся в нулевом состоянии. При этом первый, третий и пятый элементы совпадения 5,7 и 9 открыты и удерживаются в этом состоянии вторым триггером 11.

Счетчик 2 не считает поступающие на его первый счетный вход через открытый элемент совладения 9 тактовые импульсы, так как удерживается в нулевом состоянии первым триггером 10. Сигнал Установка О на выходе элемента совпадения 5 не вырабатывается и импульсный код не поступает на выход 15 шифратора,так как счетчик 2 не считает.

С приходом сигнала на вход 14 шифратор переходит во второй режим работы режим формирования величины задержки. В этом режиме первый триггер 10 устанавливается в единичное состояние и фронтом выходного сигнала устанавливает в единичное состояние второй триггер 11. разрешает работу счетчика 2 и производит запись кода в cчetчик 2 из датчика 12 кода. При этом второй триггер 11 закрывает первый, третий и пятый элементы совпадения 5.7 и 9 и открывает четвертый элемент совпадения 8, в результате чего информация на выходе 15 шифратора отсутствует и сигнал Установка О не вырабатывается.

Счетчик 2 начинает считать поступающие на его второй счетный вход тактовые импульсы. В зависимости от кода К, записанного из датчика 12 кода в счетчик 2, на выходе последнего появится сигнал, который установит второй триггер 11 в нулевое состояние, причем время задержки г и код К задержки связаны соотношением

,

где Т- период следования тактовых импульсов.

После появления импульса на четвертом выходе счетчика 2 и установки второго триггера 11 в нулевое состояние устройство переходит в третий режим работы - режим формирования М-импульсного кода. При этом счетчик 2 считает входные тактовые импульсы, поступающие на первый счетный вход через элемент совпадения 9, и последовательно подключает выходы блока 4 признаков временных интервалов к первому входу элемента ИЛИ 1 посредством мультиплексора 3. На выходе последнего появится определенное М-1 число импульсов, временное расстояние между которыми соответствует состоянию блока 4 признакой временных интервалов. Еще один импульс формируется при помощи второго элемента совпадения 6, входы которого подключены к счетчику 2. С выходов мультиплексора 3 и второго элемента совпадения б импульсы поступают на элемент ИЛИ 1, где объединяются и через элемент совпадения 7 поступают на выход 16 шифратора. По окончании формирования М-импульсного кода элементом совпадения 5 формируется сигнал установки шифратора в исходное состояние.

Таким образом осуществляется формирование М-импульсного кода. При этом в зависимости от кода, хранящегося в датчике 12 кода, счетчик 2 осуществляет задержку установки второго триггера 11 в нулевое состояние, что приводит к задержке поступления тактовых импульсов на другой счетный вход счетчика 2 через элемент совпадения 9, а значит, к задержке формированмя М-импуМьсного кода огносительно входного сигнала. При этом обеспечиваются многокодовость шифратора при одноканал.ном запуске, что, в свою очередь, позволяет осуществлять диалоговый обмен информацией между множеством объектов.

Так, в структуре М-импульсногО кода заложена информация о запрашиваемом объекте, а в задержке этого кода относительно импульса запуска-информация о том, кому производится ответ.

Формула Изобретения Многокодовый шифратор М-импульсного кода, содержащий элемент ИЛИ, счетчик импульсов, первые выходы которого соединены с соответствующими адресными входами мультиплексора, информационные входы которого подключены к соответствующим выходам блока признаков временных интервалов, отличающийся тем, что, с целью упрощения шифратора при обеспечении диалогового режима работы, в шифратор введены элементы совпадения, триггеры и датчик кода, выходы которого соединены с соответствующими входами записи счетчика импульсов, вторые выходы которого соединены с первыми входами первого элемента совпадения, выход koToрого соединен с первым входом первого триггера, прямой выход которого соединен с первым установочным входом счетчика импульсов и с первым входом второго триггера, инверсный выход первого триггера соединен со вторым установочным входом счетчика импульсов, третьи выходы которого соединены со входами второго элемента совпадения, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом третьего элемента совпадения, прямой выход второго триггера соединен с первым входом .четвертого элемента совпадения, выход которого соединен с первым счетным входом счетчика импульсов, четвертый выход которого соединен со вторым входом второго триггера, инверсный выход которого соединен со вторыми входами первого и третьего элементов совпадения и с первым входом пятого элемента совпадения, в.ыход которого соединен со вторым счетным входом счетчика импульсов, выход мультиплексора соединен со вторым входом элемента ИЛИ, вторые входы четвертого и пятого элементов совпадения объединены и являются та1(:товым входом шифратора, второй вход первого триггера i является входом задания режима шифратора, выход третьего элемента совпадения является выходом шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1432527A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Счетчик с контролем ошибок | 1988 |

|

SU1575309A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для вывода информации | 1985 |

|

SU1285460A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-30—Публикация

1988-06-06—Подача