Изобретение относится к импульсной технике и может быть использовано для преобразования информации в кодерах цифровых систем кабельной и волоконнооптической связи.

Известен кодовый преобразователь для преобразования исходной кодовой последовательности 0000 в последовательность 0001 в кодерах СНДВ-п сигналов, содержащий регистр сдвига и элемент ИЛИ-НЕ, входы которого подключены к п-выходам регистра сдвига и информационному входу, линию задержки и формирователь короткого импульса, входы которых обьединены и подключены к тактовому входу устройства, а выходы соответственно к тактовому входу регистра сдвига и п-2 входу элемента ИЛИНЕ, выход которого подсоединен к единичному входу первого разряда регистра сдвига.

Известное устройство имеет ограниченные функциональные возможности, а именно отсутствует возможность полного преобразования в СНДВ-п или НДВ-п сигнал, устройство формирует только вставки V-типа, а также недостаточно технологично ввиду наличия подбираемой линии задержки.

Наиболее близким техническим решением к предлагаемому является кодовый преобразователе содержащий регистр сдвига, п-1 первых выходов которого подключены к входу управления Записьсдвиг регистра сдвига, вход первого разряда регистра сдвига подсоединен к источнику лог. 1, выходы остальных разрядов подключены к источнику лог. О, тактовый вход регистра сдвига является тактовым входом кодового преобразователя, а информационный вход регистра сдвига является информационным входом кодового преобразователя, выход п разряда регистра является выходом устройства.

Однако данный кодовый преобразователь имеет ограниченные функциональные возможности; он преобразует исходную кодовую последовательность 0000 в последовательности типа OOOV и не может производить полное преобразование исходной последовательности по алгоритму СНДВ-3 или СНДВ-п кода.

Цель изобретения - расширение функциональных возможностей преобразователя за счет дополнительного формирования входных кодов НДВ-п, АМ1, СНДВ-п.

Для достижения поставленной цели в устройство, содержащее регистр сдвига, п-1 первых выходов которого подключены к входу управления регистра сдвига, тактовый вход (ТАКТ) соединен с тактовым входом преобразователя, информационный вход подключен к информационному входу устройства (ИНФОРМ), входы разрядов с второго по п -1 соединены между собой и

5 подключены к шине нулевого потенциала, введены триггеры, элемент НЕ и буферный элемент, вход которого является входом выбора режима работы преобразователя, прямой выход буферного элемента соединен с

0 входами первого и п+1 разрядов регистра, выход п-го разряда которого соединен с входом элемента НЕ, первый выход которого соединен с информационным входом первого триггера и первым тактовым входом

5 второго триггера, информационный вход и выход которого обьединены и подключены к входу п-ого разряда регистра, инверсный выход буферного элемента соединен с установочным входом второго триггера, второй

0 выход элемента НЕ объединен с выходом 2л-ого разряда регистра и подключен к первому тактовому входу третьего триггера, информационный вход и инверсный выход которого объединены и подключены к первому тактовому входу четвертого триггера, прямой выход третьего триггера соединен с первым тактовым входом пятого триггера, выход первого триггера соединен с информационными входами четвертого и пятого

0 триггеров, тактовый вход первого триггера объединен с вторыми тактовыми входами второго - пятого триггеров и подключен к TascTOBOMy входу преобразователя, выходы четвертого и пятого триггеров являются вы5 преобразователя.

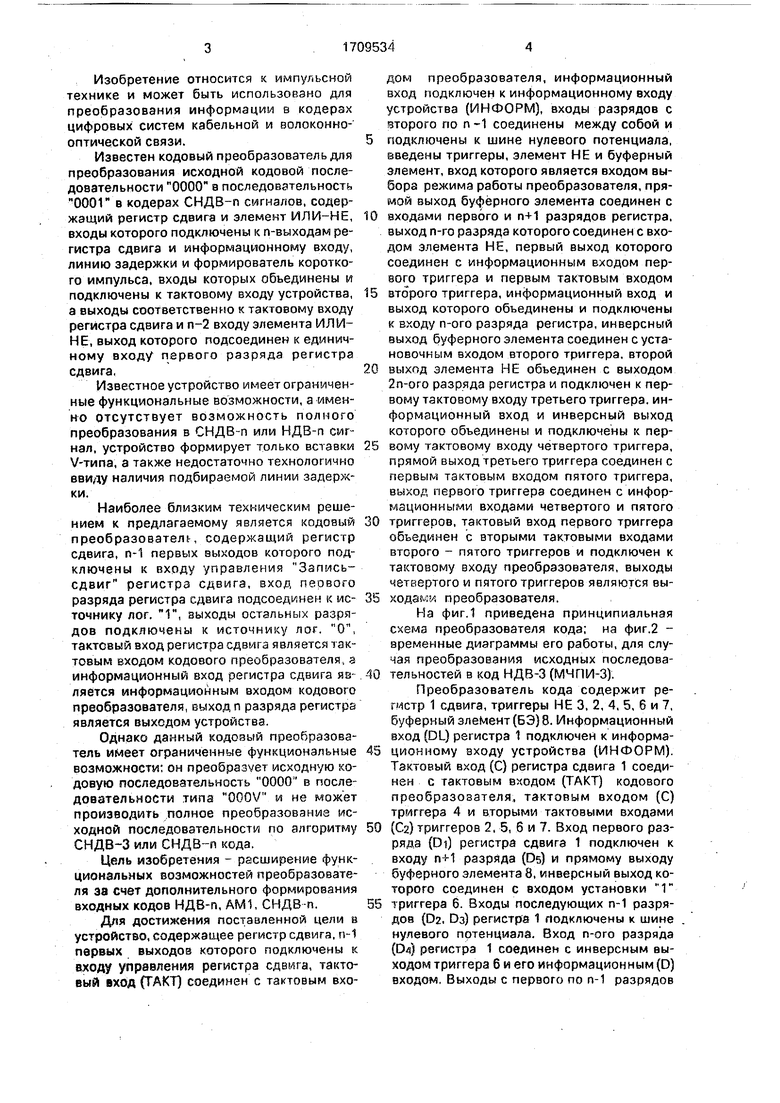

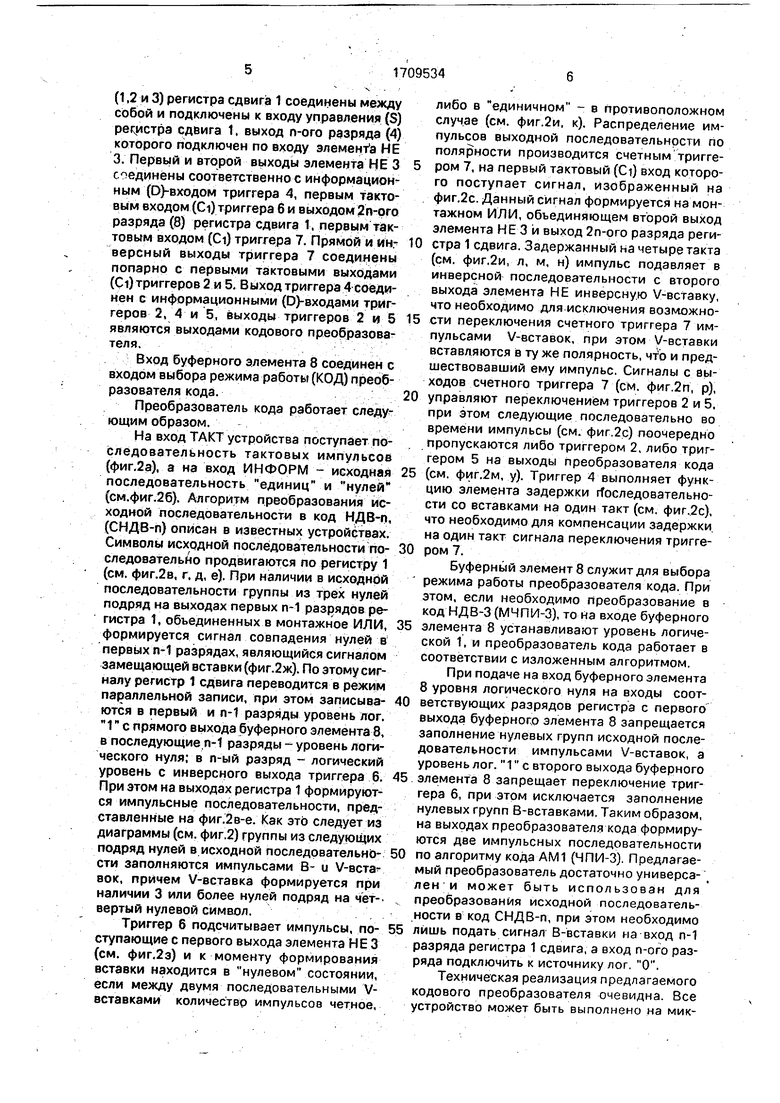

На фиг.1 приведена принципиальная схема преобразователя кода; на фиг.2 временные диаграммы его работы, для случая преобразования исходных последова0 тельностей в код НДВ-3 (МЧПИ-3).

Преобразователь кода содержит регистр 1 сдвига, триггеры НЕ 3, 2, 4, 5, 6 и 7, буферный элемент (БЭ) 8. Информационный вход (DL) регистра 1 подключен к информационному входу устройства (ИНФОРМ). Тактовый вход (С) регистра сдвига 1 соединен с тактовым входом (ТАКТ) кодового преобразователя, тактовым входом (С) триггера 4 и вторыми тактовыми входами

0 (Са) триггеров 2, 5, 6 и 7. Вход первого разряда (Di) регистра сдвига 1 подключен к входу п+1 разряда (Ds) и прямому выходу буферного элемента 8, инверсный выход которого соединен с входом установки 1

5 триггера 6. Входы последующих п-1 разрядов (D2, Оз) регистра 1 подключены к шине нулевого потенциала. Вход п-ого разряда (DA) регистра 1 соединен с инверсным выходом триггера 6 и его информационным (D) входом, Выходы с первого по п-1 разрядов

(1,2 и 3) регистра сдвига 1 соединены между собой и подключены к входу управления (S) регистра сдвига 1. выход п-ого разряда (4) которого подключен по входу элементе НЕ 3. Первый и второй выходы элемента НЕ 3 соединены соответственно с информационным (О)-входом триггера 4, первым тактовым входом (Ci) триггера б и выходом2п-рго разряда (8) регистра сдвига 1, первым тактовым входом (Ci) триггера 7. Прямой и имверсный выходы триггера 7 соединены попарно с первыми тактовыми выходами (Ci) триггеров 2 и 5, Выход триггера 4 соединен с информационными (Ь)-входами триггеров 2, 4 и 5, выходы триггеров 2 и 5 являются выходами кодового преорразователя.

Вход буферного элемента 8 соединен с входом выбора режима работы (КОД) преобразователя кода.

Преобразователь кода работает следуг ющим образом.

На вход ТАКТ устройства поступает последовательность тактовых импульсов (фиг.2а), а на вход ИНФОРМ - исходная последовательность единиц и нулей (см.фиг.26). Алгоритм преобразования исходной последовательности в код НуЦВ-п, (СНДВ-п) описан в известных устройствах. Символы исходной последовательности последовательно продвигаются по регистру 1 (см. фиг.2в, г. д, е). При наличии в исходной последовательности группы из трех нулей подряд на выходах первых п-1 раз(}ядов регистра 1, объединенных в монтажное ИЛИ, формируется сигнал совпадения нулей в первых разрядах, ЯВЛЯЮЩИЙСЯ сигналом замещающей вставки (фиг.2ж). По этому сигналу регистр 1 сдвига переводится в режим параллельной записи, при этом записываются в первый и п-1 разряды уровень лог. 1 с прямого выхода буферного элемента 8, в последующие.п-1 разряды- уровень логического нуля; в п-ый разряд - логический уровень с инверсного выхода триггера 6. При этом на выходах регистра 1 формируются импульсные последовательности, представленные на фиг.2в-е. Как это следует из диаграммы (см. фиг.2) группы из следующих подряд нулей в исходной последовательности заполняются импульсами В- и V-вста вок, причем V-вставка формируется при наличии 3 или более нулей подряд на чет-. вертый нулевой символ.,

Триггер 6 подсчитывает импульсы, поступающие с первого выхода элемента НЕ 3 (см. фиг.2з) и к моменту формирования вставки находится в нулевом состоянии, если между двумя последовательными Vвставками количество импульсов четное.

либо в единичном - в противоположном случае (см. фиг.2и, к). Распределение импульсов выходной последовательнрсти по полярности производится счетным триггером 7, на первый тактовый (Сi) вход которого поступает сигнал, изображенный на фиг.2с. Данный сигнал формируется на монтажном ИЛИ, объединяющем второй выход элемента НЕ 3 и выход 2п-ого разряда регистра 1 сдвига. Задержанный на четыре такта (см. фиг.2и, л, м, н) импульс подавляет в инверсной последовательности с второго выхода элемента НЕ инверсную V-вотавку, что необходимо для исключения возможности переключения счетного триггера 7 импульсами V-вставок, при этом у-вставки вставляются ia ту же полярность, что и предшествовавший ему импульс. Сигналы с выходов счетного триггера 7 (см. фиг.2п, р), управляют переключени ем триггеров 2 и 5, при этом следующие последовательно во времени импульсы (см. фиг.2с) поочередно пропускаются либо триггером 2, либо триггером 5 на выходы преобразователя кода (см. фиг.2м, у). Триггер 4 выполняет функцию элемента задержки гТоследовательности со вставками на один такт (см. фиг.2с), что необходимо для компенсации задержки на один такт сигнала переключения триггером 7.

Буфернь1й элемент 8 служит для выбора режима работы преобразователя кода. При этом, если необходимо преобразование в код НДВ-З(МЧПИ-З), то На входе буферного элемента 8 устанавливают уровень логической 1, и преобразователь кода работает в соответствии с изложенным алгоритмом.

При подаче на вход буферного элемента 8 уровня логического нуля на входы соответствующих разрядов регистра с первого выхода буферного элемента 8 запрещается заполнение нулевых групп исходной последовательности импульсами V-вставок, а уровень лог. 1 с второго выхода буферного элемента 8 запрещает переключение триггера б, при этом исключается заполнение нулевых групп В-вставками. Таким образом, на выходах преобразователя кода формируются две импульсных последовательности по алгоритму коДа АМ1 (ЧПИ-3). Предлагаемый преобразователь достаточно универса- лен и может быть использован для преобразования исходной последовательности в код СНДВ-п, при этом необходимо лишь подать сигнал В-вставки на вход п-1 разряда регистра 1 сдвига, а вход п-ого разряда подключить к источнику лог. О.

Техническая реализация предлагаемого кодового преобразователя очевидна. Все устройство может быть выполнено на микросхемах отечественной элементной базы. Так/например, в качестве регистра сдвига могут быть применены два универсальных регистра сдвига 500 ИР141, соединенных последовательно в 2 п-разрядный pernctp сдвига, в качестве триггеров - синхронные D-триггеры типа 500 ТМ131, в качестве элемента НЕ и буферного элемента микросхемы 100 ЛЕ211.

Предлагаемый преобразователь выгодно отличается от известного устройства {многообразием выполняемых функций, технологичностью и является универсальным устройством для формирования известных кодов с чередующейся полярностью импульсов НДВ-п {МЧПИ-3), AMI (ЧПИ-3), СНДВ-п.

Выходные триггеры 2 и 5 являются ключевыми элементами и при необходимости преобразования сигналов в импульсный код могут быть заменены элементами ИЛИ-НЕ, (И-НЕ).

Формул а изобретения Преобразователь 1):ода, содержащий 2т-разрядный регистр, информационный и тактовый входы которого являются соответственно информационным и тактовым входами преобразователя, входы второго (m-1)-ro разрядов регистра подключены к шине нулевого потенциала, выходы первого - (т-1)-го разрядов регистра объединены и подключены к управляющему входу регистра, отличающийся тем, что, с целью

расширения функциональных возможностей преобразователя путем дополнительного формирования выходных кодов НДВ-п, AMI, СНДВ-п, в него введены триггеры,

элемент НЕ и буферный элемент, вход которого является входом выбора режима работы преобразователя, прямой выход буферного элемента соединен с входами первого и (т+1)-гр разрядов регистра, выход

т-го разряда которого соединен с входом элемента НЕ, первый выход которого соединен с информационным входом первого триггера и первом тактовым входом второго триггера, информационный вход и выход

которого объединены и подключены к входу т-го разряда регистра, инверсный выход буферного элемента соединен с установочным входом второго триггера, второй выход элемента НЕ объединен с выходом 2т-го

разряда регистра и подключен к первому тактовому входу третьего триггера, информационный вход и инверсный выход которого объединены и подключены к первому тактовому входу четвертого триггера, прямой выход третьего триггера соединен с первым тактовым входом пятого триггера, выход первого триггера - с информационными входами четвертого и пятого триггеров, тактовый вход первого триггера

объединен с вторыми тактовыми входами второго - пятого триггеров и подключен к тактовому входу преобразователя, выходы четвертого и пятого триггеров являются выходами преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля достоверности передачи информации квазитроичным кодом | 1983 |

|

SU1104672A2 |

| Декодирующее устройство | 1984 |

|

SU1290532A1 |

| Способ обнаружения ошибок и устройство для его осуществления | 1989 |

|

SU1619412A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Устройство для записи и воспроизведения сигналов цифровой информации | 1982 |

|

SU1037336A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Датчик кода Морзе | 1981 |

|

SU1001496A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство для индикации экстремального значения последовательности цифровых величин | 1988 |

|

SU1529461A1 |

| Цифровое телевидение./Под ред- М.И.Кривошеева, М.: Связь, 1980 | |||

| с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-11—Подача