Изобретение относится к технике электросвязи и может использоваться дпя определения экстремального значения уровня ИКМ-кодированных сигналов в цифровых системах Г1ередачи информации .

Цель изобретения - обеспечение определения экстремального значения п уровней И 1-кодированных сигналов, где п 2 .

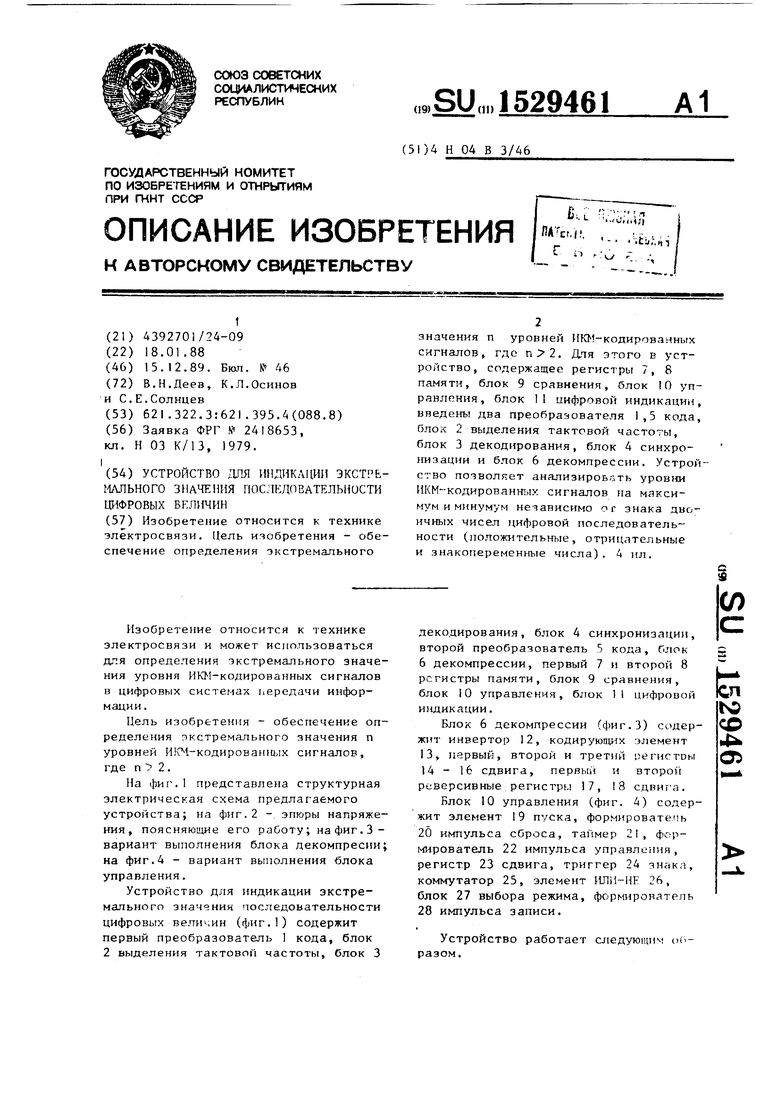

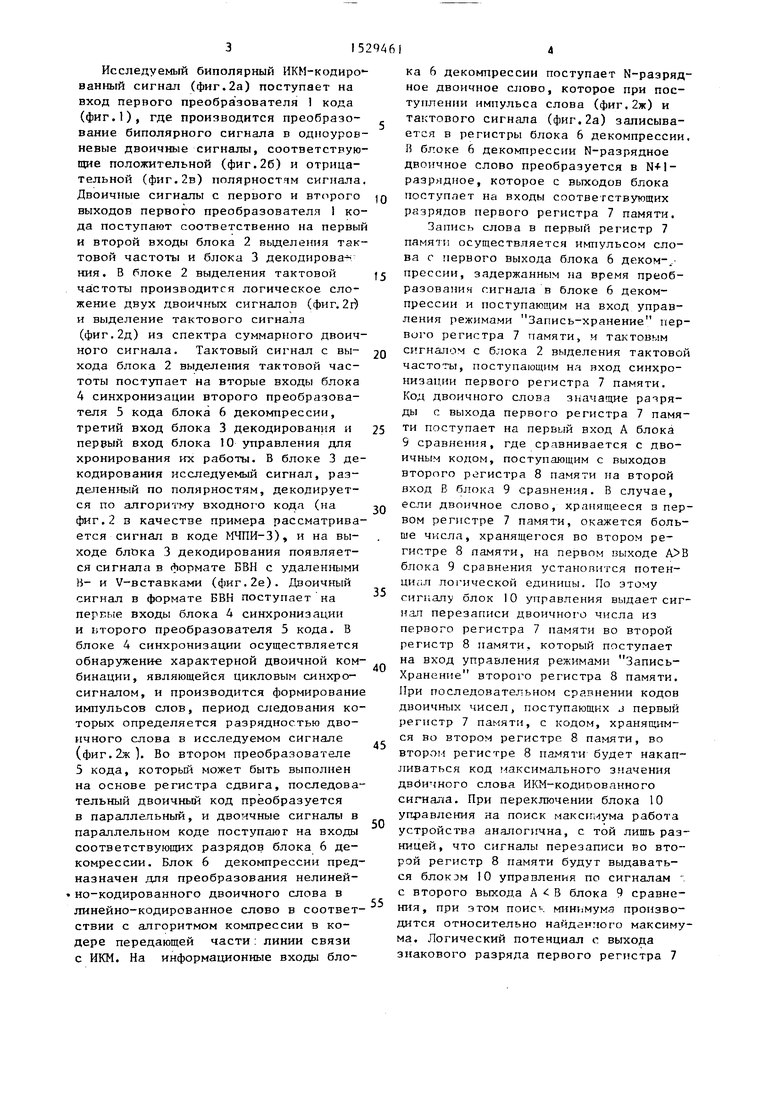

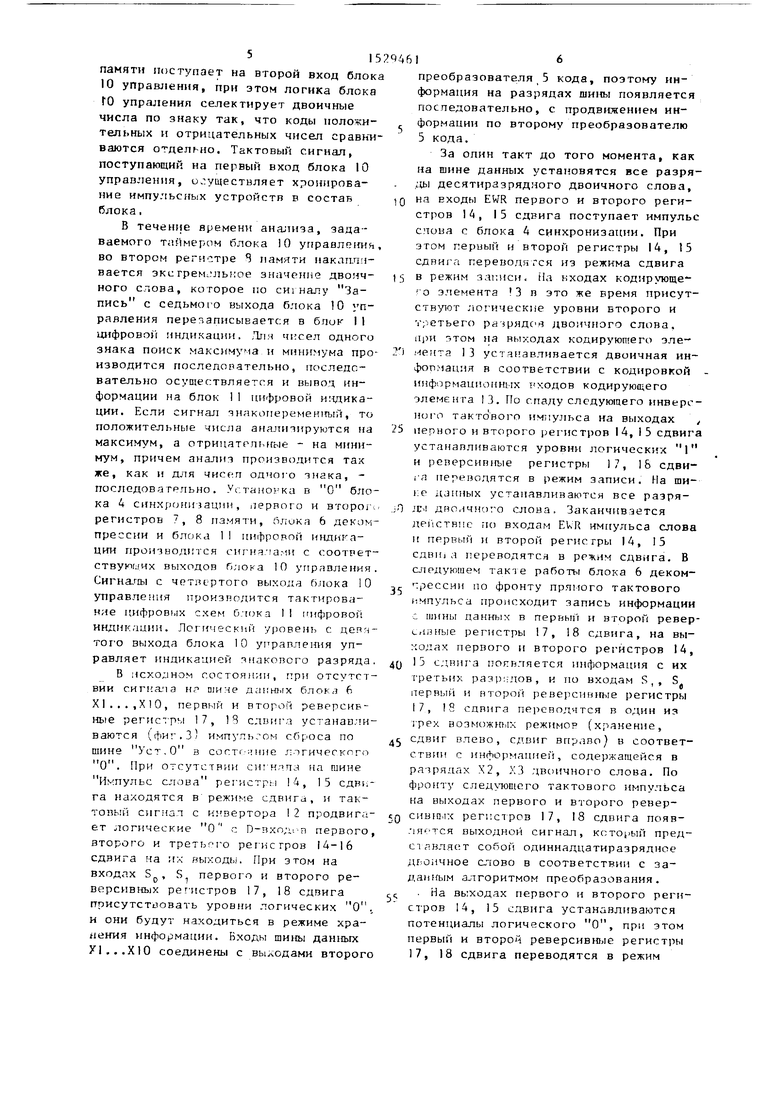

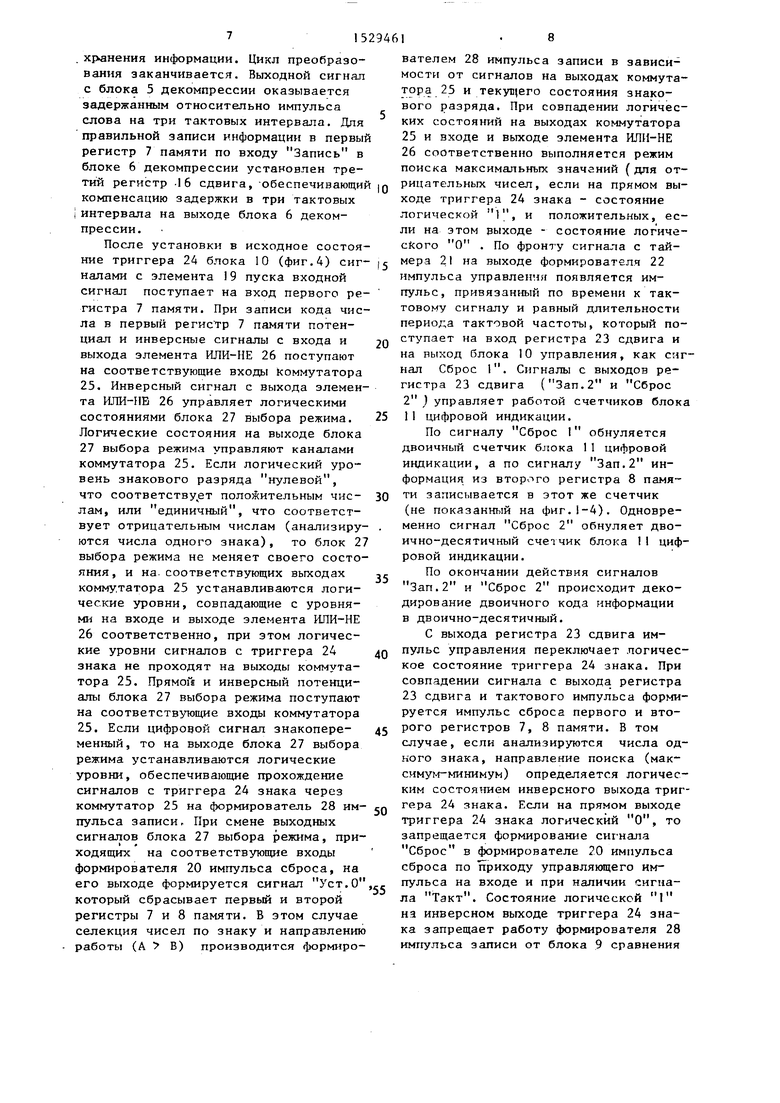

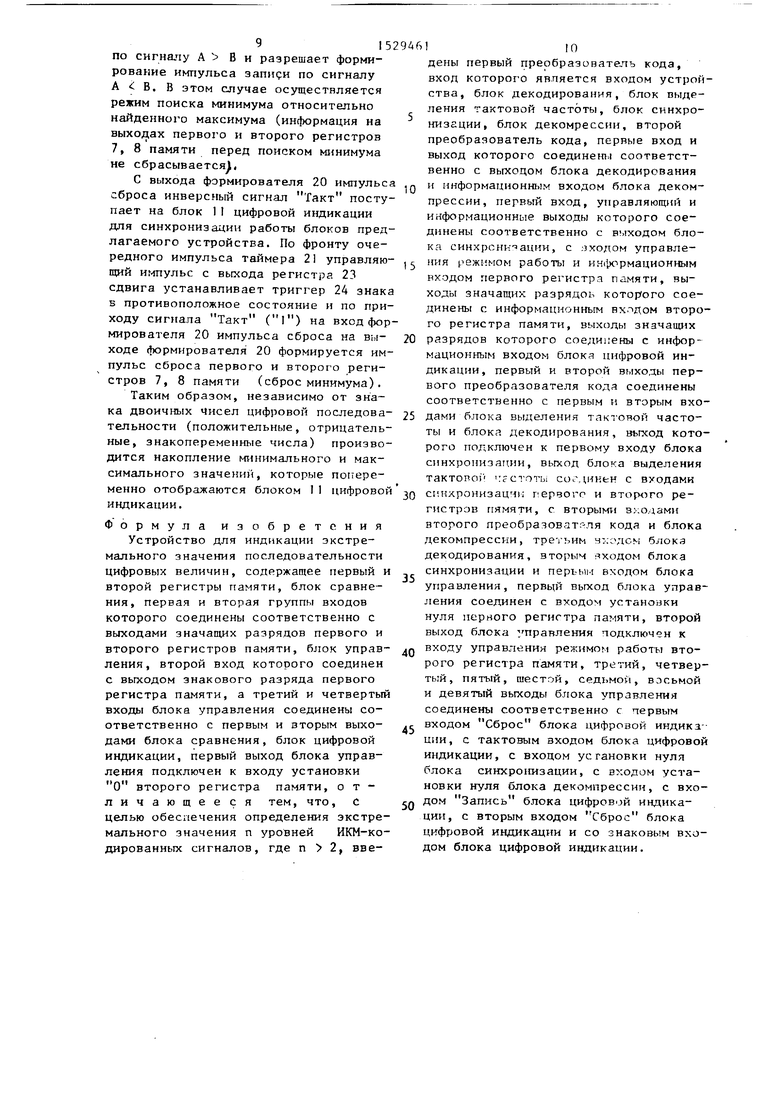

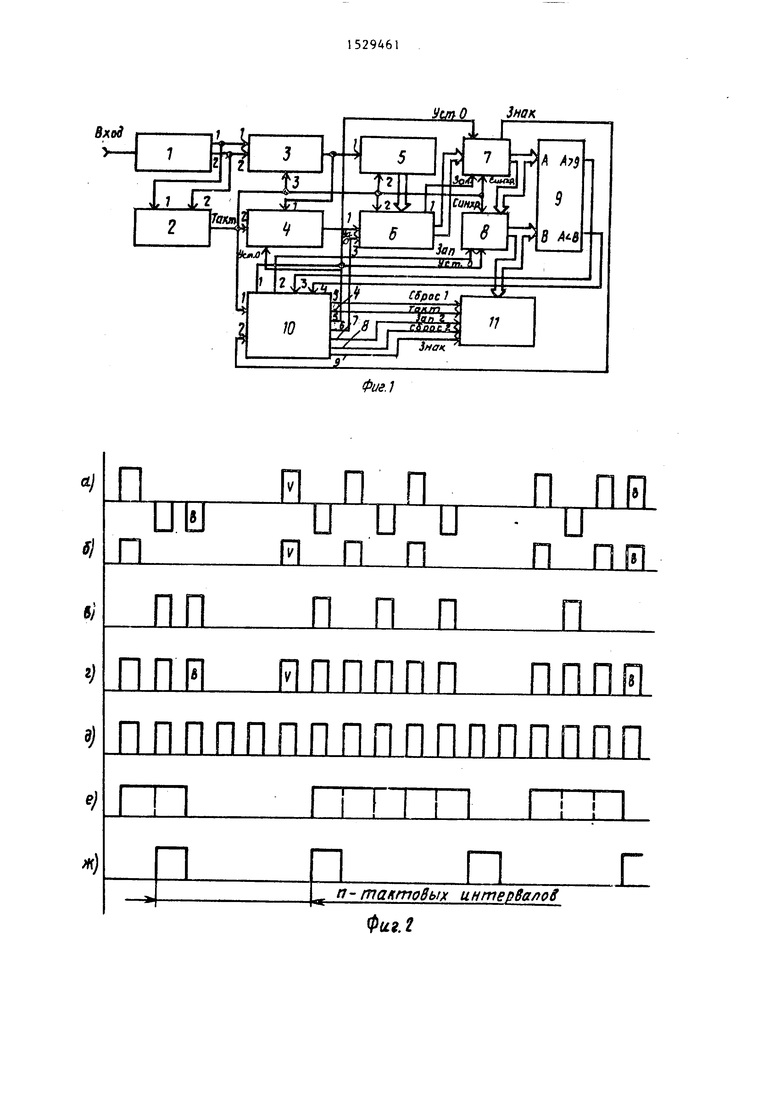

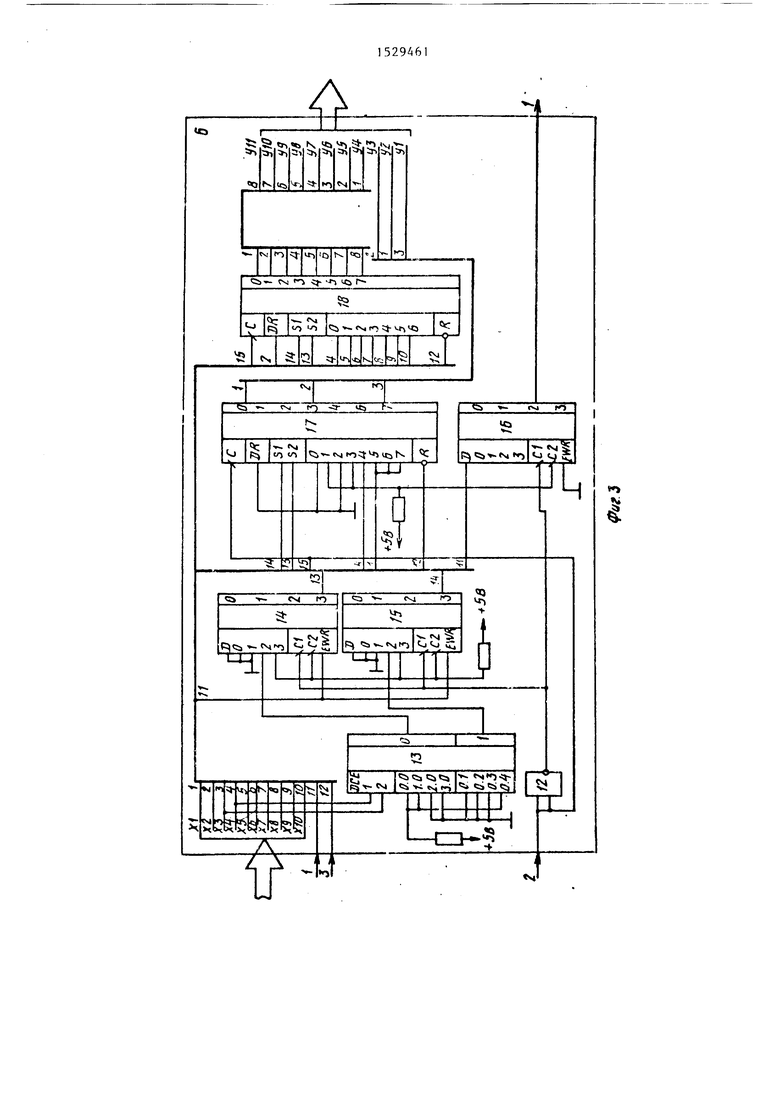

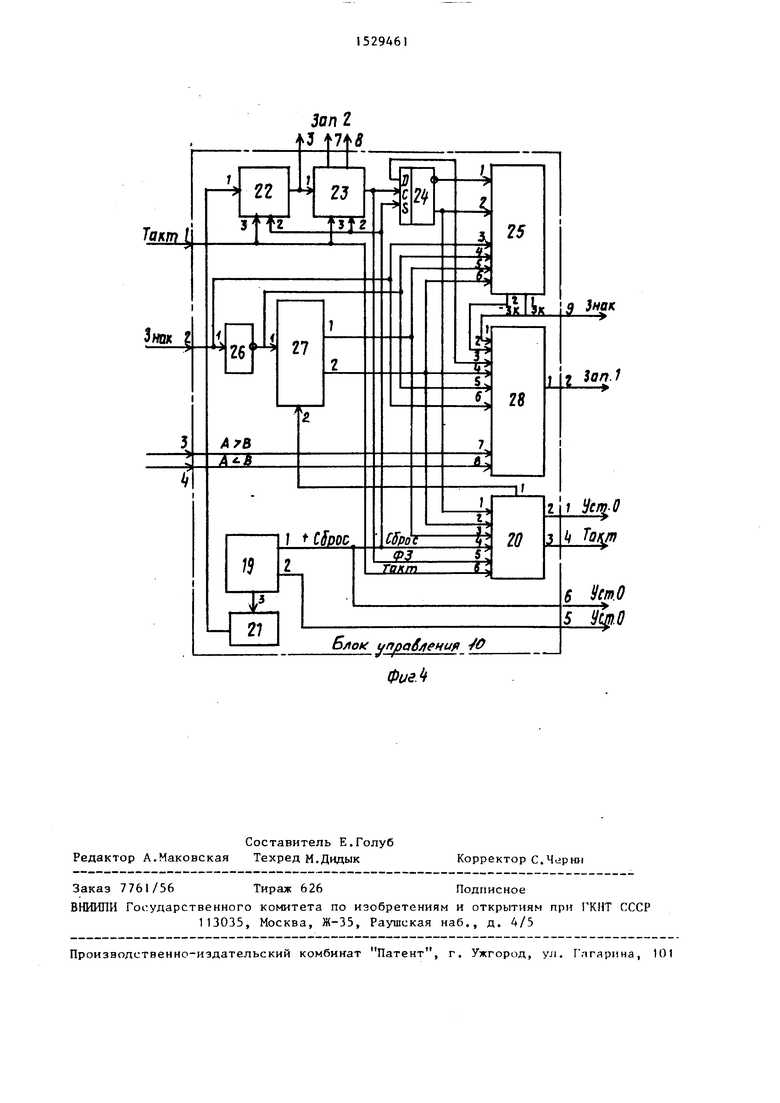

Ца фИ1 .1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - эпюры напряжения, поясняющие его работу; на фиг.3- вариант вьтолнения блока декомпресии; на фиг.4 - вариант выполнения блока управления.

Устройство для индикации экстремального значения последовательности цифровых величин (фиг.1) содержит первый преобразователь I кода, блок 2 выделения тактовой частоты, блок 3

декодирования, блок 4 синхронизации, второй преобразователь 5 кода, блок 6 декомпрессии, первый 7 и второй 8 регистры памяти, блок 9 сравнения, блок 10 управления, блок II цифровой индикации.

Блок 6 декомпрессии (фиг.З) содержит инвертор 12, кодируюпу х гзлемент 13, первый, второй и третий регистоы 14 - 16 сдвига, первый и BTopoft реверсивные регистры 17, 18 сдвиг-а.

Блок 10 управления (фиг. 4) содержит элемент 19 пуска, формирователь 20 импульса сброса, таймер 2I, фср- дарователь 22 импульса управления, регистр 23 сдвига, триггер 24 знакл, коммутатор 25, элемент ИЛИ-НЕ 26, блок 27 выбора режима, формирователь 28 импульса записи.

Устройство работает следующим образом.

fen ГО

СО

Ot

Исследуемый биполярныр ИКМ-кодиро - ванный сигнал (фиг.2а) поступает на вход первого преобра зователя 1 кода (фиг.1), где производится преобразование биполярного сигнала в одноуровневые двоичные сигналы, соответствующие положительной (фиг.26) и отрицательной (фиг.2в) полярностям сигнала Двоичные сигналы с первого и второго выходов первого преобразователя 1 кода поступают соответственно на первый и второй входы блока 2 выделения тактовой частоты и блока 3 декодирова- : НИН, В блоке 2 выделения тактовой ча стоты производится логическое сложение двух двоичных сигналов (фиг. 2г) и выделение тактового сигнала (фиг.2д) из спектра суммарного двоичного сигнала. Тактовый сигнал с выхода блока 2 выделе1гая тактовой частоты поступает на вторые входы блока

4синхронизации второго преобразователя 5 кода блока 6 декомпрессии, третий вход блока 3 декодирования и перрый вход блока 10 управления для хронирования их работы. В блоке 3 декодирования исследуемый сигнал, раз- депенный по полярностям, декодируется по алгоритму входного кода (на фиг.2 в качестве примера рассматривается сигнал в коде МЧПИ-3), и на выходе блока 3 декодирования появляется сигнала в формате БВН с удаленными В- и V-вставками (фиг.2е). Двоичный сигнал в формате БВН поступает на neppbie входы блока 4 синхронизации

и иторого преобразователя 5 кода. В блоке 4 синхронизации осуществляется обнаружение характерной двоичной комбинации, являющейся цикловым синхросигналом, и производится формирование импульсов слов, период следования которых определяется разрядностью двоичного слова в исследуемом сигнале (фиг.2ж). Во втором преобразователе

5кода, который может быть выполнен на основе регистра сдвига, последовательный двоичный код преобразуется

в параллепьный, и двоичные сигналы в параллельном коде поступают на входы соответствующих разрядов блока 6 де- комрессии. Блок 6 декомпрессии предназначен для преобразования нелиней- но-кодированного двоичного слова в линейно-кодированное слово в соответствии с алгоритмом компрессии в кодере передающей части: линии связи с ИКМ. На информационные входы бло0

5

0

5

0

5

0

5

0

5

ка 6 декомпрессии поступает N-разряд- ное двоичное слово, которое при поступлении импульса слова (фиг.2ж) и тактового сигнала (фиг.2а) записывается в регистры блока 6 декомпрессии,

8блоке 6 декомпрессии N-разрядное двоичное слово преобразуется в N+1- разрядное, которое с выходов блока поступает на входы соответствующих разрядов первого регистра 7 памяти.

Запись слова в первый регистр 7 памяти осуществляется импульсом слова г первого выхода блока 6 деком-.. прессии, задержанным на время преобразования сигнала в блоке 6 декомпрессии и поступающим на вход управления режимами Запись-хранение первого регистра 7 памяти, и тактовым сигналом с блока 2 выделения тактовой частоты, поступающим на яход синхронизации первого регистра 7 памяти. Код двоичного слова значащие разряды с выхода первого регистра 7 памяти поступает на первый вход А блока

9сравнения, где сравнивается с двоичным кодом, поступающим с выходов второго регистра 8 памяти на второй вход в блока 9 сравнения. В случае, если двоичное слово, хранящееся з первом регистре 7 памяти, окажется больше числа, хранящегося во втором регистре 8 памяти, на первом выходе блока 9 сравнения установится потенциал логической единицы. По зтому сигналу блок 10 управления выдает сигнал перезаписи двоичного числа из первого регистра 7 памяти во второй регистр 8 памяти, который поступает на вход управления режимами Запись- Хранение второго регистра 8 памяти. При последовательном сравнении кодов двоичных чисел, поступающих j первый регистр 7 памяти, с кодом, хранящимся во втором регистре 8 памяти, во BTOpoi-i регистре 8 памяти будет накапливаться код аксимапьного значения двоичного слова ИКМ-кодированного сигнагт. При переключении блока 10 управления на поиск максимума работа устройства аналогична, с той лишь разницей, что сигналы перезаписи во второй регистр 8 памяти будут выдаваться блоком 10 управления по сигналам v с второго выхода А В блока 9 сравнения, при этом поиск мин11мума производится относительно найденного максимума. Логический потенциал с выхода знакового разряда первого регистра 7

515

памяти поступает на второй вход блока 10 управления, при этом логика блока fO упраления селектирует двоичные числа по знаку так, что коды положительных и отрицательных чисел сравки- ваются отдельно. Тактовый сигнал, поступающий на первый вход блока 10 управления, о.:уществляет хронирование импульсных устройств в состав блока,

В течение яремени анализа, задаваемого таймером блока 10 угфавления во втором реги : тре Я памяти накапливается экс значение двоич- ного слова, которое но сигналу Запись с седьмого выхода блока 10 управления перезаписывается в блок I1 цифровоГг индикации. ,1пя Ч1;сел одного знака поиск максимума и минимума про- изводится последовательно, последовательно осуществляется и вывод информации на блок 1 1 цифровой и. вдика- ции. Если сигнал -энакоперемент);), то положительные числа анализируются на максимум, а отрнцатоп11(сые - на минн- мум, причем анализ производится так же, как и для чисел одного знака, - последовательно. Устаио1 ка в С блока 4 синхронизации, iiepBoro и второго регистров 7, 8 памяти, блика 6 декомпрессии и блока 1 I ци|}1ровой И1щика- ции производится сигня-чами с соотрет- ствуюыих выходов Гъ шка 10 управления Сигна.ггы с четвертого выхода блока 10 управления 1троизподится тактирование цифровых схем блока 1I цифровой индикации. Лог {ческий уровен) с девятого выхода блока 10 управлет1я управляет индикацией знакового разряда

В мсхолном состоянии, при отсутствии сиг ;а-па Hf иине блекл 6 Х1...,Х10, первый и втором реверсивные регис ры 17, 18 сдвига устанавливаются (.фиг.З) импуль. ом сброса по шине Уст. о в сост( ;;ние логическпго О. При отсутствии на шине Импульс cjroBa регистры 14, 15 сдвига находятся в режиме сдвига, и так- сигнал с инвертора 1 2 продвига- ет логические О с П-зход; П первого второго и третьего рег исгров 14-16 сдвига на их ньгходьк При этом на входах Sp, S первого и второго ре- BepcHBHbjx регистров 17, 18 сдвига присутствовать уровни логических О и они будут находиться в режиме хранения информации. Входы шины данных У1,..Х10 соединены с вь1лодами второго

6

5 5 П ц

г Q ;

5

I6

преобразователя,5 кода, поэтому информация на разрядах шины появляется последовательно, с продвижением информации по второму преобразователю 5 кода.

За один такт до того момента, как на шине данных установятся все разряда десятиразрядного двоичного слова, на входы EWR первого и второго регистров 14, 15 сдвига поступает импульс слона с блока 4 синхронизации. При этом парный и второй регистры 14, 15 сдви1 а переводя гея из режима сдвига в режим закиси. На входах кодирующего элемента 3 п это же время присутствуют логнческп е уровни второго и третьего рачрядс Я двоичного слова, при Г5ТОМ fia выходах кодирующего эле- 1-1еита 1 3 устанавливается двоичная ин- фогмация в соответствии с кодировкой - информационных рходов кодирующего элемента 13. По спаду следующего инверс- нсл о такто вого им)ульса на выходах / первого и второго регистров 14, 15 сдвига устанавливаются уровни логических 1 н реверсивные регистры 17, 18 сдви- гя иереиодятся в режим записи. На ши- i;e данных устанавливаются все разря- 1ЦЛ дг О,1чного (глова. Заканчивается aeiicTHHc по входам EWR импульса слова и первый и второй регистры 14, 15 СДВИ1а переводятся в режим сдвига. В следующем таК1е работы блока 6 декомпрессии по фронту прямого тактового импульса происходит запись информации с шины данных в первый и второй ревер- си;зные регистрь: 17, 18 сдвига, на выходах первого и второго регистров 14, 15 с;;вига появляется информация с их г ретьих разр;;лов, и по входам S,, S первый и второй реверс1ии1ые регистры 17, 18 сдвига переводятся в один из грех возмож№ 1х режимов (хранение, сдвиг влево, сдвиг вправо) в соответ- СТВ1П с информагшей, содержащейся в разрядах Х2, ХЗ двоичног о слова. По фронту след тощего тактового импульса на выходах первого и второго ревер- сивю,1Х регистров 17, 18 сдвига появ- .1яотся выходной сигнал, который пред- стг шляс-т собой одиннадцатиразрядное двоичное слово в соответствии с за- дашгым алгоритмом преобразования.

. На выходах первого и второго регистров 14, 15 сдвига устанавливаются потенциалы логического О, при этом первый и второй реверсивш ю регистры 17, 18 сдвига переводятся в режим

715

Х1 анения информации. Цикл преобразования заканчивается. Выходной сигнал с блока 5 декомпрессии оказывается задержанным относительно импульса слова на три тактовых интервала. Для правильной записи информации в первый регистр 7 памяти по входу Запись в блоке 6 декомпрессии установлен третий регистр .16 сдвига, -обеспечивающий компенсацию задержки в три тактовых j интервала на выходе блока 6 декомпрессии.

После установки в исходное состояние триггера 24 блока 10 (фиг.4) сиг- налами с элемента 19 пуска входной сигнал поступает на вход первого ре- гистра 7 памяти. При записи кода числа в первый регистр 7 памяти потенциал и инверсные сигналы с входа и выхода элемента ИЛИ-НЕ 26 поступают на соответствующие входы kOMMyTaTopa 25. Инверсный сигнал с выхода элемента ИЛИ-НБ 26 управляет логическими состояниями блока 27 выбора режима. Логические состояния на выходе блока 27 выбора режима управляют каналами коммутатора 25. Если логический уровень знакового разряда нулевой, что соответству ет положительным чис- лам, или единичный, что соответствует отрицательным числам (анализиру- ются числа одного знака), то блок 27 выбора режима не меняет своего состояния, и на- соответствующих выходах коммутатора 25 устанавливаются логические уровни, совпадающие с уровнями на входе и выходе элемента ИЛИ-НЕ 26 соответственно, при этом логические уровни сигналов с триггера 24 знака не проходят на выходы коммутатора 25. Прямой и инверсный потенциалы блока 27 выбора режима поступают на соответствующие входы коммутатора 25. Если цифровой сигнал знакопере- менный, то на выходе блока 27 выбора режима устанавливаются логические уровни, обеспечивающие прохождение сигналов с триггера 24 знака через коммутатор 25 на формирователь 28 им- пульса записи. При смене выходных сигналов блока 27 выбора режима, приходящих на соответствующие входы формирователя 20 импульса сброса, на его выходе формируется сигнал Уст.О который сбрасывает первый и второй регистры 7 и 8 памяти. В этом случае селекция чисел по знаку и направлению работы (А В) производится формиро1 8

вателем 28 импульса записи в зависимости от сигналов на выходах коммутатора 25 и текуп(его состояния знакового разряда. При совпадении логических состояний на выходах коммутатора

25и входе и выходе элемента ИЛИ-НЕ

26соответственно выполняется режим поиска максимальных значений ( для отрицательных чисел, если на прямом выходе триггера 24 знака - состояние логической 1, и положительных, если на этом выходе - состояние логичеckoro О

По фронту сигнала с таймера 21 на выходе формирователя 22 импульса управлении появляется импульс, привязанный по времени к тактовому сигналу и равный длительности периода тактовой частоты, который поступает на вход регистра 23 сдвига и на выход блока 10 управления, как сигнал Сброс 1. Сигналы с выходов регистра 23 сдвига (Зап.2 и Сброс 2 ) управляет работой счетчиков блока 11 цифровой индикации.

По сигналу Сброс I обнуляется двоичный счетчик блока 11 цифровой индикации, а по сигналу Зап.2 информация из второго регистра 8 памяти записывается в этот же счетчик (не показанный на фиг.1-4). Одновременно сигнал Сброс 2 обнуляет двоично-десятичный счетчик блока 11 цифровой индикации.

По окончании действия сигналов Зап.2 и Сброс 2 происходит декодирование двоичного кода информации в двоично-десятичный.

С выхода регистра 23 сдвига импульс управления переключает логическое состояние триггера 24 знака. При совпадении сигнала с выхода регистра 23 сдвига и тактового импульса формируется импульс сброса первого и второго регистров 7, 8 памяти. В том случае, если анализируются числа одного знака, направление поиска (максимум-минимум) определяется логическим состоянием инверсного выхода триггера 24 знака. Если на прямом выходе триггера 24 знака логический О, то запрещается формирование сигнала Сброс в формирователе 20 импульса сброса по Приходу управляющего им- пульса на входе и при наличии сигнала Такт. Состояние логической 1 на инверсном выходе триггера 24 знака запрещает работу формирователя 28 импульса записи от блока 9 сравнения

9152946

по сигналу А В и разрешает формирование импульса запи(;и по сигналу А i В. В этом случае осуществляется режим поиска минимума относительно найденного максимума (информация на выходах первого и второго регистров 7, 8 памяти перед поиском минимума не сбрасывается.

С выхода формирователя 20 импульса

10

сброса инверсный сигнал Такт поступает на блок 1I цифровой индикации для синхронизации работы блоков предлагаемого устройства. По фронту очередного импульса таймера 21 управляю- щий иг-тульс с выхода регистра 23 сдвига устанавливает триггер 24 знака в противоположное состояние и по приходу сигнала Такт (I) на вход формирователя 20 импульса сброса на вы- ходе формирователя 20 формируется импульс сброса первого и второго регистров 7, 8 памяти (сброс минимума). Таким образом, независимо от знака двоичных Чисел цифровой последова- тельности (положительные, отрицательные, знакопеременные числа) производится накопление минимального и максимального значении, которые попеременно отображаются блоком 11 цифровой индикации.

Формула изобретения

Устройство для индикации экстремального значения последовательности цифровых величин, содержащее первый и второй регистры памяти, блок сравнения, первая и вторая группы входов которого соединены соответственно с выходами значащих разрядов первого и второго регистров памяти, блок управ- ления, второй вход которого соединен с выходом знакового разряда первого регистра памяти, а третий и четвертый входы блока управления соединены соответственно с первым и вторым выхо- дами блока сравнения, блок цифровой индикации, первый выход блока управления подключен к входу установки О второго регистра памяти, отличающееся тем, что, с целью обеспечения определения экстремального значения п уровней ИКМ-ко- дированных сигналов, где п 2, вве

5 Q

, Q 0

I10

дены первый преобразователь кода, вход которого является входом устройства, блок декодирования, блок выделения тактовой частоты, блок синхронизации, блок декомрессии, второй преобразователь кода, первые вход и выход которого соединены соответственно с выходом блока декодирования и информационным входом блока декомпрессии, первый вход, управляющий и информационные выходы которого соединены соответственно с выходом блока синхрсни ации, с лходом управления режимом работы и инИрормационным входом первого регистра памяти, выходы значащих разрядоь которого соединены с информационным входом второго регистра памяти, выходы значащих разрядов которого соедиь ены с информационным входом блока цифровой индикации, первый и второй выходы первого преобразователя кодя соединены соответственно с первым и вторым входами блока выделения тактовой частоты и блока декодирования, выход которого подключен к первому входу блока синхронизации, выход блока выделения тактопо) УсСтоты сос-динен с входами синхронизацч ; первого и регистров пямяти, с вторыми в :одами второго преобразоватг ля кода и блока декомпрессии, тре 1 ьим н-;одсм блока декодирования, вторым входом блока синхронизации и перъым входом блока управления, первый выход блока управления соединен с входом установки нуля первого регистра памяти, второй выход блока управления подключен к входу управления режимом работы второго регистра памяти, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока управления соединены соответственно с первым входом Сброс блока цифровой индика-- ции, с тактовым входом блока цифровой индикации, с входом установки нуля блока синхронизации, с входом установки нуля блока декомпрессии, с входом Запись блока цифровой индикации, с вторым входом Сброс блока цифровой индикации и со знаковым входом блока цифровой индикации.

У CM О

Знак

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С НЕЛИНЕЙНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ (ИКМ) | 1998 |

|

RU2143790C1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| СПОСОБ КОМПРЕССИИ-ДЕКОМПРЕССИИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2488960C2 |

Изобретение относится к технике электросвязи. Цель изобретения - обеспечение определения экстремального значения N уровней ИКМ-кодированных сигналов, где N*982. Для этого в устройство, содержащее регистры 7, 8 памяти, блок 9 сравнения, блок 10 управления, блок 11 цифровой индикации, введены два преобразователя 1, 5 кода, блок 2 выделения тактовой частоты, блок 3 декодирования, блок 4 синхронизации и блок 6 декомпрессии. Устройство позволяет анализировать уровни ИКМ-кодированных сигналов на максимум и минимум независимо от знака двоичных чисел цифровой последовательности (положительные, отрицательные и знакопеременные числа). 4 ил.

ii Г

Ттт

Фиг, 2

б/totf unpaSjifHufl / ФиеМ

S Ует.О

.O

| ГАЗОСТАТ | 2009 |

|

RU2418653C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-01-18—Подача