Изобретение относится к области вычислительной техники и предназначено для выполнения операции преобразования последовательного двоичного кода (слова), принадлежащего ряду длин, в параллельно-последовательный код с выдачей фрагментами (слогами) в сопровождении кода номера фрагмента и сигналов готовности и синхронизации фрагмента и формирования сигналов контроля функционирования (информационной ошибки при четном числе единиц в принятом коде и сбоя битовой синхронизации при отклонении разрядности принятого кода от выбранного ряда длин) и готовности результата операции (окончания операции) с помощью обнаружения паузы с программируемым порогом.

Изобретение может быть использовано при построении устройств для ввода информации типа [1] и контроллеров локальной сети (КЛС), например КЛС на основе ГОСТ 18977-79 и РТМ 1495-75, по протоколам, которые являются правилами обмена информацией [2, с.57-64] между станциями локальной сети (СЛС) по мультиплексной и/или раздельным линиям связи сообщениями (последовательными двоичными кодами в ряде длин { 16, 24, 32} в битах младшими разрядами (битами) вперед и старшим разрядом контроля четности количества единиц в младших разрядах), разделенными между собою паузами длительностью 4-40 периодов Т частоты следования импульсов битовой синхронизации передачи сообщения.

В составе современной СЛС можно выделить (см., например, в [2] на с.221 рис. 5.9) ядро (содержит процессор или однокристальную электронную вычислительную машину (ЭВМ), схему синхронизации и начальной установки и комбинированную память (в общем случае содержит ОЗУ - оперативное запоминающее устройство, ДОЗУ - двухпортовое ОЗУ, ПЗУ - постоянное запоминающее устройство и РПЗУ - репрограммируемое ПЗУ)), КЛС (содержит устройство для ввода информации типа [1], устройство для вывода информации и устройство управления обменом (УУО) и синхронизацией (блок связи с подсистемой) для взаимосинхронизации и управления КЛС в целом), функционально ориентированные устройства для ввода-вывода информации в процессе взаимодействия СЛС с внешними объектами (пультом оператора, смежными системами, исполнительными устройствами, датчиками событий в объектах управления и т.п.), источник питания и системную магистраль (Q-BUS, ISA, VME либо другую) для обмена информацией между составными частями СЛС под управлением ЭВМ.

В общем случае составными частями устройства для ввода информации являются приемник (одноканальный или многоканальный) самосинхронизирующегося последовательного двоичного кода, декодер для формирования последовательного двоичного кода и импульсов битовой синхронизации и преобразователь последовательного двоичного кода в параллельный или параллельно-последовательный код (блок бита/слова), а устройство для вывода информации в каждом канале содержит преобразователь параллельного двоичного кода в последовательный двоичный код (блок слова/сообщения), кодер и передатчик.

Для рационального распределения в СЛС функций между аппаратно-программными средствами преобразователь последовательного двоичного кода в параллельно-последовательный код (как составная часть КЛС, входящая в СЛС) должен с помощью УУО гибко управляться от ЭВМ и быть максимально инвариантным к типу системной магистрали и протоколам локальной сети, т.е. при совершенствовании КЛС варьируемыми частями должны быть в основном УУО, приемники, передатчики, кодеры и декодеры.

Следует отметить, что при построении цифровой аппаратуры использование для передачи параллельно-последовательного кода (его называют также последовательно-параллельным кодом) позволяет экономить оборудование [3, с.66-69] , а сама операция преобразования последовательного двоичного кода в параллельный (или параллельно-последовательный) код реализуется тривиально, в частности на простейшем регистре типа 1533 ИР8 с последовательным входом и параллельным байтовым выходом или универсальном байтовом регистре типа 1533 ИР24 для двунаправленного обмена информацией как последовательными, так и параллельными кодами - см., например, [4, с.103].

Однако в КЛС каждой операции приема сообщения должна предшествовать процедура обнаружения паузы для подготовки устройства для ввода информации к выполнению очередной операции, а процесс выполнения каждой операции следует контролировать (например, формировать сигналы информационной ошибки при четном числе единиц в принятом коде и сбоя битовой синхронизации при отклонении разрядности принятого кода от выбранного ряда длин).

В этой связи создание простого преобразователя последовательного двоичного кода в параллельно-последовательный код с широкими функциональными возможностями, обеспечивающими гибкую управляемость от ЭВМ при максимальной независимости как от типа системной магистрали и способов обмена информацией между ЭВМ и составными частями КЛС, так и протоколов локальной сети, представляет, на наш взгляд, актуальную техническую задачу, разрешение которой позволит повысить качество разрабатываемых КЛС, в том числе и устройств типа [1] , поддерживающих в локальной сети при минимальных аппаратурных затратах высокую достоверность функционирования при обмене последовательными двоичными кодами в выбранном ряде длин, например в битовом ряде

{n}={8, 16,...,120, 128}. (1)

Достоверность функционирования - свойство цифрового устройства, характеризующее способность средств контроля признать выходной результат работы устройства правильным или ошибочным с помощью аппаратно-программных средств контроля [5, с.6], обеспечивающих его контролепригодность. Контролепригодность - свойство устройства, обуславливающее приспособленность контроля его технического состояния в процессе изготовления и эксплуатации [5, с.153]. Именно контролепригодность дает возможность получить на практике необходимую достоверность функционирования систем передачи обработки информации и управления [6, с.12], которые в современной аппаратуре являются также абонентами (или станциями) локальных сетей.

Основным недостатком известных преобразователей [7-10] для применения их в современных КЛС является ограниченность или узкая специализация их функциональных возможностей.

Действительно, n-разрядный преобразователь [7] функционально эквивалентен регистру типа 1533 ИР8, (n+2)-разрядный преобразователь [9] функционально также эквивалентен регистру 1533 ИР8, за исключением того, что в нем два старших разряда используются для контроля битовой синхронизации при приеме n-разрядного кода, а преобразователи [8] и [10] специализированы узко, поскольку преобразователь [8] предназначен для преобразования в параллельный код последовательного комбинированного кода, а преобразователь [10] - для преобразования последовательного двоичного кода в двоично-десятичный код.

Из известных технических решений наиболее близким к предлагаемому является преобразователь, входящий в состав устройства [1] и содержащий n-разрядные регистр сдвига и буферный регистр параллельного кода, суммирующий счетчик, триггер, элемент И-НЕ, вход последовательного двоичного кода, соединенный с информационным входом регистра сдвига, вход импульсов битовой синхронизации, соединенный с тактовым входом регистра сдвига и счетным входом суммирующего счетчика, выход переполнения которого соединен с входом установки триггера и входом записи буферного регистра, кодовый выход параллельного кода, являющийся выходом буферного регистра, кодовый вход которого соединен с кодовым выходом регистра сдвига, вход сброса готовности результата операции, соединенный с входами сбросов буферного регистра и триггера, выход сигнала готовности результата операции, соединенный с выходом триггера и первым входом элемента И-НЕ, тактовый вход, соединенный с вторым входом элемента И-НЕ, выход которого соединен с входами сброса регистра сдвига и суммирующего счетчика.

Преобразователь устройства [1] работает следующим образом.

Перед началом выполнения очередной операции преобразования он находится в исходном состоянии (режиме паузы) - регистр сдвига, буферный регистр, суммирующий счетчик и триггер сброшены в нулевые состояния.

При поступлении последовательная информация передается в регистр сдвига по импульсам битовой синхронизации, которые подсчитываются суммирующим счетчиком. Если регистр сдвига полон, то суммирующий счетчик формирует сигнал переполнения, являющийся импульсом начала паузы, по которому содержимое регистра сдвига пересылается в буферный регистр и устанавливается триггер, выставляющий сигнал готовности результата операции для передачи содержимого буферного регистра в ЭВМ в течение времени готовности Т1г <Тп, где Тп - длительность паузы, находящаяся в пределах от 4Т до 40Т периодов Т частоты следования импульсов битовой синхронизации. По сигналу готовности результата операции через элемент И-НЕ проходят тактовые импульсы и сбрасывают регистр сдвига и суммирующий счетчик, а ЭВМ, после чтения результата операции (содержимого буферного регистра), устанавливает преобразователь в исходное состояние сбросом буферного регистра и триггера сигналом с входа сброса готовности результата операции. Следовательно, ЭВМ в течение времени Т1г готовности длительностью

40Т > Т1г > 3Т (2)

должна выполнить все операции обмена с устройством, которое будет готово к выполнению следующей операции только по окончании от ЭВМ сигнала сброса готовности операции.

Основным недостатком преобразователя [1] является его сложность, пропорциональная разрядности n регистра сдвига и буферного регистра, и ограниченность его функциональных возможностей (отсутствует возможность преобразования входного кода в ряде длин, например в ряде (1), и контроля функционирования преобразователя), а также относительно малое минимальное время готовности (2) и потеря управляемости преобразованием на неопределенное время при сбое битовой синхронизации особенно в сторону уменьшения от фиксированной длины n преобразования, поскольку сигнал готовности (паузы) вырабатывается по переполнению суммирующего счетчика, а не по реальному отсутствию импульсов битовой синхронизации. Легко видеть, что при установленном триггере поступающая на преобразователь последовательная информация полностью теряется, поскольку по сигналу готовности результата операции и тактовым импульсам элемент И-НЕ постоянно сбрасывает регистр сдвига и суммирующий счетчик.

Предлагаемым изобретением решается задача упрощения преобразователя и расширения его функциональных возможностей за счет обеспечения возможности преобразования входного кода в ряде длин с выдачей результата операции фрагментами параллельно-последовательного кода в сопровождении кода номера фрагмента и сигналов готовности и синхронизации фрагмента, а также формирования сигналов контроля функционирования преобразователя (информационной ошибки при четном числе единиц во входном коде и сбоя битовой синхронизации при отклонении разрядности входного кода от установленного ряда длин) и сигнала готовности результата операции с помощью обнаружения паузы с программируемым порогом.

Для достижения этого технического результата в преобразователь последовательного двоичного кода в параллельно-последовательный код, содержащий первый триггер, регистр сдвига, первый элемент И-НЕ, суммирующий счетчик, входы тактовый, импульсов битовой синхронизации, последовательного двоичного кода и сброса готовности результата операции и выход сигнала готовности результата операции, соединенный с выходом первого триггера и первым входом первого элемента И-НЕ, дополнительно введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеры с второго по пятый, обнаружитель паузы, элемент ИЛИ-НЕ, элементы И-НЕ с второго по пятый, первый элемент ИЛИ, три элемента И, вход начального сброса, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя паузы, выходы сигналов готовности фрагмента, синхронизации фрагмента, информационной ошибки и сбоя битовой синхронизации, выход кода номера фрагмента параллельно-последовательного кода, являющийся информационным выходом суммирующего счетчика, выход переноса которого соединен с первым входом первого элемента И, и выход фрагмента параллельно-последовательного кода, выход старшего разряда которого соединен с выходом второго триггера и последовательным информационным входом регистра сдвига.

Выходы старших разрядов регистра сдвига соединены с выходами младших разрядов фрагмента параллельно-последовательного кода, выход младшего разряда которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И и тактовым входом первого триггера, информационный вход которого соединен с шиной ЛОГИЧЕСКОГО "0" преобразователя, тактовый вход которого соединен с тактовым входом обнаружителя паузы, вход установки которого в режим обнаружения соединен с входом импульсов битовой синхронизации преобразователя, третьим входом первого элемента И-НЕ, прямым входом второго элемента И-НЕ и первым входом третьего элемента И-НЕ, второй вход которого соединен с инверсным входом второго элемента И-НЕ и выходом первого элемента И, второй вход которого соединен с прямым входом четвертого элемента И-НЕ, первым входом первого элемента ИЛИ, входом управления синхронным режимом параллельная запись/сдвиг вправо регистра сдвига, выходом младшего разряда регистра сдвига и выходом сигнала готовности фрагмента параллельно-последовательного кода преобразователя, вход последовательного двоичного кода которого соединен с информационным входом второго триггера и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Выход последнего соединен с информационным входом третьего триггера, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и информационным входом четвертого триггера, тактовый вход которого соединен с выходом сигнала синхронизации фрагмента параллельно-последовательного кода преобразователя и выходом пятого элемента И-НЕ, первый вход которого соединен со счетным входом суммирующего счетчика и выходом четвертого элемента И-НЕ, инверсный вход которого соединен с выходом второго элемента И-НЕ и тактовыми входами второго и третьего триггеров и регистра сдвига, параллельный информационный вход которого соединен с входом кода константы преобразователя, у которого старший разряд единица, а остальные разряды нули, выход четвертого триггера соединен с выходом сигнала информационной ошибки преобразователя, выход сигнала сбоя битовой синхронизации которого соединен с выходом пятого триггера, инверсный вход установки которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом третьего элемента И-НЕ, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ, первый выход обнаружителя паузы соединен с вторыми входами пятого элемента И-НЕ и первого элемента ИЛИ и асинхронным инверсным входом установки первого триггера, асинхронный инверсный вход сброса которого соединен с выходом элемента ИЛИ-НЕ и вторым входом второго элемента И, выход которого соединен с асинхронными инверсными входами установки четвертого триггера и сброса суммирующего счетчика и пятого триггера.

Второй выход обнаружителя паузы соединен с асинхронными инверсными входами сброса регистра сдвига и установки второго и третьего триггеров, первый вход элемента ИЛИ-НЕ соединен с входом сброса готовности результата операции преобразователя, вход начального сброса которого соединен с вторым входом элемента ИЛИ-НЕ и входом установки в состояние паузы обнаружителя паузы, который содержит входы тактовый, установки в режим обнаружения паузы, установки в состояние паузы, первый и второй выходы, элемент НЕ, шестой элемент И-НЕ, вычитающий счетчик, второй, третий и четвертый элементы ИЛИ и кодовый вход, который соединен с информационными входами вычитающего счетчика, выходы старших разрядов которого соединены с входами второго элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, тактовый вход обнаружителя соединен с первым входом шестого элемента И-НЕ, выход которого соединен со счетным входом вычитающего счетчика и вторым входом третьего элемента ИЛИ, выход которого является первым выходом обнаружителя, второй выход которого соединен с вторым входом шестого элемента И-НЕ и выходом четвертого элемента ИЛИ, второй вход которого соединен с выходом младшего разряда вычитающего счетчика, асинхронный инверсный вход записи которого через элемент НЕ связан с входом установки в режим обнаружения паузы обнаружителя, вход установки в состояние паузы которого соединен с асинхронным входом сброса вычитающего счетчика.

Авторам неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеров с второго по пятый, обнаружителя паузы, элемента ИЛИ-НЕ, элементов И-НЕ с второго по пятый, первого элемента ИЛИ, трех элементов И, входа начального сброса, программируемого кодового входа порога обнаружения паузы, выхода фрагмента параллельно-последовательного кода и выходов кода номера фрагмента параллельно-последовательного кода и сигналов готовности и синхронизации фрагмента, информационной ошибки и сбоя битовой синхронизации), позволяющие использовать его при построении аппаратно простых КЛС, поддерживающих с высокой достоверностью в локальной сети обмен последовательными двоичными кодами с различными длинами, принадлежащими, например, ряду типа (1).

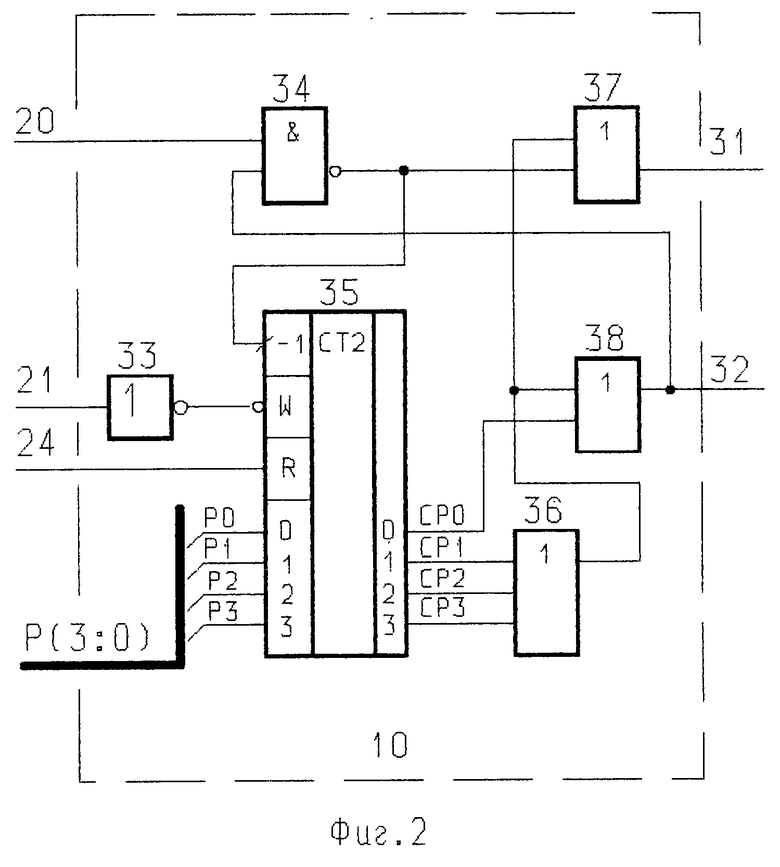

На фиг. 1-2 приведена функциональная схема преобразователя последовательного двоичного кода в параллельно-последовательный код при реализации его, в частности с использованием библиотеки элементов интегральных схем (ИС) серии 533 для работы с входными кодами, длины которых соответствуют ряду (1).

Преобразователь последовательного двоичного кода в параллельно-последовательный код (фиг. 1) содержит первый триггер 1, байтовый регистр 2 сдвига, первый элемент 3 И-НЕ, суммирующий счетчик 4, элемент 5 ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеры с второго 6 по пятый 9, обнаружитель 10 паузы, элемент 11 ИЛИ-НЕ, элементы И-НЕ с второго 12 по пятый 15, первый элемент 16 ИЛИ, три элемента И 17-19, тактовый вход 20, вход 21 импульсов битовой синхронизации, вход 22 последовательного двоичного кода, вход 23 сброса готовности результата операции, вход 24 начального сброса, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя 10, выход 25 сигнала готовности результата операции, соединенный с выходом триггера 1 и первым входом элемента 3, выходы 26, 27, 28 и 29 соответственно сигналов готовности фрагмента, синхронизации фрагмента, информационной ошибки и сбоя битовой синхронизации, выход 30 переноса счетчика 4, соединенный с первым входом элемента 17, первый 31 и второй 32 выходы обнаружителя 10, выход кода номера фрагмента параллельно-последовательного кода, являющийся информационным выходом счетчика 4, и выход фрагмента параллельно-последовательного кода, выход старшего разряда которого соединен с выходом триггера 6 и последовательным информационным входом регистра 2.

Выходы старших разрядов регистра соединены с выходами младших разрядов фрагмента параллельно - последовательного кода, выход младшего разряда которого соединен с вторым входом элемента 3, выход которого соединен с первым входом элемента 18 и тактовым входом триггера 1, информационный вход которого соединен с шиной ЛОГИЧЕСКОГО "0" преобразователя, тактовый вход 20 которого соединен с тактовым входом обнаружителя 10, вход установки которого в режим обнаружения соединен с входом 21 импульсов битовой синхронизации преобразователя, третьим входом элемента 3, прямым входом элемента 12 и первым входом элемента 13, второй вход которого соединен с инверсным входом элемента 12 и выходом элемента 17, второй вход которого соединен с прямым входом элемента 14, первым входом элемента 16, входом выбора синхронного режима параллельная запись/сдвиг вправо регистра 2, выходом младшего разряда регистра 2 и выходом 26 сигнала готовности фрагмента параллельно-последовательного кода преобразователя, вход 22 последовательного двоичного кода которого соединен с информационным входом триггера 6 и первым входом элемента 5, выход которого соединен с информационным входом триггера 7, выход которого соединен с вторым входом элемента 5 и информационным входом триггера 8.

Тактовый вход триггера 8 соединен с выходом 27 сигнала синхронизации фрагмента параллельно-последовательного кода преобразователя и выходом элемента 15, первый вход которого соединен со счетным входом счетчика 4 и выходом элемента 14, инверсный вход которого соединен с выходом элемента 12 и тактовыми входами триггеров 6 и 7 и регистра 2, параллельный информационный вход которого соединен с входом кода константы преобразователя, у которого старший разряд единица, а остальные разряды нули, выход триггера 8 соединен с выходом 28 сигнала информационной ошибки преобразователя, выход 29 сигнала сбоя битовой синхронизации которого соединен с выходом триггера 9, инверсный вход установки которого соединен с выходом элемента 19, первый вход которого соединен с выходом элемента 13, второй вход элемента 19 соединен с выходом элемента 16, выход 31 обнаружителя 10 соединен с вторыми входами элементов 15 и 16 и асинхронным инверсным входом установки триггера 1, асинхронный инверсный вход сброса которого соединен с выходом элемента 11 и вторым входом элемента 18, выход которого соединен с инверсными асинхронными входами установки триггера 8 и сброса счетчика 4 и триггера 9, выход 32 обнаружителя 10 соединен с асинхронными инверсными входами сброса регистра 2 и установки триггеров 6 и 7, первый вход элемента 11 соединен с входом 23 сброса готовности результата операции преобразователя, вход 24 начального сброса которого соединен с вторым входом элемента 11 и входом установки в состояние паузы обнаружителя 10.

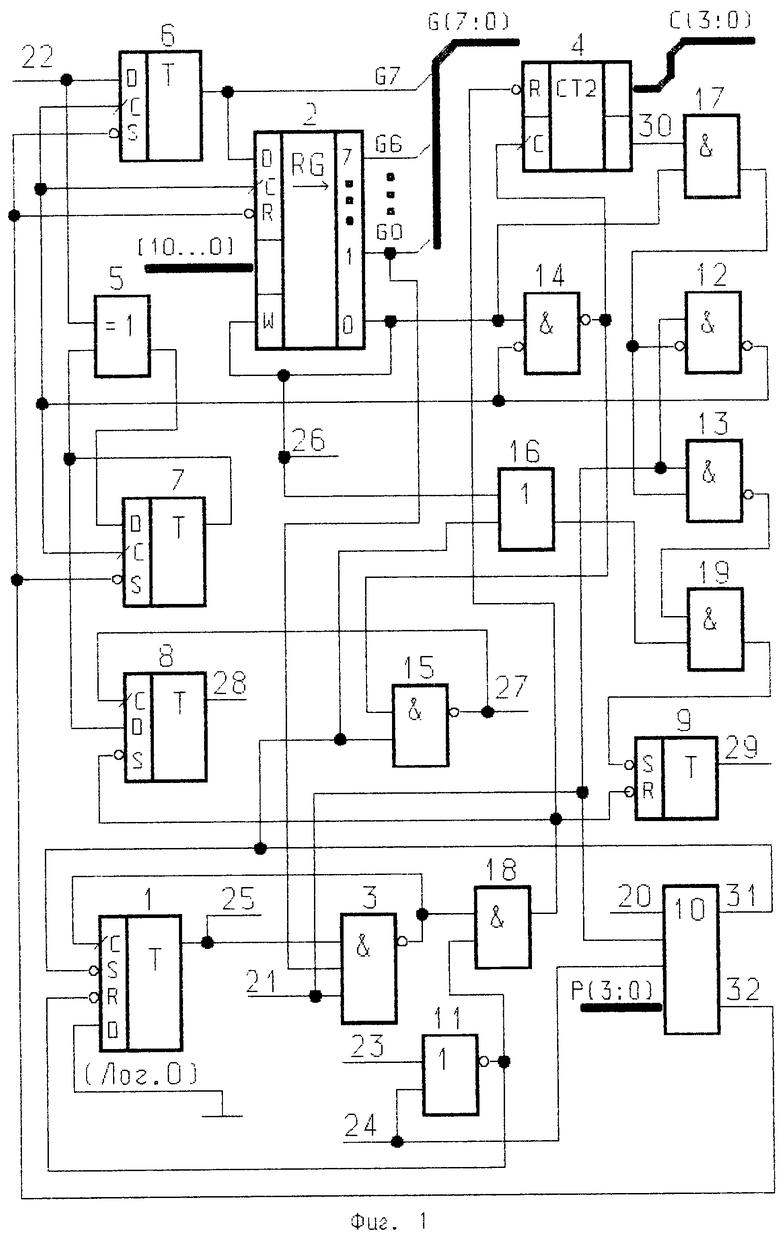

Обнаружитель 10 паузы (фиг.2) содержит входы 20, 21 и 24 соответственно тактовый, установки в режим обнаружения паузы и установки в состояние паузы, первый 31 и второй 32 выходы, элемент 33 НЕ, шестой элемент 34 И-НЕ, первый вход которого соединен с тактовым входом 20, вычитающий счетчик 35, второй 36, третий 37 и четвертый 38 элементы ИЛИ и кодовый вход, который соединен с информационными входами счетчика 35, выходы старших разрядов которого соединены с входами элемента 36, выход которого соединен с первыми входами элементов 37 и 38, выход элемента 37 является выходом 31 обнаружителя 10, выход 32 которого соединен с вторым входом элемента 34 и выходом элемента 38, второй вход которого соединен с выходом младшего разряда счетчика 35, инверсный асинхронный вход записи которого через элемент 33 связан с входом 21 установки в режим обнаружения паузы обнаружителя 10, вход 24 установки в состояние паузы которого соединен с асинхронным входом сброса счетчика 35.

При реализации преобразователя (фиг.1-2) в библиотеке элементов ИС серии 533 можно выполнить триггеры 1, 6-8 на двух ИС ТМ2, причем у триггеров 6-8 асинхронные инверсные входы сброса должны быть подключены к шине ЛОГИЧЕСКОЙ "1" преобразователя (на фиг. 1 это не показано); регистр 2 выполнен на двух ИС ИР11А, образующих собой байтовый регистр с асинхронным инверсным сбросом и синхронным функционированием по фронтам импульсов на тактовом входе или в режиме параллельной записи кода (10...0) константы при W=1, либо в режиме приема входного последовательного кода с выхода триггера 6 младшими разрядами вперед (т.е. со сдвигом вправо) при W=0, где W - сигнал режима функционирования регистра 2 на соответствующем входе каждой из ИС ИР11А, представляющей собой четырехразрядный реверсивный сдвиговый регистр с параллельным выходом, синхронным последовательно-параллельным вводом и асинхронным инверсным сбросом.

Cчетчик 4 выполнен на ИС ИЕ10 - четырехразрядном двоичном счетчике с асинхронным инверсным сбросом; счетчик 35 выполнен на ИС ИЕ7 - четырехразрядном двоичном реверсивном счетчике с асинхронным входом сброса и асинхронным инверсным входом загрузки в счетчик кода с параллельных информационных входов; остальные составные части устройства выполнены на комбинационных элементах соответствующих ИС, в частности триггер 9 реализован на двух элементах 2И-НЕ ИС ЛА3.

Описание функционирования преобразователя осуществляется с помощью системы положений и обозначений, определенных в следующих пунктах.

1. Входные, промежуточные (формируемые на выходах соответствующих составных частей преобразователя) и выходные (формируемые на выходах преобразователя) прямые (или инверсные) переменные обозначим соответственно через Xi, Zj (или NZj) и Yk (или NYk), где число из множества {i, j, k} означает или номер входа, или номер составной части, или номер выхода преобразователя или его составной части. Например, Х20 - тактовые импульсы на тактовом входе 20, Х21 - импульсы на входе 21 импульсов битовой синхронизации; NZ12 и NZ13 - инверсные импульсы на выходах элементов 12 и 13 соответственно; Y25=Z1 - сигнал готовности результата операции на выходе 25 преобразователя, Y30 - сигнал на выходе 30 переноса счетчика 4, NY31 и NY32 - инверсный импульс начала паузы и инверсный сигнал паузы соответственно на выходах 31 и 32 обнаружителя 10. Кроме того, коды на выходе фрагмента параллельно-последовательного кода, выходе кода номера фрагмента параллельно-последовательного кода, выходе счетчика 35 и кодовом входе обнаружителя 10 обозначим соответственно через G(7:0)=G7...G0, С(3:0)=С3 С2 С1 С0, СР(3:0)=СР3 СР2 СР1 СР0 и Р(3: 0)=Р3 Р2 Р1 Р0, где G0, С0, СР0 и Р0 - младшие, а G7, С3, СР3 и Р3 - старшие разрядные цифры (т.е. 0 или 1) этих кодов.

2. Используется модифицированный язык описания Булевых (логических) функций ABEL, в котором операторы "Конъюнкции", "Дизъюнкции", "Инверсии" и "Исключающее ИЛИ" имеют обозначения "& ", "#", "!" и "$" соответственно. Например, элементы 12 и 17 формируют переменные NZ12 и Z17 согласно выражениям NZ12=![(!Z17)&Х21] и Z17=Y30&Y26 соответственно.

3. Под фронтом или спадом любого сигнала (прямого или инверсного) понимается смена логического значения этого сигнала из "0" в "1" или из "1" в "0" соответственно.

4. Под сбросом (или установкой), например, триггера 9 понимается переключение этого триггера в "0" (или "1").

5. В процессе функционирования преобразователя вырабатывается сигнал Y25 готовности результата операции и сигнал NY32 паузы так, что можно выделить следующие четыре режима его работы:

РР0 ожидания (холостого хода) при Y25 NY32=00 (3),

РР1 преобразования при Y25 NY32=01 (4),

РР2 готовности при Y25 NY32=10 (5),

РР3 готовности и преобразования при Y25 NY32=11 (6).

С учетом принятой системы положений и обозначений опишем сначала функционирование преобразователя в целом как конечного автомата с памятью, а затем работу его составных частей.

Исходным состоянием преобразователя является режим РР0 (3), в котором триггеры 1 и 9, счетчик 4 сброшены, триггер 8 установлен, регистр 2 сброшен инверсным сигналом NY32=0 паузы, триггеры 6 и 7 установлены. Установка преобразователя в исходное состояние осуществляется или при включении аппаратуры по сигналу Х24=1 начальной установки, или при переходе из режима РР2 (5) по сигналу Х23=1 сброса готовности результата операции.

Каждая операция преобразования начинается с поступлением на входы 21 и 22 соответственно последовательности из П импульсов Х21 битовой синхронизации и сигнала Х22 последовательного двоичного кода, длина которого в битах должна принадлежать ряду (1), т.е. для корректного функционирования преобразователя число П также должно принадлежать ряду (1). Непосредственно по первому импульсу Х21 последовательности П обнаружитель 10 устанавливается в режим обнаружения паузы (по первому, а затем по каждому импульсу NZ33=!X21=0 в счетчик 35 загружается код СР(3:0)=Р(3:0) порога обнаружения паузы) и преобразователь переходит в режим РР1 (4) преобразования, в котором элементы 12-14 формируют инверсные импульсы согласно выражениям

NZ12=![(!Z17)&X21], (7)

NZ13=![Z17 &X21], (8)

NZ14=![Y26 &Z12], (9)

где Y26 - сигнал, переключающийся в "1" по спаду (или фронту) каждого кратного восьми импульса Х21 (или NZ12) последовательности П, где число П принадлежит ряду (1).

По фронту каждого импульса NZ12=!X21 триггеры 6 и 7 устанавливаются в состояния

Z6=G7=X22 (в момент фронта NZ12), (10)

Z7=Х22$Z7 (в момент фронта NZ12), (11),

а содержимое регистра 2 при Y26 =0 сдвигается вправо с приемом в старший разряд G6 бита G7=Z6 (в момент фронта NZ12), а при Y26=1 старший разряд G6 регистра 2 устанавливается, а младшие разряды сбрасываются, т.е. G(6:0)= (1000000), Y26=0.

Следовательно, после окончания 8-го, 16-го,..., 120-го, 128-го импульсов NZ12 (7) регистр 2 выставит сигнал Y26=1 готовности фрагмента 0-го, 1-го,... , 14 и 15-го выходного G(7:0) параллельно-последовательного кода и установятся следующие состояния:

G(7:0)=D(7:0), D(16:8),..., D(119:112) и D(127:120), (12)

С(3:0)-(0000), (0001),..., (1110) и (1111), (13)

а затем сформируется импульс

Y27=Z15=(!NZ14)#(!NZ31)=Z14#Z31 (14)

синхронизации фрагмента G(7:0) параллельно-последовательного кода результата (12) по 9-му, 17-му,..., 121 импульсам NZ12=!X21 и инверсному импульсу NZ31 обнаружения паузы. По фронту каждого импульса Y27 (14) триггер 8 устанавливается в состояние

Y28=Z8-Z7 (в момент фрoнта Y27), (15)

а также может быть снят с преобразователя соответствующий фрагмент G(7: 0) результата (12) операции. В процессе выполнения операции элемент 19 формирует при П, не принадлежащем множеству (1), инверсный импульс

NZ19=NZ13&(Y26#NZ31), (16)

так что NZ19= NZ13 (или (Y26#NZ31)) при П > 128 (или при П < 128 и не кратном восьми). По импульсу NZ19=0 триггер 9 устанавливается и выставляет сигнал Y29=1 сбоя битовой синхронизации.

В течение времени преобразования по фронту каждого импульса NZ12 (или Y27) триггер 7 (или 8) при Х22=1 переключается в противоположное состояние (11) (или в состояние Z7). Поэтому после окончания последовательности П импульсов Х21 битовой синхронизации и по окончании фронта импульса Z27=!NZ31 триггеры 7 и 9 находятся в одинаковых состояниях (т.е. Z7=Z8=Y28) и при Y28= 0 информационная ошибка отсутствует, а при Y28=1 обнаружена информационная ошибка, т.е. четное число единиц в преобразованном входном последовательном двоичном коде Х22.

Кроме того, непосредственно по инверсному импульсу NY31=0 устанавливается триггер 1 и выставляет сигнал Y25=Z1=1 готовности результата операции

{D((n-1):0), C(3:0), Y25, Y28, Y29}, (17)

где n принадлежит множеству (1).

По окончании импульса NY31 обнаружитель 10 выставляет инверсный сигнал NY32= 0 паузы, и преобразователь переходит в режим РР2 (5), в котором по сигналу Y25= 1 прерывается ЭВМ для сообщения о завершении очередной операции преобразования и съема кода С(3:0) номера последнего фрагмента G(7:0) параллельного кода D((n-1): 0) и сигналов Y28 (15) информационной ошибки и Y29 сбоя битовой синхронизации. В процессе выполнения прерывающей программы ЭВМ формирует сигнал Х23 сброса готовности результата, который через элемент 11 сбрасывает триггер 1, а через элементы 11 и 18 сбрасывает счетчик 4 и триггер 9, устанавливает триггер 8 и переключает устройство в исходное состояние - режим РР0 (3).

Если ЭВМ сигнал Х23=1 не формирует, то преобразователь переходит в режим РР3 (6) с поступлением на его входы очередной последовательности П импульсов Х21 битовой синхронизации и сигнала Х22 последовательного двоичного кода. В этом режиме по окончании 7-го импульса NZ12=!X21 регистр 2 выставляет сигнал G0= 1, с помощью которого элементы 3 и 18 по 8-му импульсу Х21 формируют инверсные импульсы

NZ3=!(Y25&G0&X21), (18)

NZ18=!(Z3#X23#X24).(19)

Непосредственно по импульсу NZ18=0 счетчик 4 и триггер 9 сбрасываются, триггер 8 устанавливается, а по окончании импульса NZ3=0 триггер 1 сбрасывается (вырабатывает сигнал Y25=Z1=0), и преобразователь переходит в режим РР1 (4), описанный ранее.

Таким образом, функционирование преобразователя как конечного автомата с памятью состоит в чередовании режимов его работы, например РР0, РР1, РР2, РР3, РР1 и т. п., так, что переход в РР0 может быть осуществлен из любого другого режима по сигналу Х24 начального сброса или из режима РР2 по сигналу Х23 сброса готовности результата, в РР1 - из режима РР0 непосредственно по первому импульсу Х21 последовательности П импульсов Х21 битовой синхронизации или из режима РР3 непосредственно по сигналу Х23 или по окончании инверсного импульса NZ3 (18), в РР2 - только из режима РР1 по окончании инверсного импульса NY31, в РР3 - только из РР2 по первому импульсу Х21.

Функционирование отдельных составных частей преобразователя заключается в следующем.

Триггер 1 по инверсному импульсу NY31 устанавливается, а сбрасывается или по инверсному сигналу NZ11=!(X23#X24), или по фронту импульса NZ3 (18).

Регистр 2 по инверсному сигналу NY32=0 паузы зафиксирован в нуле, а при NY32= 1 по фронту каждого инверсного импульса NZ12 (7) содержимое регистра 2 при Y26= 0 (или Y26=1) сдвигается вправо с приемом в старший разряд G6 бита G7=Z6 (или становится равным коду (10000000) константы преобразователя), где Y26 - значение младшего бита регистра 2.

Счетчик 4 по инверсному сигналу NZ18=0 (19) зафиксирован в нуле, а при NZ18=1 по окончании каждого инверсного импульса NZ14 (9) содержимое счетчика 4 (код С(3: 0)) увеличивается на единицу и на выходе 30 формируется сигнал переноса

Y30=C0&C1&C2&C3. (20)

Триггер 6 (или 7) по инверсному сигналу NY32=0 паузы установлен, а при NY32=1 триггер 6 (или 7) функционирует согласно (10) (или (11)).

Триггер 8 функционирует согласно (15).

Триггер 9 по инверсным импульсам NZ19 (16) и NZ18 (19) устанавливается и сбрасывается соответственно.

Обнаружитель 10 (фиг.2) вырабатывает инверсный импульс NY31 обнаружения паузы и инверсный сигнал NY32 паузы согласно выражениям

NY31=[!(X20&CP0)]#CP1#CP2#CP3, (21)

NY32=CP0#CP1#CP2#CP3, (22)

так, что он находится при NY32=0 в состоянии паузы, а при NY32=1 в режиме обнаружения паузы, который заканчивается по окончании фронта импульса NY31. Из фиг.2 и (21) следует, что импульс NY31 вырабатывается по тактовому импульсу Х20 при нахождении счетчика 35 в состоянии СР(3:0)=(0001), а сигнал паузы NY32= 0 выставляется при нахождении счетчика 35 в состоянии СР(3:0)= (0000), в котором счетчик 35 может быть зафиксирован сигналом Х24=1 начального сброса. При Х24=0 счетчик 35 по коду Р(3:0) и инверсным импульсам NZ33= ! Х21 и NZ34=!(Х20&NY32) функционирует следующим образом. Каждым импульсом NZ33=0 счетчик 35 фиксируется в состоянии СР(3:0)=Р(3:0), которое определяет порог Р обнаружения как число согласно выражению

P=P0 + 2P1 + 4P2 + 8P3. (23)

При наступлении паузы формирование импульсов NZ33=!X21 прекращается, и при NY32= 1 элемент 34 формирует ровно Р (23) импульсов NZ34 (отсчитываются от последнего импульса NZ33=0), по фронту каждого из которых содержимое счетчика 35 уменьшается на единицу, а по импульсу Р этой последовательности формируется импульс NY31 (21) обнаружения паузы, по окончании которого счетчик 35 переходит в состояние СР(3:0)=(0000), обнаружитель 10 выставляет сигнал NY32= 0 паузы и блокирует работу элемента 34 по тактовым импульсам Х20. В состоянии паузы обнаружитель 10 остается до поступления на него очередной последовательности П импульсов Х21 битовой синхронизации. В этой связи порог обнаружения Р (23), частоту F20=kxF21 тактовых импульсов Х20 и частоту F21 следования импульсов Х21 битовой синхронизации необходимо выбирать из условия

2/F21 > P/F20 > 1/F21=Т (24).

вариацией двух чисел k > 1 и Р > 2, обеспечивающих длительность То временного порога обнаружения паузы согласно выражению

To = P/F20=P/(kxF21)=T(P/k), (25)

где k - коэффициент пропорциональности;

х и / - операторы арифметических операций умножения и деления соответственно.

По импульсу NY31= 0 триггер 1 выставляет сигнал Y25=1 готовности результата, длительность которого максимальна при отсутствии от ЭВМ сигнала Х23 и с учетом условия (24) при Тп=4Т оценивается выражением

Т25г=10 Т. (26)

Сравнивая (2) и (26), получаем

Т25г/Т1г > 2,5, (27)

что длительность времени готовности Т25г (26) результата операции предлагаемого преобразователя в несколько раз выше длительности времени готовности Т1г (2) прототипа [1].

Легко видеть, что в общем случае предлагаемый преобразователь аппаратурно значительно проще прототипа [1], поскольку прототип содержит многоразрядные (n-разрядные) буферный регистр и регистр сдвига, емкость каждого из которых во много раз больше емкости регистра сдвига данного преобразователя (например, при n=128 в 16 раз).

Наличие на выходах преобразователя сигнала Y26 готовности и импульса Y27 (14) синхронизации каждого фрагмента G(7:0) параллельно-последовательного кода (его форму см. в (12) при n=128) обеспечивает множество вариантов передачи в ЭВМ через УУO результата операции (17).

Опишем два возможных варианта ввода результата (17) соответственно по импульсам Y27 (14) и сигналам Y26 готовности фрагментов.

В первом случае в УУО по фронту каждого импульса Y27 текущий фрагмент G(7:0) загружается в регистр типа ИР23 и вызывает прерывание ЭВМ первого типа. При выполнении первой прерывающей программы ЭВМ в своей оперативной памяти формирует код D((n-1):0). По окончании каждой операции преобразователь выставляет сигнал Y25=1 и вызывает прерывание ЭВМ второго типа. При выполнении второй прерывающей программы ЭВМ считывает оставшуюся часть {С(3:0), Y28, Y29} результата (17), формирует сигнал Х23=1 сброса готовности результата, затем ЭВМ при Y28 # Y29=0 пересылает, например, информационную часть кода D((n-1): 0) абоненту (приемнику), а при Y28#Y29=1 результат игнорируется, поскольку обнаружена ошибка в коде D((n-1):0) при Y28=1 или/и сбой битовой синхронизации при Y29=1.

Во втором случае УУО по каждому сигналу Y26=1 и коду С(3:0) записывает каждый фрагмент G(7:0) кода D((n-1):0) в оперативную память (ОЗУ, ДОЗУ или аппаратный стек). По окончании каждой операции преобразователь выставляет сигнал Y25= 1 прерывания ЭВМ, которая в течение времени Т25г (26) выполняет прерывающую программу, аналогичную второй прерывающей программе, описанной для первого случая.

Таким образом, предлагаемый преобразователь благодаря его существенным признакам проще прототипа [1] и по сравнению с ним обладает более широкими функциональными возможностями за счет обеспечения возможности как преобразования входного последовательного двоичного кода в ряде длин типа (1) с обнаружением информационной ошибки и сбоя битовой синхронизации, так и большого разнообразия вариантов ввода в ЭВМ результата (17) при увеличенном времени (26) готовности результата операции в несколько раз (см. оценку (27)). В этой связи данный преобразователь можно использовать для построения аппаратно простых КЛС, поддерживающих с высокой достоверностью в локальной сети обмен последовательными двоичными кодами как с фиксированными, так и различными длинами, принадлежащими, например, ряду (1).

Литература

1. А.с. 1786491, М.кл. G 06 F 13/00, СССР. Устройство для ввода информации. Д.Ю. Гусев и Ю.В. Крюков. Опубл. 07.01.1993. Бюл. 1(прототип).

2. Организация последовательных мультиплексных каналов систем автоматического управления. С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой. Под общ. ред. С.Т. Хвоща. - Машиностроение. Ленингр. Отд-ние, 1989. - 271 с., ил.

3. Каган Б. М. - Электронные вычислительные машины и системы: Учебное пособие для вузов. - 3-е изд., перераб. и доп.- Энергоатомиздат, 1991. - 592 с., ил.

4. Ю. В. Новиков, Д.Г. Карпенко. Аппаратура локальных сетей: функции, выбор, разработка. Под общей редакцией Ю.В. Новикова. - М.: Издательство ЭКОМ, 1998. - 288с., ил.

5. Щербаков Н. С. Достоверность работы цифровых устройств. - М.: Машиностроение, 1989. 224 с., ил.

6. Контроль функционирования больших систем. Г.П. Шибанов, Е.А. Артеменко, А. А. Матешкин, Н.И. Циклинский. Под ред. заслуженного изобретателя РСФСР д.т.н. Г.П. Шибанова. - М.: Машиностроение, 1977, 360 с.

7. А. с. 822175, М.кл. 3 G 06 F 5/04, СССР. Преобразователь последовательного кода в параллельный код. Ю.А. Плужников, Е.А. Евсеев, В.И. Косогоров и А.Н. Горбунов. Опубл. 15.04.1981. Бюл. 14.

8. А. с. 1078424, М.кл. G 04 F 5/04, СССР. Преобразователь последовательного комбинированного кода в параллельный двоичный код. В.Д. Гладков. Опубл. 07.03.1984. Бюл. 9.

9. А.с. 1081639, М.кл. G 06 F 5/04, СССР. Устройство для преобразования последовательного кода в параллельный. В.И. Соловьев и А.Е. Кравец. Опубл. 23.03.1984. Бюл. 11.

10. А. с. 1084780, М.кл. G 06 F 5/02, СССР. Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код. Е.А. Шурмухин и К.В. Королева. Опубл. 07.04.1984. Бюл. 13.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в упрощении преобразователя и расширении его функциональных возможностей. Устройство обеспечивает преобразование входного последовательного кода в ряде длин кодов с выдачей результата операции фрагментами параллельно-последовательного кода с обнаружением информационной ошибки и сбоя битовой синхронизации и формирование сигнала готовности результата с помощью обнаружения паузы с программируемым порогом. 2 ил.

Преобразователь последовательного двоичного кода в параллельно-последовательный код, содержащий первый триггер, регистр сдвига, первый элемент И-НЕ, суммирующий счетчик, входы тактовый, импульсов битовой синхронизации, последовательного двоичного кода и сброса готовности результата операции и выход сигнала готовности результата операции, соединенный с выходом первого триггера и первым входом первого элемента И-НЕ, отличающийся тем, что он дополнительно содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеры с второго по пятый, обнаружитель паузы, элемент ИЛИ-НЕ, элементы И-НЕ с второго по пятый, первый элемент ИЛИ, три элемента И, вход начального сброса, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя паузы, выходы сигналов готовности фрагмента, синхронизации фрагмента, информационной ошибки и сбоя битовой синхронизации, выход кода номера фрагмента параллельно-последовательного кода, являющийся информационным выходом суммирующего счетчика, выход переноса которого соединен с первым входом первого элемента И, и выход фрагмента параллельно-последовательного кода, выход старшего разряда которого соединен с выходом второго триггера и последовательным информационным входом регистра сдвига, выходы старших разрядов которого соединены с выходами младших разрядов фрагмента параллельно-последовательного кода, выход младшего разряда которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И и тактовым входом первого триггера, информационный вход которого соединен с шиной ЛОГИЧЕСКОГО “0” преобразователя, тактовый вход которого соединен с тактовым входом обнаружителя паузы, вход установки которого в режим обнаружения соединен с входом импульсов битовой синхронизации преобразователя, третьим входом первого элемента И-НЕ, прямым входом второго элемента И-НЕ и первым входом третьего элемента И-НЕ, второй вход которого соединен с инверсным входом второго элемента И-НЕ и выходом первого элемента И, второй вход которого соединен с прямым входом четвертого элемента И-НЕ, первым входом первого элемента ИЛИ, входом управления синхронным режимом параллельная запись/сдвиг вправо регистра сдвига, выходом младшего разряда регистра сдвига и выходом сигнала готовности фрагмента преобразователя, вход последовательного двоичного кода которого соединен с информационным входом второго триггера и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом третьего триггера, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и информационным входом четвертого триггера, тактовый вход которого соединен с выходом сигнала синхронизации фрагмента преобразователя и выходом пятого элемента И-НЕ, первый вход которого соединен с счетным входом суммирующего счетчика и выходом четвертого элемента И-НЕ, инверсный вход которого соединен с выходом второго элемента И-НЕ и тактовыми входами второго и третьего триггеров и регистра сдвига, параллельный информационный вход которого соединен с входом кода константы преобразователя, у которого старший разряд единица, а остальные разряды нули, выход четвертого триггера соединен с выходом сигнала информационной ошибки преобразователя, выход сигнала сбоя битовой синхронизации которого соединен с выходом пятого триггера, инверсный вход установки которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом третьего элемента И-НЕ, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ, первый выход обнаружителя паузы соединен с вторыми входами пятого элемента И-НЕ и первого элемента ИЛИ и асинхронным инверсным входом установки первого триггера, асинхронный инверсный вход сброса которого соединен с выходом элемента ИЛИ-НЕ и вторым входом второго элемента И, выход которого соединен с асинхронными инверсными входами установки четвертого триггера и сброса суммирующего счетчика и пятого триггера, второй выход обнаружителя паузы соединен с асинхронными инверсными входами сброса регистра сдвига и установки второго и третьего триггеров, первый вход элемента ИЛИ-НЕ соединен с входом сброса результата операции преобразователя, вход начального сброса которого соединен с вторым входом элемента ИЛИ-НЕ и входом установки в состояние паузы обнаружителя паузы, который содержит входы тактовый, установки в режим обнаружения паузы, установки в состояние паузы, первый и второй выходы, элемент НЕ, шестой элемент И-НЕ, вычитающий счетчик, второй, третий и четвертый элементы ИЛИ, и кодовый вход, который соединен с информационными входами вычитающего счетчика, выходы старших разрядов которого соединены с входами второго элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, тактовый вход обнаружителя соединен с первым входом шестого элемента И-НЕ, выход которого соединен с счетным входом вычитающего счетчика и вторым входом третьего элемента ИЛИ, выход которого является первым выходом обнаружителя, второй выход которого соединен с вторым входом шестого элемента И-НЕ и выходом четвертого элемента ИЛИ, второй вход которого соединен с выходом младшего разряда вычитающего счетчика, асинхронный инверсный вход записи которого через элемент НЕ связан с входом установки в режим обнаружения паузы обнаружителя, вход установки в состояние паузы которого соединен с асинхронным входом сброса вычитающего счетчика.

| Устройство для ввода информации | 1990 |

|

SU1786491A1 |

| RU 2066066 С1, 27.08.1996 | |||

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2017211C1 |

| JP 61147332, 05.07.1986 | |||

| Преобразователь последовательногоКОдА B пАРАллЕльНый | 1979 |

|

SU822175A2 |

| Преобразователь последовательного комбинированного кода в параллельный двоичный код | 1982 |

|

SU1078424A1 |

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

Авторы

Даты

2003-12-27—Публикация

2001-10-15—Подача