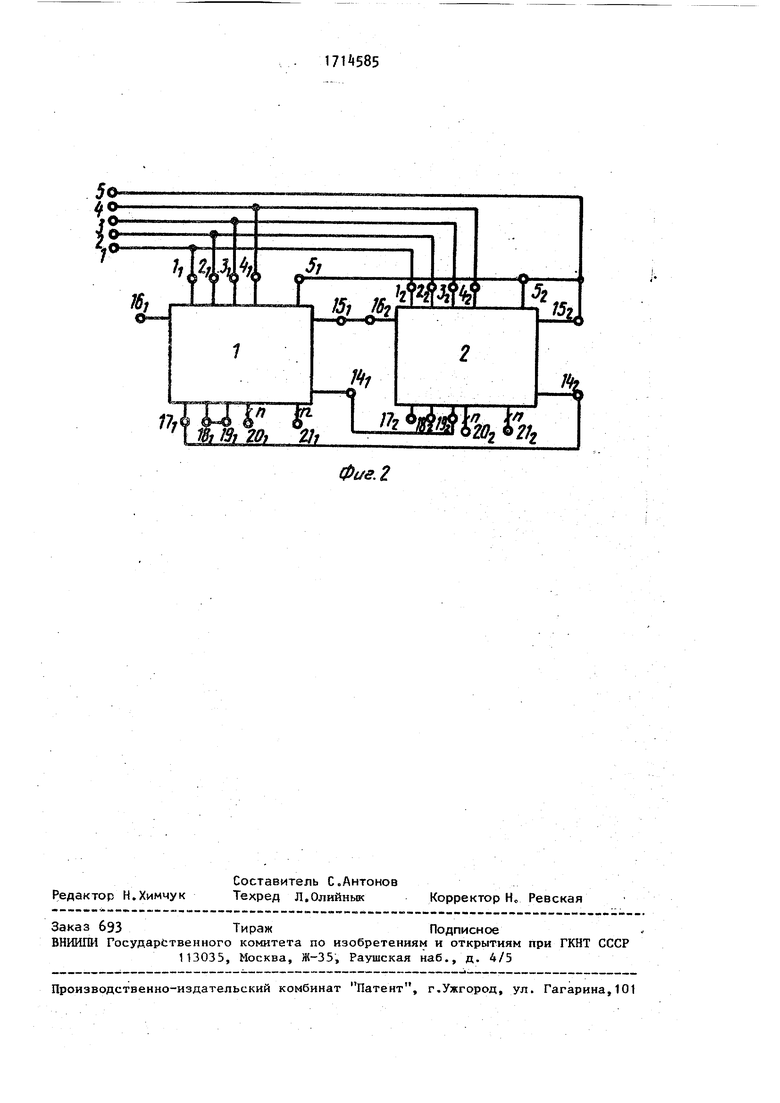

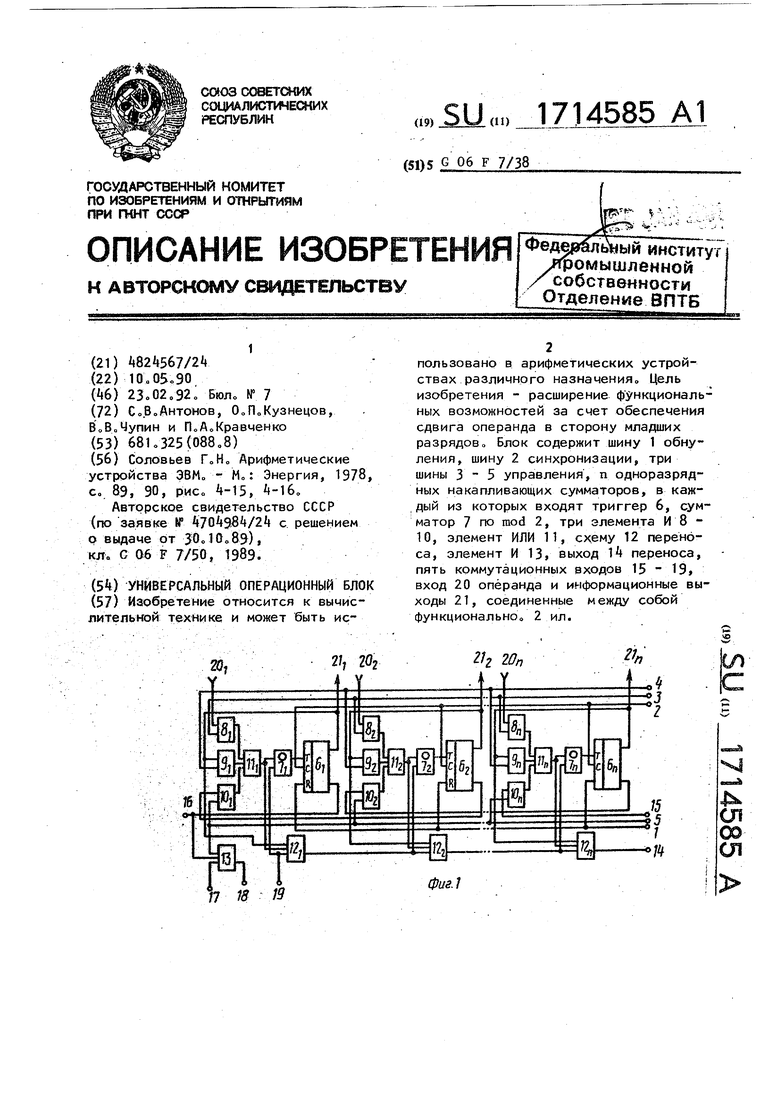

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах различного назначения Известны операционные блоки, пред ставляющие собой сумматоры параллель ного действия, содержащие п одноразрядных комбинационных сумматоров и регистр фиксации результата позво ляющие суммировать п - разрядные чис ла, подаеаеууе .одновременно,, Отсутст вие .двига в данных сумма торахуслЬжняет арифметико-логически устройства (А)1У), так как в АЛУ процессОроВнеойбхйдййо. выполнять арифме тические и логические операции, част которых предполагает сдвиг информа ции на выходе сумматора с помощью специальных регистров сдвигвг. Наиболее близким к предлагаемому является операционный блок, построен ный на базе накапливающего сумматора который принят за базовый, содержащий п одноразрядных сумматоров, выполненных на счетном триггере, сумма торе по nrod 2, коммутаторе, состоящем из двух элементов И и элемента ИЛИ, схемы параллельного переноса, двух управляющих шин, шины синхрони зации и шины обнуленияс .. Недостатком этого операционного блока является отсутствие возможности сдвига вправо (в сторону глладших разрядов). Цель изобретения -- расширение функциональных возможностей за счет обеспечении сдвига операнда.в сторон младших разрядов„ Поставленная цель достигается тем что в операционный блок, содержащий п одноразрядных накапливающих сумматоров, каждый из которых состоит из счетного триггера, сумматора nomod 2 первого и второго элементов И, элемента ИЛИ, схемы переноса, причем первый вход первого элемента И соеди нен с входом данного разряда суммато ра, первый вход второго элемента И соединен с прямым выходом счетного триггера и первым входом схемы переноса данного разряда, выходы первого и второго элементов И соединены с первым и вторым входами элемента ИЛИ выход koToporo соединен с первым входом сумматора по mod 2 и вторым входом схемы переноса Второй вход сумматора по mod 2 соединен с третьи входом схемы переноса, выход сумматора по nrad 2 соединен с Т-входом. счетного триггера, вторые входы пер-, вого и второго элементов И соединены соответственно с первой и второй шинами управления операционного блока, информационные разрядные выходы которого соединены соответственно с прямыми выходами счетных триггеров, выход схемы переноса i-ro разряда (где 1 1, 2, 3, ..«, п-1) соединен с третьим входом схемы переноса (i+1)-ro разряда, выход схемы переноса п-го разряда является выходом переноса операционного блока, шина синхронизации которого соединена с входами синхронизации п счетных триггеров, входы начальной установки которых соединены с шиной обнуления операционного блока, в него дополнительно введены п третьих двухвходовых элементов И и дополнительный трехвходовой элемент И, причем первый вход третьего элемента И i-ro разряда соединен с инверсным выходом счетного триггера (i+l)ro разряда, первьй вход третьего элемента И п-го разряда соединен с первым коммутационным входом операционного блока, вторые входы п третьих элементов И соединены с третьей шиной управления операционного блока и первым входом дополнительного элемента И, второй вход которого соединен с инверсным выходом счетного триггера первого разря да и вторым коммутационным входом операционного блока, трютий вход дополнительного элемента И соединен с третьим коммутационным входом операционного блока, выход дополнительного элемента И соединен с четвертым коммутационным входом операционного блока, пятый коммутационный вход которого соединен с третьим входом схемы переноса первого разряда. Сдвиг в сторону старших разрядов реализуется как и для базового устройства путем увеличения содержимого на капливающего сумматора в два раза. Режим счета с заданным шагом реализуется подачей на шину синхронизации счетных импульсов, предварительно установив на входах операнда код шага счета. Режим сдвига в сторону младших . разрядов является режимом, расширяющим функциональные возможности операционного блока относительно базового устройства, и реализуется путем вычитания из содержимого накапливающег сумматора этого же содержимого, но сдвинутого вправо. На фиг. 1 представлена функционал ная схема операционного блока, на фиг. 2 - соединение входов и шин. Операционный блок содержит шину 1 обнуления; шину 2 синхронизацииj пер вую 3J вторую 4, третью 5 шины управ ления, п одноразрядных накапливающих сумматоров, в каждый из которых входя счетный триггер 6, сумматор 7 по mod 2, коммутатор, состоящий из первого 8 и второго 9 элементов И, допблнительного двухвходового элемента И 10 и элемента ИЛИ 11, схемы 12 переноса; дополнительный трехвходовой элемент И 13, выход k переноса операционного блока , первый 15, второй 16, третий.17, четвертый 18, пятый 19 коммутационные входы операционного блока, входы 20 операнда; инфор мационные выходы 21 операционного блока. Первый вход первого элемента И 8 соединен с входом 20 данного разряда операнда, первый вход второго элемен та И 9 соединен с прямым выходом сче ного триггера 6 и первым входом схемы 12 переноса данного разряда, вторые входы первого В и второго 9 элементов И соединены соответственно с первой 3 и второй управляющей шиной, выходы элементов И 8 и 9 соединены с первым и вторым входами элемента ИЛИ 11, выход которого соединен с первым входом сумматора 7 по mod 2 и вторым входом схемы 12 пере носа, второй вход сумматрра ,7 по mod 2 соединен с третьим входом схемы 12 переноса, прямые выходы счетны триггеров 6 соединены с информационными выходами 21 операционного блока, выходы схемы 12 переноса i-ro разряда, кроме старшего, соединены с третьим входом схемы 12 переноса (i-fl)TO разряда, выход схемы перено са 12 старшего разряда является выходом 14 переноса операционного блока, выход сумматора 7; по mod 2 соединен с Т;-входом счетного триггера 6,, шина 2 синхронизации операционного блока соединена с входами синхронизации счетных триггеров 6, шина 1 обнуления соединена с входами начальной установки триггеров 6, первый вход дополнительного двухвходо-вого элемента И 10 i-ro разряда. кроме старшего, соединены с инверсным выходами счетных триггеров 6,(i+1 )-го разряда, первый вход дополнительного двухвходового эле мента И 10 старшего разряда соединен с первым коммутационным входом 15 операционного блока, вторые входы дополнительных двухвходовых элементов И 10 соединены с третьей шиной 5 управления и первым входом дополнительного трехвходового элемента И 13, второй вход которого соединен с инверсным выходом счетного триггера 6. младшего разряда и вторым коммутационным входом 16 операционного блока, третий вход дополнительного трехвходового элементы И 13 соединен с третьим коммутационным входом 17 операционного блока, выход дополнительного трехвходового И 13 и третий вход схемы 12 переноса младшего раряда соединены с четвертым 18 и пятым 19 коммутационными входами операционного блока соответственно.. Операционный блок работает следующим образом. Для выполнения функций суммирования, сдвига влево и сдвига.вправо необходимо выход 1 переноса операцион ного блока соединить с третьим коммутационным входом 17 операционного блока, четвертый 18 и пятый 19 коммутационные входы соединить между собой, первый коммутационный вход 15 соединить с третьей шиной 5 управения. Тогда функция возбуждения для Т -вход-а триггера 6, i-ro разряда кроме старшего и младшего разрядов, перационного блока будет -т; (Xgoj.Ij VS|l4VS;,l5)©P;,,. Для старшего разряда функция озбуждения имеет вид т„ (.,.,. Значення выходных сигналов пере- j оса i-ro разряда, кроме старшего младшего разряда будут Р; P;.,.S; VPj.XjojIjVSiI VSit, xl5)VS;(X,jo..,VS;,l5). ля старшего разряда значение сигнаа переноса вычисляется по формуле РП РИМ- S П V РПН ( V В„ 14 V Ig )V VS CX onliVS I VIj). 717 Значение функции возбуждения для младшего разряда определяется, выражениемТ, (X, S, )©(PnS,l5) Перенос из младшего разряда будет связан с сигналом переноса из старшего разряда Р (,l5)(P,S,l5)(X,jl3VS,x )VS(X20,l5VS,l,VS,jl5), где I,, Ig- управляющие сигналы на соответствующих шинах управления. Из приведенных выражений видно, что возможны три режима работы операционного блока: 1 1 Режим суммирования. Функция возбуждения для Т-5 Омладшего разряда в этом случае будет

TI X

lOt

а перенос из младшего разряда зависит только от значения сигнала в младшем разряда операнда и состояния триггера 6 этого разряда

Р - , Для остальных разрядов Tj и Р; будут

л Т; Хзд;©Р;м,(О

Р; P,--,S;V.Pi.,X2o;MS; X,,-(2j

Выражения (1) и (2) соответствует функциям одноразрядного сумматора, построенного на синхронном Т-триггер Значение выходного сигнала на информационной шине 21 для любого разряда после подами синхроимпульса по шине 2 определяется по формуле:

S; (t + &t) S; (t)@T;.(t),

что соответствует сложению двоичных цифр S;(t) и учетом переноса из млади их разрядов Р,,. Задавая на входной шине 20 код шага счета можно при подаче синхроимпульса по шине 2 производить счет с заданным шагом.

Режим сдвига влево (в сторону старших разрядов). 1(1, 1 15 Ос Данный режим обеспечивается коммутацией на первый вход сумматоров 7 по mod 2 значений сигналов состояния триггеров 6 в соответствующих разрядах. В этом случае при псдаче синхроимпульса по шине 2 произойдет суммирование числа, находящегося в сумматоре, с самим соОчевидно, что для реализации данного принципа необходимо на коммутатор (элемент И 10„) старшего разряда подать логическую единицу, что обеспечивается соединением первого коммутационного входа 15 с третьей шиной 5 управления, а на схему 12 переноса младшего разряда подать конъюнкцию S, Р, что обеспечивается дополнительным трехвходовым элементом И 13 и попарным соединением входов 17, 1 и 18, 19 соответственно. Предлагаемая организация универсального операционного блока позволяет практически неограниченно наращивать разрядность операндов. Для этого необходимо соединить входы и шины в соответствии с фиг.2.

Управляющие шины 3 и Л, шины синхронизации 2 и обнуления 1 соединяются параллельно и являются входами расширенного операционного блока. Первый коммутационный вход 15j j-ro операционного блока, кроме старшего соединяют,с вторым коммутационным входом I6j + i (j-fl)-ro операционного блока. Выход переноса И j-ro операционного блока кроме старшего соединяют с пятым 19 коммутационным входом (j4-l)-ro операционного блока. Выход l4 переноса старшего операционного блока соединяют с третьим коммутационным входом 174 младшего операционного блока, четвертый коммута5 бой, т.е. увеличение его в два раза, что соответствует сдвигу числа влево. S;(t+ ut) S;(t)@S;(t)©P-,(t) Режим сдвига вправо. 1г 1. Данная операция основана на принципе вычитания из исходного мисла S его половины S(t+ &t) .S(t) - S(t)/2. Если к исходному числу S(t) прибавить по правилам сложения обратных кодов инверсию от этого числа S(t), сдвинутую вправо относительно исходHoroj то в результате получим половину от исходного числа, что соответст вует сдвигу вправо ционный вход 18( младшего операционного блока соединяют с пятым коммутационным входом Входной операн подается на входные информационные шины 20 операционных блоков, а инфор мация снимается с выходных информационных шины 21 о Первый коммутационный вход 15 старшего операционного блока соединяют с третьей шиной 5 уп равления каждого операционного блока Технико-экономическая эффективность предлагаемого универсального операционного блока определяется воз можностью выполнять на одном устройctse функции сумматора, счетчика, регистра сдвига вправо и влево, а также возможностью наращивания разрядности обрабатываемых операндов. ф о р м у л аизобретения Универсальный операционный блок содержащий п одноразрядных накапливающих сумматоров, каждый из которых состоит из счетного триггера, сумматора по mod 2, первого и второго элементов И, элемента ИЛИ, схемы переноса, причем первый вход первого элемента И соединен с входом данного разряда операнда сумматора, первый вход второго элемента И соединен с прямым выходом счетного триггера и первым входом схемы переноса данного разряда, выходы первого и второго элементов И соединены с первым и вто рым входами элемента ИЛИ, выход которого соединен с первым входом сумматора по rood 2 вторым входом схемы переноса, второй вход сумматора по mod 2 соединен с третьим рходом схемы переноса, выход сумматора по rood 2 соединен с Т-входом счетного триггера, вторые входы первого и второго элементов И соединены соответственно с первой и второй шинами управления операционного блока, информационные разрядные выходы которого соединены соответственно с прямыми выходами счетных триггеров, выход схемы переноса 1-го разряда (где i 1,2,3,4, .,,п-1) соединен с третьим входом схемы переноса (i+l)-ro разряда, выход схемы переноса п-го разряда является выходом переноса операционного блока, шина синхронизации которого соединена с входами синхронизации п счетных триггеров,входы начальной установки которых соединены с шиной обнуления операционного блока, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения сдвига операнда в сторону младших разрядов, в негр дополнительно введены п третьих двухвходовых эле- ментов И и дополнительный трехвходовой элемент И, причем первый вход третьего элемента И i-ro разряда соединен с инверсным выходом счетного триггера (i+1)-ro разряда, первый вход третьего элемента И п-го разряда соединен с первым коммутационным входом операционного блока, вторые входы п третьих элементов И соединены с третьей шиной управления операционного блока и первым входом дополнительного элемента И, второй вход которого соединен с инверсным выходом счетного триггера первого разряда и вторым коммутационным входом операционногЬ блока, третий вход дополнительного элемента И соединен с третьим коммутационным входом операционного блока, выход дополнитель- ного элемента И соединен с четвертым коммутационным входом операционного блока, пятый коммутационный вход коорого соединен с третьим входом схеы переноса первого разряда.

Фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Арифметико-логическое устройство для вычитания чисел по модулю | 2016 |

|

RU2628175C1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для сложения п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU824203A1 |

| Устройство для умножения | 1978 |

|

SU896617A2 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

Изобретение относится к вычислительной технике и может быть ис~пользовано в арифметических устройствах различного назначения. Цель изобретения - расширение ф:/нкциональ- ных возможностей за счет обеспечения сдвига операнда в сторону младших разрядов» Блок содержит шину 1 обнуления, шину 2 синхронизации, три шины 3-5 управления, п одноразрядных накапливающих сумматоров, в каждый из которых входят триггер 6, сумматор 7 по mod 2, три элемента И 8 - 10, элемент ИЛИ 11, схему 12 переноса, элемент И 13, выход 14 переноса, пять коммутационных входов 15 - 19, вход 20 операнда и информационные выходы 21, соединенные между собой функционально» 2 ил.^318 J9фиг.1сл00 СП>&

| Соловьев Го Но Арифметические устройства ЭВМо — Но: Энергия, 1978, Со, 89, 90, рисо ^-15, А-16,Авторское свидетельство СССР (по заявке № Л70^Э8'»/2'» с решением о выдаче от 30.1Оо89), кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-23—Публикация

1990-05-10—Подача