а в накапливающий сумматор введен (п -1- 2) разрядный сумматор, причем выходы второй группысумматоров и (п + 2) разрядного сумматора явялются соответственно первым и вторым информационным выходами накапливающего сумматора, первый и второй информационные входы (п + 2) разрядного сумматора соединены соответственно с информационными входами

третьего и четвертого регистров, входы сброса второго, третьего и четвертого регистров объединены и являются первым управля101цим входом накапливающего сумматора, тактовые входы первого, второго, третьего и четвертого регистров объединены и являются вторым управляющим входом накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Вычислительное устройство | 1985 |

|

SU1262485A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕНИЙ по авт.св.№905814, отличающееся тем, что, с целью повышения быстродействия при нахождении произведения одиночных пар операндов, в него введены элемент НЕ, элемент И-НЕ, коммутатор, причем вход элемента НЕ соединен с шиной управления устройства, а выход - с первым входом элемента И-НЕ, второй вход которого соединен с шиной тактовых импульсов устройства, вход элемента НЕ соеди нен с первым управляющим входом каждого (i,j)-ro вычислительного элемента матрицы, управляющим входом коммутатора, выход элемента PIHE соединен с вторым управляющим входом каждого (i,j)-ro вычислительного элемента матрицы, с вторым управляющим входом накапливающего сумматора, с управляющими входами первого и второго регистров операнда, управляющими входами первого, второго, третьего триггеров , первый и второй информационные выходы накапливающего сумматора соединены соответственно с первым и вторым входами коммутатора, выход которого является выходом устройства, а в каждый

Изобретение относится к вычислительной технике, в частности к выполнению арифметических операций в многорегистровых арифметических устройствах, выполненных на узлах с большой степеню интеграции. По основному авт.св. № 905814 известно устройство для вычисления сумм произведений, содержащее матрицу вычислительных элементов, которая содержит п+1 строк, первые три строки имеют 2п+1 вычислительных элементов, каждая последующая строка матрицы имеет на один вычислительный элемент меньше, последняя строка содержит п+3 вычислительных элемен- тов, (п н- 1)-разрядные первый и второй регистры операнда (.где п - разряд ность операндов), первую и вторую группу элементов И-НЕ, накапливаклций сумматор, причем первая входная ши на соединена с информационными входа ми первого регистра операнда, вторая входная шина соединена с информацион ными входами второго регистра операнда, выходы значащих разрядов первого регистра операнда и второго регистра операнда соответственно соеди нены с первыми входами элементов И-Н первой и второй групп, вторые входы элементов И-НЕ первой группы соедине ы с выходом знакового разряда второго регистра операнда, вторые входы элементов И-НЕ второй группы соединены с выходом знакового разряда первого регистра операнда, первые и вторые информационные входы накапливающего сумматора соответственно соединены с1(п+2) младшими выходами и с (пН-2) старшими выходами вычислительных элементов последней строки матрицы, первый управляющий вход накапливающего сумматора под ключен к шине установки в ноль, выходы накапливающего сумматора соединенЕл с выходной шиной устройства шина тактовых импульсов соединена с управляющим входом накапливающего сум1чатора, с управляющим входом сумматора, с управлякядим входом каждо- ; го вычислительного элемента матрицы, с управляющими входами первого и второго регистров операндов, первый, второй, третий триггеры, первый и второй выходы каждого (i , J ) го вычислительного элемента ( 1 1 , .. ... п, J 2,...,2п) соединены соответственно с первым входом (i +1, j -1)-го вычислительного эле мента и вторым входом (1+1, j+1)-ro. вычислительного элемента, а выходы поразрядной суммы и переноса соответственно с входом поразрядной суммы (1 +1, j )-гоi-вычислительного элемента и входом переноса (i +1, (j-1)-го вычислительного элемента, первый выход каждого (i,j)-ro вычис;лительного элемента (i 1,2п,, j 1) соединен с вторым входом (i + l,j)-ro вычислительного эле йента, а выход поразрядной сум№л с входом поразрядной суммы(i + 1 , j ) -го вычислительного элемента, выход переноса (i,j)-ro вычислительного элемента (i 1, 2, J 2n--i-.l) соединен с входом переноса ( + 1 , j )-го ;вычислительного элемента, вход переноса (2п+1)-го вычислительного элемента второй строки матрицы соединен с выходом первого триггера, вход переноса (2n+l)-ro вычислительного элемента третьей строки матрицы соединен с выходом второго триггера, информационный вход которого соединен с выходом третьего триггера, управляющие входы первого, второго и третьего триггеров объединены и подключены к шине тактовых импульсов, первые и вторые входы вычислительных элементов нечетных столбцов первой строки матрицы поразрядно связаны соответственно с выходами второго и первого регистров операнда, первые и вторые входы вычислительных элементов четных столбцов первой строки матрицы поразрядно связаны соо ветственно с П. младшими выходами первого регистра операнда и с n старшими выходаг и второго регистра операнда, входы поразрядной суммы и переноса вычислительных эле ментов с первого по ц-ый столбец первой строки матрицы поразрядно соединены соответственно с выходами элементов И-НЕ второй группы и с выходами элементов И-НЕ первой груп пы, а входы поразрядной суммы и пе,реноса вычислительных элементов остальных столбцов первой строки матрицы соответственно с выходом знако вого разряда первого разряда второго регистра операнда, которые соответственно соединены с входами первого и третьего триггеров, а каждый вычислительный элемент содержит полусумматор, элемент И, пер вый, второй триггеры, триггер переноса и триггер поразрядной суммы, причем тактовые входы первого, второго триггеров, триггеров поразрядн суммы и переноска объединены и являются управляющим входом вычислитель ного элемента, информационный вход первого триггера является первым входом вычислительного элемента, информационный вход второго триггегра является вторым входом вычислительного элемента, информационные входы триггеров поразрядной суммы и переноса являются соответственно входами поразрядной суммы и переноса вычислительного элемента, выход первого триггера соединен с первым входом элемента И и является первым выходом вычислительного элемента, выход второго триггера соединен с вторым входом элемента И и является вторым .выходом вычислительного |Элемента, выход элемента И соединен с первым входом полусумматора, второй и третий входы которого соедине ны соответственно с выходами тригге ров поразрядной суммы и переноса, первый выход полусумматора является выходом переноса вычислительного элемента, второй выход полусумматора является выходом поразрядной су1«1мы вычислительного элемента, а накапливаклций сумматор содержит пер вую группу из (п+1о§2К+2) полусумма торов, вторую группу из (n+log2N+l) полусумматоров, первый {n+log2N)-pa рядный регистр, второй (n+log2N+l)разрядный регистр, третий и четвер.тый (пн-2)-разрядные регистры, причем тактовые входы первого, второго третьего и четвёртого регистров объединены и являются вторым управляющим входом накапливающего сумматора, информационные входы третье го и четвертого регистров являются соответственно вторым и первым информаицонными входами накапливающе го сумматора, (п+1) младшие разряды третьего и четвертого регистров поразрядно соединены соответственно с первыми и вторыми входами соответствующих (п+1)-ых младших полусумматоров первой группы, старшие разряды третьего и четвертого регистров соответственно соединены с первым и вторым входами (log2N+l)го полусумматора первой группы, третьи входы (n-Hog N + l) старших полусумматоров первой группы соединены поразрядно с выходами второго регистра, выходы (n+log H-i-l) младших и выходы ( n-flog2N + l) старших полусумматоров первой группы поразрядно соединены с первыми и вторыми входами полусумматоров второй группы, выходы первого регистра соответственно соединены с третьими входами (n+logjN) старших полусумматоров второй группы, выходы (.n+log2N) младших полусумматоров второй группы поразрядно соединены с информацион- ными входами первого регистра, выходы (n+log2N+1) полусумматоров второй группы поразрядно соединены с информационными входами второго регистра и являются выходами накапливающего сумматора, вход установки в ноль первого регистра явпяется первым управляющим входом накапливающего сумматора l . С помощью этого устройства возможно нахождение (n + loggK- - ) старших разрядов суммы произведений N пар операндов, представленных дополнительным кодом, при этом на каждом следующем такте на входы устройства может быть принята новая пара сомножителей (п-разрядность операндов J. Для получения на ь-ыходах устройства результата с распространенными переносами на его вуоды в течение (r.+log2H) тактов должны быть поданы нулевые сомножители. .При этом операнды новой nocj. ловательности на входы устройства могут подаваться на (n+log2N+l)-ом такте. Недостатком этого устройства является то, что при вычислении произведений одиночных пар сомножителей очередная пара сомножителей может быть принята на входы устройства только по истечении (п + -Hog.N) холостых тактов после прие- . ма предыдущей пары. Цель изобретения - повышение быстродействия при нахождении произведения одиночных пар операндов. Поставленная цель достигается тем, что в устройство вводятся элемент НЕ, элемент И-НЕ, коммутатор, причем вход элемента НЕ соединен с шиной управления устройства, а выход - с первым входом элемента И-НЕ, второй вход которого соединен с шиной тактовых импульсов устройства, вход элемента НЕ соединен с первым управляющим входом

каждого (ijjj-ro вычислительного элемента, матрицы, управляющим входом .коммутатора, выход элемента ИНЕ соединен с вторым управляющим входомкаждого {i,j)-ro вычислитель ного элемента матрицы, с вторым управляющим входом накапливающего сумматора, с управляницими входами первого и второго регистров операнда, управляющими входами первого второго, третьего триггеров, первый и второй информационные выходы накапливающего сумматора соединены .соотверственно с первым и вторым входами коммутатора, выход которого является выходом устройства, а в кадый ( i , ,1 ) -ый вычислительный элемент введены второй, третий, четвертый, пятый элементы И,-первый, второй, третий и четвертый элементы ИЛИ, причем первый вход второго элемента- И, управляющие входы первого, второго триггера,-триггера поразрядной суммы и триггера переноса объединены и являются вторым управляющим входом ti,j)-ro вычислительного элемента,второй, .вход второго элемента И, первые входы третьего, четвертого и пятого элементов И объединены и являются первым управляющим входом Ci,j}-ro вычислительного элемента, второй вход третьего элемента И соединен с информационны входом триггера поразрядной суммы, второй вход четвертого элемента И соединен с информационным входом .триггера переноса, второй вход пятого элемента И соединен с информационным входом второго триггера, выход второго элемента и и выход первого триггера соединены соответственно С первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ и является вторым выходом (i,j -ro вычислительного элемента, выход второго элемента ИЛ соединен с входом поразрядной суммы одноразрядного сумматора, вход переноса которого соединен с выходом третьего элемента ИЛИ, выход третьего элемента И и выход триггера поразрядной суммы соединены соотверственно с первым и вторым входами второго элемента ИЛИ, выход четвертого элемента И и выход триггера переноса соединены соответствено с первым и вторым входами третьего элемента ИЛИ, выход пятого элемента И и выход второго триггера соединены соответственно с первым и вторым входами четвертого элемента ИЛИ а в накапливающий сумматор введен (п+.) разрядный сумматор, причем : выходы второй группы сумматоров и ;(п-ь2) разрядного сумматора являются

соответственно первым и вторым информационными выходками накапливающего сумматора, первый и второй информационн е входы (п + 2) разрядного сумматора соединены соответственно с информационными входами третьего и четвертого регистров, входы I второго, третьего и четверTolrb регистров объединены и являются первым управлякмцим входом накапливающего сумматора, тактовые входы первого, второго, третьего и четвертого регистров объединены и являются вторым управляющим входом накапливающего сумматора.

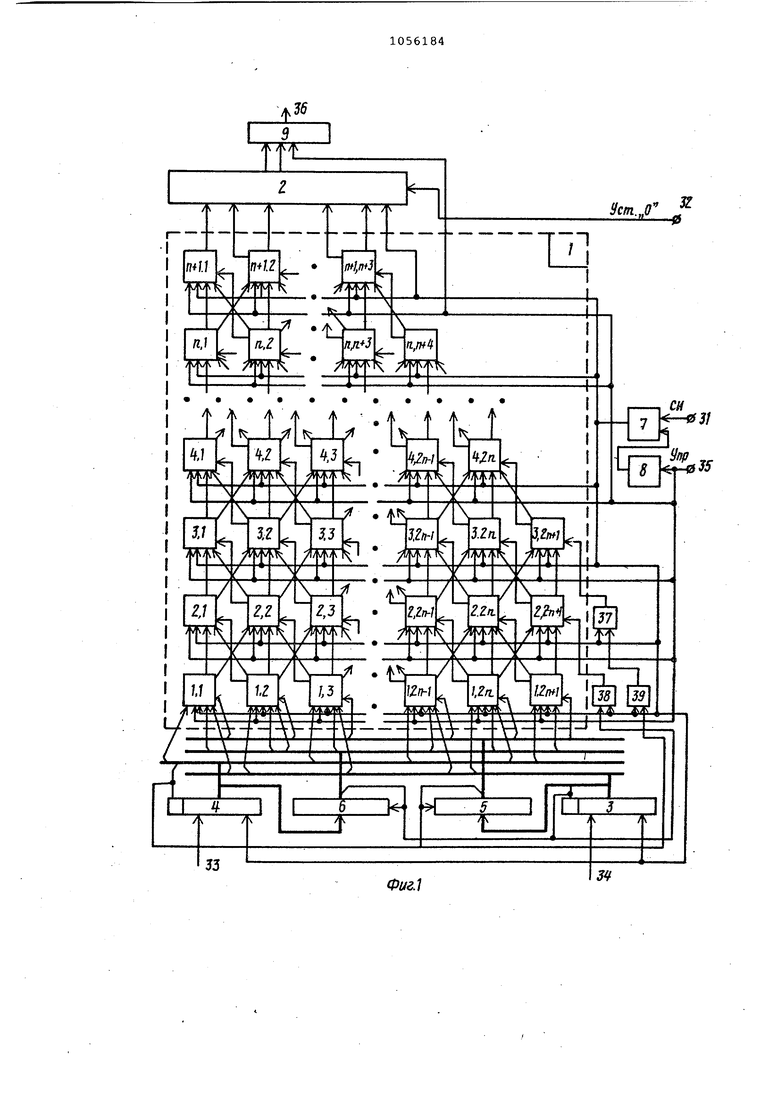

На фиг. 1 изображена структурная схема предлагаемого устройства/ на фиг. 2 - структурная схема вычислительного элемента; на фиг. 3 структурная схема накапливающего сумматора.

Устройство состоит из матрицы 1 вычислительных элементов, имеющей п+1 строку, причем первые три строки содержат по ()-му вычислительному элементу, а каждая последующая строка имеет на один вычислительный элемент меньше по сравнению с предыдущей, накапливающего сумматора 2, :регистров: 3 и 4 операндов, группы элементов И-НЕ 5 и элемента И-НЕ 7, элемента НЕ 8,и коммутатора 9. Одноразрядный элемент 1 содержит одноразрядный сумматор 10, элемент И 11, триггеры 12 и 13, триггер 14 поразрядной суммы, триггер 15 переноса, элементы И 16-19, элементы ИЛИ 20-23. Накапливакщий сумматор 2 содержит регистры 24-27, группы одноразрядных сумматоров 28 и 29 и (п+2) разрядный сумматор 30, Кроме того, в устройстве имеется тактовая шина 31, шина 32 установки в О, щины 33 и 34 операндов, управляющая шина 35, выходная шина 36 и

триггеры 37-39.

Устройство работает следующим образом.

При наличии на упрёвляющей шине 35 логического О устройство принимает на каждом такте новую пару операндов, при этом элементы И 16-19 в вычислительных элементах 1 заперты низким управляквдим уровнем, а выходы второй группы сумматоров 28 через коммутатор 9 поступают на выходную шину 36,

При наличии на управляющей шине 35 уровня логический 1 сигнал с выхода элемента НЕ 8 поступает на вход элемента И-НЕ 7 и запрещает поступление тактирующих импульсов на все триггеры и регист ы устройстве. Тем самым он запрещает прием информации в триггеры 12-15 каждого (i,j)-ro вычислительного элемента матрицы 1 и регистры 24накапливающего сумматора 2. Одновременно этот сигнал, поступая на первые входы элементов И 16-19 каждого вычислительного элемента матрицы 1 разрешает распространение сумм и переносов в матрице 1 вычислительных элементов и накапливающем сумматоре 2. Содержимое регистров 3 и 4 (где находится пара сомножителей А и В в дополни тельном двоичном коде) передается на элемент И 11, на первый вход ко торого будет подан код Ь а.Ъ . , . а.Ь„.,а,Ьп ,а на второй вход (, ,,. ап.Ъ„.а„. Вместе код ад UQ с этим, в зависимости от знаков сомножителей и в соответствии с табл. 1, через элемент И 17 и ИЛИ 21, а также через элементы И и ИЛИ 22 на входы сумматоров 10 вычислительных элементов первой строки через группы элементов И-НЕ 5 и б поступят удвоенные обратные коды содержимого регистров 3 и 4. При этом, если произоиша передача удвоенного обратного кода какоголибо из сомножителей на входы мат рицы 1, через триггер 38 либо чер триггер 39 распространится 1, п назначенная для формирования допол нительного кода этого сомножителя Это необходимо для коррекции резул тата, так как в результате перемн жения в Матрице 1 вычислительных элементов чисел А и В,представленны дополнительным кодом, знаковые ра ряды операндов участвуют в выполн емой операции наравне со значащим и происходит искажение результата I Формирование произведения в виде поразрядных сумм и переносов происходит в результате ихраспрос ранения с 1-ой строки на i+1 строку и т.д. до последней строки матрицы вычислительных элементов. При чем распространение переносов i-ой строки матрицы 1 вычислительных эл ментов к i+1 строке матрицы 1 осуществляется через Элементы И 16 и ИЛИ 20 со сдвигом на один разряд в во, а через элементы И 19 и ИЛИ 23 со сдвигом на разряд вправо, что обеспечивает формирование всех п+1 частичных произведений. С выходов последней строки матрицы 1, содержащей п+3 вычислительных элементов значения (п+2)-ых старших поразряд ных сумм и переносов, представляющих п+2 старших разряда произведения, поступают на первые и вторые входы (п+2)-ых разрядного сумматора 30 и с его выходов после распро транения переноса произведение пары операндов через коммутатор 9 поступает на выходную шину 36, при этом коммутатор 9 пропускает информацию с выходов (п+2) разрядного сумматора 30 при высоком уровне на шину 35. Длительность такта в известном устройствене может быть меньше суммы задержек распространения сигнала через триггер (), одноразрядный сумматор (t, ) и элемент И (t,,) вычислительного элемента. т iT сч Зи При использовании элементов 155 серии эти задержки соответственно составляют: tj-, 20 не, t 15 не, 8 НС, а минимальное время такта t 43 НС. Таким образом, в известном устройстве на выходе матрицы 1 вычислительных элементов через Тч (п+1) xt,, появится произведение пары операндов в виде поразрядных сумм и переносов. Для получения произведения пары операндов с распространенными переносами необходимы еще п+2 такта работы накапливающего сумматора, при этом новые операнды на выходы устройства принимать нельзя. Таким образом, при разрядности операндов п 16 на выходе устройства произведение появится через (2п+3) такта или через 1505 НС ,5 МКС. В предлагаемом устройстве задержка распространения сигнала через вычислительный элемент состоит из суммы задержек на двух элементах И (2t3y), элементе ИЛИ (1)„д, ) и одноразрядного сумматора ( Ч(„). При его реализации на элементах 155 серии задержка распространения сигнала через одноразрядный элемент составит tf 2tl + t-jKAU + .HvjM 2 +8 + 15 (не); ЧиАИ Так как матрица 1 вычислительных элементов состоит из (п+1)-ой строки, то череэ Т (п+1) tj. на ее выходе появится произведение пары операндов в виде поразрядных сумм и переносов. Это время составляет т| (16 + 1)39 663 НС. Для получения произведения с распространенными переносами необходимо поразрядные суммы и переносы подать на 18 разряд (при ), сумматор с групповым переносом, реализованный на 5-ти микросхемах ; Н155ИПЩ и одной микросхеме К155ИП4, при этом время задержки распространения сигнала составит т 90.не. Общее время умножения пары операндов, таким образом, в предлагаемом устройстве составляет 753 нсгО,75 мкс, что в 2 раза меньше, чем в известном.

Дополнительные

Сомножители коды А и В АЙВ

О В О

А; В l-f(l-A) В

О).В О

AJ 14-(1-В)

О; В О 1+(1-А)} l-f(l-B)

Of В (I Примечание. При А О и в О ментов будет представляет

Результат без

Коррекция коррекции

А X В А X В

II+CI-A)) хв 2В-АВ

Ах(1+(1-В)) 2А- АВ (1+(1-А)) х(1+(1-В) 4-2В-2А+АВ на выходах матрицы 1 вычислительных элерезультат -2В -2А.+АВ, так как четверка собой перенос в несуществующий разряд.

/k

.z

e1

,

/

h A

.

I lyU I U- I : к 1 |VL Л 4,Z .3 .

Уш.„0 /

/i,

СИ -0J/ yf

Упр

55

Фиг. I

1/71 I гч

/ч/ч /ч

/Г

6

М J /

1f 1

s /ч 7ч

I 30 I

177

ч 7v

Ч /ч

74

зг

is;7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-23—Публикация

1982-08-17—Подача