1

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств в любой позиционной системе.

По основному авт.св. № 769540 известно устройство для умножения, содержащее регистры множимого и множителя, накапливающий сумматор, п постоянных запоминающих блоков и буферных регистров (п - разрядность операндов), причем первый, второй и третий адресные входы каждого постоянного запоминающего блока подключемы к выходам соответствукяцего разряда регистра множимого, выходу первого разряда регистра множителя и выходу соответствующего буферного регистра, вход которого соединен с выходом старших разрядов соответствующего постоянного запоминающего блока, выход младших разрядов которого подключен ко входу соответствующего разряда накапливагадего сумматора, первый, второй и .третий управляющие входы устройства подключены ко входам сдвига регистра множителя, и накапливающего сумматора и с управляющими входами перезаписи буферных резисторов Cl 1Недостатком этого устройства является недостаточное быстродействие, ввиду использования накапливающего сумматора с распространением переноса.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что каждый разряд накапливающеtoго сумматора содержит одноразрядный накапливающий сумматор, два коммутатора, узел хранения переноса, узел формирования транзитного переноса и узел формирования выходного

ts переноса, причем входы первого коммутатора подключены ко входу данного разряда накапливающего сумматора и выходу одноразрядного накапливающего сумматора последующего разряда, а выход - ко входу накаплнвакяцего

20 сумматора данного разряда, выход которого подключен к выходу данного разряда накапливакидегр сумматора, выход переноса одноразрядного накап25ливакидего сумматора соединен со входом узла хранения переноса, выход которого соединен с первым входом узла формирования выходного переноса, выход которого является выходом переноса из данного разряда,накапли30

веющего сумматора, входы второго коммутатора соединены с выходом блока хранения переноса и входом переноса из предыдущего разряда накап ливающего сумматора, а выход - со входом переноса одноразрядного накапливающего сумматора, входы узла формирования транзитного переноса соединены с выходом одноразрядного накапливающего сукотатора и входом переноса из предьшувдего разряда накапливающего сумматора, а выход подключен ко второму входу узла формирования выходного переноса, управляющий вход первого коммутатора соединен со входом управления сдвигом накапливающего сумматора, управляющий вход разрешения записи одноразрядного накапливающего сумматора соединен с четвертым управляющим входом устройства, управляющие входы блока хранения переноса и второго коммутатора соединены с пятым и шестым управлякяцими входами устройства.

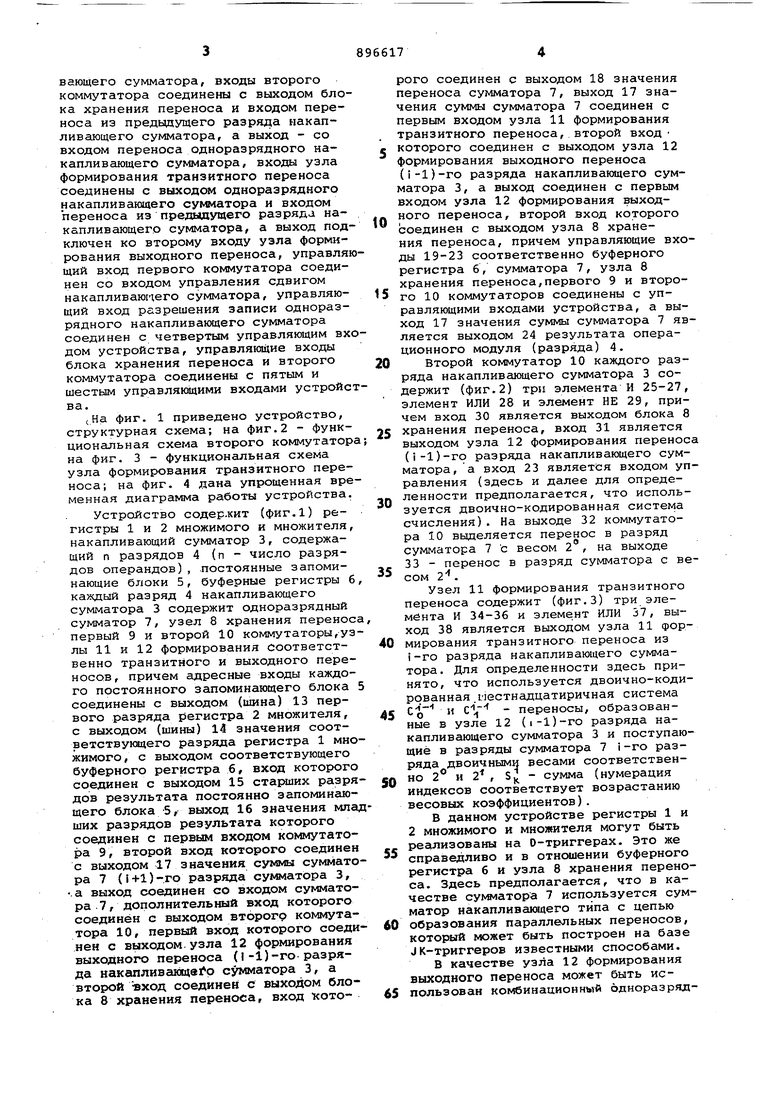

с На фиг. 1 приведено устройство, структурная схема; на фиг.2 - функциональная схема второго коммутатора на фиг. 3 - функциональная схема узла формирования транзитного переноса; на фиг. 4 дана упрощенная временная диаграмма работы устройства.

Устройство содержит (фиг.1) регистры 1 и 2 множимого и множителя, накапливающий сумматор 3, содержащий п разрядов 4 (п - число разрядов операндов), .постоянные запоминающие блоки 5, буферные регистры 6 каждый разряд 4 накапливающего сумматора 3 содержит одноразрядный сумматор 7, узел 8 хранения переноса первый 9 и второй 10 коммутаторы,узлы 11 и 12 формирования соответственно транзитного и выходного переносов, причем адресные входы каждого постоянного запоминающего блока 5 соединены с выходом (шина) 13 первого разряда регистра 2 множителя, с выходом (шины) 14 значения соответствуницего разряда регистра 1 множимого , с выходом соответствующего буферного регистра 6, вход которого соединен с выходом 15 старяиих разрядов результата постоянно запоминающего блока 5, выход 16 значения младших разрядов результата которого соединен с первым входом коммутатора 9, второй вход которого соединен с выходом 17 значения суммы сумматора 7 (1+1)-го разряда cyNwaTOpa 3, .а выход соединен со входом сумматора 7, дополнительный вход которого соединён с выходом второго коммутатора 10, первый вход которого соединен с выходом.узла 12 формирования выходного переноса (I-1)-го разряда накапливаю дв р сумматора 3, а второй вход соединен с выходом блока 8 хранения переноса, вход которого соединен с выходом 18 значения переноса сумматора 7, выход 17 значения суммы сумматора 7 соединен с первым входом узла 11 формирования транзитного переноса, второй вход которого соединен с выходом узла 12 формирования выходного переноса (i-l)-ro разряда накапливающего сумматора 3, а выход соединен с первым входом узла 12 формирования выходного переноса, второй вход которого соединен с выходом узла 8 хранения переноса, причем управляющие входы 19-23 соответственно буферного регистра 6, сумматора 7, узла 8 хранения переноса,первого 9 и второго 10 коммутаторов соединены с управляющими входами устройства, а выход 17 значения суммы сумматора 7 является выходом 24 результата операционного модуля (разряда) 4.

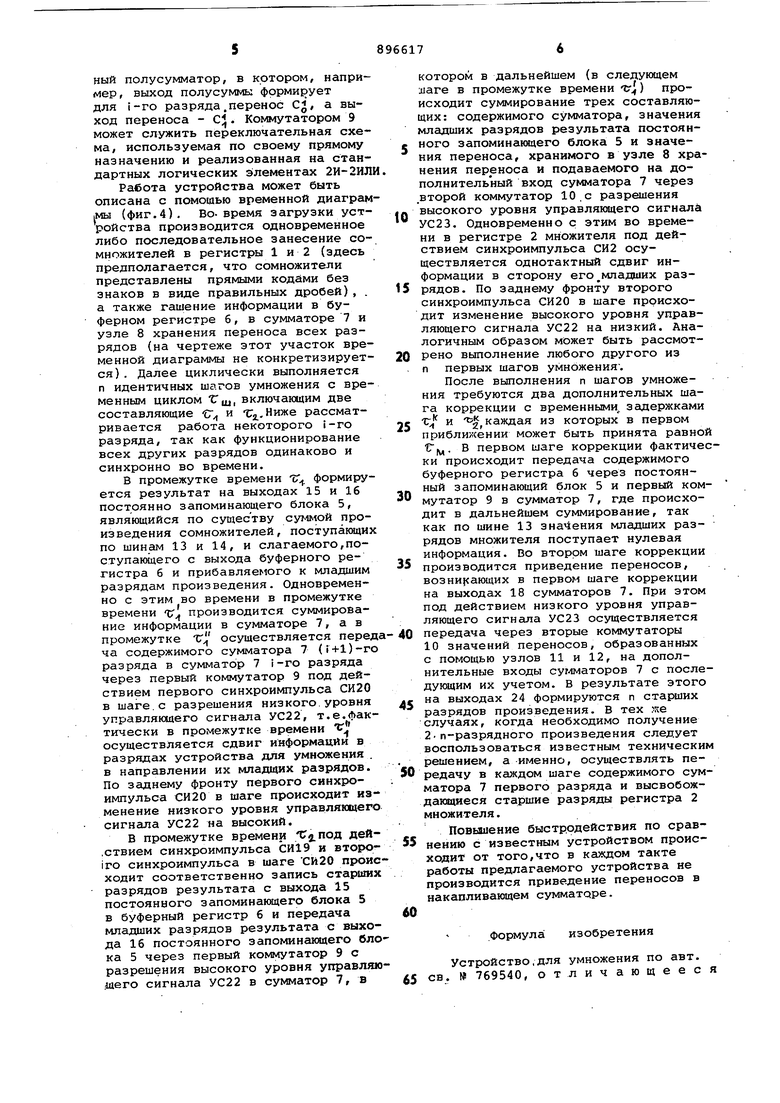

Второй коммутатор 10 каждого разряда накапливающего сумматора 3 содержит (фиг.2) три элемента И 25-27 элемент ИЛИ 28 и элемент НЕ 29, причем вход 30 является выходом блока 8 хранения переноса, вход 31 является выходом узла 12 формирования перенос (i-l)-ro разряда накапливающего сумматора, а вход 23 является входом управления (здесь и далее для определенности предполагается, что используется двоично-кодированная система счисления) . На выходе 32 коммутатора 10 выделяется перенос в разряд сумматора 7 с весом 2°, на выходе 33 - перенос в разряд сумматора с весом 2.

Узел 11 формирования транзитного переноса содержит (фиг.З) три элемента И 34-36 и элемент ИЛИ 37, выход 38 является выходом узла 11 формирования транзитного переноса из i-ro разряда накапливающего сумматора. Для определенности здесь принято, что используется двоично-кодированная .шестнадцатиричная система С и С - переносы, образованные в узле 12 (i-l)-ro разряда накапливающего сумматора 3 и поступающие в разряды сумматора 7 i-ro разряда двоичными весами соответственно 2° и 2 , Sj - сумма (нумерация индексов соответствует возрастанию весовых коэффициентов).

В данном устройстве регистры 1 и 2 множимого и множителя могут быть реализованы на D-триггерах. Это же справедливо и в отношении буферного регистра 6 и узла 8 хранения переноса. Здесь предполагается, что в качестве сумматора 7 используется сумматор накапливакяцего типа с цепью образования параллельных переносов, который может быть построен на базе JK-триггеров известными способами.

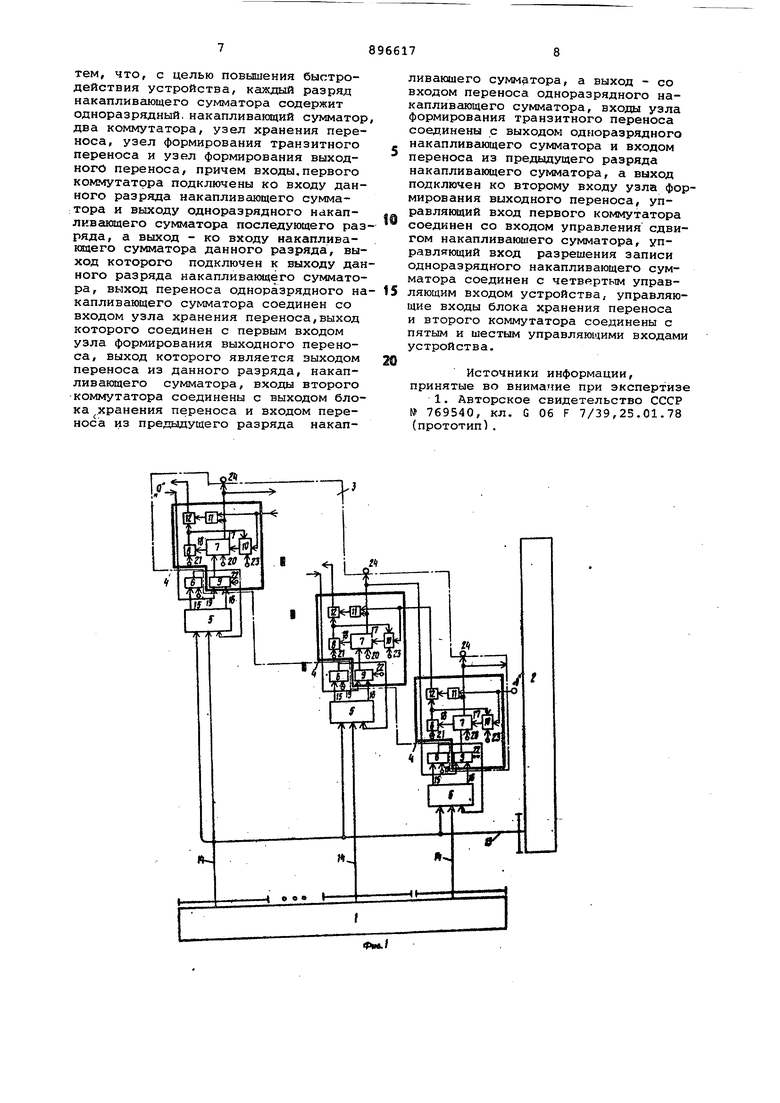

В качестве узла 12 формирования выходного переноса может быть использован комбинационный одноразрядный полусумматор, в котором, например , выход полусуммы фррми)ует для i-ro разряда.перенос С, а выход переноса - С;}. Коммутатором 9 может служить переключательная схема, используемая по своему прямому назначению и реализованная на стандартных логических элементах 2И-2ИЛ Работа устройства может быть описана с помощью временной диаграм 1МЫ (фиг.4). Во-время загрузки устройства производится одновременное либо последовательное занесение сомножителей в регистры 1 и 2 (здесь предполагается, что сомножители представлены прямыми кодами без знаков в виде правильных дробей), . а также гашение информации в буферном регистре б, в сумматоре 7 и узле 8 хранения переноса всех разрядов (на чертеже этот участок временной диаграммы не конкретизируется). Далее циклически выполняется п идентичных шагов умножения с временным циклом Тщ, включающим две составляющие СГ и Тд. Ниже рассматривается работа некоторого i-ro разряда, так как функционирование всех других разрядов одинаково и синхронно во времени. В промежутке времени ТГ формируется результат на выходах 15 и 16 постоянно запоминающего блока 5, являющийся по существу суммой произведения сомножителей, поступакицих по шинам 13 и 14, и слагаемого,поступающего с выхода буферного регистра б и прибавляемого к младшим разрядам произведения. Одновременно с этим во времени в промежутке времени tT производится суммирование информации в сумматоре 7, а в промежутке осуществляется перед ча содержимого суьдалатора 7 (i+l)-ro разряда в сумматор 7 i-ro разряда через первый коммутатор 9 под действием первого синхроимпульса СИ20 в шаге.с разрешения низкого.уровня управляющего сигнала УС22, т.е.фактически в промежутке времени С осуществляется сдвиг информации в разрядах устройства для умножения . в направлении их младщих разрядов. По заднему фронту первого синхроимпульса СИ20 в шаге происходит изменение низкого уровня управляющего сигнала УС22 на высокий. В промежутке времени дей.ствием синхроимпульса СИ19 и второiro синхроимпульса в шаге СИ20 проис ходит соответственно запись старютх разрядов результата с выхода 15 постоянного запоминающего блока 5 в буферный регистр б и передача младших разрядов результата с выхода 16 постоянного запоминающего бло ка 5 через первый коммутатор 9 с разрешения высокого уровня управляю .laero сигнала УС22 в сумматор 7, в котором в дальнейшем (в следующем маге в промежутке времени tr) происходит суммирование трех составляющих: содержимого сумматора, значения младших разрядов результата постоянного запоминающего блока 5 и значения переноса, хранимого в узле 8 хранения переноса и подаваемого на дополнительный вход сумматора 7 через .второй коммутатор 10.с разрешения высокого уровня управляющего сигнала УС23. Одновременно с этим во времени в регистре 2 множителя под действием синхроимпульса СИ2 осуществляется однотактный сдвиг информации в сторону его младших разрядов. По заднему фронту второго синхроимпульса СИ20 в шаге происходит изменение высокого уровня управляющего сигнала УС22 на низкий. Аналогичным образом может быть рассмотрено выполнение любого другого из п первых шагов умножения-. После выполнения п шагов умножения требуются два дополнительных шага коррекции с временными задержками каждая из которых в первом приближении может быть принята равной tr. В первом шаге коррекции фактически происходит передача содержимого буферного регистра б через постоянный запоминающий блок 5 и первый коммутатор 9 в сумматор 7, где происходит в дальнейшем суммирование, так как по шине 13 зна4ения младших разрядов множителя поступает нулевая информация. Во втором шаге коррекции производится приведение переносов, возни| ающих в первом шаге коррекции на выходах 18 сумматоров 7. При этом под действием низкого уровня управляющего сигнала УС23 осуществляется передача через вторые коммутаторы 10 значений переносов, образованных с помощью узлов 11 и 12, на дополнительные входы сумматоров 7 с последукяцим их учетом. В результате этого на выходах 24 формируются п старших разрядов произведения. В тех же случаях, когда необходимо получение 2-п-разрядного произведения следует воспользоваться известным техническим решением, а именно, осуидествлять передачу в каждом шаге содержимого сумматора 7 первого разряда и высвобождаквдиеся старшие разряды регистра 2 множителя. Повьшение быстродействия по сравнению с известным устройством происходит от того,что в каждом такте работы предлагаемого устройства не производится приведение переносов в накапливающем сумматоре. Формула; изобретения Устройство,для умножения по авт. св. № 769540, отличающееся , носа из предыдущего разряда накап896617„ ливаюшего сумматора, а выхоп «формирования JS StoS,Si , Источники информации, принятые во внимачие при экспертизе № 7ко. свидетельство СССР № 769540, кл. G 06 F 7/39,25 01 7Я (прототип)./J,5.01.78

ИФиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

Авторы

Даты

1982-01-07—Публикация

1978-02-15—Подача