Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки информации и в устройствах цифровой обработки сигналов.

Цель изобретения - повышение производительности конвейерного сумматора.

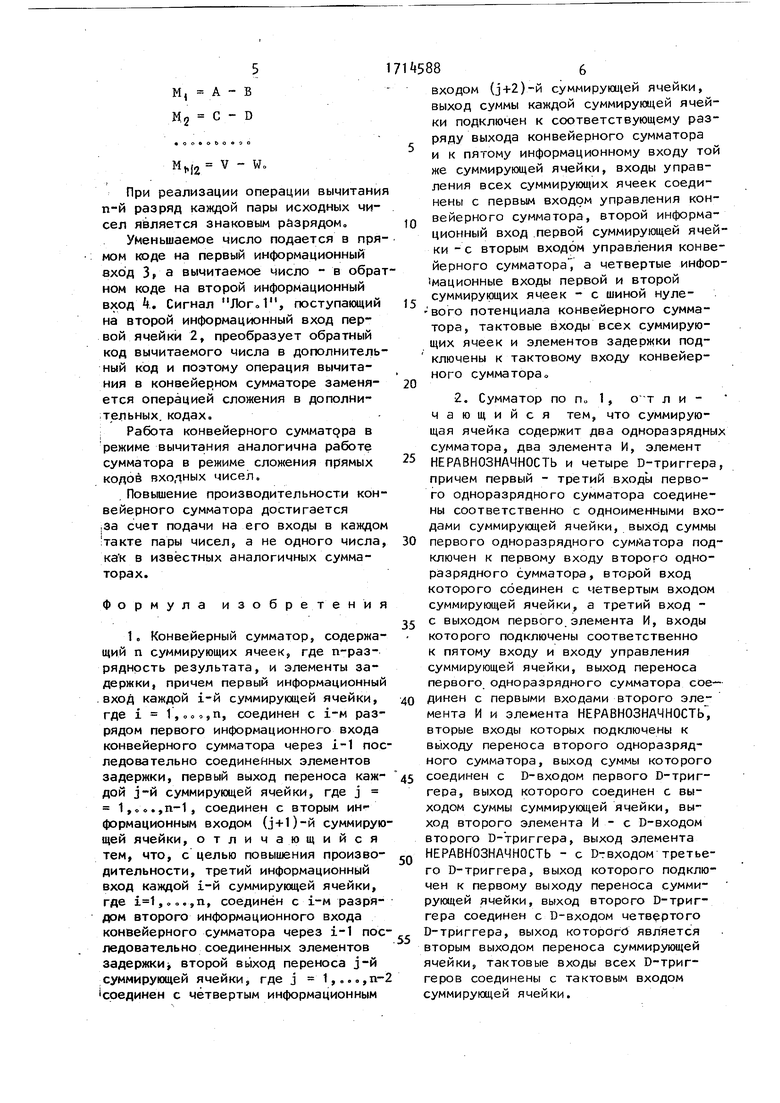

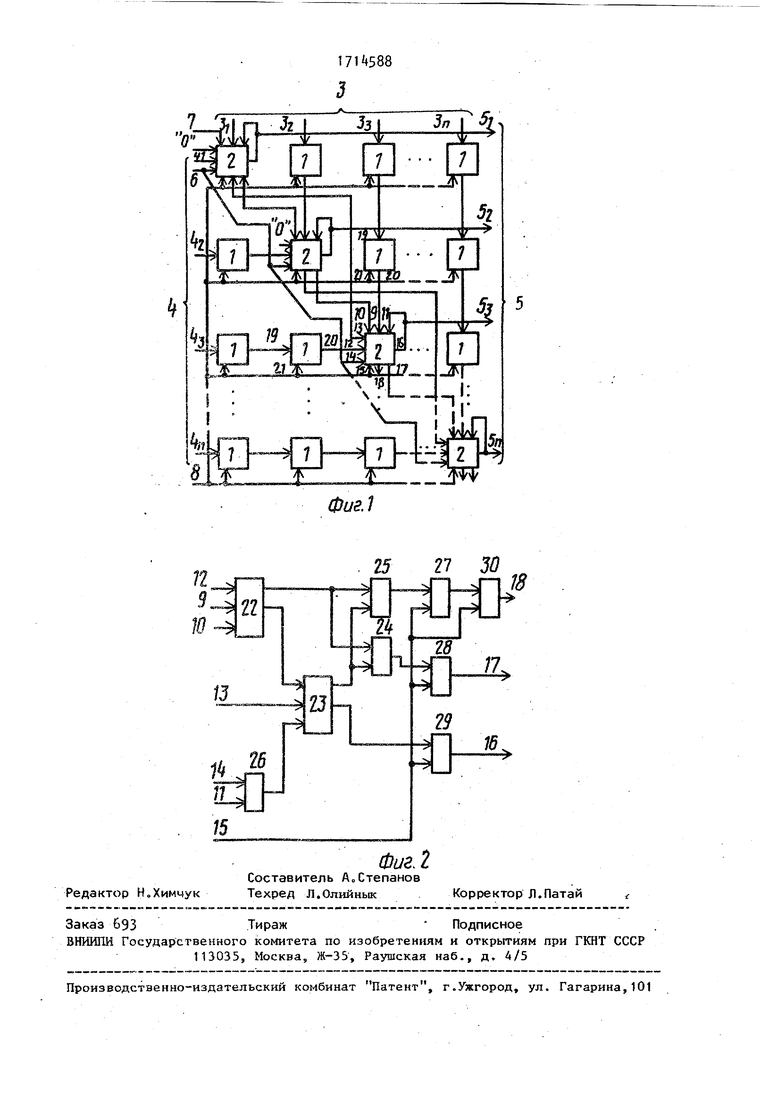

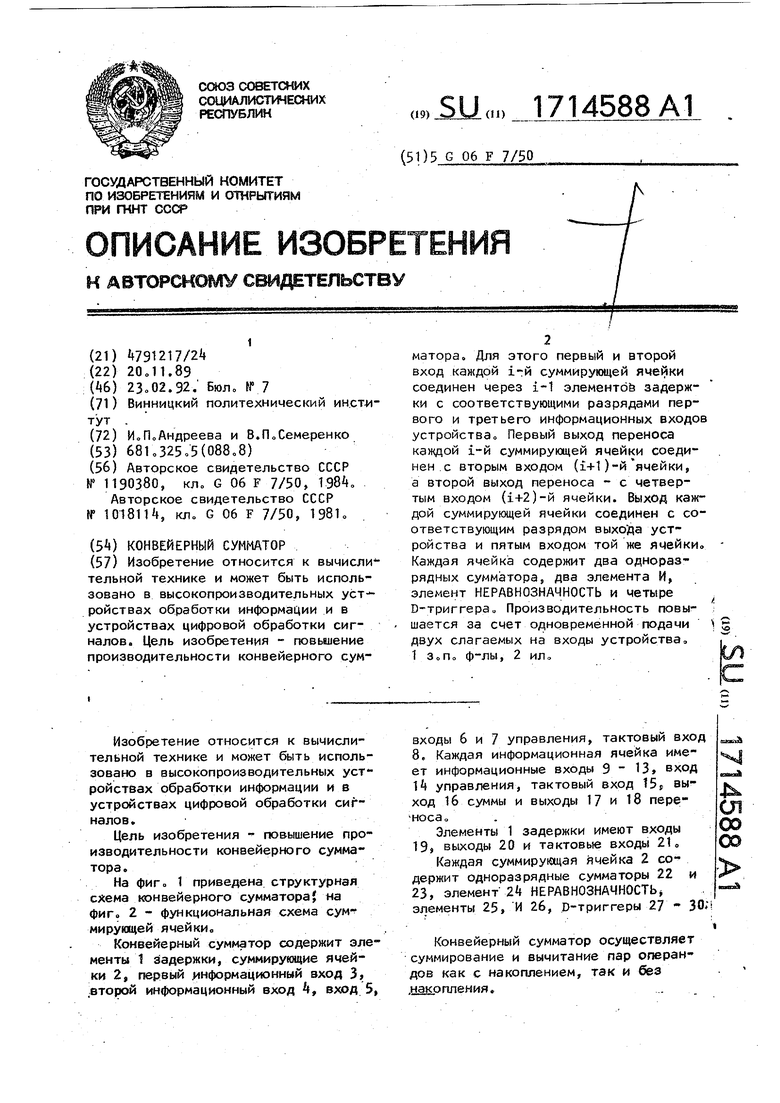

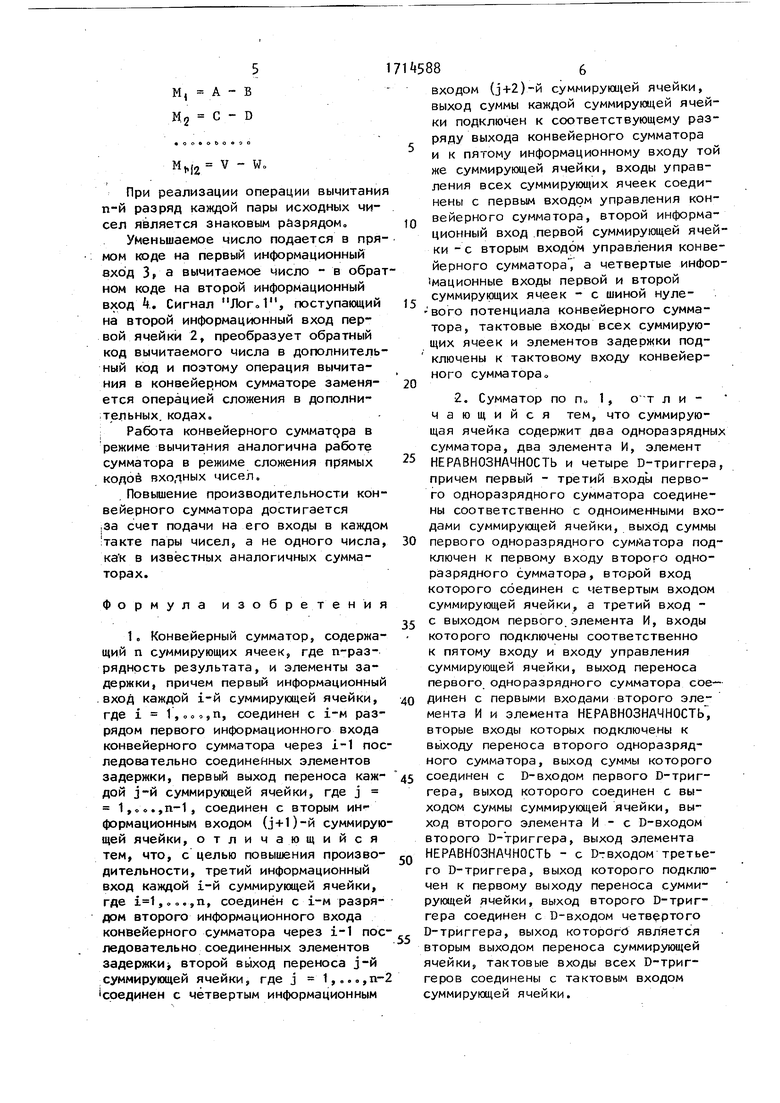

На фиг о 1 приведена структурная схема конвейерного сумматораJ «а фиго 2 - функциональная схема суммиру щей ячейки

Конвейерный сумматор содержит элементы 1 задержки, суммирующие ячейки 2, первый информационный вход 3 второй информационный вход , вход 5,

входы 6 и 7 управления, тактовый вход 8, Каждая информационная ячейка имеет информационные входы Э 13 вход Ii управления, тактовый вход t5f выход 16 суммы и выходы 17 и 18 пере-носа. .

Элементы 1 задержки имеют входы 19 выходы 20 и тактовые входы 21 о

Каждая суммируюцая ячейка 2 содержит одноразрядные сумматоры 22 и 23, элемент 2 НЕРАВНОЗНАЧНОСТЬ элементы 25, И 26, р-триггеры 27 - ЗОЛ

Конвейерный сумматор осуществляет суммирование и вычитание пар операндов как с накоплением, так и без накопления. Конвейерный сумматор работает следующим образом. При подаче на первый вход 6 управления сигнала Лого 1 и на второ вход 7 управления сигнала конвейерный сумматор работает в режиме параллельного накапливающего сумматора. В этом режиме происходит вычисле ние локальной суммы S, г, т-разряд ных исходных чисел. Вычисление суммы Sp осуществляет по тактамс На первом такте работы конвейерного сумматора на первый ин формационный вход 3 поступает парал лельный код первого числа А и одновременно на второй информационный вход А гюступает параллельный код второго числа В, В первой ячейке 2 происходит вы гюлнение операции сложения и формируются значения сигналов суммы и переносов На втором такте работы конвейерного сумматора на информационные входы второй ячейки 2 поступают вто f, чисел А рые разряды а и Ъ „(( переноса Р, также значение псрсп ьа Г2 информационные входы первой ячейки 2 поступают первые разряды с следующей пары чисел С и D, На S-M такте работы на информационные входы первой ячейки 2 посту пают первые разряды и Wry) послед ней пары исходных чисел V и W и н информационном выходе 5 формируетс значение первого разряда суммы S|,o На ( -i- m-1)-M такте работы конв йерного сумматора на информационные входы ш-й ячейки 2 поступают разряд у.и Wp, последней пары исходных чисел V и W и на информационном вых де формируется значение ш-го раз ряда суммы SP. На входы i-й () ячейки 2 кро ме соответствуюдих разрядов двух чи сел поступают также одновременно си нал переноса из /1-1 )-й ячейки SM сигнал переноса {1-2)-й ячейки 2, а на выходах указанной ячейки 2 формируются сигнал суммы S .; и сигнал переноса в (i+1}- o ячейку 2 и .сигнал переноса Р. в (1+2)-ю ячейку 2 о Поскольку возможны переносы при сложении чисел, поэтому для окончанияоперации сложения г чисел, представленных в двоичной форме счисления, необходимо продолжить работу конвейерного сумматора еще в течение 1 тактой: 11о84г, где означает округление до ближайшего целого в большую сторону. Следовательно, разрядность п конвейерного сумматора для вычисления S г, т-разрядных локальной суммы чисел равна: + m . В течение последних тактов работы на разряды 3,,.., 3, первого информационного входа 3 и на разряды орогО информационного входа Ц должны поступать сигналы ЛоГоО. В течение всех тактов работы конвейерного сумматора в этом режиме на разряды 3,,+.,,.... ,3„ первого информационного входа 3 и на разря- . п второго информационного входа должны поступать сигналы Лого О. При подаче на первый вход 6 управления и на второй вход 7 управления сигнала Лог.О конвейерный сумматор работает в режиме сложения прямых кодов входных чисел. В этом режиме происходит вычисление отдельных сумм S ,.., S ,/-2 каадой пары г,п-разрядных исходных чисел: 2,„ V W. В i-й ячейке 2 на (к+1-1)-м такте работы происходит вычисление i-ro разряда суммы К-й пары исходных чисел (,п, К 1,г/2), причем указанное значение сохраняется в ячейках 2 только в течение одного такта. При подаче на первый вход 6 управления сигнала Лог.О и на второй вход 7 управления сигнала Лог конвейерный сумматор работает в режиме вычитания кодов входных чисел. В этом режиме происходит выполнение, операции вычитания отдельных пар ,п-1-разрядных чисел

М, А - в М.2 С - D

V - Wo

М

М2

При реализации операции вычитания п-й разряд каждой пары исходных чисел яйляется знаковым разрядом.

Уменьшаемое число подается в прямом коде на первый информационный вход 3f а вычитаемое число - в обратном коде на второй информационный вход 4. Сигнал Лог.1, поступающий на второй информационный вход первой ячейки 2, преобразует обратный код вычитаемого числа в дополнительный код и поэтому операция вычитания в конвейерном сумматоре заменяется операцией сложения в дополнительных, кодах.

: Работа конвейерного сумматора в режиме вычитания аналогична работе сумматора в режиме сложения прямых кодоё входных чисел.

Повышение производительности конвейерного сумматора достигается |3а счет подачи на его входы в каждом такте пары чисел, а не одного числа, как в известных аналогичных сумматорах.

Формула изобретения

1, Конвейерный сумматор, содержащий п суммирующих ячеек, где п-разрядность результата, и элементы задержки, причем первый информационный

.вход каждой i-й суммирующей ячейки, где i 1,ооо,п, соединен с i-м разрядом первого информационного входа конвейерного сумматора через i-1 последовательно соединенных элементов задержки, первый выход переноса каждой j-й суммирующей ячейки, где j 1,«.,п-1, соединен с вторым информационным входом 0 + 1)-й суммирующей ячейки, отличающийся тем, что, с целью повышения производительности, третий информационный вход каждой i-й суммирующей ячейки, где ,,.,п, соединён с i-м разрядом второго информационного входа конвейерного сумматора через i-1 последовательно соединенных элементов задержки второй выход переноса j-й суммирующей ячейки, где j 1,...,п-2

соединен с четвертым информационным

1А5886

входом (з+2)-й суммирующей ячейки, выход суммы каждой суммирующей ячейки подключен к соответствующему разряду выхода конвейерного сумматора и к пятому информационному входу той же суммирующей ячейки, входы управления всех суммирующих ячеек соединены с первым входом управления конвейерного сумматора, второй информа10ционный вход .первой суммирующей ячейки -с вторым входом управления конвейерного сумматора, а четвертые информационные входы первой и второй суммирущих ячеек - с шиной нуле15вого потенциала конвейерного сумматора, тактовые входы всех суммирующих ячеек и элементов задержки подключены к тактовому входу конвейерного сумматора

2. Сумматор по п„ 1, л и чающийся тем, что суммирующая ячейка содержит два одноразрядных сумматора, два элемента И, элемент 25 НЕРАВНОЗНАЧНОСТЬ и четыре D-триггера, причем первый - третий входы первого одноразрядного сумматора соединены соответственно с одноименными входами суммирующей ячейки, выход суммы

30 первого одноразрядного сумматора подключен к первому входу второго одноразрядного сумматора, второй вход которого соединен с четвертым входом суммирующей ячейки, а третий вход 5 с выходом первого элемента И, входы которого подключены соответственно к пятому входу и входу управления суммирующей ячейки, выход переноса первого, одноразрядного сумматора соединен с первыми входами второго эле0мента И и элемента НЕРАВНОЗНАЧНОСТЬ, вторые входы которых подключены к выходу переноса второго одноразрядного сумматора, выход суммы которого соединен с D-входом первого D-триг5гера, выход которого соединен с выходом суммы суммирукхцей ячейки, выход второго элемента И - с D-входом второго D-Vpиггepa, выход элемента НЕРАВНОЗНАЧНОСТЬ - с D-входом третье0го D-триггера, выход которого подключен к первому выходу переноса суммирующей ячейки, выход второго D-триггера соединен с D-входом четвертого D-триггера, выход которогсз является

5 вторым выходом переноса суммирующей ячейки, тактовые входы всех D-триггеров соединены с тактовым входом суммирующей ячейки.

3

г;

M

рПГ77

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерный сумматор | 1987 |

|

SU1427359A1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

| КОНВЕЙЕРНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНЫМ МОДУЛЯМ | 2024 |

|

RU2823911C1 |

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2829093C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

Изобретение относится к вычисли*- тельной технике и может быть использовано в высокопроизводительных уст-*- ройствах обработки информации и в устройствах цифровой обработки сигналов. Цель изобретения - повьшение производительности конвейерного сум-матера. Для этого первый и второй вход каждой i-й суммирующей ячейки соединен через i-1 элементов задержки с соответствующими разрядами первого и третьего информационных входов устройства» Первый выход переноса каждой i-й суммирующей ячейки соединен.с вторым входом (?+1)-и'ячейки, а второй выход переноса - с четвертым входом

| Конвейерный накапливающий сумматор | 1984 |

|

SU1190380A1 |

Авторы

Даты

1992-02-23—Публикация

1989-11-20—Подача