сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Устройство для измерения девиации частоты линейно частотно-модулированного колебания | 1983 |

|

SU1190281A1 |

| Устройство задержки последовательности импульсов с цифровым управлением | 1985 |

|

SU1285576A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2276457C2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| Устройство для перемещения магнитной ленты | 1990 |

|

SU1705865A1 |

| Ретранслятор сообщений | 1990 |

|

SU1734227A1 |

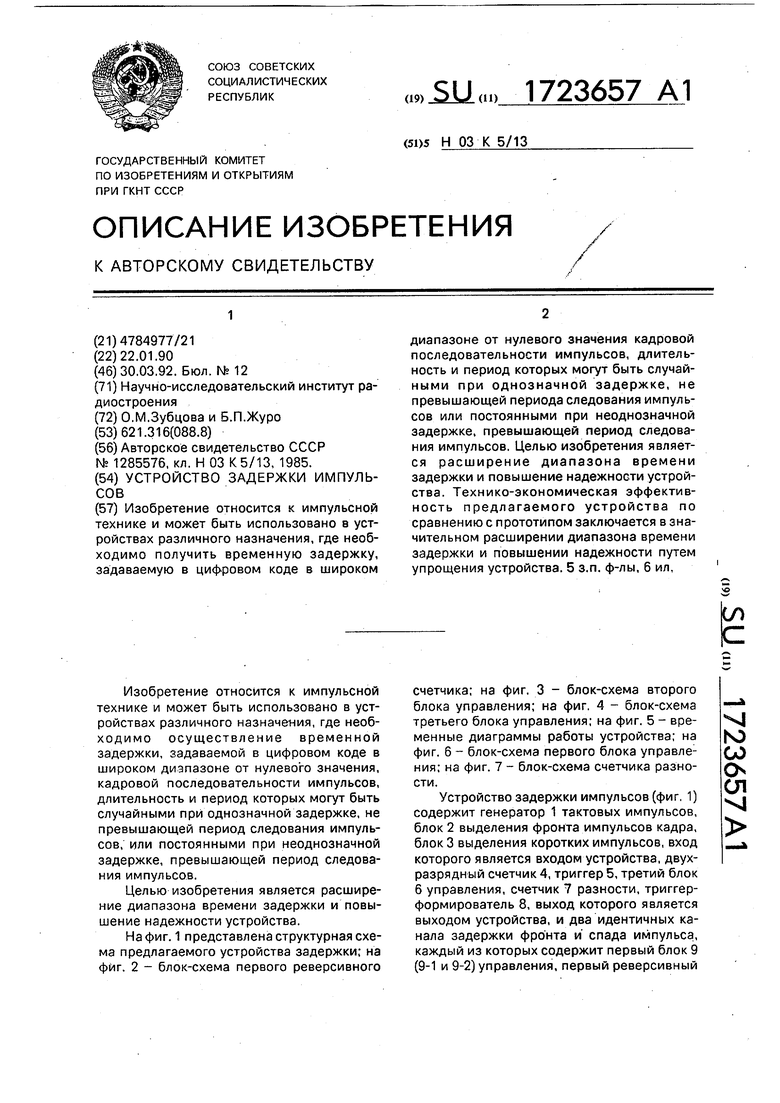

Изобретение относится к импульсной технике и может быть использовано в устройствах различного назначения, где необходимо получить временную задержку, задаваемую в цифровом коде в широком диапазоне от нулевого значения кадровой последовательности импульсов, длительность и период которых могут быть случайными при однозначной задержке, не превышающей периода следования импульсов или постоянными при неоднозначной задержке, превышающей период следования импульсов. Целью изобретения является расширение диапазона времени задержки и повышение надежности устройства. Технико-экономическая эффективность предлагаемого устройства по сравнению с прототипом заключается в значительном расширении диапазона времени задержки и повышении надежности путем упрощения устройства. 5 з.п. ф-лы, 6 ил,

Изобретение относится к импульсной технике и может быть использовано в устройствах различного назначения, где необходимо осуществление временной задержки, задаваемой в цифровом коде в широком диапазоне от нулевого значения, кадровой последовательности импульсов, длительность и период которых могут быть случайными при однозначной задержке, не превышающей период следования импульсов, или постоянными при неоднозначной задержке, превышающей период следования импульсов.

Целью изобретения является расширение диапазона времени задержки и повышение надежности устройства.

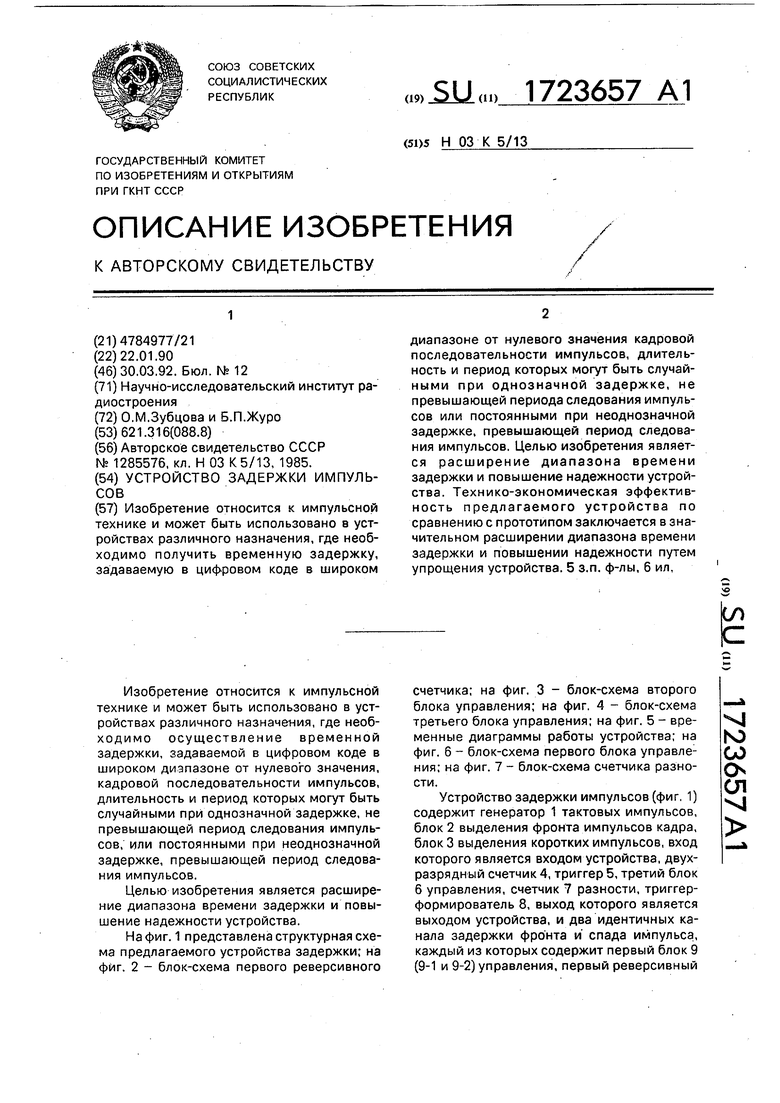

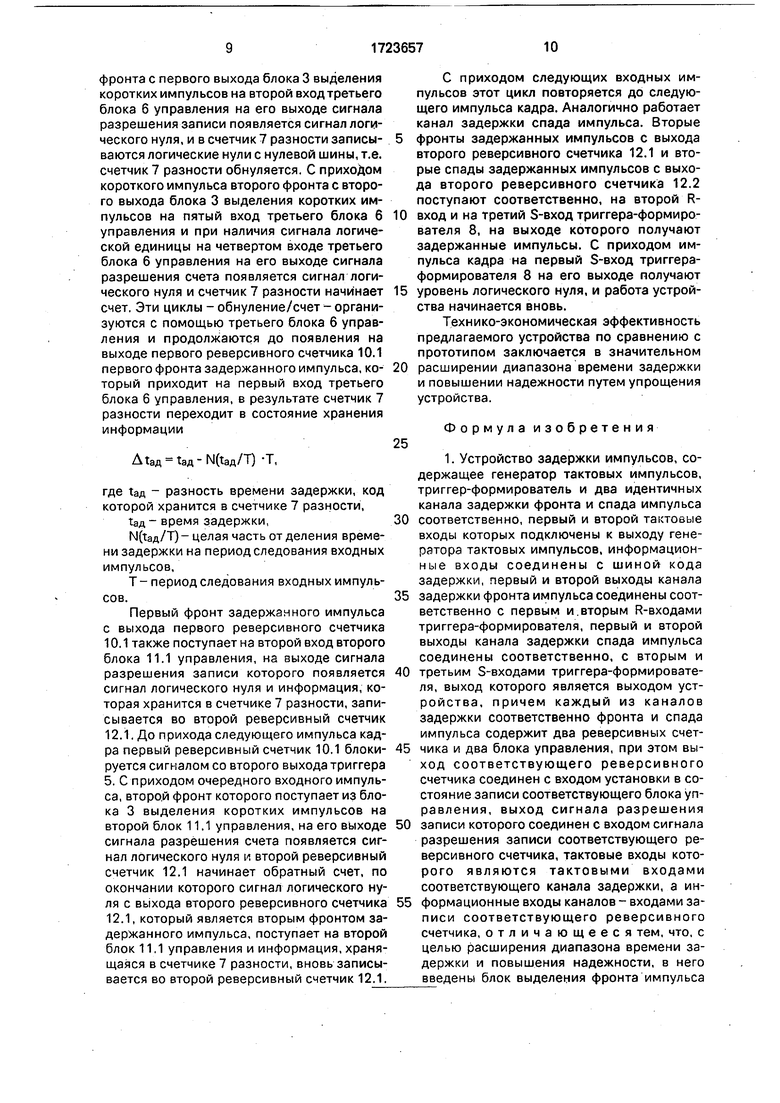

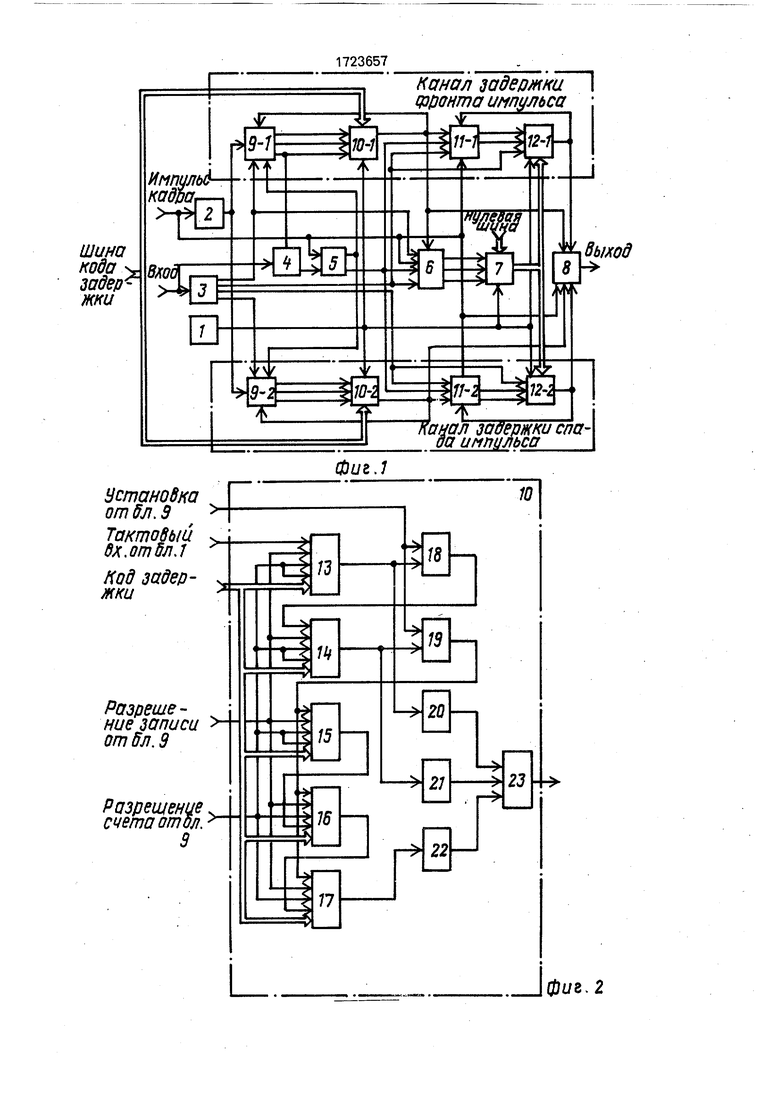

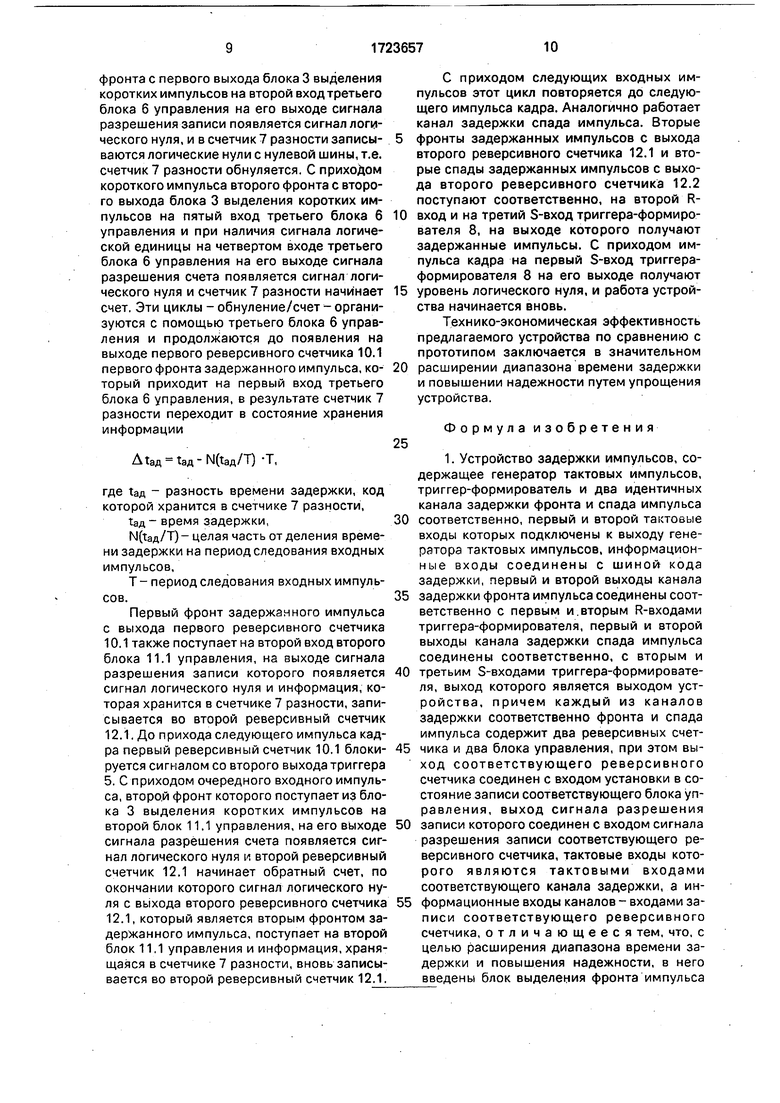

На фиг. 1 представлена структурная схема предлагаемого устройства задержки; на фиг. 2 - блок-схема первого реверсивного

счетчика; на фиг. 3 - блок-схема второго блока управления; на фиг. 4 - блок-схема третьего блока управления; на фиг. 5 - временные диаграммы работы устройства; на фиг. 6 - блок-схема первого блока управле1- ния; на фиг. 7 - блок-схема счетчика разности.

Устройство задержки импульсов (фиг. 1) содержит генератор 1 тактовых импульсов, блок 2 выделения фронта импульсов кадра, блокЗ выделения коротких импульсов, вход которого является входом устройства, двухразрядный счетчик 4, триггер 5, третий блок 6 управления, счетчик 7 разности, триггер- формирователь 8, выход которого является выходом устройства, и два идентичных канала задержки фронта и спада импульса, каждый из которых содержит первый блок 9 (9-1 и 9-2) управления, первый реверсивный

XI

ю со

CS

сл VI

счетчик 10(10-1 и 10-2), второй блок 11 (11-1 и 11-2) управления, второй реверсивный счетчик 12 (12-1 и 12-2). Первый и второй реверсивные счетчики 10 и 12 имеют одинаковую блок схему (фиг. 2).

Выход генератора 1 тактовых импульсов соединен с тактовыми входами счетчика 7 разности, первых реверсивных счетчиков

вторых блоков управления 11.1 и 11.2 с четвертым входом третьего блока 6 управления, два выхода сигналов разрешения записи и счета которого соединены с входами сигналов разрешения записи и счета счетчика 7 разности, выходы которого соединены с входами записи вторых реверсив- ных счетчиков 1.2, выходы которого соединены с первыми входами вторых бло0 ков управления 11.1 и 11.2. Выход второго реверсивного счетчика 12.1, который является вторым выходом канала задержки фронта импульса, также соединен с вторым R-входом триггера-формирователя 8. Выход

5 второго реверсивного счетчика 12.2, который является вторым выходом канала задержки спада импульса, также соединен с третьим S-входом триггера-формирователя 8, выход которого является выходом устрой0 ства задержки. Второй выход блока 3 выделения коротких импульсов соединен с четвёртым входом второго блока 11.1 управления, с входом установки второго реверсивного счетчика 12.1, с пятым входом

5 третьего блока 6 управления, выход сигнала установки которого соединен с входом установки счетчика 7 разности, входы записи которого соединены с нулевой шиной.

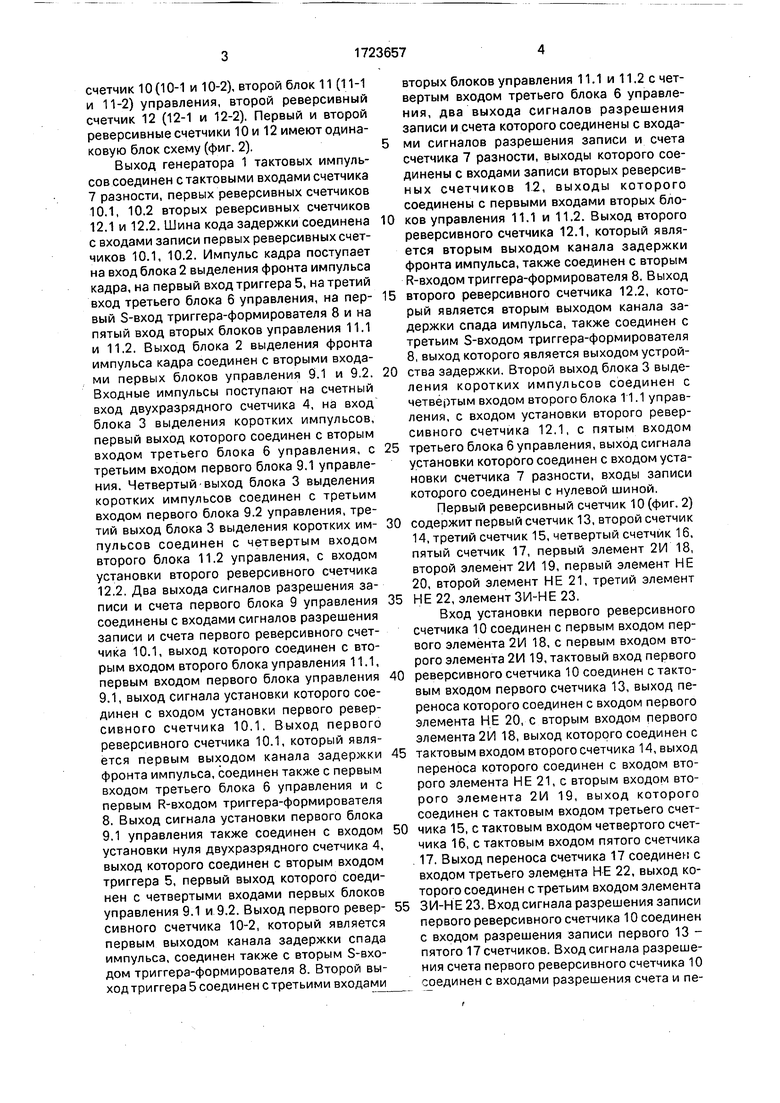

Первый реверсивный счетчик 10 (фиг. 2)

0 содержит первый счетчик 13, второй счетчик 14, третий счетчик 15, четвертый счетчик 16, пятый счетчик 17, первый элемент 2И 18, второй элемент 2И 19, первый элемент НЕ 20, второй элемент НЕ 21, третий элемент

5 НЕ 22, элемент ЗИ-НЕ 23,

Вход установки первого реверсивного счетчика 10 соединен с первым входом первого элемента 2И 18, с первым входом второго элемента 2И 19, тактовый вход первого

0 реверсивного счетчика 10 соединен с тактовым входом первого счетчика 13, выход переноса которого соединен с входом первого элемента НЕ 20, с вторым входом первого элемента 2И 18, выход которого соединен с

5 тактовым входом второго счетчика 14, выход переноса которого соединен с входом второго элемента НЕ 21, с вторым входом второго элемента 2И 19, выход которого соединен с тактовым входом третьего счет0 чика 15, с тактовым входом четвертого счетчика 16, с тактовым входом пятого счетчика . 17. Выход переноса счетчика 17 соединен с входом третьего элемента НЕ 22, выход которого соединен с третьим входом элемента

5 ЗИ-НЕ 23. Вход сигнала разрешения записи первого реверсивного счетчика 10 соединен с входом разрешения записи первого 13 - пятого 17 счетчиков. Вход сигнала разрешения счета первого реверсивного счетчика 10 соединен с входами разрешения счета и переноса первого счетчика 13, второго счетчика 14, с входом разрешения счета четвертого счетчика 16, с входом, разрешения счета пятого счетчика 17, с входами разрешения счета и переноса третьего счетчика 15. Выход переноса счетчика 15 соединен с входом разрешения переноса четвертого счетчика 16, выход переноса которого соединен с входом разрешения переноса пятого счетчика 17. Шина кода задержки первого реверсивного счетчика 10 соединена с входами записи счетчиков 13-17, выход первого элемента НЕ 20 соединен с первым входом элемента ЗИ-НЕ 23, выход второго элемента НЕ 21 соединен с вторым входом элемента ЗИ-НЕ 23, выход которого является выходом первого реверсивного счетчика 10.

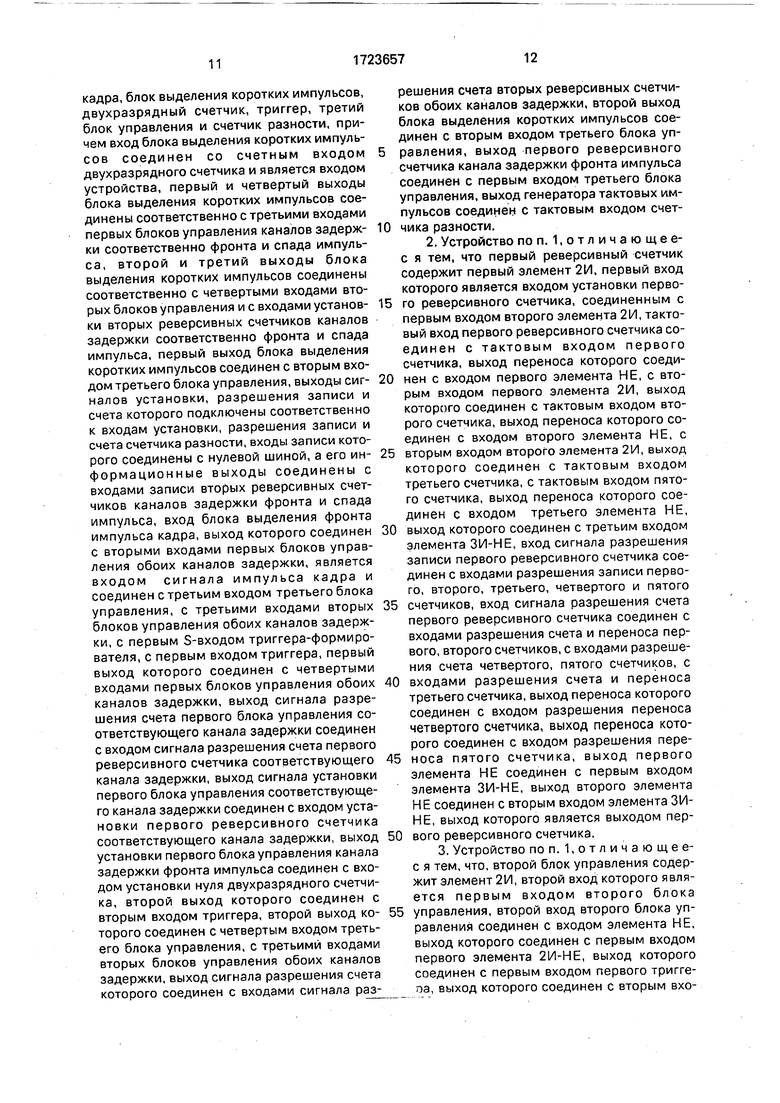

Второй блок 11 управления (фиг. 3) содержит элемент НЕ 24, первый элемент 2И- НЕ 25, первый триггер 26, второй элемент 2И-НЕ 27, элемент 2И 28, второй триггер 29, третий элемент 2И-НЕ 30, четвертый элемент 2И-НЕ 31.

Первый вход второго блока 11 управления соединен с вторым входом элемента 2И

28,второй вход второго блока 11 управления соединен с входом элемента НЕ 24, выход которого соединен с первым входом первого элемента 2И-НЕ 25, выход которого соединен с первым входом первого триггера 26. Выход триггера 26 соединен с вторым входом второго элемента 2И-НЕ 27, с первым входом третьего элемента 2И-НЕ 30, с первым входом четвертого элемента 2И-НЕ 31. Третий вход второго блока 11 управления соединен с вторым входом первого элемента 2И-НЕ 25, четвертый вход второго блока 11 управления соеА лнен с первым входом второго элемента 2И-НЕ 27, выход которого соединен с первым входом второго триггера 29, первый выход которого соединен с вторым входом третьего элемента 2И-НЕ 30, выход которого является выходом сигнала разрешения записи. Пятый вход второго блока 11 управления соединен с вторым входом первого триггера 26, с первым входом элемента 2И 28, выход которого соединен с вторым входом второго триггера

29,второй выход которого соединён с вторым входом четвертого элемента 2И-НЕ 31, выход которого является выходом сигнала разрешения счета;

Третий блок 6 управления (фиг, 4) содержит первый триггер 32, первый элемент 2И- Н Е 33, элемент ЗИ-Н Е 34, второй триггер 35, второй элемент 2И-НЕ 36.

Первый вход третьего блока 6 управления соединен с первым входом первого триггера 32, второй вход третьего блока 6

управления соединен с первым входом первого элемента 2И-НЕ 33, третий вход третьего блока 6 управления соединен с вторым входом первого триггера 32. Выход триггера

32 соединен с первым входом элемента ЗИ-Н Е 34, с вторым входом первого элемента 2И-НЕ 36, с вторым входом первого элемента 2И-НЕ 33, выход которого соединен с первым входом второго триггера 35 и явля0 ется выходом сигнала установки. Четвертый вход третьего блока 6 управления соединен с вторым входом элемента ЗИ-НЕ 34, пятый вход третьего блока 6 управления соединен с третьим входом элемента ЗИ-НЕ 34, выход

5 которого соединен с вторым входом второго триггера 35, выход которого является выходом сигнала разрешения записи и соединен с первым входом второго элемента 2И-НЕ 36, выход которого является выходом сигна0 ла разрешения счета.

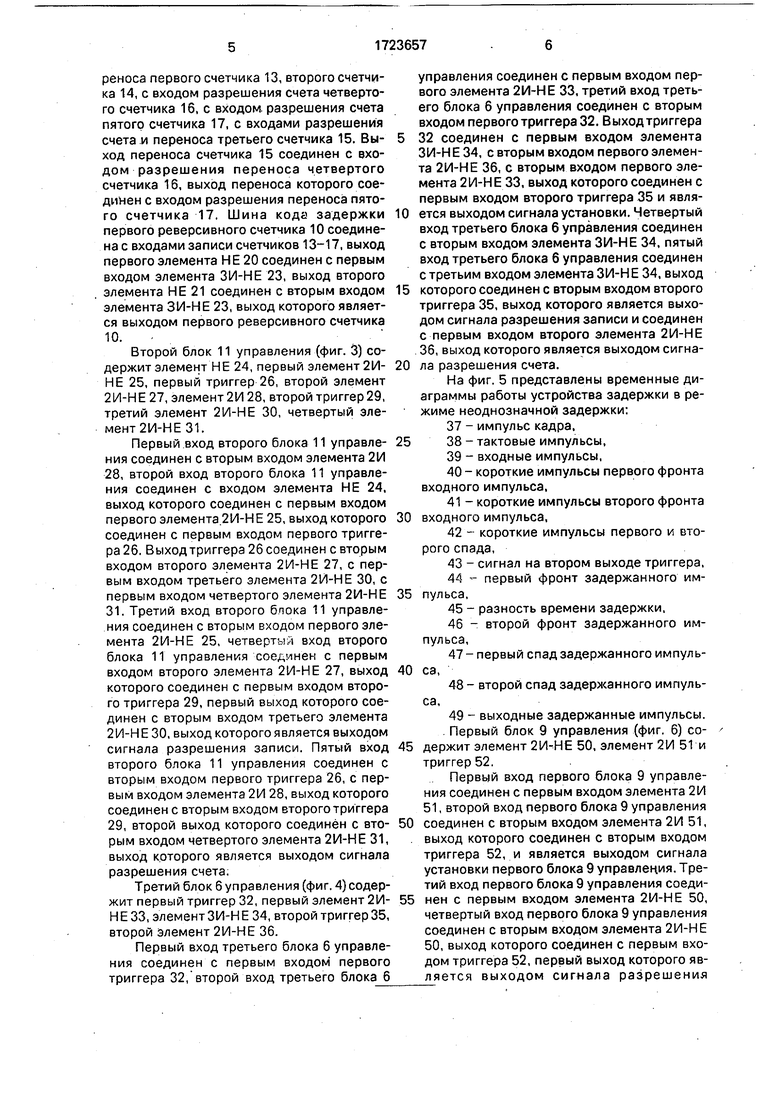

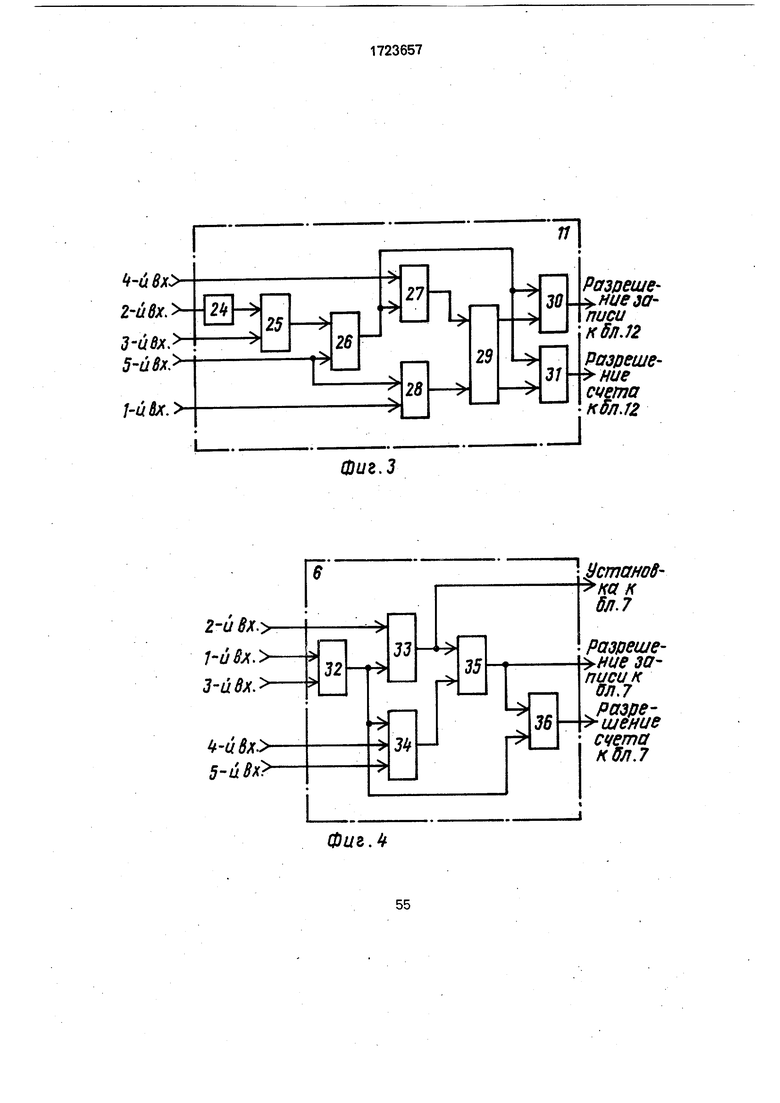

На фиг. 5 представлены временные диаграммы работы устройства задержки в режиме неоднозначной задержки: 37 - импульс кадра.

5 38-тактовые импульсы,

39- входные импульсы,

40- короткие импульсы первого фронта входного импульса,

41- короткие импульсы второго фронта 0 входного импульса,

42- короткие импульсы первого и второго спада,

43- сигнал на втором выходе триггера,

44- первый фронт задержанного им- 5 пульса,

45- разность времени задержки,

46- второй фронт задержанного импульса,

47- первый спад задержанного импуль- 0 са,

48- второй спад задержанного импульса,

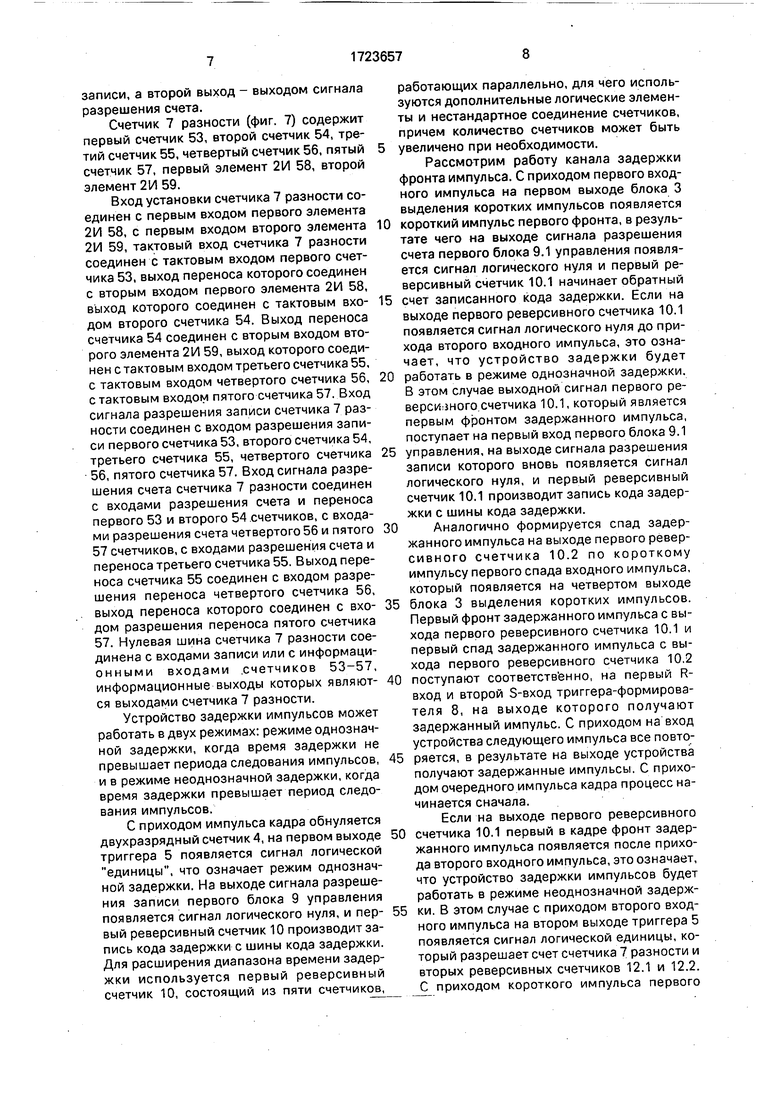

49- выходные задержанные импульсы. Первый блок 9 управления (фиг. 6) со5 держит элемент 2И-НЕ 50, элемент 2И 51 и триггер 52,

Первый вход первого блока 9 управления соединен с первым входом элемента 2И 51, второй вход первого блока 9 управления

0 соединен с вторым входом элемента 2И 51, . выход которого соединен с вторым входом триггера 52, и является выходом сигнала установки первого блока 9 управления. Третий вход первого блока 9 управления соеди5 нен с первым входом элемента 2И-НЕ 50, четвертый вход первого блока 9 управления соединен с вторым входом элемента 2И-НЕ 50, выход которого соединен с первым входом триггера 52, первый выход которого является выходом сигнала разрешения

записи, а второй выход - выходом сигнала разрешения счета.

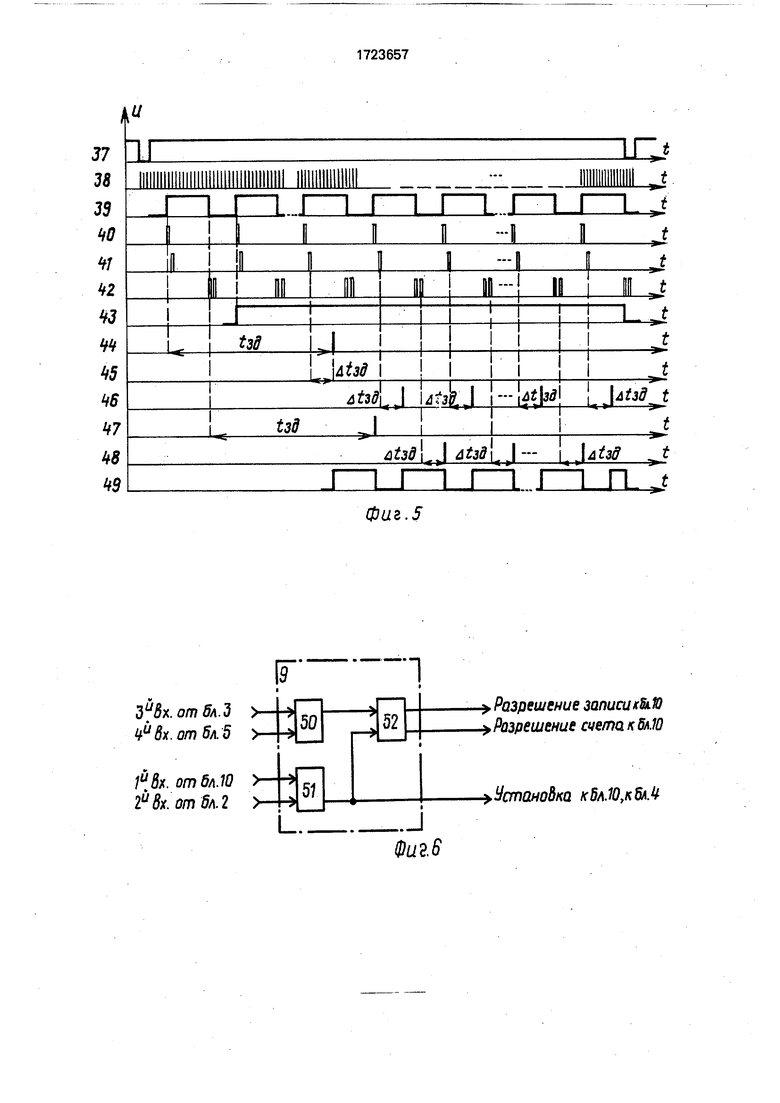

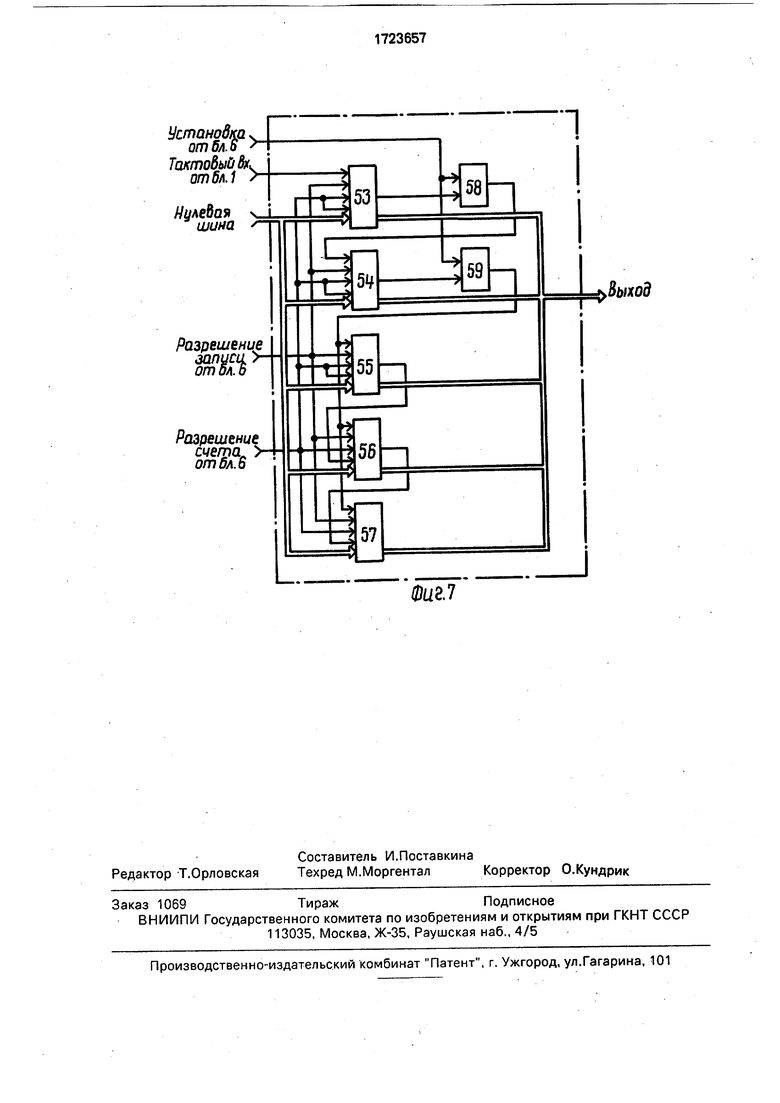

Счетчик 7 разности (фиг. 7) содержит первый счетчик 53, второй счетчик 54, третий счетчик 55, четвертый счетчик 56, пятый счетчик 57, первый элемент 2И 58, второй элемент 2И 59.

Вход установки счетчика 7 разности соединен с первым входом первого элемента 2И 58, с первым входом второго элемента 2И 59, тактовый вход счетчика 7 разности соединен с тактовым входом первого счетчика 53, выход переноса которого соединен с вторым входом первого элемента 2И 58, выход которого соединен с тактовым входом второго счетчика 54. Выход переноса счетчика 54 соединен с вторым входом второго элемента 2И 59, выход которого соединен с тактовым входом третьего счетчика 55, с тактовым входом четвертого счетчика 56, с тактовым входом пятого счетчика 57. Вход сигнала разрешения записи счетчика 7 разности соединен с входом разрешения записи первого счетчика 53, второго счетчика 54, третьего счетчика 55, четвертого счетчика

56,пятого счетчика 57. Вход сигнала разрешения счета счетчика 7 разности соединен с входами разрешения счета и переноса первого 53 и второго 54 .счетчиков, с входами разрешения счета четвертого 56 и пятого 57 счетчиков, с входами разрешения счета и переноса третьего счетчика 55. Выход переноса счетчика 55 соединен с входом разрешения переноса четвертого счетчика 56, выход переноса которого соединен с входом разрешения переноса пятого счетчика

57,Нулевая шина счетчика 7 разности соединена с входами записи или с информаци- онными входами .счетчиков 53-57, информационные выходы которых являются выходами счетчика 7 разности.

Устройство задержки импульсов может работать в двух режимах: режиме однозначной задержки, когда время задержки не превышает периода следования импульсов, и в режиме неоднозначной задержки, когда время задержки превышает период следования импульсов.

С приходом импульса кадра обнуляется двухразрядный счетчик 4, на первом выходе триггера 5 появляется сигнал логической единицы, что означает режим однозначной задержки. На выходе сигнала разрешения записи первого блока 9 управления появляется сигнал логического нуля, и первый реверсивный счетчик 10 производит запись кода задержки с шины кода задержки. Для расширения диапазона времени задержки используется первый реверсивный счетчик 10, состоящий из пяти счетчиков,

работающих параллельно, для чего используются дополнительные логические элементы и нестандартное соединение счетчиков, причем количество счетчиков может быть

увеличено при необходимости.

Рассмотрим работу канала задержки фронта импульса. С приходом первого входного импульса на первом выходе блока 3 выделения коротких импульсов появляется

0 короткий импульс первого фронта, в результате чего на выходе сигнала разрешения счета первого блока 9.1 управления появляется сигнал логического нуля и первый реверсивный счетчик 10.1 начинает обратный

5 счет записанного кода задержки. Если на выходе первого реверсивного счетчика 10.1 появляется сигнал логического нуля до прихода второго входного импульса, это означает, что устройство задержки будет

0 работать в режиме однозначной задержки. В этом случае выходной сигнал первого ре- верси;зного.счетчика 10.1, который является первым фронтом задержанного импульса, поступает на первый вход первого блока 9.1

5 управления, на выходе сигнала разрешения записи которого вновь появляется сигнал логического нуля, и первый реверсивный счетчик 10.1 производит запись кода задержки с шины кода задержки.

0 Аналогично формируется спад задержанного импульса на выходе первого реверсивного счетчика 10.2 по короткому импульсу первого спада входного импульса, который появляется на четвертом выходе

5 блока 3 выделения коротких импульсов. Первый фронт задержанного импульса с выхода первого реверсивного счетчика 10.1 и первый спад задержанного импульса с выхода первого реверсивного счетчика 10.2

0 поступают соответственно, на первый R- вход и второй S-вход триггера-формирователя 8, на выходе которого получают задержанный импульс. С приходом на вход устройства следующего импульса все повто5 ряется, в результате на выходе устройства получают задержанные импульсы. С приходом очередного импульса кадра процесс начинается сначала.

Если на выходе первого реверсивного

0 счетчика 10.1 первый в кадре фронт задержанного импульса появляется после прихода второго входного импульса, это означает, что устройство задержки импульсов будет работать в режиме неоднозначной задерж5 ки. В этом случае с приходом второго входного импульса на втором выходе триггера 5 появляется сигнал логической единицы, который разрешает счет счетчика 7 разности и вторых реверсивных счетчиков 12.1 и 12.2. С приходом короткого импульса первого

фронта с первого выхода блока 3 выделения коротких импульсов на второй вход третьего блока 6 управления на его выходе сигнала разрешения записи появляется сигнал логического нуля, и в счетчик 7 разности записываются логические нули с нулевой шины, т.е. счетчик 7 разности обнуляется. С приходом короткого импульса второго фронта с второго выхода блока 3 выделения коротких импульсов на пятый вход третьего блока б управления и при наличия сигнала логической единицы на четвертом входе третьего блока 6 управления на его выходе сигнала разрешения счета появляется сигнал логического нуля и счетчик 7 разности начинает счет. Эти циклы - обнуление/счет - организуются с помощью третьего блока 6 управления и продолжаются до появления на выходе первого реверсивного счетчика 10.1 первого фронта задержанного импульса, который приходит на первый вход третьего блока 6 управления, в результате счетчик 7 разности переходит в состояние хранения информации

AtaA taA-N(taA/T) -Т,

где тад - разность времени задержки, код которой хранится в счетчике 7 разности,

1ад- время задержки,

N(taA/T)- целая часть отделения времени задержки на период следования входных импульсов,

Т - период следования входных импульсов.

Первый фронт задержанного импульса с выхода первого реверсивного счетчика 10.1 также поступает на второй вход второго блока 11.1 управления, на выходе сигнала разрешения записи которого появляется сигнал логического нуля и информация, которая хранится в счетчике 7 разности, записывается во второй реверсивный счетчик 12.1. До прихода следующего импульса кадра первый реверсивный счетчик 10.1 блокируется сигналом со второго выхода триггера 5. С приходом очередного входного импульса, второй фронт которого поступает из блока 3 выделения коротких импульсов на второй блок 11.1 управления, на его выходе сигнала разрешения счета появляется сигнал логического нуля и второй реверсивный счетчик 12.1 начинает обратный счет, по окончании которого сигнал логического нуля с выхода второго реверсивного счетчика 12.1, который является вторым фронтом задержанного импульса, поступает на второй блок 11,1 управления и информация, хранящаяся в счетчике 7 разности, вновь записывается во второй реверсивный счетчик 12.1.

С приходом следующих входных импульсов этот цикл повторяется до следующего импульса кадра. Аналогично работает канал задержки спада импульса. Вторые

фронты задержанных импульсов с выхода второго реверсивного счетчика 12.1 и вторые спады задержанных импульсов с выхода второго реверсивного счетчика 12.2 поступают соответственно, на второй Rвход и на третий S-вход триггера-формирователя 8, на выходе которого получают задержанные импульсы. С приходом импульса кадра на первый S-вход триггера- формирователя В на его выходе получают

уровень логического нуля, и работа устройства начинается вновь.

Технико-экономическая эффективность предлагаемого устройства по сравнению с прототипом заключается в значительном

расширении диапазона времени задержки и повышении надежности путем упрощения устройства.

25

Формула изобретения

0 соответственно, первый и второй тактовые входы которых подключены к выходу генератора тактовых импульсов, информационные входы соединены с шиной кода задержки, первый и второй выходы канала

5 задержки фронта импульса соединены соответственно с первым и.вторым R-входами триггера-формирователя, первый и второй выходы канала задержки спада импульса соединены соответственно, с вторым и

0 третьим S-входами триггера-формирователя, выход которого является выходом устройства, причем каждый из каналов задержки соответственно фронта и спада импульса содержит два реверсивных счет5 чика и два блока управления, при этом выход соответствующего реверсивного счетчика соединен с входом установки в состояние записи соответствующего блока управления, выход сигнала разрешения

0 записи которого соединен с входом сигнала разрешения записи соответствующего реверсивного счетчика, тактовые входы которого являются тактовыми входами соответствующего канала задержки, а ин5 формационные входы каналов - входами за- писи соответствующего реверсивного счетчика, отличающееся тем, что, с целью расширения диапазона времени задержки и повышения надежности, в него введены блок выделения фронта импульса

кадра, блок выделения коротких импульсов, двухразрядный счетчик, триггер, третий блок управления и счетчик разности, причем вход блока выделения коротких импульсов соединен со счетным входом двухразрядного счетчика и является входом устройства, первый и четвертый выходы блока выделения коротких импульсов соединены соответственно с третьими входами первых блоков управления каналов задержки соответственно фронта и спада импульса, второй и третий выходы блока выделения коротких импульсов соединены соответственно с четвертыми входами вторых блоков управления и с входами установки вторых реверсивных счетчиков каналов задержки соответственно фронта и спада импульса, первый выход блока выделения коротких импульсов соединен с вторым входом третьего блока управления, выходы сиг- налов установки, разрешения записи и счета которого подключены соответственно к входам установки, разрешения записи и счета счетчика разности, входы записи которого соединены с нулевой шиной, а его ин- формационные выходы соединены с входами записи вторых реверсивных счетчиков каналов задержки фронта и спада импульса, вход блока выделения фронта импульса кадра, выход которого соединен с вторыми входами первых блоков управления обоих каналов задержки, является входом сигнала импульса кадра и соединен с третьим входом третьего блока управления, с третьими входами вторых блоков управления обоих каналов задержки, с первым S-входом триггера-формирователя, с первым входом триггера, первый выход которого соединен с четвертыми входами первых блоков управления обоих каналов задержки, выход сигнала разрешения счета первого блока управления соответствующего канала задержки соединен с входом сигнала разрешения счета первого реверсивного счетчика соответствующего канала задержки, выход сигнала установки первого блока управления соответствующего канала задержки соединен с входом установки первого реверсивного счетчика соответствующего канала задержки, выход установки первого блока управления канала задержки фронта импульса соединен с входом установки нуля двухразрядного счетчика, второй выход которого соединен с вторым входом триггера, второй выход которого соединен с четвертым входом третьего блока управления, с третьими входами вторых блоков управления обоих каналов задержки, выход сигнала разрешения счета которого соединен с входами сигнала разрешения счета вторых реверсивных счетчиков обоих каналов задержки, второй выход блока выделения коротких импульсов соединен с вторым входом третьего блока управления, выход первого реверсивного счетчика канала задержки фронта импульса соединен с первым входом третьего блока управления, выход генератора тактовых импульсов соединен с тактовым входом счет0 чика разности.

5 вторым входом второго элемента 2И, выход которого соединен с тактовым входом третьего счетчика, с тактовым входом пятого счетчика, выход переноса которого соединен с входом третьего элемента НЕ,

0 выход которого соединен с третьим входом элемента ЗИ-НЕ, вход сигнала разрешения записи первого реверсивного счетчика соединен с входами разрешения записи первого, второго, третьего, четвертого и пятого

5 счетчиков, вход сигнала разрешения счета первого реверсивного счетчика соединен с входами разрешения счета и переноса первого, второго счетчиков, с входами разрешения счета четвертого, пятого счетчиков, с

0 входами разрешения счета и переноса третьего счетчика, выход переноса которого соединен с входом разрешения переноса четвертого счетчика, выход переноса которого соединен с входом разрешения пере5 носа пятого счетчика, выход первого элемента НЕ соединен с первым входом элемента ЗИ-НЕ, выход второго элемента НЕ соединен с вторым входом элемента ЗИНЕ, выход которого является выходом пер0 вого реверсивного счетчика,

3,Устройство по п. 1,отличающее- с я тем, что, второй блок управления содержит элемент 2И, второй вход которого является первым входом второго блока

5 управления, второй вход второго блока управления соединен с входом элемента НЕ, выход которого соединен с первым входом первого элемента 2И-НЕ, выход которого соединен с первым входом первого тригге- оа, выход которого соединен с вторым входом второго элемента 2И-НЕ, с первым входом третьего элемента 2Й-НЕ, с первым входом четвертого элемента 2И-НЕ, третий вход второго блока управления соединен с вторым входом первого элемента 2И-НЕ, четвертый вход второго блока управления соединен с первым входом второго элемента 2И-НЕ, выход которого соединен с первым входом второго триггера, первый выход которого соединен с вторым входом третьего элемента 2И-НЕ, выход которого является выходом сигнала разрешения записи, пятый вход второго блока управления соединен с вторым входом первого триггера, с первым входом элемента 2И, выход которого соединен с вторым входом второго триггера, второй выход которого соединен с вторым входом четвертого элемента 2И-НЕ, выход которого является выходом сигнала разрешения счета.

блока управления соединен с первым входом элемента 2И-НЕ, четвертый вход первого блока управления соединен с вторым входом элемента 2И-НЕ, выход которого соединен с первым входом триггера, первый выход которого является выходом сигнала разрешения записи, а второй выход которого является выходом сигнала разрешения счета.

соединен с вторым входом второго элемента 2И, соединенного выходом с тактовым входом третьего счетчика, с тактовым входом четвертого счетчика, с тактовым входом пятого счетчика, вход сигнала разрешения

записи счетчика разности соединен с входом разрешения записи первого, второго, -ретьего, четвертого и пятого счетчиков, вход сигнала разрешения счета счетчика разности соединен с входами разрешения

счета и переноса первого счетчика, второго счетчика, с входом разрешения счета четвертого счетчика, с входом разрешения счета пятого счетчика, с входами разрешения счета и переноса третьего счетчика, выход

переноса которого соединен с входом разрешения переноса четвертого счетчика, выход переноса которого соединен с входом разрешения переноса пятого счетчика, нулевая шина счетчика разности является входами записи первого, второго, третьего, четвертого и пятого счетчиков, информационные выходы которых являются выходами счетчика разности.

Установка от бл. 9

Тактовый вх.отблл

Код задер- ти

Разрешение записи от . 9

Разрешение счета от ол.

9

Ю

Ј

3 ЈМ Я tjfci

ins IIP

«SAG

s

К o

CO

M rfc

П

Ю Ю

CO

5J

S

J

F

.omfii.3 -U 4й 8х. от 6л. 5 -Ц

50

/Й0х. отб/.0 гй8 :отбл.2

51

L.

фиг.5

П

52

- Разрешение записик&Ю - Разрешение счета к Вл.Ю

- Устанодка кбл.Ю,к6л.Ц

„J

Фиг-ff

Выход

Фиг. 7

| Устройство задержки последовательности импульсов с цифровым управлением | 1985 |

|

SU1285576A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-03-30—Публикация

1990-01-22—Подача