J

Ј

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1985 |

|

SU1322300A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Транслятор языков программирования | 1981 |

|

SU1387018A1 |

| Устройство для цифровой записи и считывания речевых сигналов | 1985 |

|

SU1302291A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

Сущность изобретения: ретранслятор сообщений содержит К блоков 1 трансляции, формирователь 2 сигналов приоритета и сумматор 3. Каждый блок 1 трансляции содержит согласующий блок 4, коммутатор 5, детектор 6 информации, блок 7 сравнения сигналов приоритета и блок 8 памяти. 3 з.п. ф-лы, 1 табл., 3 ил.

vi

OJ

fe

ю

4

Изобретение относится к радиотехнике и связи и может быть использовано для приема и трансляции телефонных сообщений в системе диспетчерской связи без избирательного вызова абонентов при большой интенсивности коротких сообщений.

Цель изобретения - повышение пропускной способности.

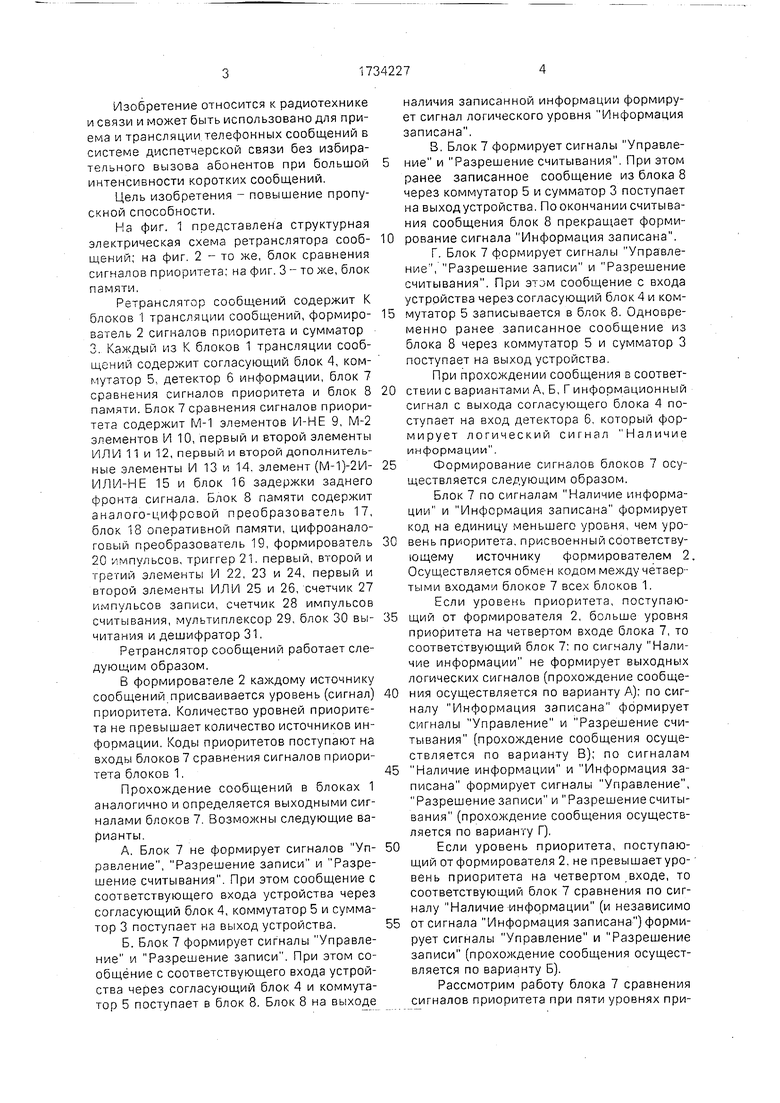

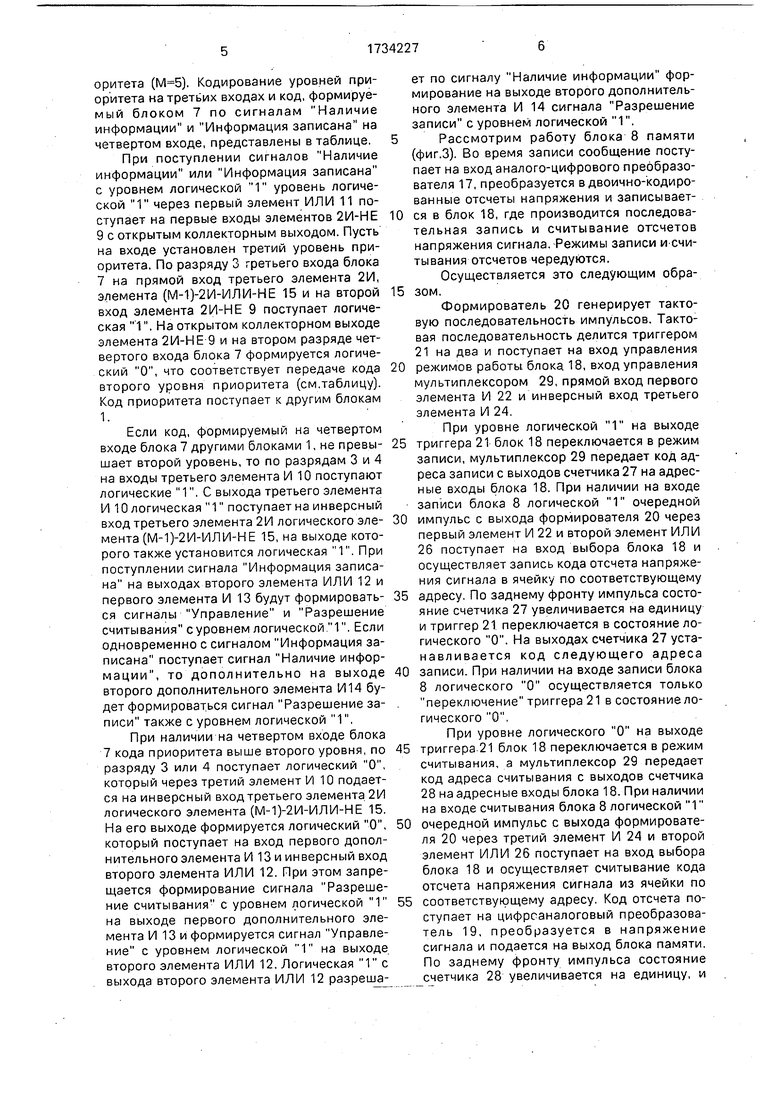

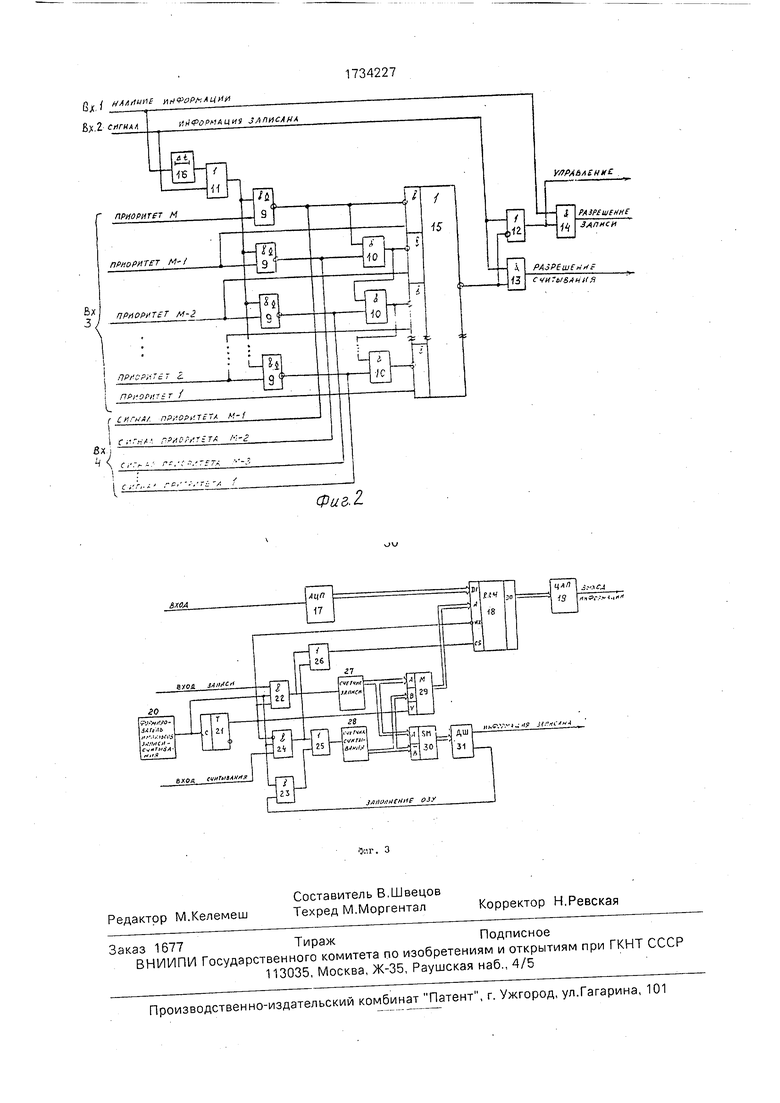

На фиг. 1 представлена структурная электрическая схема ретранслятора сообщений; на фиг. 2 - то же, блок сравнения сигналов приоритета; на фиг. 3 - то же, блок памяти.

Ретранслятор сообщений содержит К блоков 1 трансляции сообщений, формирователь 2 сигналов приоритета и сумматор 3. Каждый из К блоков 1 трансляции сообщений содержит согласующий блок 4, коммутатор 5. детектор 6 информации, блок 7 сравнения сигналов приоритета и блок 8 памяти. Блок 7 сравнения сигналов приоритета содержит М-1 элементов И-НЕ 9, М-2 элементов И 10,первый и второй элементы ИЛИ 11 и 12, первый и второй дополнительные элементы И 13 и 14. элемент (М-1)-2И- И Л И-НЕ 15 и блок 16 задержки заднего фронта сигнала. Блок 8 памяти содержит аналого-цифровой преобразователь 17, блок 18 оперативной памяти, цифроанало- говый преобразователь 19, формирователь 20 импульсов, триггер 21, первый, второй и третий элементы И 22, 23 и 24, первый и второй элементы ИЛИ 25 и 26, счетчик 27 импульсов записи, счетчик 28 импульсов считывания, мультиплексор 29. блок 30 вычитания и дешифратор 31.

Ретранслятор сообщений работает следующим образом,

В формирователе 2 каждому источнику сообщений присваивается уровень (сигнал) приоритета. Количество уровней приоритета не превышает количество источников информации. Коды приоритетов поступают на входы блоков 7 сравнения сигналов приоритета блоков 1.

Прохождение сообщений в блоках 1 аналогично и определяется выходными сигналами блоков 7. Возможны следующие варианты.

А. Блок 7 не формирует сигналов Управление, Разрешение записи и Разрешение считывания. При этом сообщение с соответствующего входа устройства через согласующий блок 4, коммутатор 5 и сумматор 3 поступает на выход устройства.

Б. Блок 7 формирует сигналы Управление и Разрешение записи. При этом сообщение с соответствующего входа устройства через согласующий блок 4 и коммутатор 5 поступает в блок 8. Блок 8 на выходе

наличия записанной информации формирует сигнал логического уровня Информация записана.

В. Блок 7 формирует сигналы Управление и Разрешение считывания. При этом ранее записанное сообщение из блока 8 через коммутатор 5 и сумматор 3 поступает на выход устройства. По окончании считывания сообщения блок 8 прекращает форми0 рование сигнала Информация записана.

Г. Блок 7 формирует сигналы Управление, Разрешение записи и Разрешение считывания. При зим сообщение с входа устройства через согласующий блок 4 и ком5 мутатор 5 записывается в блок 8. Одновременно ранее записанное сообщение из блока 8 через коммутатор 5 и сумматор 3 поступает на выход устройства.

При прохождении сообщения в соответ0 ствии с вариантами А, Б, Г информационный сигнал с выхода согласующего блока 4 поступает на вход детектора 6, который формирует логический сигнал Наличие информации.

5Формирование сигналов блоков 7 осуществляется следующим образом.

Блок 7 по сигналам Наличие информации и Информация записана формирует код на единицу меньшего уровня, чем уроС вень приоритета, присвоенный соответствующему источнику формирователем 2. Осуществляется обмен кодом между четвертыми входами блокое 7 всех блоков 1.

Если уровень приоритета, поступаю5 щий от формирователя 2, больше уровня приоритета на четвертом входе блока 7, то соответствующий блок 7: по сигналу Наличие информации не формирует выходных логических сигналов (прохождение сообще0 ния осуществляется по варианту А); по сигналу Информация записана формирует сигналы Управление и Разрешение считывания (прохождение сообщения осуществляется по варианту В); по сигналам

5 Наличие информации и Информация записана формирует сигналы Управление, Разрешение записи и Разрешение считывания (прохождение сообщения осуществляется по варианту Г).

0Если уровень приоритета, поступающий от формирователя 2. не превышает уровень приоритета на четвертом входе, то соответствующий блок 7 сравнения по сигналу Наличие информации (и независимо

5 от сигнала Информация записана) формирует сигналы Управление и Разрешение записи (прохождение сообщения осуществляется по варианту Б).

Рассмотрим работу блока 7 сравнения сигналов приоритета при пяти уровнях приоритета (). Кодирование уровней приоритета на третьих входах и код, формируе- мый блоком 7 по сигналам Наличие информации и Информация записана на четвертом входе, представлены в таблице.

При поступлении сигналов Наличие информации или Информация записана с уровнем логической 1 уровень логической 1 через первый элемент ИЛИ 11 поступает на первые входы элементов 2И-НЕ 9 с открытым коллекторным выходом. Пусть на входе установлен третий уровень приоритета. По разряду 3 третьего входа блока 7 на прямой вход третьего элемента 2И, элемента (М-1)-2И-ИЛИ-НЕ 15 и на второй вход элемента 2И-НЕ 9 поступает логическая 1. На открытом коллекторном выходе элемента 2И-НЕ 9 и на втором разряде четвертого входа блока 7 формируется логический О, что соответствует передаче кода второго уровня приоритета (см.таблицу). Код приоритета поступает к другим блокам 1.

Если код, формируемый на четвертом входе блока 7 другими блоками 1, не превышает второй уровень, то по разрядам 3 и 4 на входы третьего элемента И 10 поступают логические 1. С выхода третьего элемента И 10 логическая 1 поступает на инверсный вход третьего элемента 2И логического элемента (М-1)-2И-ИЛИ-НЕ 15, на выходе которого также установится логическая 1. При поступлении сигнала Информация записана на выходах второго элемента ИЛИ 12 и первого элемента И 13 будут формироваться сигналы Управление и Разрешение считывания с уровнем логической 1. Если одновременно с сигналом Информация записана поступает сигнал Наличие информации, то дополнительно на выходе второго дополнительного элемента И14 будет формироваться сигнал Разрешение записи также с уровнем логической 1,

При наличии на четвертом входе блока 7 кода приоритета выше второго уровня, по разряду 3 или 4 поступает логический О, который через третий элемент И 10 подается на инверсный вход третьего элемента 2И логического элемента (М-1)-2И-ИЛИ-НЕ 15. На его выходе формируется логический О, который поступает на вход первого дополнительного элемента И 13 и инверсный вход второго элемента ИЛИ 12. При этом запрещается формирование сигнала Разрешение считывания с уровнем логической 1 на выходе первого дополнительного элемента И 13 и формируется сигнал Управление с уровнем логической 1 на выходе второго элемента ИЛИ 12. Логическая 1 с выхода второго элемента ИЛИ 12 разрешает по сигналу Наличие информации формирование на выходе второго дополнительного элемента И 14 сигнала Разрешение записи с уровнем логической 1.

Рассмотрим работу блока 8 памяти

(фиг.З). Во время записи сообщение поступает на вход аналого-цифрового преобразователя 17, преобразуется в двоично-кодированные отсчеты напряжения и записывает0 ся в блок 18, где производится последовательная запись и считывание отсчетов напряжения сигнала. Режимы записи и считывания отсчетов чередуются.

Осуществляется это следующим обра5 зом.

Формирователь 20 генерирует тактовую последовательность импульсов. Тактовая последовательность делится триггером 21 на два и поступает на вход управления

0 режимов работы блока 18, вход управления мультиплексором 29, прямой вход первого элемента И 22 и инверсный вход третьего элемента И 24.

При уровне логической 1 на выходе

5 триггера 21 блок 18 переключается в режим записи, мультиплексор 29 передает код адреса записи с выходов счетчика 27 на адресные входы блока 18. При наличии на входе записи блока 8 логической 1 очередной

0 импульс с выхода формирователя 20 через первый элемент И 22 и второй элемент ИЛИ 26 поступает на вход выбора блока 18 и осуществляет запись кода отсчета напряжения сигнала в ячейку по соответствующему

5 адресу. По заднему фронту импульса состояние счетчика 27 увеличивается на единицу и триггер 21 переключается в состояние логического О. На выходах счетчика 27 устанавливается код следующего адреса

0 записи. При наличии на входе записи блока 8 логического О осуществляется только переключение триггера 21 в состояниело- гического О.

При уровне логического О на выходе

5 триггера 21 блок 18 переключается в режим считывания, а мультиплексор 29 передает код адреса считывания с выходов счетчика 28 на адресные входы блока 18. При наличии на входе считывания блока 8 логической 1

0 очередной импульс с выхода формирователя 20 через третий элемент И 24 и второй элемент ИЛИ 26 поступает на вход выбора блока 18 и осуществляет считывание кода отсчета напряжения сигнала из ячейки по

5 соответствующему адресу. Код отсчета поступает на цифрганалоговый преобразователь 19, преобразуется в напряжение сигнала и подается на выход блока памяти. По заднему фронту импульса состояние счетчика 28 увеличивается на единицу, и

триггер 21 переключается в состояние логической 1. На выходах счетчика 28 устанавливается код следующего адреса считывания. При наличии на входе считывания блока 8 логического О осуществляется только переключение триггера 21 в состояние логической 1.

Блоком 30 определяется разность между кодом адреса записи и кодом адреса счи- тывания. Разность кодов подается на дешифратор 31. Если разность кодов больше нуля, дешифратор 31 формирует на выходе наличия записанной информации блока памяти сигнал Информация записана.

Коэффициент пересчета счетчиков 27 и 28 равен количеству ячеек в блоке 18. При длительном сообщении объем памяти блока 18 может оказаться недостаточным для записи всего сообщения. В этом случае будут заполнены все его ячейки, причем на место начальной части сообщения будет записано окончание сообщения. Так как считывание информации из блока 8 может быть осуществлено только при наличии сигнала Информация записана, т.е. при разности кодов счетчиков 27 и 28 больше нуля, то из блока 18 может быть считано не более N-1 отсчетов. Для поддержания во время записи разности кодов на выходах счетчиков 27 и 28, равной N-1, дешифратор 31 при разности N-1 формирует на втором выходе логическую 1. Логической 1 решается прохождение импульсов через второй элемент И 23 и первый элемент ИЛИ 25 на вход счетчика 28 считывания. Состояние счетчика 28 во время записи принудительно циклически увеличивается и состояние счетчика 27 не достигает состояния счетчика 28. При последующем считывании будут считаны N-1 последних отсчетов сообщения.

Использование детекторов информационных сигналов 6 с минимальной длительностью выключения и включение в блоки 7 сравнения сигналов приоритета блоков 16 задержки заднего фронта позволяет дополнительно увеличить пропускную способность ретранслятора. Это осуществляется за счет того, что при записи сообщений в блоки 8 исключается запись пауз между отдельными словами и фразами, т.е. производится временное сжатие сообщения. Сигналы Наличие информации и Разрешение записи формируются в такт со словами и фразами записываемого сообщения. Одновременно, чтобы сообщение от источника с более высоким приоритетом, которое транслируется согласно варианту А. не перемешивалось с сообщением от источника

низшего приоритета, прохождение которого осуществляется по варианту Б, уровень приоритета на шине не должен изменяться в такт с сигналом Наличие информации.

Это обеспечивается при прохождении сигнала Наличие информации через блок 16 На выходе блока 16 формируется непрерывный логический сигнал на время трансляции всего сообщения.

0Формула изобретения

0 Кблоковтрансляциисообщений, первыеуп- равляющие входы которых подключены к соответствующим выходам формирователя сигналов приоритета, вторые управляющие входы всех блоков трансляции сообщении

5 объединены, а в каждый блок трансляции сообщений введен детектор, детектор информационных сигналов, блок сравнения сигналов приоритета и коммутатор, первый вход которого подключен к выходу согласу0 ющего блока и входу детектора информационных сигналов, выход которого подключен к первому входу блока сравнения сигналов приоритета, второй вход коммутатора соединен с выходом блока памяти, информаци5 онный вход которого соединен с первым выходом коммутатора, управляющий вход которого подключен к первому выходу блока сравнения сигналов приоритета, второй и третий выходы которого подключены к

0 входам записи и считывания блока памяти, выход наличия записанной информации которого подключен к второму входу блока сравнения сигналов приоритета, третий и четвертый входы которого являются первым

5 и вторым управляющими входами блока трансляции сообщений, выходом которого является второй выход коммутатора.

5 элемент (М-1)-2И-ИЛИ-НЕ, причем первые входы всех М-1 элементов И-НЕ объединены и подключены к выходу первого элемента ИЛИ, первый вход которого, объединенный с первым входом второго дополнительного элемента И, является первым входом блока сравнения сигналов приоритета, вторым входом которого являются объединенные второй вход первого элемента ИЛИ и первые входы первого дополнительного элемента И и второго элемента ИЛИ, выход которого, соединенный с вторичным входом второго дополнительного элемента И, является первым выходом блока сравнения сигналов приоритета, вторым выходом которого является выход второго дополнительного элемента И, третьим выходом блока сравнения сигналов приоритета является выход первого дополнительного элемента И, второй вход которого объединен с инверсным входом второго элемента ИЛИ и подключен к выходу элемента (М-1)- 2И-ИЛИ-НЕ, первый инверсный вход которого объединен с первым входом первого элемента И и подключен к выходу первого элемента И-НЕ, выходы с второго по(М-1)-й элементов .И-НЕ подключены к вторым входам соответствующих М-2 элементов И, выходы которых соединены соответственно с второго по (М-1)-й инверсными входами элемента (М-1)-2И-ИЛИ-НЕ, первые М-2 прямых входа которого подключены к вторым входам с второго по (М-1)-й элементы И-НЕ, вторые входы всех М-1 элементов И-НЕ и (М-1)-й прямой вход элемента (М-1)-2И- ИЛИ-НЕ подключены к третьему входу блока сравнения сигналов приоритета, четвертый вход которого подключен к выходам М-1 элементов И-НЕ.

тель, а также последовательно соединенные формирователь импульсов, первый элемент И и счетчик импульсов записи, выход которого подключен к первым входам мульти5 плексора и блока вычитания, выход которого подключен к последовательно соединенным дешифратору, второму элементу И, первому элементу ИЛИ и счетчику импульсов считывания, выход которого под10 ключей к вторым входам блока вычитания и мультиплексора, выход которого подключен к адресному входу блока оперативной памяти, первый управляющий вход которого соединен с управляющим входом мультип15 лексора, вторым входом первого элемента И, инверсным входом третьего элемента И и выходом триггера, вход которого соединен с выходом формирователя импульсов, вторым входом второго элемента И и пер- 20 вым входом третьего элемента И, выход которого подключен к второму входу первого элемента ИЛИ и вместе с выходом первого элемента И через второй элемент ИЛИ подключены к второму управляющему входу бло25 ка оперативной памяти, причем входами записи и считывания блока памяти являются соответственно третий вход первого элемента И и второй вход третьего элемента И, а второй выходдешифратора является выхо30 дом наличия записанной информации блока памяти.

35 приоритете содержит блок задержки заднего фронта сигнала, включенный между первым входом блока сравнения сигналов приоритета и первым входом первого элемента ИЛИ.

40

g / AM/I/f« Ј n,(tftf

Фиг. 2.

&XOA

| Система телефонной связи с записью продиктованного текста и воспроизведением его | 1977 |

|

SU690650A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-05-15—Публикация

1990-02-14—Подача