w

&

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1985 |

|

SU1363296A1 |

| Устройство для отображения информации | 1985 |

|

SU1278928A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| Устройство перемежения данных | 1990 |

|

SU1815670A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1399809A1 |

| Устройство для ввода изображения в ЭВМ | 1988 |

|

SU1644402A1 |

| Устройство для ввода информации | 1990 |

|

SU1698890A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода в процессорные средства обработки данных многоканальной информации, накапливаемой во время проведения сложных экспериментов. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения циклического вывода соответствующих данных. Устройство содержит блок формирователей 1, одновибратор 2, первый элемент НЕ 3, первый элемент И 4, первый 5 и второй 6 переключатели, дешифратор 7, счетчик каналов 8, второй элемент И 9. блок выбора информации 10, блок управления 11, триггер 12, третий элемент И 13, блок памяти 14, элемент ИЛИ 15, второй 16 и третий 17 элементы НЕ, схему сравнения 18, регистр адреса 19, счетчик адреса.20. 2 ил.

Устройство относится к автоматике и вычислительной технике и может быть использовано для ввода в процессорные средства обработки данных многоканальной информации, накапливаемой во время проведения сложных экспериментов.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения циклического вывода соответствующих данных.

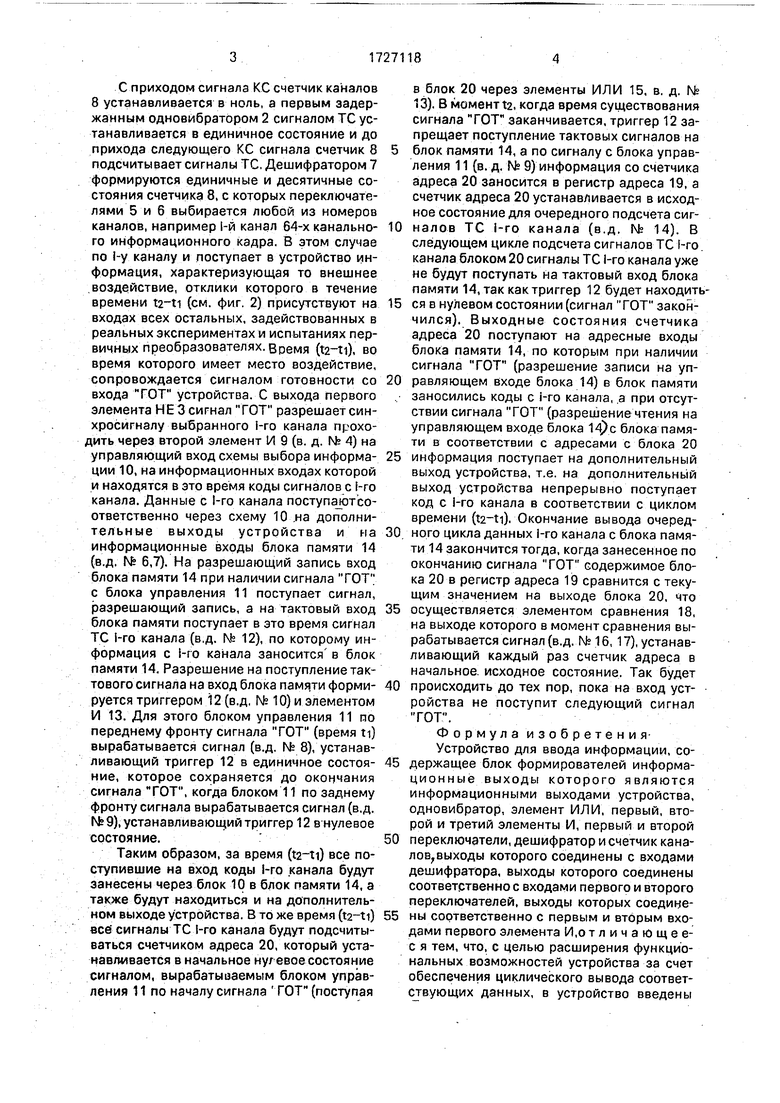

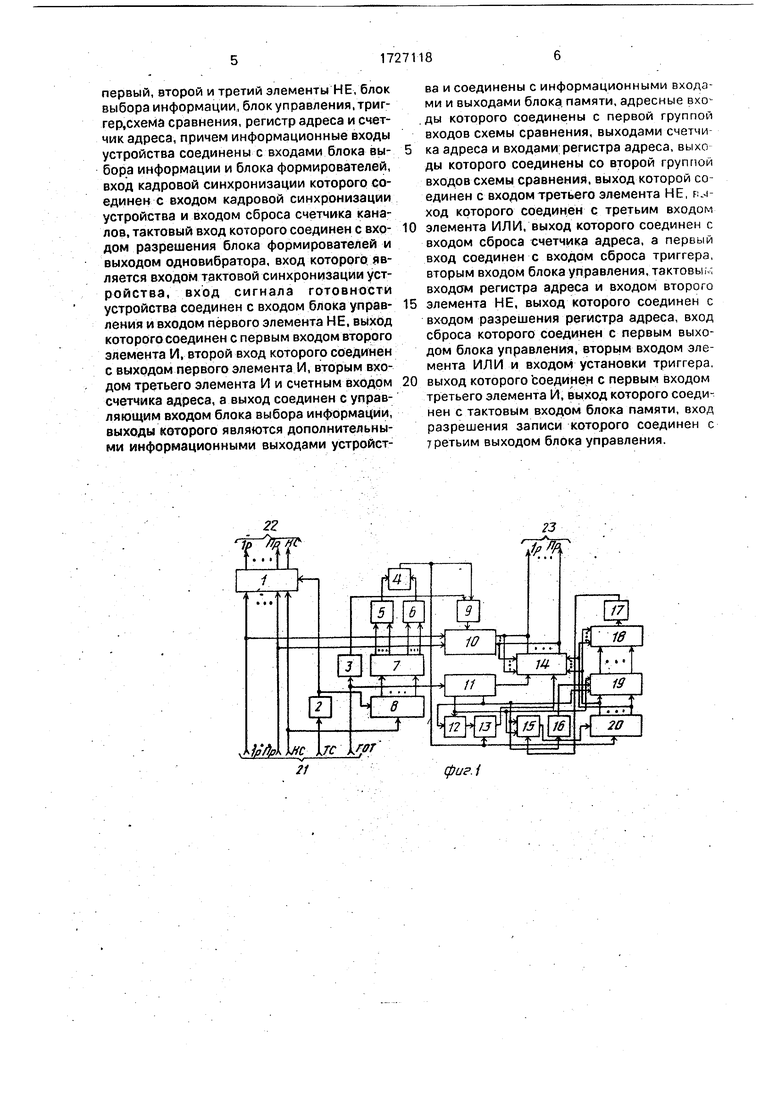

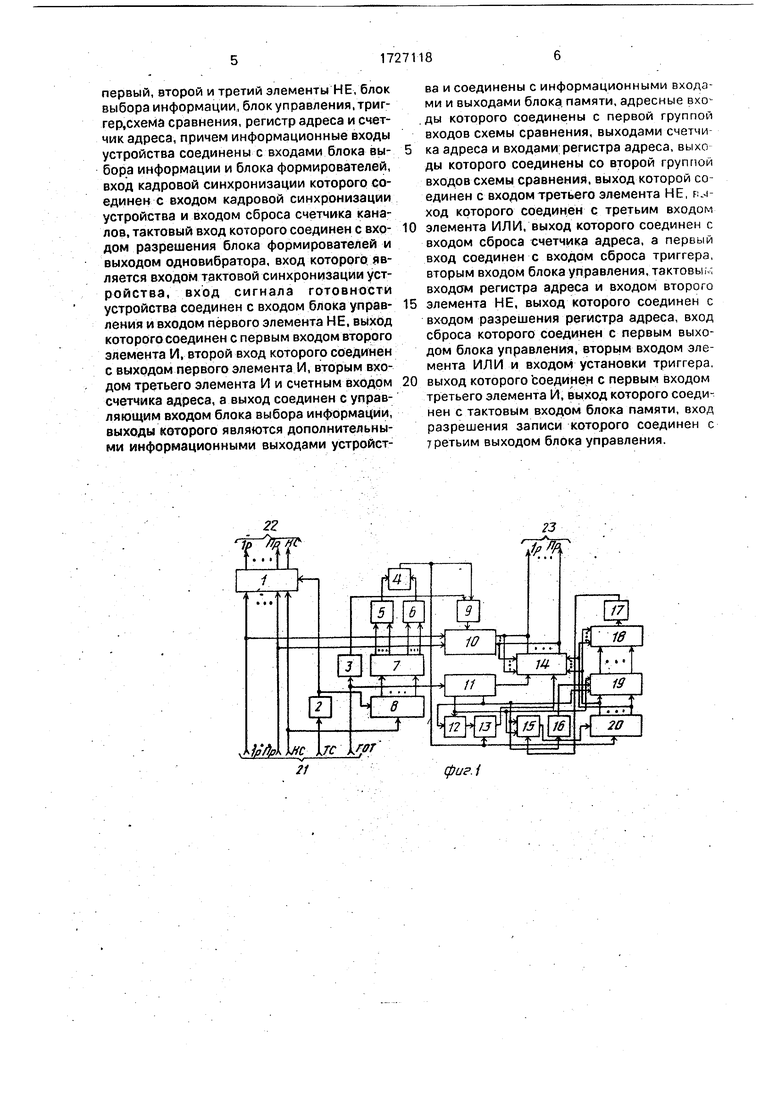

На фиг. 1 приведена структурная схема устройства; на фиг. 2 приведена временная диаграмма его работы.

Устройство содержит блок формирователей 1, одновибратор 2, первый элемент Н Е 3, первый элемент И 4, первый 5 и второй 6 переключатели, дешифратор 7, счетчик каналов 8, второй элемент И 9, блок выбора информации 10, блок управления 11, триггер 12, третий элемент И 13, блок памяти 14, элемент ИЛИ 15, второй элемент НЕ 16,

третий элемент НЕ 17, схему сравнения 18, регистр адреса 19 и счетчик адреса 20.

Устройство работает следующим образом,

На информационные входы устройства поступает многоканальная информация, представленная в формате кадровой структуры. Кадровая структура информации - это последовательность параллельных Двоичных кодов, поступающих по раздельным входным каналам. Каждый двоичны и код соответствует конкретному входному каналу, синхронизация которого осуществляется сигналом синхронизации ТС. Сигнал кадровой синхронизации КС синхронизирует последовательность двоичных кодов и их сигналов ТС в соответствии с числом каналов. КС поступает на вход устройства одновременно с первым сигналом ТС, т.е. в канал, в котором находится информация первого измерительного сигнала. .

Ч КЭ VI

00

С приходом сигнала КС счетчик каналов 8 устанавливается в ноль, а первым задержанным одновйбратором 2 сигналом ТС устанавливается в единичное состояние и до прихода следующего КС сигнала счетчик 8 подсчитывает сигналы ТС, Дешифратором 7 формируются единичные и десятичные состояния счетчика 8, с которых переключателями 5 и б выбирается любой из номеров каналов, например 1-й канал 64-х канального информационного кадра. В этом случае по 1-у каналу и поступает в устройство информация, характеризующая то внешнее .воздействие, отклики которого в течение времени (см. фиг. 2) присутствуют на входах всех остальных, задействованных в реальных экспериментах и испытаниях первичных преобразователях. Время (t2-ti), во время которого имеет место воздействие, сопровождается сигналом готовности со входа ТОТ устройства. С выхода первого элемента Н Е З сигнал ГОТ разрешает синхросигналу выбранного 1-го канала проходить через второй элемент И 9 (в. д. № 4) на управляющий вход схемы выбора информации 10, на информационных входах которой и находятся в это время коды сигналов с i-ro канала. Данные с 1-го канала поступалртсо- ответственно через схему 10 .на дополнительные выходы устройства и на информационные входы блока памяти 14 (в.д. № 6,7). На разрешающий запись вход блока памяти 14 при наличии сигнала ГОТ с блока управления 11 поступает сигнал, разрешающий запись, а на тактовый вход блока памяти поступает в это время сигнал ТС i-ro канала (в.д. № 12), по которому информация с i-ro канала заносится в блок памяти 14. Разрешение на поступление тактового сигнала на вход блока памяти формируется триггером 12 (в.д. Мг 10) и элементом И 13. Для этого блоком управления 11 по переднему фронту сигнала ГОТ (время ti) вырабатывается сигнал (в.д. № 8), устанавливающий триггер 12 в единичное состояние, которое сохраняется до окончания сигнала ТОТ, когда блоком 11 по заднему фронту сигнала вырабатывается сигнал (в.д. №9), устанавливающий триггер 12 в нулевое состояние.

Таким образом, за время (ta-ti) все поступившие на вход коды 1-го канала будут занесены через блок 10 в блок памяти 14, а также будут находиться и на дополнительном выходе устройства. В то же время (ta-ti) всё сигналы ТС 1-го канала будут подсчитываться счетчиком адреса 20, который устанавливается в начальное ну/евоесостояние сигналом, вырабатываемым блоком управления 11 по началу сигнала ТОТ (поступая

в блок 20 через элементы ИЛИ 15, в. д. № 13). В момент t2, когда время существования сигнала ГОТ заканчивается, триггер 12 запрещает поступление тактовых сигналов на

блок памяти 14, а по сигналу с блока управления 11 (в. д. № 9) информация со счетчика адреса 20 заносится в регистр адреса 1.9, а счетчик адреса 20 устанавливается в исходное состояние для очередного подсчета сиг0 налов ТС i-ro канала (в.д. № 14). В следующем цикле подсчета сигналов ТС 1-го. канала блоком 20 сигналы ТС 1-го канала уже не будут поступать на тактовый вход блока памяти 14, так как триггер 12 будет находить5 ся в нулевом состоянии (сигнал ГОТ закончился). Выходные состояния счетчика адреса 20 поступают на адресные входы блока памяти 14, по которым при наличии сигнала ГОТ (разрешение записи на уп0 равляющем входе блока 14) в блок памяти . заносились коды с i-ro канала, а при отсутствии сигнала ГОТ (разрешение чтения на управляющем входе блока 14} с блока памяти в соответствии с адресами с блока 20

5 информация поступает на дополнительный выход устройства, т.е. на дополнительный выход устройства непрерывно поступает код с i-ro канала в соответствии с циклом времени (). Окончание вывода очеред0. ного цикла данных i-ro канала с блока памяти 14 закончится тогда, когда занесенное по окончанию сигнала ГОТ содержимое блока 20 в регистр адреса 19 сравнится с текущим значением на выходе блока 20, что

5 осуществляется элементом сравнения 18, на выходе которого в момент сравнения вырабатывается сигнал (в.д. Ns 16,17), устанавливающий каждый раз счетчик адреса в начальное, исходное состояние. Так будет

0 происходить до тех пор, пока на вход устройства не поступит следующий сигнал ТОТ.

Фор мула изобретения- Устройство для ввода информации, со5 держащее блок формирователей информационные выходы которого являются информационными выходами устройства, одновибратор, элемент ИЛИ, первый, второй и третий элементы И, первый и второй

0 переключатели, дешифратор и счетчик кана- лов,выходы которого соединены с входами дешифратора, выходы которого соединены соответственно с входами первого и второго переключателей, выходы которых соедине5 ны соответственно с первым и вторым входами первого элемента И,о т личающее- с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения циклического вывода соответствующих данных, в устройство введены

первый, второй и третий элементы НЕ, блок выбора информации, блок управления, триг- гер,схема сравнения, регистр адреса и счетчик адреса, причем информационные входы устройства соединены с входами блока выбора информации и блока формирователей, вход кадровой синхронизации которого соединен с входом кадровой синхронизации устройства и входом сброса счетчика каналов, тактовый вход которого соединен с входом разрешения блока формирователей и выходом одновибратора, вход которого является входом тактовой синхронизации уст- ройства, вход сигнала готовности устройства соединен с входом блока управления и входом первого элемента НЕ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходам первого элемента И, вторым входом третьего элемента И и счетным входом счетчика адреса, а выход соединен с управляющим входом блока выбора информации, выходы которого являются дополнительными информационными выходами устройства и соединены с информационными входами и выходами блока, памяти, адресные вхсг .ды которого соединены с первой группой входов схемы сравнения, выходами счетчи

ка адреса и входами: регистра адреса, выхо ды которого соединены со второй группой входов схемы сравнения, выход которой соединен с входом третьего элемента НЕ, пл- ход которого соединен с третьим входом

элемента ИЛИ, выход которого соединен с входом сброса счетчика адреса, а первый вход соединен с входом сброса триггера, вторым входом блока управления, тактовые входе регистра адреса и входом второго

элемента НЕ, выход которого соединен с входом разрешения регистра адреса, вход сброса которого соединен с первым выходом блока управления, вторым входом элемента ИЛИ и входом установки триггера,

выход которого соединен с первым входом третьего элемента И, выход которого соединен с тактовым входом блока памяти, вход разрешения записи которого соединен с третьим выходом блока управления.

| Устройство для ввода информации | 1987 |

|

SU1424002A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-15—Публикация

1990-03-01—Подача