Изобретение относится к специализированным устройствам вычислительной техники и может использоваться в декодирующих устройствах, работающих с двоичными каскадными блоковыми кодами, использующих межблоковое деперемеже- ние данных, например, в устройствах приема данных, передающих через канал связи с помехами (передача цифровой звуковой информации в теле- и радиовещании, в телемеханике и др.).

Целью изобретения является расширение функциональных возможностей пере- межателя путем выполнения нелинейного деперемежения данных непостоянной разностью задержки каждого предыдущего и следующего за ним данного в блоках данных кода.

На чертежах приняты следующие обозначения:

S - число данных в блоке данных кода,

i - номер данного в блоке данных кода, i 1,2,3,....S;

Bi - число блоков данных кода, на которое задерживается 1-е данное в блоке данных кода при деперемежении данных, при этом Bs 0, BI , BI Вм;

bi - разность числа блоков данных кода, на которые задерживаются 1-е и (К1)-е дан00

ел

ON 4

О

мое в блоке данных кода, при этом bi 5:2. bs «0. bi BI- Вн-1 1.

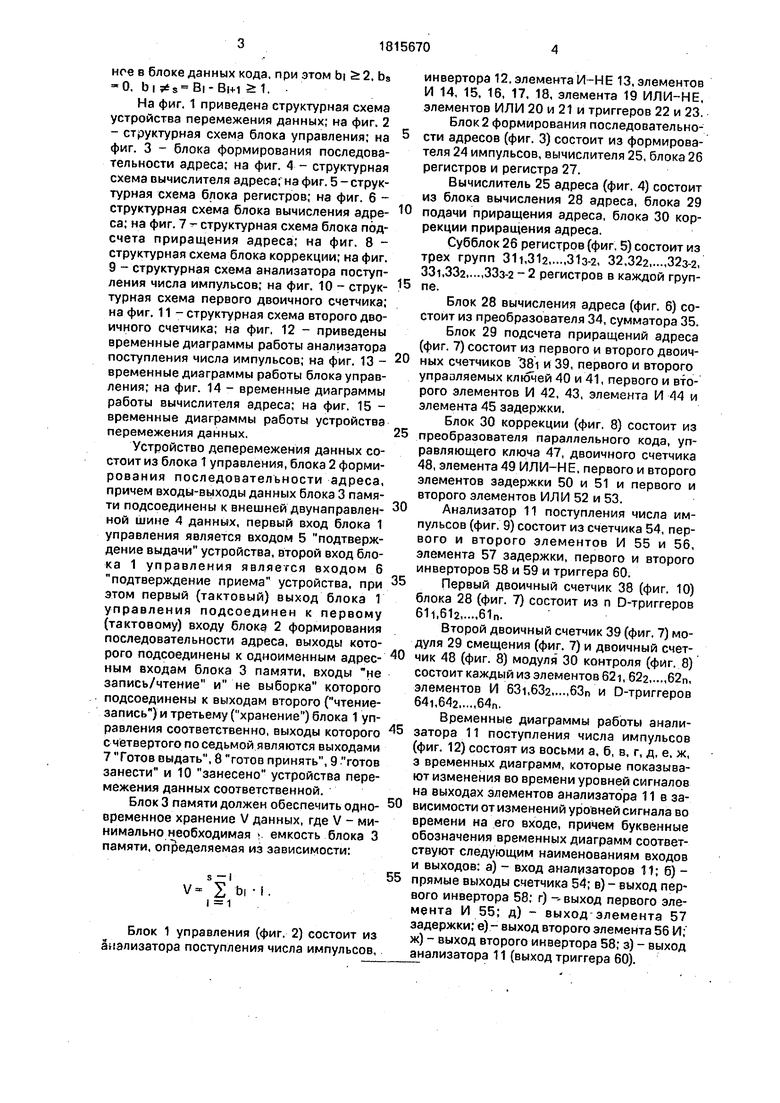

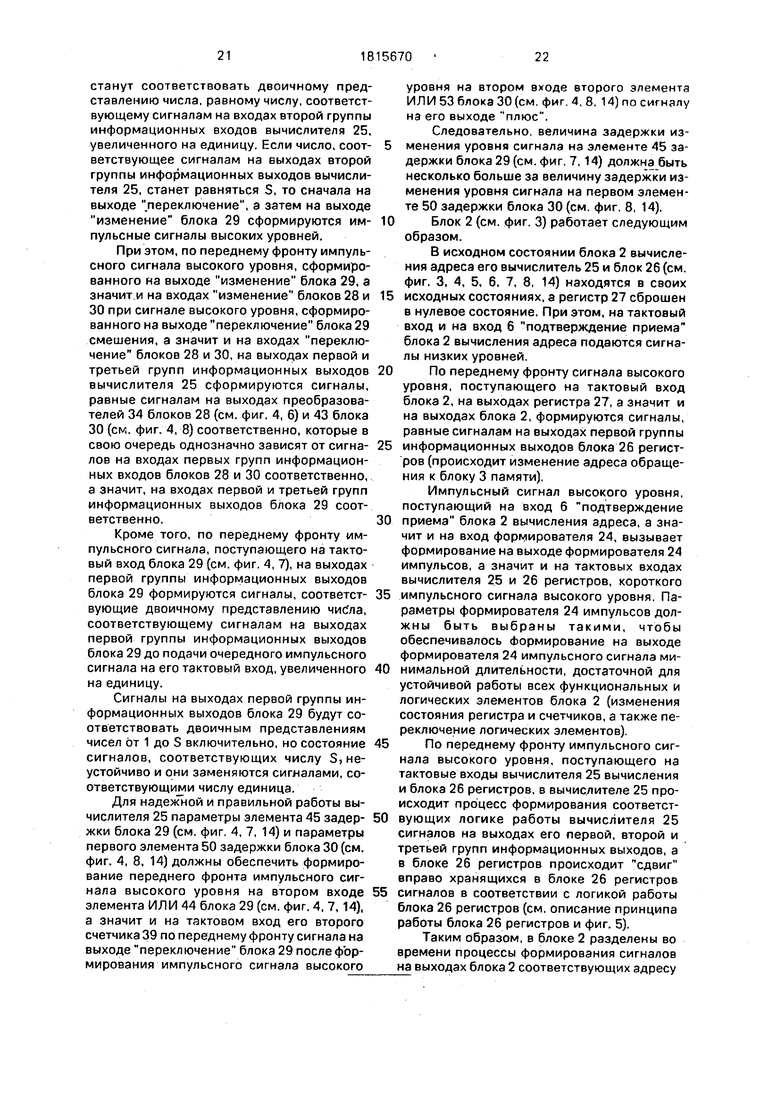

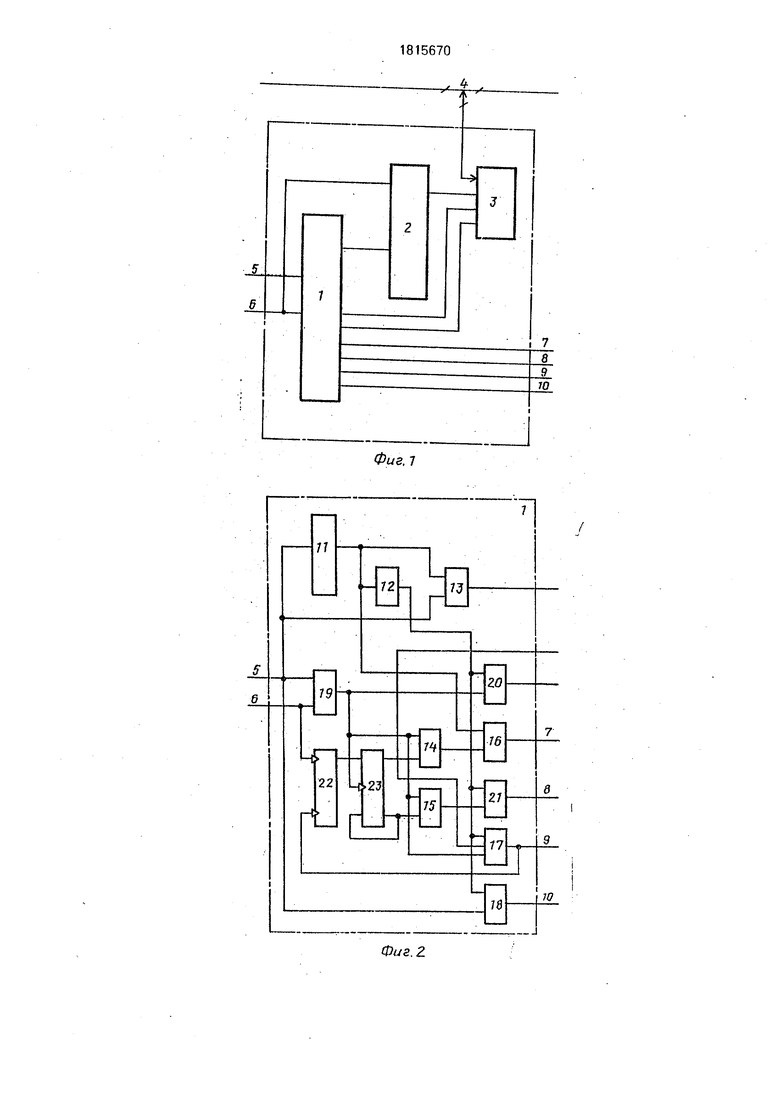

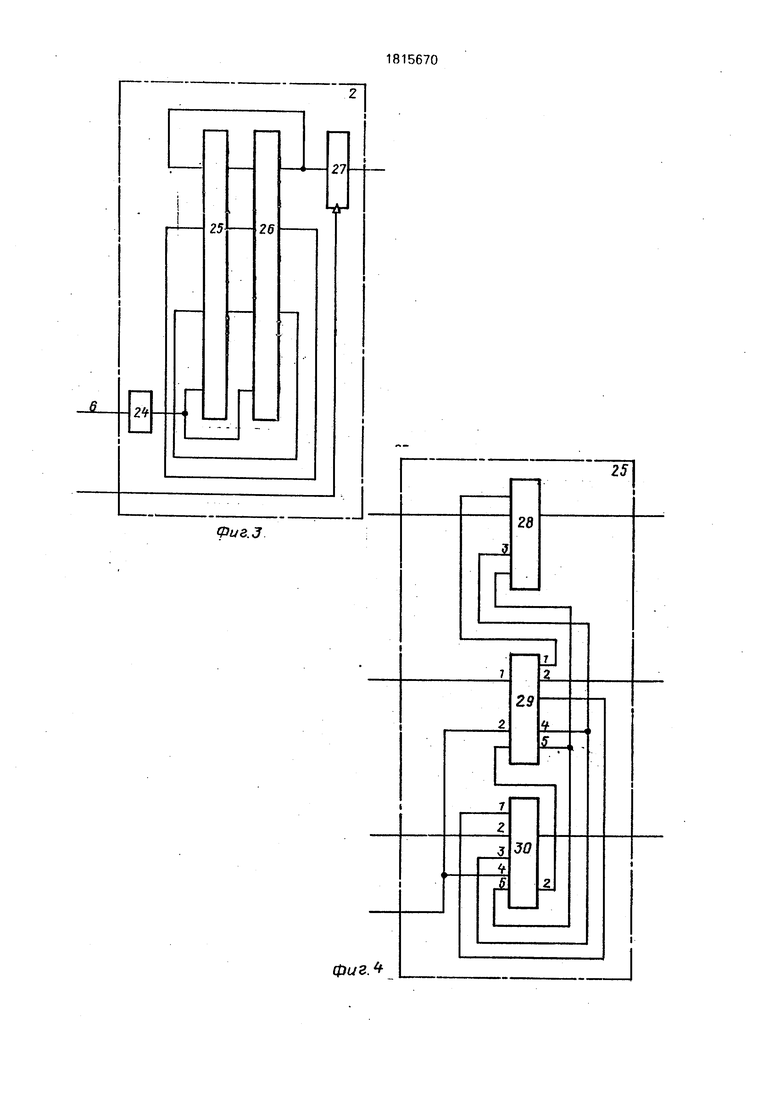

На фиг. 1 приведена структурная схема устройства перемежения данных; на фиг. 2 - структурная схема блока управления: на фиг. 3 - блока формирования последовательности адреса; на фиг. 4 - структурная схема вычислителя адреса; на фиг. 5-структурная схема блока регистров; на фиг. 6 - структурная схема блока вычисления адреса; на фиг. 7 т структурная схема блока подсчета приращения адреса; на фиг. 8 - структурная схема блока коррекции; на фиг. 9 - структурная схема анализатора поступления числа импульсов; на фиг. 10 - структурная схема первого двоичного счетчика; на фиг. 11 - структурная схема второго двоичного счетчика; на фиг. 12 - приведены временные диаграммы работы анализатора поступления числа импульсов; на фиг. 13 - временные диаграммы работы блока управления; на фиг. 14 - временные диаграммы работы вычислителя адреса; на фиг. 15 - временные диаграммы работы устройства перемежения данных.

Устройство деперемежения данных состоит из блока 1 управления, блока 2 формирования последовательности адреса, причем входы-выходы данных блока 3 памяти подсоединены к внешней двунаправленной тине 4 данных, первый вход блока 1 управления является входом 5 подтверждение выдачи устройства, второй вход блока 1 управления является входом 6 подтверждение приема устройства, при этом первый (тактовый) выход блока 1 управления подсоединен к первому (тактовому) входу блока 2 формирования последовательности адреса, выходы которого подсоединены к одноименным адресным входам блока 3 памяти, входы не запись/чтение и не выборка которого подсоединены к выходам второго (чтение- запись) и третьему (хранение) блока 1 управления соответственно, выходы которого с четвертого по седьмой являются выходами 7 Готов выдать, 8 готов принять, 9 готов занести и 10 занесено устройства пере- меженил данных соответственной.

Блок 3 памяти должен обеспечить одновременное хранение V данных, где V - минимально необходимая емкость блока 3 памяти, определяемая из зависимости:

s - I

V- Ј Ы I- .

Блок 1 управления (фиг, 2) состоит из анализатора поступления числа импульсов,

инвертора 12. элемента И-НЕ 13, элементов

И 14, 15, 16, 17, 18, элемента 19 ИЛИ-НЕ,

элементов ИЛИ 20 и 21 и триггеров 22 и 23.

Блок 2 формирования последовательности адресов (фиг. 3) состоит из формирователя 24 импульсов, вычислителя 25, блока 26 регистров и регистра 27.

Вычислитель 25 адреса (фиг. 4) состоит из блока вычисления 28 адреса, блока 29

подачи приращения адреса, блока 30 коррекции приращения адреса.

Субблок 26 регистров (фиг. 5) состоит из трех групп 311,312,....31з-2, 32,322,...,32з-2, 331,332,...,ЗЗз-2 - 2 регистров в каждой груп5 пе.

Блок 28 вычисления адреса (фиг. 6) состоит из преобразователя 34, сумматора 35. Блок 29 подсчета приращений адреса (фиг. 7) состоит из первого и второго двоич0 ных счетчиков 38i и 39, первого и второго управляемых ключей 40 и 41, первого и второго элементов И 42, 43, элемента И 44 и элемента 45 задержки.

Блок 30 коррекции (фиг. 8) состоит из

5 преобразователя параллельного кода, управляющего ключа 47, двоичного счетчика 48, элемента 49 ИЛИ-НЕ, первого и второго элементов задержки 50 и 51 и первого и второго элементов ИЛИ 52 и 53.

0 Анализатор 11 поступления числа импульсов (фиг. 9) состоит из счетчика 54, первого и второго элементов И 55 и 56, элемента 57 задержки, первого и второго инверторов 58 и 59 и триггера 60.

5 Первый двоичный счетчик 38 (фиг. 10) блока 28 (фиг. 7) состоит из п D-триггеров

61l,6l2,....61n.

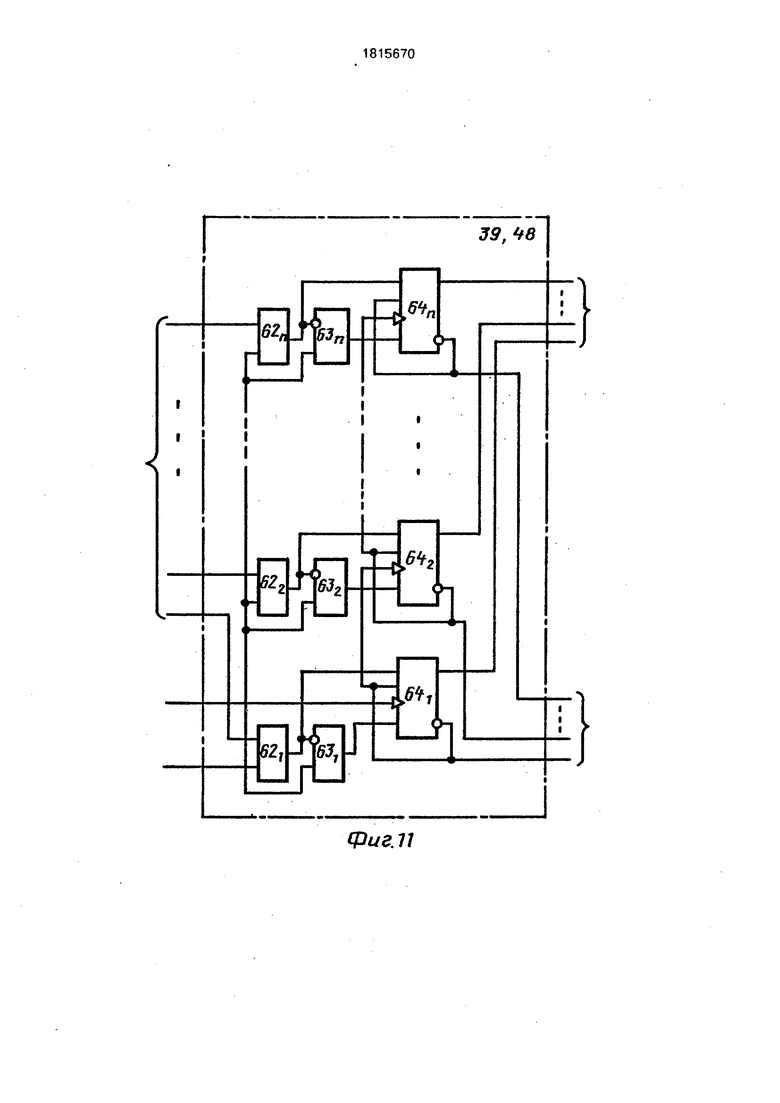

Второй двоичный счетчик 39 (фиг. 7) модуля 29 смещения (фиг. 7) и двоичный счет0 чик 48 (фиг. 8) модуля 30 контроля (фиг. 8) состоит каждый из элементов 62i, 622,...,62П, элементов И 63i,632,...,63n и D-триггеров 641,642....,64П.

Временные диаграммы работы анали5 затора 11 поступления числа импульсов (фиг. 12) состоят из восьми а, б, в, г, д, е. ж, з временных диаграмм, которые показывают изменения во времени уровней сигналов на выходах элементов анализатора 11 в за0 висимости от изменений уровней сигнала во времени на его входе, причем буквенные обозначения временных диаграмм соответствуют следующим наименованиям входов и выходов: а) - вход анализаторов 11; б) 5 прямые выходы счетчика 54; в) - выход первого инвертора 58; г) -- выход первого элемента И 55; д) - выход элемента 57 задержки; е) - выход второго элемента 56 И; ж) - выход второго инвертора 58; з) - выход анализатора 11 (выход триггера 60).

Временные диаграммы работы блока 1 управления (фиг. 13} состоят из тринадцати а, б, в, г, д, е, ж, з, и, и, к, л, м временных диаграмм работы блока 1 управления. Временные диаграммы работы блока 1 управле- ния (см. фиг. 14) показывают изменения во времени уровней сигналов на выходах блока 1 управления и его элементов в зависимости от изменений уровней сигналов на входах блока 1 управления.

На фиг. 13 буквенные обозначения временных диаграмм соответствуют следующим наименованиям входов и выходов: а) - вход 5 подтверждение выдачи блока 1 управления; б) - вход б подтверждение при- ема блока 1 управления; в) -. выход анализатора 11; г) - тактовый выход блока 1 управления; д) - выход инвертора 12; е) - выход первого триггера 22; ж) - выход элемента ИЛИ-НЕ 19; з) - выход чтение/за- пись блока 1 управления; и) - выход хранение блока 1 управления; и) - выход 7 готов выдать блока 1 управления; к) - выход 8 готов принять блока 1 управления; л) - выход 9 готов занести блока 1 управления; м)- выход 10 занесение блока 1 управления.

Временные диаграммы работы вычислителя 25 адреса (фиг. 14) состоят из двенадцати а, б, в, г, д, е, ж, з, и, к, л, м временных диаграмм, которые показывают изменения уровней сигналов во времени на выходах вычислителя 25 и на выходах его функциональных элементов (см. фиг. 3, 4, 6, 7, 8) в зависимости от изменений уровня сигнала на тактовом входе вычислителя 25, причем буквенные обозначения временных диаграмм соответствуют следующим наименованиям входов и выходов: а)- тактовый вход вычислителя 25; б) - выход переключение блока 29 (выход элемента И 43 блока 29); в) - выход изменение блока 29 (тактовый вход второго счетчика 39 блока 29); г) - выход плюс блока 30 (выход элемента 49 ИЛИ-НЕ блока 30); д) - выход элемента 45 задержки блока 29; е) - выход первого элемента И 42 блока 29; ж) - счетный вход счетчика 48 блока 30; з) - тактовый вход счетчика 48 блока 30; и) - выход первого элемента ИЛИ 52 блока 30; к) - выход пер- вого элемента 50 задержки блока 30; л) - группа информационных выходов блока 30 (прямые выходы счетчика 48 блока 30); м) - вторая группа информационных выходов блока 29 (прямые выходы второго счетчика 39 блока 29).

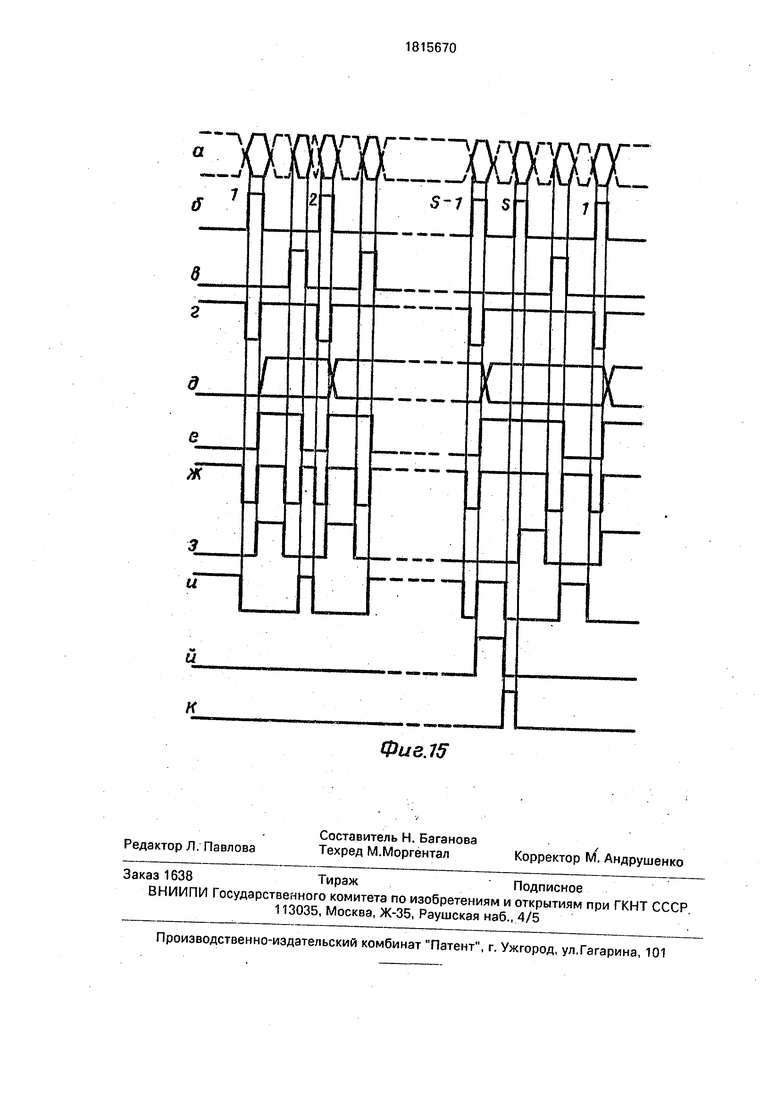

Временные диаграммы работы устройства нелинейного деперемежения данных (фиг. 15) состоят .из одиннадцати а, б, в, г, д, е, ж, з, и, и, к временных диаграмм работы

устройства нелинейного деперемежения данных. Временные диаграммы работы устройства нелинейного перемежения данных (см. фиг, 15) показывают изменения во времени уровней сигналов на входах и выходах устройства и его блоков, а также на шине данных. На фиг. 15 буквенные обозначения временных диаграмм соответствуют следующим наименованиям входов и выходов: а) - шина 4 данных; б) - вход 5 подтверждение выдачи устройства; в) - вход 6 подтверждение приема устройства; г) - тактовый выход блока 1 управления; д) - выхода блока 2; е)- выход чтение/запись блока 1 управления; ж) - выход хранение блока 1 управления; з) - выход 7 готов выдать устройства; и) - выход 8 готов принять устройства; и) - выход 9 готов занести устройства: к) - выход 10 занесение устройства.

Устройство нелинейного деперемежения данных (фиг. 1) работает по следующему принципу: данные на вход устройства нелинейного перемежения данных поступают последовательно во времени друг за другом по шине 4 данных; 1-е данное текущего 0ло- ка данных, при , записывается устройством нелинейного перемежения данных в блок 3 памяти и затем считывается на шину 4 данных из блока 3 памяти.

Анализатор 11 (фиг. 2,9) работает следующим образом.

В исходном состоянии анализатора 11 его счетчик 54 сброшен в нуль (на всех прямых выходах счетчика 54 сформированы сигналы низких уровней), триггер 60 установлен в единицу, а на выход анализатора 11 полагается сигнал низкого уровня. При этом, на его выходе сформирован сигнал высокого уровня, а на выходах первого и второго элементов И 55 и 56 сформированы сигналы низких уровней, а на выходах первого и второго инверторов 58 и 59 - сигналы высоких уровней. По переднему фронту импульсного сигнала высокого уровня, поступающего на вход анализатора 11, состояние счетчика 54 увеличивается на единицу (сигналы на прямых выходах счетчика 54 формируются в соответствии с двоичным представлением числа на единицу большего за число, соответствующее сигналам на прямых выходах счетчика 54, при его предыдущем состоянии), а по сразу этого сигнала, благодаря первому инвертору 58 - на выходе триггера 60 формируется сигнал по уровню равный сигналу на его информационном входе.

Следовательно, первое изменение состояния триггера 60 произойдет только после поступления на вход анализатора 11

(s-1)-ro no порядку счета импульсного сигнала высокого уровня.

При поступлении на вход анализатора 11 S-ro по порядку счета импульсного сигнала высокого давления, на выходе первого элемента И 55 сформируется сигнал высокого уровня, по которому через время задержки на элементе 57 задержки счетчик 54 сбросится в нуль и на выходе первого элемента 55 сформируется сигнал низкого уровня. При этом, благодаря первому инвертору 58 по сигналу высокого уровня на информационном входе триггер 60 установится в единицу и анализатор 11 переходит в свое исходное состояние. Время задержки т,3ад изменения уровня сигнала на элементе 57 задержки выбирается из условия надежной работы анализатора 11 и должно как можно больше приближаться к нулю.

Блок 1 управления (фиг. 2, 13) работает следующим образом.

В исходном состоянии блока 1 управления анализатор 11 находится в своем исходном состоянии, а триггеры 22 и 23 сброшены в нуль. На входы 5 подтверждение выдачи и 6 подтверждение приема блока 1 управления в его исходном состоянии подаются сигналы низкого уровня. При этом, на инверсном выходе триггера 23, на выходе элемента ИЛИ-НЕ 19 и на выходе анализатора 11 сформированы сигналы высокого уровня, а на выходе инвертора 12 - сигнал низкого уровня. Следовательно, на выходах 7 готов выдать, 9 готов занести, 10 занесение и чтение/запись блока 1 управления сформированы сигналы низкого уровня, а на его выходах 8 готов принять, хранение и на тактовом выходе - сформированы сигналы высокого уровня. При поступлении импульсного сигнала высокого уровня на вход 5 подтверждение выдачи блока 1 управления на выходе его элемента ИЛИ-НЕ формируется импульсный сигнал низкого уровня, а на выходе элемента И-НЕ 13, а значит и на тактовом выходе блока 1 управления, при сигнале высокого уровня на его первом входе элемента И-НЕ 13, формируется импульсный сигнал низкого уровня. По заднему фронту импульсного сигнала низкого уровня (при переходе уровня сигнала с низкого на высокий) на выходе элемента ИЛИ-НЕ 19 происходит изменение состояния второго триггера 23, если на его вход принудительной установки в единичное состояние подается сигнал низкого уровня, так как инверсный выход подсоединен к информационному входу триггера 23 (и на базе триггера 23 организован двоичный счетчик по модулю два. Следовательно, во

время действия импульсного сигнала высокого уровня на входе 5 подтверждение выдачи блока 1 управления, на его тактовом выходе формируется импульсный сигнал

высокого уровня, а на выходе хранение - импульсный сигнал низкого уровня. При этом, на выходе 8 готов принять формируется сигнал низкого уровня. По окончании действия импульсного сигнала высокого

0 уровня на выходе 5 подтверждение выдачи блока 1 управления, на его выходах 7 готов выдать, хранение и на тактовом выходе формируются сигналы высокого уровня, а на выходе 8 готов принять 5 сигнал низкого уровня не изменяется.

При поступлении импульсного сигнала высокого уровня на вход б подтверждение приема блока 1 управления на выходе элемента ИЛИ-НЕ 19 формируется импульс0 ный сигнал низкого уровня, а триггер 22 сбросится в нуль, если он находился в единичном состоянии.

Следовательно, во время действия импульсного сигнала высокого уровня на вхо5 де 6 подтверждение приема блока 1 управления на его выходе чтение/запись будет поддерживаться сигнал высокого уровня, а на. выходе 7 готов выдать, 8 готов принять - будут сформированы сигна0 лы низкого уровня. По окончании действия импульсного сигнала высокого уровня на входе 6 подтверждение приема блока 1 управления по сигналу на выходе элемента ИЛИ-НЕ 19 его триггер 23 изменит свое со5 стояние (на нулевое), если на его вход принудительной установки в единичное состояние не подается сигнал высокого уровня. Следовательно, если триггер 23 сбросится в нулевое состояние, то на выходах 8 готов принять и

0 хранение сформируются сигналы высокого уровня, а на выходе 7 готов выдать - сигнал низкого уровня.

Сигналы на выходах 9 готов занести, 10 занесение и тактовом выходе блока 1

5 управления не изменяют свой низкий уровень, если на вход 6 подтверждение приема блока 1 управления подаются импульсные сигналы высокого уровня.

Кроме того, учитывая логику работы

0 анализатора 11 анализа (см. фиг. 12, 9) на время между окончаниями поступления каждого (S-1)-ro и S-ro по порядку счета импульсного сигнала высокого уровня на вход 5 подтверждение выдачи блока 1 управле5 ния, на входе инвертора 12 и на первых входах элементов И-НЕ 13 и И 16 формируется сигнал низкого уровня. Следовательно, в этом случае на выходе хранение и 8 готов принять блока 1 управления формируются сигналы высокого уровня.

По окончании действия каждого (S-l)-ro по порядку счета импульсного сигнала высокого уровня, поступающего на вход 5 подтверждение выдачи блока t управления на первом, втором и третьем входах элемента 17 И формируются сигналы высокого уровня. Следовательно, по окончании действия каждого (S-1)-ro по порядку счета импульсного сигнала высокого уровня, поступающего на вход 5 подтверждение выдачи блока 1 уп- равления, на его выходе 9 готов занести формируется сигнал высокого уровня, по переднему фронту которого триггер 22 установится в единичное состояние. ч

При поступлении на вход 5 подтверж- дение выдачи блока 1 управления каждого S-ro по порядку счета импульсного сигнала высокого уровня, на выходах 10 занесение блока 1 управления формируется сигнал высокого уровня, а на тактовом выходе блока 1 управления -уровень сигнала не изменяется (низкий уровень).

Таким образом, по окончании действия каждого S-ro по порядку счета импульсного сигнала высокого уровня, поступающего на вход 5 подтверждение выдачи блока 1 управления, блок 1 управления переходит в свое исходное состояние. Изменения уровней сигналов на входах и выходах блока 1 управления и основных его элементов приведены на временных диаграммах работы блока 1 управления {см. фиг. 13).

Блок 28 вычисления адреса (см. фиг. 6) работает следующим образом. В исходном состоянии блока 28 адреса сигналы на выходах регистра 37 соответствуют двоичному представлению числа, равного единице, а на входы переключение и изменение подаются сигналы низкого уровня.

По переднему фронту импульсного сигнала высокого уровня, поступающего на вход изменение блока 28, на выходах регистра 37, а значив на выходах блока 28 адреса, сформируются сигналы, равные либо сигналам на одноименных выходах сумматора 35, если на вход переключение блока 28 подается сигнал низкого уровня, либо сигналам на одноименных выходах преобразователя 34, если на вход переключение блока 28 подается сигнал высокого уровня. Сигналы на выходах преобразователя 34 зависят от сигналов на его входах, а значит и на входах первой группы информационных входов блока 28.

Эта зависимость описывается следующим образом.

Если на входы первой группы информационных входов блока 28 поступают сигналы, соответствующие двоичному представлению числа J. где j GN, ,2,3,...,S-1, то на выходах преобразователя 34 сформируются сигналы, соответствующие двоичному представлению числа

AJ AJ-I + о -1) Ьм + 1,

где AJ-I - значение числа AJ при , при этом принимается:

А0 -1, bo 0.

Начальный адрес области блока 3 памяти, предназначенного для перемежения данных, соответствующих числу Ai.

+ (1 - 1)-0+1 -1+0+1 0.

По этому адресу записывается первое данное первого блока данных кода, поступающего по шине 4 данных (см. фиг. 1) на перемеженив:

Таким образом, таблица истинности преобразователя 34. показывающая зависимость сигналов на его выходах от сигналов на его входах, будет иметь вид:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство перемежения-деперемежения данных | 1990 |

|

SU1714639A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

Изобретение относится к специализированным устройствам вычислительной техники и может использоваться в декодирующих устройствах, работающих с двоичными каскадными блоковыми кодами, использующих межблоковое демеремеже- ние данных. Цель изобретения - расширение функциональных возможностей устройства. Устройство деперемежения данных содержит ОЗУ, блок вычисления адреса, блок управления. Блок вычисления адреса содержит формирователь импульсов, субблок вычисления, субблок регистров и регистр. Субблок вычисления содержит модуль адреса, модуль смещения и модуль контроля. Модуль адреса содержит преобразователь, сумматор, управляемый ключ и регистр. Модуль смещения содержит первый и второй управляемые ключи, первый и второй элементы И, элемент ИЛИ и элемент задержки. Модуль контроля содержит преобразователь, управляемый ключ, двоичный счетчик, элемент ИЛИ-НЕ, первый и второй элементы задержки, а также первый и второй элементы ИЛИ. 5 з.п.ф-лы, 15 ил. 2 табл.

Таблица истинности преобразователя 34

Числа, двоичные представления

на входах преобразователя 34

1

2

3

s-1

Таблица 1

которых соответствуют сигналам

на выходах преобразователя 34 в зависимо- сти от сигналов на его входах

At-О

+ 1

Аз Аа + -2 Ь2 + 1

А Aj-1 + 0 - 1) bj-1 + 1

Ag-1 . As-2 + (s - 2) bs-2 J 1

Сигналы на выходах сумматора 35 соответствуют двоичному представлению суммы чисел, соответствующих сигналам на входах первой и второй групп информационных входов блока 28.

Первый двоичный счетчик 38 (фиг. 10) блока 29 (фиг. 7) работает следующим образом.

В исходном состоянии первый D-триг- гер 61 двоичного счетчика 38 установлен в единицу, а все остальные D-триггеры 61J, где ,3,...,ni, сброшены в нуль, а на счетный вход и вход установки в единицу двоичного счетчика 38 подаются сигналы низких уровней. При этом, на группе прямых выходов первого двоичного счетчика 38 блока 29 формируются сигналы, соответствующие числу единица, а на инверсных выходах числу2п1-2.

По переднему фронту импульсного сигнала, поступающего на счетный вход счетчика 38, первый D-триггер 611 сбросится в нуль, а второй D-триггер 612 - установится в единицу. Таким образом, состояние счетчика 38 увеличилось на единицу и на прямых выходах счетчика 38 сформировались сигналы, соответствующие двоичному представлению числа два.

При поступлении очередного импульсного сигнала на счетный вход счетчика 38 его состояние увеличивается на единицу.

При подаче сигнала высокого уровня на вход установки в единицу двоичного счетчика 38 двоичный счетчик 38 устанавливается в свое исходное состояние.

Второй двоичный счетчик 39 (фиг. 11) блока 29 (фиг. 7) и двоичный счетчик 48 (фиг. 11) блока 30 (фиг. 8) работает следующим образом.

В исходном состоянии второго двоичного счетчика 39 блока 29 смещения первый его D-триггер 64 установлен в единичное состояние, а все остальные D-триггеры 64J, где ,3,4,...,n2, сброшены в нуль.

При этом, на прямых выходах второго двоичного счетчика 39 блока 29 сформированы сигналы, соответствующие двоичному представлению числа один. В исходном состоянии двоичного счетчика 48 блока 30 его D-триггеры 64 j, для которых j-e разряды, начиная с самого младшего за номером один, двоичного представления числа

+ 1 - bi равны единице, установлены в единичное состояние,- а остальные - сброшены в нуль.

При этом на прямых выходах двоичного счетчика 48 блока 30 сформированы сигна0

5

0

5

0

5

0

5

0

5

лы, соответствующие двоичному представлению числа + 1 - bi.

Например, пусть пз 3 и bi 3.

Тогда, 23 + 1 - 3 6ю 1102 и, следовательно, в исходное состояние двоичного счетчика 48 блока 30 контроля его первый триггер 64 будет сброшен в нуль, а второй и третий D-триггеры 64а и 64з- будут установлены в единичное состояние.

Кроме того, в исходном состоянии второго двоичного счетчика 39 блока 29 и счетчика 48 блока 30 на их счетные входы и тактовые входы подаются сигналы низких уровней.

При этом, на выходах всех элементов 621,622.....62П И и И 56, 63i.632,...,63h с первым инверсным входом, а, значит, и на установочных и сбросовых входах всех D-триггеров 64i. 642,..., 64П сформированы сигналы низких уровней.

По переднему фронту импульсного сигнала, поступающего на счетный вход счетчиков 39 и 40, состояние счетчиков 39 и 48 увеличился на единицу аналогично работе первого двоичного счетчика 38 блока 29 (см. фиг. 10 и описание работы первого двоичного счетчика 38 блока 29).

При изменении уровней сигналов на входах принудительной установки счетчиков 39 и 40 при сигнале низкого уровня на их тактовом входе на установочных и на сбросовых входах всех D-триггеров 64i,642,...,64n сигналы не изменяют своих уровней, ибо при сигнале низкого уровня на тактовых входах счетчиков 39 и 48 на выходах всех его элементов И 62i. 622,....62П и И 631,632,....63п с первым инверсным входом сформируются сигналы низких уровней.

Если же на J-м входе принудительной установки двоичного счетчика 38 и 48 сформирован сигнал высокого уровня, то при подаче сигнала высокого уровня на тактовый вход счетчика 39 или 48 соответственно, на выходе его элемента И сформируется сигнал высокого уровня, а на выходе его элемента 63 j И с первым инверсным входом - сигнал низкого уровня, ибо на инверсный вход элемента 63 j И с первым инверсным входом подается сигнал высокого уровня, который сформирует на его выходе сигнал низкого уровня. При этом, на установочном входе D-триггера 64i,642....,64п сформируется сигнал высокого уровня, а на сбросовом входе - низкого уровня и D-триггер 64 j принудительно установится в единичное состояние, если был сброшен в.нуль, или не изменит своего состояния, если был уста- ловлен в единичное состояние.

Если же на k-м входе принудительной установки двоичного счетчика 39 или 48, где ,2,3,..,n2 или пЗ соответственно, сформирован сигнал низкого уровня, то при подаче сигнала высокого уровня на тактовый вход счетчика 39 или 48 соответственно, на выходе его элемента 62 И сформируется сигнал низкого уровня, а на выходе его элемента 62 И с первым инверсным входом - сигнал высокого уровня, ибо по сигналу низкого уровня, поступающего на инверсный вход элемента 62 И с первым инверсным входом при сигнале высокого уровня, поступающего на его второй прямой вход, на выходе элемента 62 к И с первым инверсным входом формируется сигнал высокого уровня. При этом, на установочном входе D-триггера 64 формируется сигнал низкого уровня, а на сбросовом входе - высокого уровня и D-триггер 64 принудительного сбрасывается в нуль, если он был установленным в единицу, или не меняет своего состояния, если он был сброшен в нуль.

Следовательно, при подаче сигнала высокого уровня на тактовые входы двоичных счетчиков 39 и 48 на их прямых выходах формируются сигналы, равные сигналам на одноименных их входах принудительной установки соответственно.

Блок 29 (см. фиг. 7) работает следующим образом.

В исходном состоянии блока 29 его первый и второй счетчики 38 и 39 установлены в состояния, соответствующие двоичному представлению числа единица, а на тактовый вход и вход плюс - подаются сигналы низких уровней, При этом, на выходах первого и второго элементов И 42 и 43 сформированы сигналы низких уровней, так как S 1. Следовательно, на выходе элемента 45 задержки и, значит, на втором входе элемента ИЛИ 44 сформирован сигнал низкого уровня. Отсюда следует, что на выходах переключение и изменение блока 39 при его исходном состоянии сформированы сигналы низких уровней, а на первой и второй группах информационных выходов блока 29 - сформированы соответственно сигналы, соответствующие двоичному представлению числа, равного единице. По переднему фронту импульсного сигнала высокого уровня, поступающего на тактовый вход блока 29, состояние первого двоичного счетчика 38 увеличивается на единицу. Если при этом сигналы на выходах первого двоичного счетчика 38 станут соответствовать числу S, то на всех диодах и на выходе

первого элемента И 42 сформируются сигналы высоких уровней.

При достижении сигналом, сформированного на выходе первого элемента И 42

5 высокого уровня, на выходах первого двоичного счетчика 38 сформируются сигналы, соответствующие двоичному представлению числа один, а на выходе первого элемента И 42 снова сформируется сигнал низкого

0 уровня. Таким образом, устойчивые состояния первого двоичного счетчика 38 будут изменяться от единицы до S-1 включительно. Кроме того, по переднему фронту импульсного сигнала высокого уровня.

5 поступающего на тактовый вход блока 29, при сигнале низкого уровня на втором входе элемента ИЛИ 44, на выходах второго двоичного счетчика 39 сформируются сигналы, равные сигналам на группе информацион0 ных входов блока 29 при сигнале низкого уровня на его выходе переключение. По переднему фронту импульсного сигнала высокого уровня, поступающего на вход плюс блока 29, состояние второго двоич5 ного счетчика 39 увеличивается на единицу При этом, если на прямых выходах второго двоичного счетчика 39 сформируются сигналы, соответствующие двоичному пред0 ставлению сила то на всех входах и на выходе второго элемента И 43 сформируется сигнал высокого уровня, который подается на управляющие входы первого и второго управляемых ключей 40 и 41, на вход эле5 мента 42 задержки и на выход переключение блока 29 значит, начиная со времени, когда на выходе второго элемента И 43 сформируется сигнал высокого уровня, на входы принудительной установки второго

0 двоичного счетчика 39 подаются сигналы, равные сигналам на прямых выходах первого двоичного счетчика 38, на выходах второй группы информационных выводов блока 29 формируются сигналы, равные

5 сигналам на прямых выходах второго двоичного счетчика 39, а через время, определяемое параметрами элемента 45 задержки, на втором входе элемента ИЛИ 44 и на его выходе, при сигнале низкого

0 уровня на его первом входе, сформируется сигнал высокого уровня, поступающий на выход изменение блока 29, и по переднему фронту которого на прямых выходах второго двоичного счетчика 39 сформиру5 ются сигналы, равные сигналам на одноименных выходах первого двоичного счетчика 38, которые не будут соответствовать числу, большему за S-1. Следовательно, на выходе второго элемента И 43 снова сформируется сигнал низкого уровня, который поступит на управляющие входы первого и второго управляемых ключей 40 и 41, на вход элемента 45 задержки и на выход переключение блока 29, а через время, определяемое параметрами элемента 45 задержки, поступит и на тактовый вход второго двоичного счетчика 39 и на выход изменение блока 29.

Таким образом, при поступлении на вход плюс блока 29 S-ro по порядку счета импульсного сигнала высокого уровня, на выходах переключение и изменение блока 29 формируются импульсные сигналы высокого уровня, причем сигнал на выходе изменение будет задержанным относительно сигнала на выходе переключение блока 29.

Такая задержка необходима для того, чтобы сигналы с соответствующих входов первого управляемого ключа 40 успели передаться на входы принудительной установки второго двоичного счетчика 39 до прихода переднего фронта сигнала высокого уровня на его тактовый вход. Блок 30 (см. фиг. 8) работает следующим образом.

В исходном состоянии блока 30 на выходах счетчика 48, а значит на группе информационных выходов блока 30 контроля и на входах элемента ИЛИ-НЕ 49, сформированы сигналы, соответствующие двоичному представлению числа 2ПЗ + 1 - bi, где пз - разрядность счетчика 48, a bi - разность числа блоков данных кодов, на которые задерживаются первое и второе данные в блоке данных кода при деперемежении,

причем 2 bi 2п3. Крометого, в исходном

Таблица истинности преобразователя 46

Числа, которые соответствуют сигналам

на входах преобразователя 46

на выходах пре

1

2

s-1

s

0

5

0

5

0

5

состоянии блока 30, на его тактовый вход и на входы переключение и изменение подаются сигналы низких уровней. При этом, на выходе элемента ИЛИ-НЕ 49. а значит, на выходе плюс блока 30 и на управляющем входе управляемого ключа 47 сформирован сигнал низкого уровня, так

как 2ПЗ + 1 - bi 0, при 2 bi 2ПЗ . Если на вход переключение блока 30 поступает сигнал высокого уровня или на выходе плюс блока 30 форсируется сигнал высокого уровня, то по сигналу высокого уровня, формирующемуся в этом случае на выходе первого элемента ИЛИ 52, на входах принудительной установки двоичного счетчика 48 формируются сигналы, равные сигналам на выходе преобразователя 46, которые зависят, причем однозначно, от сигналов на его входах, а значит, от сигналов на первой группе информационных входов блока 30. Эта зависимость сигналов на выходах преобразователя 46 от сигналов на его входах описывается следующим образом: если на вход преобразователя 46 подаются сигналы, соответствующие двоичному представлению числа j, ,2,3,...,5, то на выходах преобразователя 46 формируются сигналы, соответствующие двоичному представлению числа 2ПЗ - bj, где пз - разрядность двоичного счетчика 48, a bj - разность числа блоков данных кода, на которые задерживаются j-e и Q+1)-e данное в блоке данных кода.

Таким образом, таблица истинности преобразователя 46 имеет следующий вид:

Таблица 2

уют сигналам

на выходах преобраздвателя 46

, 2ПЗ - Ь2 2ПЗ - Ь3

2 м bs 1

При одновременном наличии сигналов низких уровней на входе переключение и выходе плюс блока 30 контроля на управляющем входе управляемого ключа 47 формируется сигнал низкого уровня и на входах принудительной установки двоичного счетчика 48 формируются сигналы, равные сигналам на второй группе информационных входов блока 30.

При подаче импульсного сигнала высокого уровня на тактовый вход блока 30 на выходах счетчика 48 сначала формируются сигналы, равные сигналам на его входах принудительной установки, а затем, через время, определение параметрами второго элемента 51 задержки, импульсный сигнал высокого уровня сформируется на счетном входе двоичного счетчика 48, по переднему фронту которого состояние двоичного счетчика 48 увеличивается на единицу. При этом, если предыдущее состояние двоичного счетчика 48 соответствовало двоичному

представлению числа 2ПЗ -1, то двоичный счетчик 48 устанавливается в нулевое состояние и сигналы на его прямых входах станут соответствовать двоичному представлению сил числа нуль. Как только двоичный счетчик 48 установится в нулевое состояние, то на выходе элемента ИЛИ-НЕ 49 сформируется сигнал высокого уровня, который подается на выход плюс блока 30, на вход первого элемента 50 задержки и на второй вход первого элемента ИЛИ 52, на выходе которого при сигнале низкого уровня на его первом входе, тоже формируется сигнал высокого уровня.

Через время, определяемое параметрами первого элемента 50 задержки, сигнал высокого уровня сформируется ,на втором входе второго элемента ИЛИ 53, на выходе которого при сигнале низкого уровня на его первом входе тоже формируется сигнал высокого уровня, который поступает на тактовый вход двоичного счетчика 48.

По переднему фронту сигнала высокого уровня, поступающего на тактовый вход двоичного счетчика 48, на прямых выходах счетчика 48 формируются сигналы, равные сигналам на его входах установки в принудительное состояние.

Сигнал высокого уровня на тактовом входе двоичного счетчика 48 может сформироваться также еще и при подаче на вход изменение модуля контроля сигнала высокого уровня. Параметры первого элемента ЬО задержки выбираются из условия устойчивости работы блока 30 и должны обеспечить формирование сигнала высокого уровня на тактовом входе двоичного счетчика 48 после формирования сигналов на

выходах управляемого ключа 47 при изменении уровня сигнала с низкого на высокий на его управляющем входе при формировании сигнала высокого уровня на выходе 5 плюс блока 30. Задержка изменения уровня сигнала первым элементом 50 должна быть по возможности минимальной.

Параметры второго элемента 51 задержки выбираются из условия устойчи10 вой работы блока 30 и должны обеспечить формирование импульсного сигнала на счетном входе двоичного счетчика 48 после формирования импульсного сигнала высокого уровня на его тактовом входе и после

15 формирования сигналов на его прямых выходах по переднему фронту сигнала, поступающего на тактовый вход двоичного счетчика 48, при условии, что импульсные сигналы высокого уровня подаются на

0 тактовый вход и вход изменение блока 30 одновременно (синхронно). Другими словами, при одновременной подаче импульсных сигналов высокого уровня на тактовый вход и вход изменение модуля 30 контро5 ля, на прямых выходах двоичного счетчика 48 должны сначала сформироваться сигналы, равные сигналам на его входах принуди- тельной установки, а затем состояние двоичного счетчика 48 должно увеличиться

0 на единицу. Задержка изменения уровня сигнала вторым элементом 51 должна быть по возможности минимальной.

После того, как произойдет изменение состояния двоичного счетчика 48 после фор5 мирования сигнала высокого уровня на выходе плюс блока 30 (сигналы на прямых выходах двоичного счетчика 48, а значит и на группе информационных выходов блока 30, станут равными сигналами на выходах

0 преобразователя 46, соответствующие числу, большему за нуль) на выходе элемента ИЛИ-НЕ 49, а значит, на выходе плюс блока 30, на втором входе первого элемента ИЛИ 52 и на входе первого элемента 50

5 задержки, а затем, на тактовом входе двоичного счетчика 48, формируются сигналы Низкого уровня.

Таким образом, нулевое состояние двоичного счетчика 48 является неустойчивым,

0 а установление нулевого состояния двоичного счетчика 48 сопровождается формированием импульсного сигнала высокого уровня на выходе плюс блока 30. При этом, из группы информационных выходов

5 блока 30 формируются сигналы, соответствующие двоичному представлению числа

2ПЗ - bj, если сигналы на первой группе информационных входов блока 30 соответствуют двоичному представлению числа J, где Ы.2,3....,5-1.

Блок 26 регистров (см. фиг. 5) работает следующим образом.

В исходном состоянии блока 26 сигналы на выходах его регистров 31 J, где ,2,3,...,S-2 - порядковый номер регистра 31 в блоке 26 регистров, соответствуют двоичным представлениям чисел AJ, определяемых зависимостями:

Aj-s-2 +1

AJ s-2 Aj+i + (S-j - 1) bs-j-i + 1,

сигналы на выходах регистров 31 J, где ,2,3,...,s-2 - порядковый номер регистра

32 в блоке 26 регистров, соответствуют двоичным представлениям числа С, определяемых зависимостью:

Cj S-j,

а сигналы на выходах регистров 33, где ,2,3,...,s-2 - порядковый номер регистра

33 в блоке 26 регистров, соответствуют двоичным представлениям число DJ, определяемых зависимостью:

DJ 2ПЗ - bs-j,где п3 - число разрядов регистров 33, равное числу разрядов счетчика 48 блока 30 блока 25 вычисления. По переднему фронту импульсного сигнала, поступающего на тактовый вход блока 26 регистров, происходит сдвиг сигналов со входом первой, второй и третьей групп информационных входов блока 26 регистров на выходы первых регистров 30i, 311 и 321 соответственно, сигналы с выходов предыдущих регистров 30j, 31 j и 32j, где ,2,...,s-3 - номера регистров в группах регистров блока 26 регистров соответственно, сдвигаются на выходы следующих регистров 30j+i, 3.1 j+i и 32j+i соответственно. При этом, сигналы на выходах первой, второй и третьей групп выходов становятся равными сигналам, которые были на выходах регистров 305-з, 318-з и 325-з до поступления импульсного сигнала высокого уровня на тактовый вход блока 26 регистров. Блок 26 регистров может быть реализован и на базе, например ОЗУ.

Вычислитель 25 (см. фиг. 4, 14) работает следующим образом.

При исходном состоянии блока 25 вычисления его блоки 28, 29 и 30 находятся в своих исходных состояниях соответственно (см. фиг. 4, 6, 7, 8, 14). При этом, на первой, второй и третьей группах информационных -входов блока 25 вычисления сформированы

,;

10

15

20

25

30

35

40

45

50

55

сигналы, соответствующие двоичным представлениям числа, соответственно, один и

- bi + 1, на выходах переключение, изменение блока 29 смещения и на выходе плюс блока 30 контроля сформированы сигналы низких уровней, а на первых группах информационных входов модуля 28 адреса и блока 30 сформированы сигналы, соответствующие двоичному представлению числа один. По переднему фронту импульсного сигнала высокого уровня, поступающего на тактовый вход блока 25 вычисления, а значит, и на тактовые входы блоков 29 и 30. сигналы со входом второй и третьей групп информационных входов блока 25 вычисления передаются на одноименные выходы его второй и третьей групп информационных выходов соответственно (см. фиг. 4, 7, 8). При этом, на выходе изменение блока 29, а значит и на входах изменение блоков 28 и 30, формируется импульсный сигнал высокого уровня. По переднему фронту импульсного сигнала высокого уровня, поступающего на вход изменение блока 28, на выходах первой группы информационных выходов блока 25 вычисления формируются сигналы, соответствующие двоичному представлению сумм, соответствующих сигналам на входах первой и второй групп информационных входов блока 28 (см. фиг. 4,6). По переднему фронту импульсного сигнала, поступающего на вход изменение блока 30 (см. фиг. 4, 8), сигналы на выходах счетчика 48 по сигналу на его тактовом входе станут равняться сигналам на входах принудительной установки счетчика 48, а через время, определяемое параметрами второго элемента 51 задержки модуля 30 контроля, состояние счетчика 48 блока 30 увеличится на единицу. Значит, сигналы на выходах третьей группы информационных выходов вычислителя 25 после подачи на его тактовый вход импульсного сигнала высокого уровня станут соответствовать двоичному представлению числа, равному числу, соответствующему сигналам на входах третьей группы информационных входов вычислителя 25, увеличенного на единицу. При этом, если число, соответствующее сигналам на выходах третьей группы информационных выходов вычислителя 25, станет равняться числу S, то на выходе плюс блока 30, а значит, на выходе плюс блока 29, формируется импульсный сигнал высокого уровня по переднему фронту которого состояние счетчика 39 блока 29 (см. фиг. 4, 7) увеличивается на единицу, а сиг налы на выходах второй группы информационных выходов вычислителя 25 вычисления

станут соответствовать двоичному представлению числа, равному числу, соответствующему сигналам на входах второй группы информационных входов вычислителя 25, увеличенного на единицу. Если число, соот- ветствующее сигналам на выходах второй группы информационных выходов вычислителя 25, станет равняться S, то сначала на выходе переключение, а затем на выходе изменение блока 29 сформируются им- пульсные сигналы высоких уровней.

При этом, по переднему фронту импульсного сигнала высокого уровня, сформированного на выходе изменение блока 29, а значит и на входах изменение блоков 28 и 30 при сигнале высокого уровня, сформированного на выходе переключение блока 29 смешения, а значит и на входах переключение блоков 28 и 30, на выходах первой и третьей групп информационных выходов вычислителя 25 сформируются сигналы, равные сигналам на выходах преобразователей 34 блоков 28 (см. фиг. 4, 6) и 43 блока 30 (см. фиг. 4, 8) соответственно, которые в свою очередь однозначно зависят от сигна- лов на входах первых групп информационных входов блоков 28 и 30 соответственно, а значит, на входах первой и третьей групп информационных выходов блока 29 соответственно.

Кроме того, по переднему фронту импульсного сигнала, поступающего на тактовый вход блока 29 (см. фиг. 4, 7), на выходах первой группы информационных выходов блока 29 формируются сигналы, соответст- вующие двоичному представлению чиСла, соответствующему сигналам на выходах первой группы информационных выходов блока 29 до подачи очередного импульсного сигнала на его тактовый вход, увеличенного на единицу.

Сигналы на выходах первой группы информационных выходов блока 29 будут соответствовать двоичным представлениям чисел от 1 до S включительно, но состояние сигналов, соответствующих числу S, неустойчиво и они заменяются сигналами, соответствующими числу единица.

Для надежной и правильной работы вычислителя 25 параметры элемента 45 задер- жки блока 29 (см. фиг. 4, 7, 14) и параметры первого элемента 50 задержки блока 30 (см. фиг. 4, 8, 14) должны обеспечить формирование переднего фронта импульсного сигнала высокого уровня на втором входе элемента ИЛИ 44 блока 29 (см. фиг. 4. 7, 14), а значит и на тактовом вход его второго счетчика 39 по переднему фронту сигнала на выходе переключение блока 29 после формирования импульсного сигнала высокого

уровня на втором входе второго элемента ИЛИ 53 блока 30 (см. фиг. 4, 8. 14) по сигналу на его выходе плюс.

Следовательно, величина задержки изменения уровня сигнала на элементе 45 задержки блока 29 (см. фиг. 7,14) должна быть несколько больше за величину задержки изменения уровня сигнала на первом элементе 50 задержки блока 30 (см. фиг. 8, 14).

Блок 2 (см. фиг. 3) работает следующим образом.

В исходном состоянии блока 2 вычисления адреса его вычислитель 25 и блок 26 (см. фиг. 3. 4, 5, 6, 7, 8, 14) находятся в своих исходных состояниях, а регистр 27 сброшен в нулевое состояние. При этом, на тактовый вход и на вход 6 подтверждение приема блока 2 вычисления адреса подаются сигналы низких уровней.

По переднему фронту сигнала высокого уровня, поступающего на тактовый вход блока 2, на выходах регистра 27, а значит и на выходах блока 2, формируются сигналы, равные сигналам на выходах первой группы информационных выходов блока 26 регистров (происходит изменение адреса обращения к блоку 3 памяти),

Импульсный сигнал высокого уровня, поступающий на вход 6 подтверждение приема блока 2 вычисления адреса, а значит и на вход формирователя 24, вызывает формирование на выходе формирователя 24 импульсов, а значит и на тактовых входах вычислителя 25 и 26 регистров, короткого импульсного сигнала высокого уровня. Параметры формирователя 24 импульсов должны быть выбраны такими, чтобы обеспечивалось Формирование на выходе формирователя 24 импульсного сигнала минимальной длительности, достаточной для устойчивой работы всех функциональных и логических элементов блока 2 (изменения состояния регистра и счетчиков, а также переключение логических элементов).

По переднему фронту импульсного сигнала высокого уровня, поступающего на тактовые входы вычислителя 25 вычисления и блока 26 регистров, в вычислителе 25 происходит процесс формирования соответствующих логике работы вычислителя 25 сигналов на выходах его первой, второй и третьей групп информационных выходов, а в блоке 26 регистров происходит сдвиг вправо хранящихся в блоке 26 регистров сигналов в соответствии с логикой работы блока 26 регистров (см. описание принципа работы блока 26 регистров и фиг. 5).

Таким образом, в блоке 2 разделены во времени процессы формирования сигналов на выходах блока 2 соответствующих адресу

обращения к блоку 3 и формирования сигналов, соответствующих следующим адреса обращения к блоку 3, что увеличивает быстродействие блока 2.

Устройство нелинейного перемежения данных работает следующим образом. .

В исходном состоянии устройства нелинейного перемежения данных на его входы 5 подтверждение выдачи и 6 подтверждение приема подаются сигналы низких уров- ней, блок и 1 управления и 2 вычисления адреса находятся в своих исходных состояниях, в блоке 3 памяти по всем адресам от нудя до V -1 включительно хранятся либо произвольные данные, либо данные, значе- ния которых определяются устройствами- приемниками деперемежения данных, например, нули, а значения уровней сигналов на шине 4 данных не определяются и могут бьггь произвольными.

При этом, на выходах 7 готов выдать, 9 готов занести и 10 занесение устройства нелинейного деперемежения данных сформированы сигналы низких уровней, а на выходе 8 готов принять устройства - сформирован сигнал высокого уровня. Кроме того, в исходном состоянии устройства нелинейного деперемежения данных, на выходах блока 2 вычисления адреса и.на выходе чтение/запись блока 1 управления сформированы сигналы низких уровней, а на выходе хранение блока 1 управления - сформирован сигнал высокого уровня. Наличие укэзанн ./й комбинации уровней сигналов на выхгдах устройства нелинейного перемежения данных указывает внешним устройства -приемникам перемежения данных на TJ, что устройство нелинейного деперемежения данных не готово к выдаче им очередного данного по шине данных, а устройствам - источникам данных - указывает на то, что устройство нелинейного перемежения данных готово принять очередные данные по шине 4 данных на деперемежение. При этом, по сигналу высо- кого уровня на выходе хранение блока 1 управления блока 3 памяти находится в режиме хранения данных.

Начало работы устройства нелинейного перемежения данных инициирует внешнее устройство- источник данных путем формирования сигналов на шине 4 данных, соответствующих значению первого данного, подающегося на деперемежение, а затем подачей импульсного сигнала высокого уровня на вход 5 подтверждение выдачи устройства нелинейного перемежения дан- . ных.

Длительность импульсного сигнала высокого уровня ня входе 5 подтверждение

выдачи устройства нелинейного перемежения данных должна быть не меньше минимального необходимого времени для записи данного в блок 3 памяти и определяется параметрами блока 3 памяти.

При этом на токовом выходе блока 1 управления формируется импульсный сигнал высокого уровня, а на выходе хранение блока 1 управления - формируется импульсный сигнал низкого уровня, по которому осуществляется запись данного в блок 3 памяти при сигнале низкого уровня на выходе чтение/запись блока 1 управления.

Кроме того, на выходе 8 готов принять устройства нелинейного деперемежения данных формируется сигнал низкого уровня. Одновременное наличие сигналов низких уровней на выходах 7 готов выдать и 8 готов принять устройства нелинейного деперемежения данных указывает внешним устройствам, что устройство нелинейного деперемежения данных занято своим внутренним циклом работы и не готово к обмену данными с внешними устройствами.

По окончании действия импульсного сигнала на входе 5 подтверждение выдачи устройства нелинейного перемежения данных происходит формирование сигналов высоких уровней на выходе 7 готов выдать устройства и на выходах чтение/запись и хранение блока 1 управления, а также на выходах блока 2 устанавливаются уровни сигналов, соответствующие адресу следующего обращения к блоку 3 памяти.

При этом устройство - источник данных должно освободить шину 4 данных.

Наличие сформированной комбинации уровней сигналов на выходах устройства нелинейного деперемежения данных указывает внешним устройствам на то, что устройство нелинейного деперемежения данных готово выдать им очередное пере- межение данное, а внешним устройствам - источникам данных - указывает на то, что устройство нелинейного перемежения данных не готово принять от них очередное данное.

При этом в начале приема перемежения данных внешние устройства - приемники перемеженных данных цолжны быть готовы примять не первое, а второе данное первого блока перемеженных данных. Значение первого данного должно быть сформировано самими устройствами - приемниками данных по такому же правилу, как и занесение на хранение данных в блок 3 памяти (ОЗУ) при его исходном состоянии, ибо первое данное, поступившее на вуод устройства нелинейного перемежения данных для

деперемежения не будет первым выходным перемеженным данным устройства. Такая логика работы устройства нелинейного пе- ремежения данных позволяет делать внешние устройства-приемники перемеженных данных не активными в случае отсутствия выдавливаемых для них перемеженных данных.

Для получения очередного перемеженного данного внешнее устройство-прием- ник перемеженных данных должно быть готово принять данное по шине 4 данных и выдать на вход 6 подтверждение приема устройства нелинейного перемежения данных импульсный сигнал высокого уровня длительностью, не меньшей минимально необходимой длительности сигналов на входах блока 3 памяти для осуществления считывания из него данного на шину 4 данных.

При поступлении импульсного сигнала высокого уровня на вход 6 подтверждение приема устройства нелинейного перемежения данных на выходе хранение блока 1 управления формируется импульсный сигнал низкого уровня, по которому при сигнале высокого уровня на выходе чтение/запись блока 1 управления происходит считывание очередного данного из блока 3 памяти по адресу, соответствующе- му сигналам на выходах блока 2, а на выходе 7 готов выдать устройства нелинейного перемежения данных - формируется сигнал низкого уровня. По окончании действия им- пульсного сигнала высокого уровня на вхо- де 6 подтверждение приема устройства нелинейного деперемежения данных на выходе 8 готов принять устройства формируется сигнал высокого уровня, а на выходе чтение/запись блока 1 управления - сиг- нал низкого уровня.

При этом устройство нелинейного перемежения данных становится готовым к приему следующего данного для деперемежения от внешних устройство-источников данных.

По такой логике работы устройство нелинейного перемежения данных принимает данные на перемежение и выдает перемеженные данные по шине 4 данных до тех пор, пока не закончит прием очередного (S-1)-ro данного в текущем блоке данных.

По окончании приема устройством нелинейного перемежения данных (S-1)-ro данного по (S-1)-y импульсному сигналу, поступающему на вход 5 подтверждение выдачи устройства нелинейного перемежения данных, происходит формирование сигналов высокого уровня на выходах 8 готов принять и 9 готов занести устройства нелинейного перемежения данных, указывающих внешним устройствам - источникам данных на то, что устройство нелинейного деперемежения данных готово принять от них очередное, S-e данное в текущем блоке данных кода, а устройствам - приемникам перемеженных данных - на то, что они должны быть готовы к принудительному приему данного по шине 4 данных, сопровождаемого импульсным сигналом высокого уровня на выходе 10 занесение устройства нелинейного перемежения денных (строб.).

Последнее S-e данное текущего блока данных кода передается по шине 4 данных от внешних устройств - источников данных по S-y по порядку счета импульсному сигналу высокого уровня, подающегося на вход 5 подтверждение выдачи устройства нелинейного перемежения данных, на вход внешних устройств-приемников перемеженных данных по сформированному в блоке 1 управления импульсного сигнала высокого уровня на выходе 10 занесение устройства нелинейного перемежения данных, совпадающего по времени с импульсным сигналом высокого уровня, подающегося на вход 5 подтверждение выдачи устройства нелинейного перемежения данных.

По окончании S-ro по порядку счета импульсного сигнала высокого уровня, подающегося на вход 5 подтверждение выдачи устройства нелинейного перемежения данных, только на выходе 7 готов выдать устройства нелинейного деперемежения данных формируется сигнал высокого уровня и устройство становится готовым выдать очередное деперемеженное данное внешним устройствам-приемникам перемеженных данных, причем это данное будет первым данным следующего очередного текущего деперемеженного выходного блока данных кода.

В дальнейшем логика работы устройства нелинейного перемежения данных будет повторяться, i

Импульсный сигнал высокого уровня на выходе 10 занесение устройства нелинейного перемежения данных может указывать внешним устройствам на то, что по шине 4 данных передается последнее данное текущего блока данных кода. В данном описании принципа действия устройства нелинейного перемежения данных счет импульсных сигналов, поступающих на вход 5 подтверждение выдачи устройства производится от единицы до S включительно, затем счет опять повторяется с единицы (см. фиг. 10).

После поступления на вход 6 подтверждение выдачи устройства нелинейного перемежения данных определенного количества импульсов устройство нелинейного перемежения данных переходит в свое ис- ходное состояние и работа устройства повторяется.

Значит, работа устройства нелинейного перемежения данных носит периодический характер, может продолжаться сколь угодно длительно, а исходным состоянием устройства может быть выбрано его любое разрешенное устойчивое состояние.

Выше описанная логика работы устройства нелинейного перемежения данных обеспечивает расширение функциональных возможностей за счет осуществления им функции перемежения данных путем обеспечения произвольных, необязательно одинаковых, разностей задержек каждых предыдущих и следующих за ними данных в блоках данных кода. Этим .обеспечивается цель изобретения.

Формула изобрете-имя

подсоединены к первым информационным входам управляемого ключа, вторые информационные входы которого подсоединены к выходам сумматора, вторые информационные входы которого являют- ся вторыми информационными входами блока вычисления адреса, третий вход которого соединен с управляющим входом управляемого ключа, выходы которого подключены к информационным входам ре- гистра, выходы которого являются информационными выходами блока вычисления адреса, тактовый вход регистра является четвертым входом блока вычисления адреса.

адреса, выход первого элемента И подключен к входу установки в 1 первого двоичного счетчика, выход элемента задержки соединен со вторым входом элемента ИЛИ, выход которого подключен к входу разрешения принудительной установки второго двоичного счетчика и является пятым выходом блока подсчета приращения адреса, счетный вход второго двоичного счетчика является третьим входом блока подсчета приращения адреса.

01

Bl

LZ

Si

91

hi

02

-ч

ь

Ј L

i

e-i

OZ99181

ЈZ

г г

б/

ter

i/

.

L гпф

Л

25

26

J

Фиг.З

фиг.

28

у

Р

F

2ГП

J6

J7

rtJ

Фиг.6

Г

чо,

39

frj,--Щ.

Фиг.7

L

Фие.8

29

JA

«,

1

30

о t-«D

ю со

фг/2.77

ж

iftue.lZ i гs-i s

1

Фиг. 13

Фие. 74130

П U

П

i

w S

П

l

u ;

Фиг.15

| Девеза Г.Д.,, Коган A.M., Подобед В.В | |||

| Об одном подходе к реализации устройств перемещения цифровой информации в звукозаписи (Сер.Техника средств связи | |||

| Вып.З, 1984, с.83, рис.3 | |||

| Устройство для декодирования слов данных,передаваемых по каналу передачи данных и поблочно защищенных посредством корректирующего кода (его варианты) | 1981 |

|

SU1271382A3 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1993-05-15—Публикация

1990-06-15—Подача