Изобретение относится к вычисли - тельной технике и может быть использовано в многоканальных системах управления и обработки информации.

Цель изобретения - повьииение про- изводительности устройства.

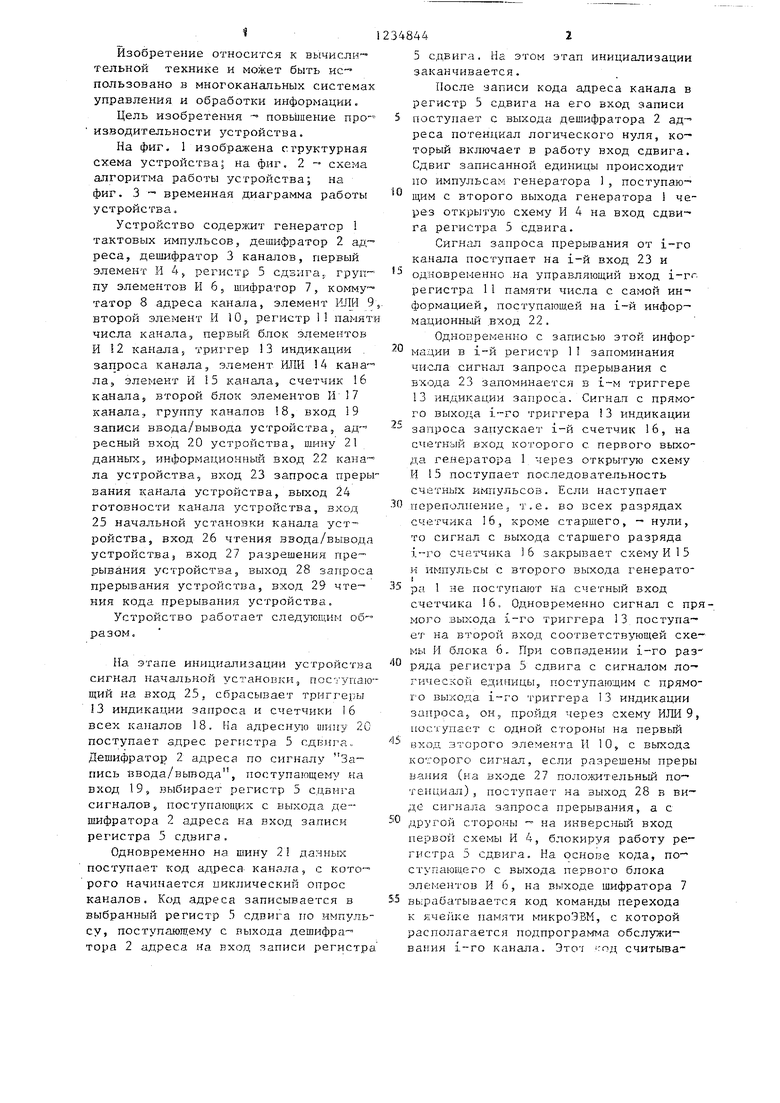

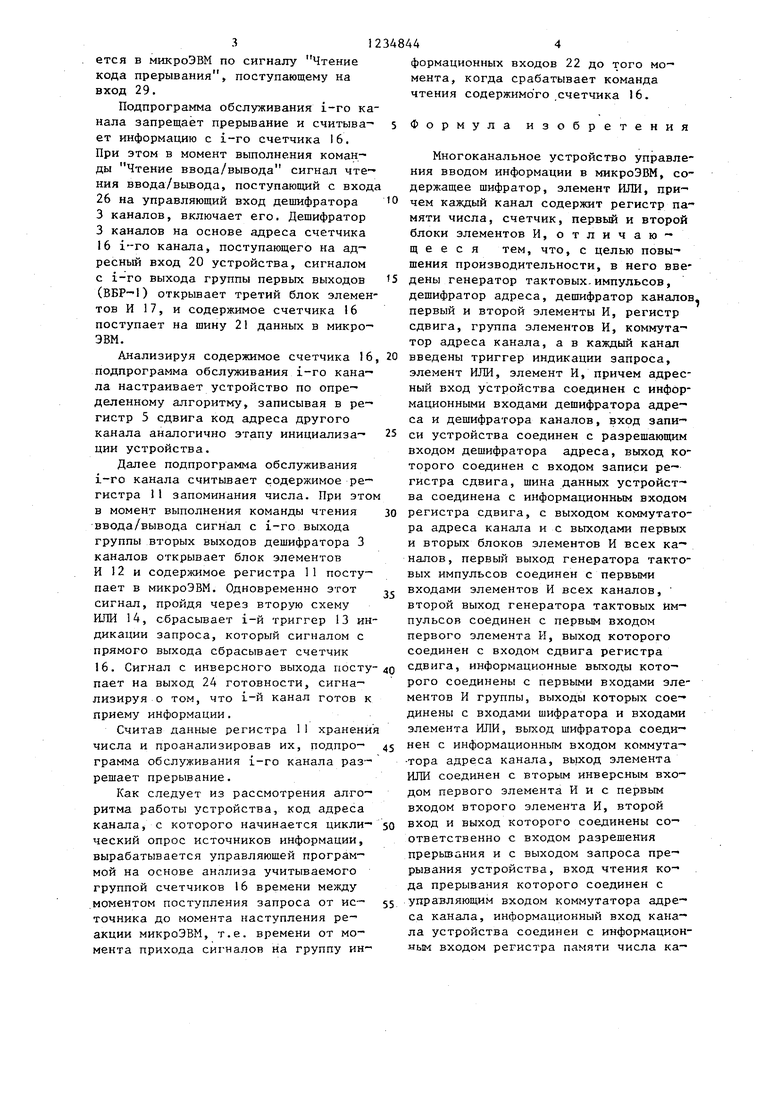

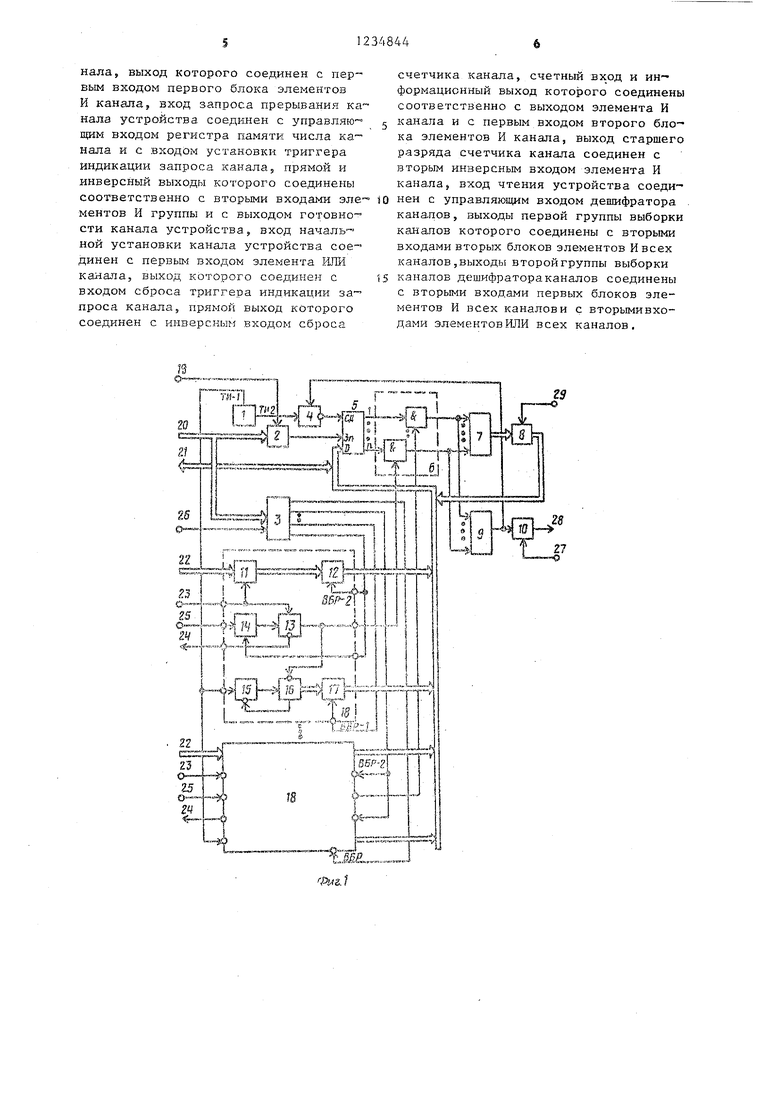

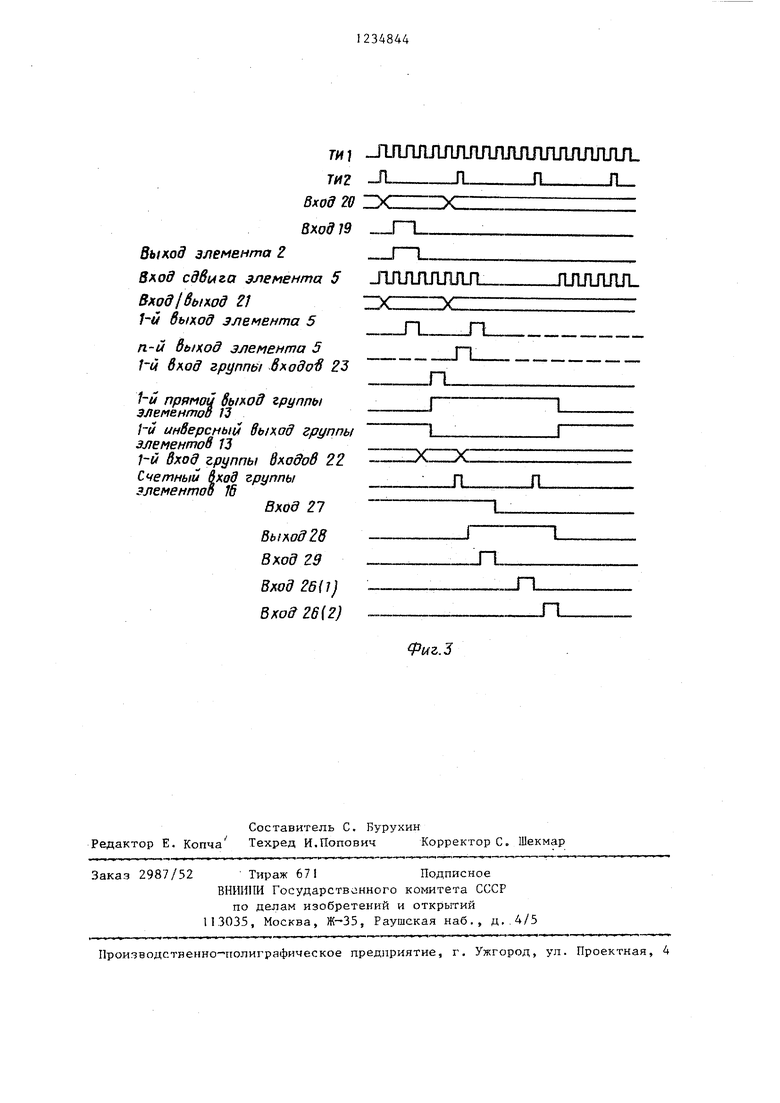

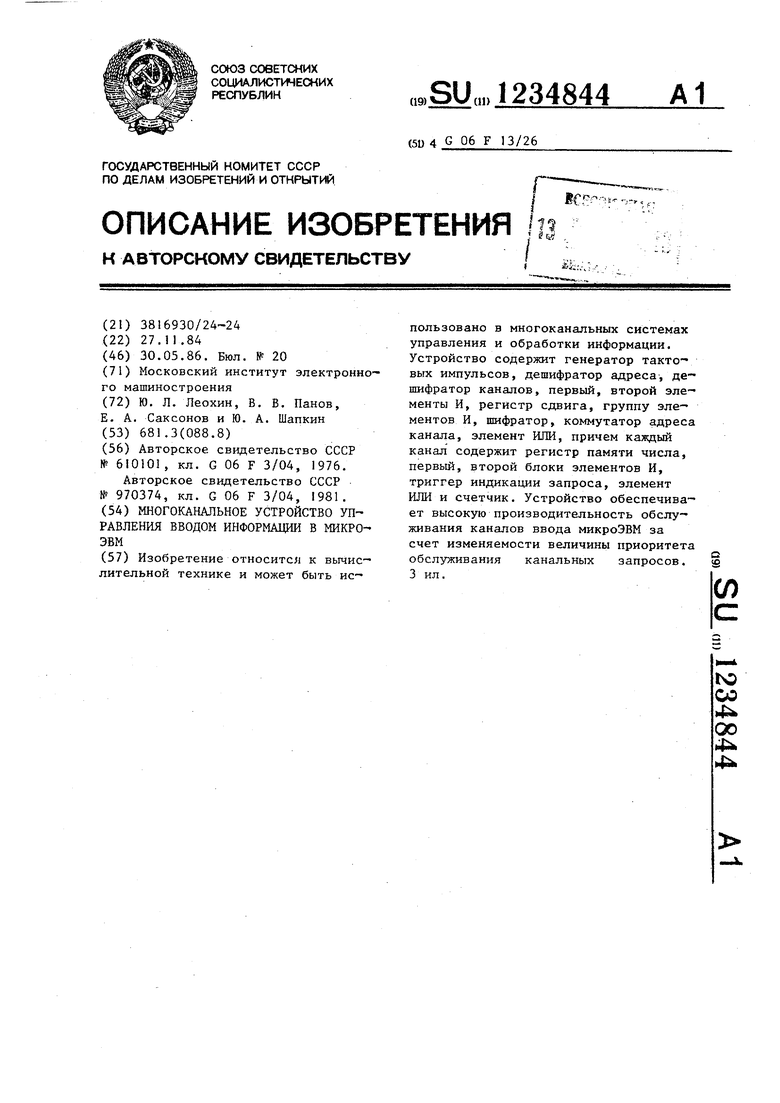

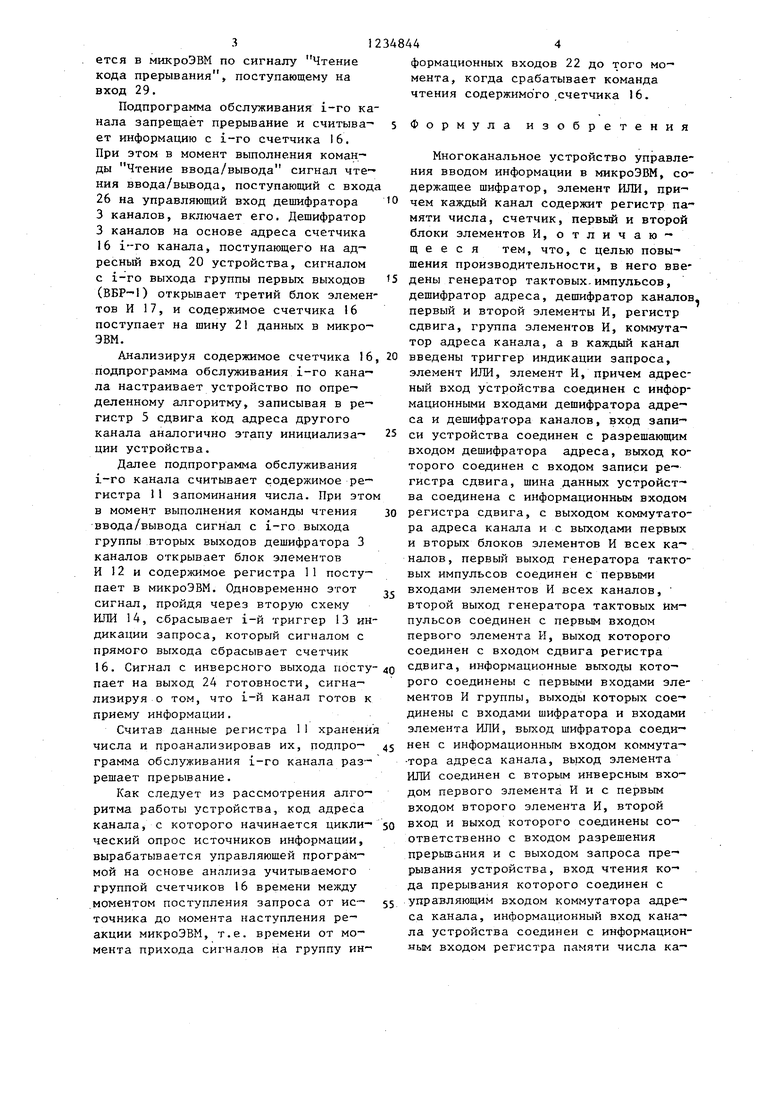

На фиг, 1 изображена структурная схема устройства; на фиг. 2 - схема алгоритма работы устройства; на фиг. 3 - временная диаграмма работы устройства.

Устройство содержит генератор тактовых импульсов, дешифратор 2 адреса, дешифратор 3 каналов, первый элемент И 4 регистр 5 сдвига, группу элементов И 6, шифратор 7, коммутатор 8 адреса канала, элемент ШШ 9 второй элемент И 10, регистр 1 памяти числа канала, первый блок элементов И 12 канала, триггер 3 индикации . запроса канала, элемент Ш1И 14 кана - ла, элемент И 15 канала, счетчик 16 канала, второй блок элементов И 17 канала, группу каналов 18, вход 19 записи ввода/вывода устройства, ресный вход 20 устройства, шииу 21 данньге, информационный вход 22 кана- ла устройства, вход 23 запроса прерывания канала устройства, выход 24 готовности канала устройства, вход 25 начальной установки канала устройства, вход 26 чтения ввода/вывода устройства, вход 27 разрешения прерывания устройства, выход 28 запроса прерывания устройства, вход 29 чте- НИН кода прерывания устройства.

Устройство работает следуюацин об- разом.

На этапе инициализации устройства сигнал начальной установки, поступающий на вход 25, сбрасывает тригге);-ы 13 индикации запроса и счетчики 16 всех каналов 18. На адресн ло инлгу 20 поступает адрес регистра 5 сдвига., Дешифратор 2 адреса по сигналу Запись ввода/вьтода, поступающему ка вход 19, выбирает регистр 5 сдвига сигналов, поступаюи т( с выхода дешифратора 2 адреса на вход записи регистра 5 сдвига.

Одновременно на шину 2 i данных поступает код адреса канала, с кото-- рого начинается циклический опрос каналов. Код адреса записывается в выбранный регистр 5 сдвига по импульсу, поступающему с выхода дешифра- тора 2 адреса на вход записи регистра

34844г

5 сдвига. НЕ этом этап инициализации заканчивается.

После записи кода адреса канала в регистр 5 сдвига на его вход записи 5 поступает с выхода дешифратора 2 ад- реса потенциал логического нуля, который включает в работу вход сдвига. Сдвиг записанной единицы происходит по импульсам генератора 1, поступаю- щим с второго выхода генератора 1 через открытую схему И 4 на вход сдви- га регистра 5 сдвига.

Сигн;1л запроса прерывания от i-ro канала поступает на i-й вход 23 и

5

одновременно на управляющий вход i-rc

регистра 1I памяти числа с самой информацией, поступающей на L-Й инфор- мационный вход 22.

Одновременко с записью этой информадии в i-й регистр 11 запоминания числа сигнал запроса прерывания с входа 23 запоминается в триггере 13 индикации запроса. Сигнал с прямого выхода i-ro триггера 3 индикации

запроса запускает i-й счетчик 16, на счетный вход которого с первого выхода генератора 1 через открытую схему И 15 поступает последовательность счетньгх импульсов. Если наступает

переполнение,, т.е. во всех разрядах счетчика 16, кроме cTapEiero, - нули, то сигнал с выхода старшего разряда i-ro счетчика 16 закрывает схему И 15

и импульсы с второго выхода генерато- i , pa 1 не поступают на счетный вход

счетчика &. Одновременно сигнал с пря- мо-го выхода i-ro триггера 13 поступает на второй вход соответствующей схемы И блока 6. При совпадении i-ro раз-

ряда регистра 5 сдвига с сигналом логической едгп-пщы, поступающим с прямо- г о выхода i-ro триггера 13 индикации запроса; он, пройдя через схему ИЛИ 9, 11оступа€ Т с одной стороны на первьй

вход 3-i oporo элемента И 10, с выхода которого сигнал, если разрешены преры ваыия (на входе 27 поло;«ительный по- гепциш) , поступает на выход 28 в виде сигнала запроса прерывания, а с

другой стороны - на 15кверсньш вход первой схемы И 4, блокируя работу регистра 5 сдвига. На основе кода, по- ступающего с выхода первого блока элементов И 6, на шифратора 7

вырабатывается код команды перехода к ячейке памяти мнкроЭВМ, с которой располагается подпрограмма обслужи- i-ro канала. Этот од считьшается в микроэвм по сигналу Чтение кода прерывания, поступающему на вход 29.

Подпрограмма обслуживания i-ro канала запрещает прерывание и считыва ет информацию с i-ro счетчика 16, При этом в момент выполнения коман-- ды Чтение ввода/вывода сигнал чтения ввода/вьшода, поступающий с вход 26 на управляющий вход дешифратора 3 каналов, включает его. Дешифратор 3 каналов на основе адреса счетчика 16 i-ro канала, поступающего на адресный вход 20 устройства, сигналом с i-ro выхода группы первых выходов (ВБР-1) открывает третий блок элементов И 17, и содержимое счетчика 16 поступает на шину 21 данных в микро- ЭВМ,

Анализируя содержимое счетчика 16 подпрограмма обслуживания i-ro канала настраивает устройство по определенному алгоритму, записывая в регистр 5 сдвига код адреса другого канала аналогично этапу инициализа- ции устройства.

Далее подпрограмма обслуживания i-ro канала считывает содержимое регистра 11 запоминания числа. При это в момент выполнения команды чтения ввода/вывода сигнал с i-ro выхода группы вторых выходов дешифратора 3 каналов открывает блок элементов И 12 и содержимое регистра 11 поступает в микроэвм. Одновременно этот сигнал, пройдя через вторую схему ИЛИ 14, сбрасьшает i-й триггер 13 индикации запроса, который сигналом с прямого выхода сбрасывает счетчик 16. Сигнал с инверсного выхода посту пает на выход 24 готовности, сигнализируя о том, что i-й канал готов к приему информации.

Считав данные регистра 11 хранени числа и проанализировав их, подпро- грамма обслуживания i-ro канала разрешает прерывание.

Как следует из рассмотрения алгоритма работы устройства, код адреса канала, с которого начинается цикли- ческий опрос источников информации, вырабатывается управляющей программой на основе анализа учитываемого группой счетчиков 16 времени между моментом поступления запроса от ис- точника до момента наступления реакции микроэвм, т.е. времени от момента прихода сигналов на группу ин

5 О 5

0 5

О

5

о 5

формационных входов 22 до того момента, когда срабатывает команда чтения содержимого счетчика 16.

Формула изобретения

Многоканальное устройство управления вводом информации в микроЭВМ, содержащее шифратор, элемент ИЛИ, причем каждый канал содержит регистр памяти числа, счетчик, первый и второй блоки элементов И, отличающее с я тем, что, с целью повышения производительности, в него вве дены генератор тактовых.импульсов, дешифратор адреса, дешифратор каналов. первый и второй элементы И, регистр сдвига, группа элементов И, коммутатор адреса канала, а в каждый канал введены триггер индикации запроса, элемент ИЛИ, элемент И, причем адресный вход устройства соединен с информационными входами дещифратора адреса и дешифратора каналов, вход записи устройства соединен с разрешающим входом дешифратора адреса, выход которого соединен с входом записи регистра сдвига, шина данных устройства соединена с информационным входом регистра сдвига, с выходом коммутатора адреса канала и с выходами первых и вторых блоков элементов И всех каналов, первый выход генератора тактовых импульсов соединен с первыми входами элементов И всех каналов, второй выход генератора тактовых Импульсов соединен с первым входом первого элемента И, выход которого соединен с входом сдвига регистра сдвига, информационные выходы которого соединены с первыми входами элементов И группы, выходы которых соединены с входами шифратора и входами элемента ИЛИ, выход шифратора соединен с информационным входом коммута- тора адреса канала, выход элемента ИЛИ соединен с вторым инверсным входом первого элемента И и с первым входом второго элемента И, второй вход и выход которого соединены соответственно с входом разрешения прерьшания и с выходом запроса прерывания устройства, вход чтения кода прерывания которого соединен с управляющим входом коммутатора адреса канала, информационный вход канала устройства соединен с информационным входом регистра памяти числа канала, выход которого соединен с первым входом первого блока элементов И канала, вход запроса прерывания ка нала устройства соединен с управляю- щим входом регистра памяти числа ка- Нала и с входом установки триггера индикации запроса канала, прямой и инверсный выходы которого соединены соответственно с вторыми входа ш элементов И группы и с выходом готовно сти канала устройства, вход начальной установки канала устройства сое- динен с первым входом элемента ИЛИ канала, выход которого соединен с входом сброса триггера индикации за- проса канала, прямой выход которого соединен с инверсным входом сброса

счетчика канала, счетный и информационный выход которого соединены соответственно с выходом элемента И

канала и с первым входом второго блока элемвнтов И канала, выход старшего разряда счетчика канала соединен с вторым инверсным входом элемента И канала, вход чтения устройства соединен с управляющим входом дешифратора каналов, выходы первой группы выборки каналов которого соединены с вторыми входами вторых блоков элементов И всех каналов5выходы второйгруппы выборки

каналов дешифратора каналов соединены с вторыми входами первых блоков элементов И всех каналов и с вторымивхо- дами элементов ИЛИ всех каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования системы сбора данных | 1988 |

|

SU1534469A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

Изобретение относится к вычислительной технике и может быть использовано в многоканальных системах управления и обработки информации. Устройство содержит генератор такто вых импульсов, дешифратор адреса, дешифратор каналов, первый, второй элементы И, регистр сдвига, группу элементов И, шифратор, ко1 мутатор адреса канала, элемент ИЛИ, причем каждый канал содержит регистр памяти числа, первый, второй блоки элементов И, триггер индикации эапроса, элемент ИЛИ и счетчик. Устройство обеспечивает высокую производительность обслуживания каналов ввода микроЭВМ за счет изменяемости величины приоритета обслуживания канальных запросов. 3 ил. с (О (Л го со 4 00 0:;

L., ,,

J л п WJ , {

М..„.Н-,-И Г

ruijTzzr y

jj vn

I J™-- U™-6-i ui

«. |. - -™---., J V tTT gu r- mnimv-}n; TKi &vinvX j j

-- 1..,™.-,.

t,,,li J I i

it}

.,™-. ,„. I I

1 I

и„А4 Т

л J i

а

tt в

--

гз

Г-

zzr y

j

vU

0

fi

у

аааяа

Ю

JiS

11

L..I

PtfS.Z

ги JlfшяJшл.пля гш ллллялJL

7HZ -Л--АПП

SxodJdr L

Вь1мд элемента 2-I I,

Влод cdBiAza элемента 5ИПЛДПЙПП ПППППП

Вход1вымд У

выкод элемента 5г

п-й 6ы)(од элемента 5

Составитель С. Бурухин Редактор Е. Копча Техред И.Попович Корректоре. Шекмар

Заказ 2987/52 Тираж 671Подписное

ВНИНПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж- 35, Раушская наб., д., 4/5

Производстнеино-полиграфическое пред 1риятие, г, Ужгород, ул. Проектная, 4

IAZ.3

| Многоканальное устройство для приема информации | 1976 |

|

SU610101A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство приоритетного управления вводом информации в цифровую вычислительную машину | 1981 |

|

SU970374A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-11-27—Подача