Изобретение относится к вычислительной технике и может быть использовано при построении аналого-цифровых интегрирующих машин и специализированных процессов, предназначенных для решения систем дифференциальных уравнений.

Известно устройство для решения дифференциальных уравнений по неявной схеме переменных направлений, Содержащее матрицу размером KxL арифметических блоков, блок синхронизации. При работе устройства происходит аппаратная реализация неявной схемы переменных наг правлений Писмана-Ракфорда. Вычисление каждой итерации выполняется параллельно для всех значений в соответствующих арифметических блоках матрицы и сводится к решению системы алгебраических уравнений с трехдиагональной матрицей. Это устройство требует больших машинных затрат, обусловленных итерационной схемой вычисления функции. Кроме того, из-за структурных ограничений, обусловленных алгоритмом вычисления, это устройство не мо- жетопределять фундаментальную матрицу линейного дифференциального уравнения.

Известно устройство для решения систем линейных дифференциальных уравнений, содержащее п блоков памяти, п блоков сдвига, п сумматоров, п накапливающих сумматоров, блок управления, счетчик, группы элементов U, регистр, коммутатор, блок анализа, элемент ИЛИ, п кодирующих элементов. Устройство предназначено для решения систем линейных дифференциальных уравнений с постоянными коэффициенХ|

ю

Vsl

со

о

тами вида ,

У(0)У0,

где А и В - матрица и вектор коэффициентов соответственно.

На каждом шаге интегрирования в данном устройстве находится первое приближение к решению по интерполяционной формуле и, чтобы удовлетворить заданной точности, производится уточнение решения по интерполяционной формуле, причем остаток округления используется на следующей итерации вычислений по интерполяционной формуле.

Это устройство требует больших машинных затрат, обусловленных интерполя- ционной схемой вычисления, причем повышение точности вычислений требует еще больших машинных и временных затрат. Данное устройство в силу предложенного алгоритма вычислений не позволяет решать систему дифференциальных уравнений с переменными параметрами и находить фундаментальное решение системы уравнений.

Наиболее близким по технической сущности к изобретению является устройство для решения систем дифференциальных уравнений, содержащее три блока постоянной памяти, три блока памяти, два умножителя, сумматор, и синхрогенератор. Данное устройство осуществляет нахождение фундаментального решения системы уравнений с переменными коэффициентами.

Однако в силу предложенного итеративного алгоритма вычислений данное устройство требует больших вычислительных затрат. Кроме того, оно не позволяет решать неоднородную систему уравнений с переменными коэффициентами и формировать найденное решение в виде непрерывной функции времени.

Цель изобретения - расширение функциональных возможностей за счет решения неоднородной системы дифференциальных уравнений с переменными коэффициентами и формирования найденного решения в виде непрерывной функции времени.

Указанная цель достигается тем, что в устройство, содержащее первый, второй и третий блоки буферной памяти, первый и второй умножители, первый, второй и третий блоки памяти, первый сумматор и синхрогенератор, причем первый выход синхрогенератора подключен к входам считывания первого и второго блоков буферной памяти, входы начальной установки первого, второго и третьего блоков буферной памяти подключены соответственно к первому, второму и третьему информационным входам устройства, управляющий вход Синхрогенератора подключен к входу запуска устройства, второй выход синхрогенератора подключен ко входам считывания/установки первого, второго и третьего блоков памяти, вход обнуления которого соединен с входом начальной установки устройства,

входы начальной установки первого и второго блоков памяти соединены с четвертым и пятым информационными входами устройства соответственно, выход первого блока буферной памяти соединен с первым

0 информационным входом первого умножителя, выход первого сумматора соединен с информационным входом первого блока памяти, выход третьего блока буферной памяти соединен с первым информационным

5 входом первого сумматора, дополнительно введены генератор пилообразного напряжения, квадратор, третий и четвертый умножители, первый, второй и третий цифроаналоговые преобразователи, второй, третий, четвертый,

0 пятый и шестой сумматоры, счетчик, причем

. выход первого умножителя соединен со вторым информационным входом первого сумматора, третий информационный вход которого соединен с выходом второго умно5 жителя, первый информационный вход которого соединен с выходом второго блока буферной памяти, а второй информационный вход - с выходом первого блока памяти и с информационными входами первого

0 цифроаналогового преобразователя и второго блока памяти, выход которого соединен со вторым информационным входом первого умножителя и с информационными входами второго цифроаналогового преоб5 рэзователя и третьего блока памяти, выход которого соединен с информационным входом третьего цифроаналогового преобразователя, выход первого цифроаналогового преобразователя подключен к первым вхо0 дам второго третьего и четвертого сумматоров, выходы которых подключены соответственно к первым входам третьего, четвертого умножителей и пятого сумматора, выход которого является информацирн5 ным выходом устройства, выход второго цифроаналогового преобразователя подключен к вторым входам второго и четвертого сумматоров, третий вход которого соединен с третьим входом второго сумма0 тора, вторым входом третьего сумматора и выходом третьего цифроаналогового преобразователя, первый выход синхрогенератора подключен к первым управляющим входам первого и второго умножителей, вто5 рые управляющие входы которых соединены с выходом считывания третьего блока буферной памяти, с третьим выходом синхрогенератора и с первым управляющим входом первого сумматора, второй управляющий вход которого соединение вторым выходом синхрогенерзтора, четвертый выход которого соединен с. входом синхронизации генератора пилообразного напряжения и счетным входом счетчика, вход начальной установки которого соединен с входом Минус единица устройства, а выход является первым выходом канала времени устройства, выход генератора пилообразного напряжения соединен через квадратор с вторым входом третьего умножителя, выход которого соединен с вторым входом пятого сумматора, третий вход которого соединен с выходом четвертого умножителя, второй вход которого соединен с выходом генератора пилообразного напряжения и с первым входом шестого сумматора, второй вход и выход которого подключены соответственно к входу константы устройства и к второму выходу канала времени устройства..

Использование сплайн-аппроксммации решения системы дифференциальных уравнений позволяет найти глобальное приближенное решение, т.е. решение, определенное на всем отрезке.

Сущность изобретения состоит в том, что, в отличие от известного, в предлагаемом устройстве изменены связи между известными блоками, в результате чего осуществляется вычисление коэффициентов сплайна, и введены дополнительные блоки, в результате чего формируется мо- дель решения системы дифференциальных уравнений в виде непрерывной функции времени.

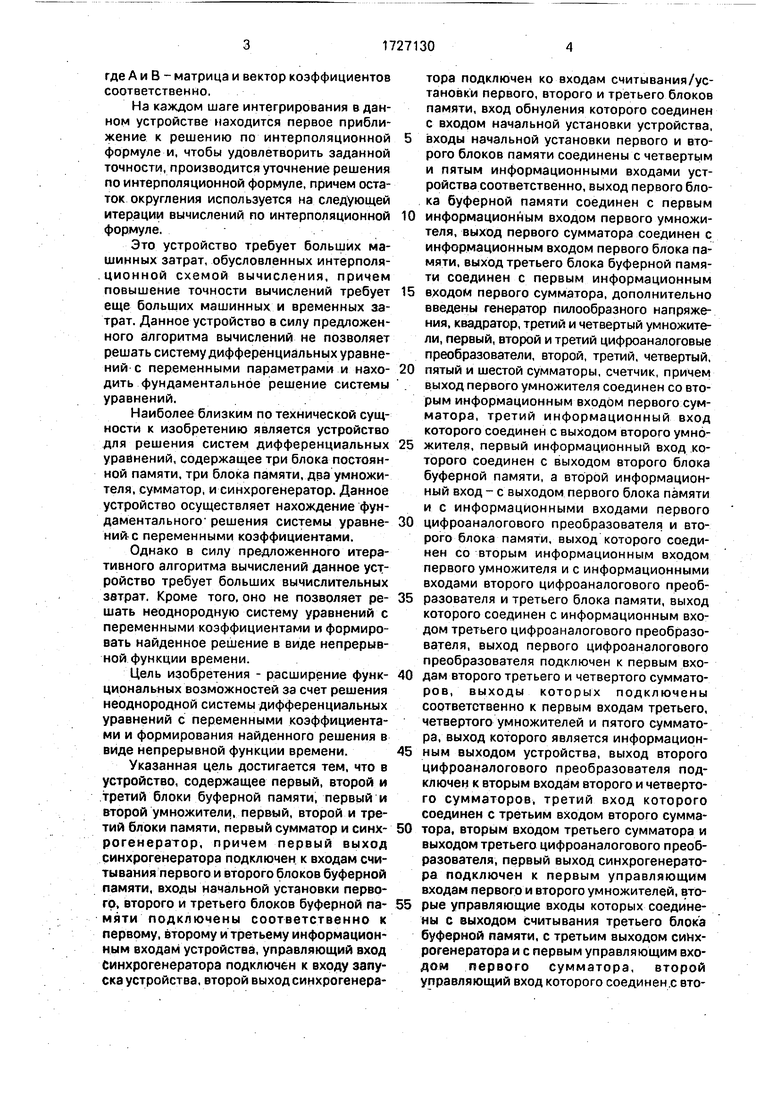

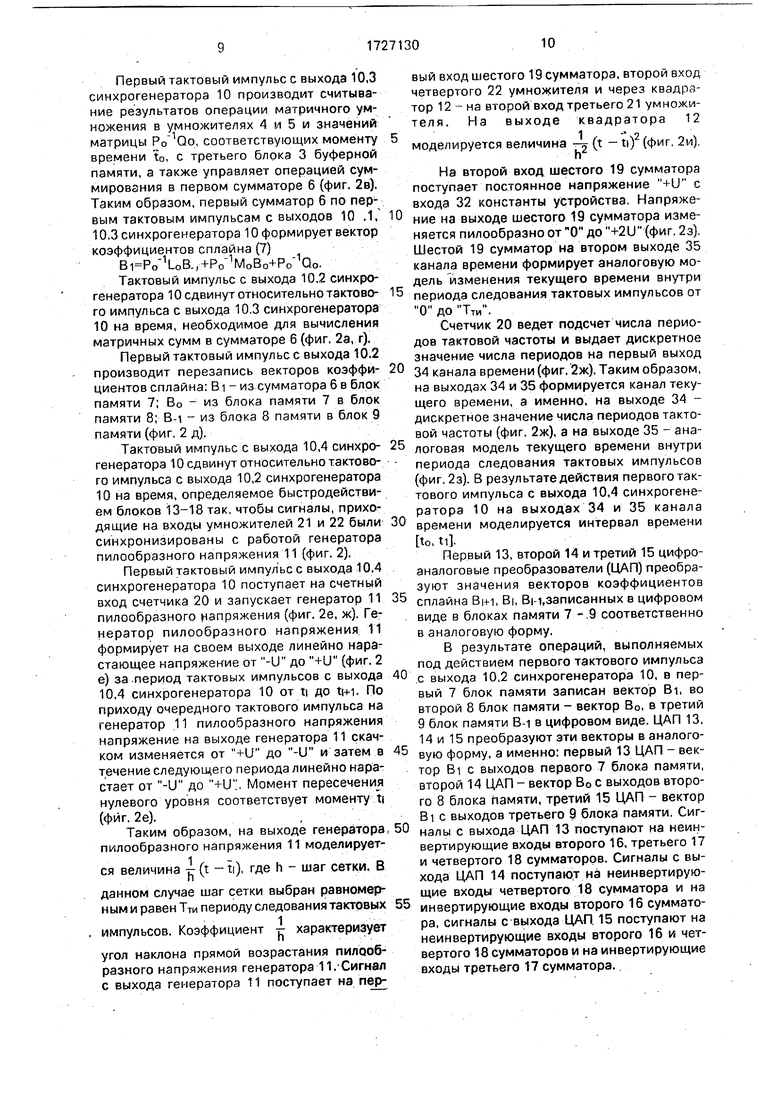

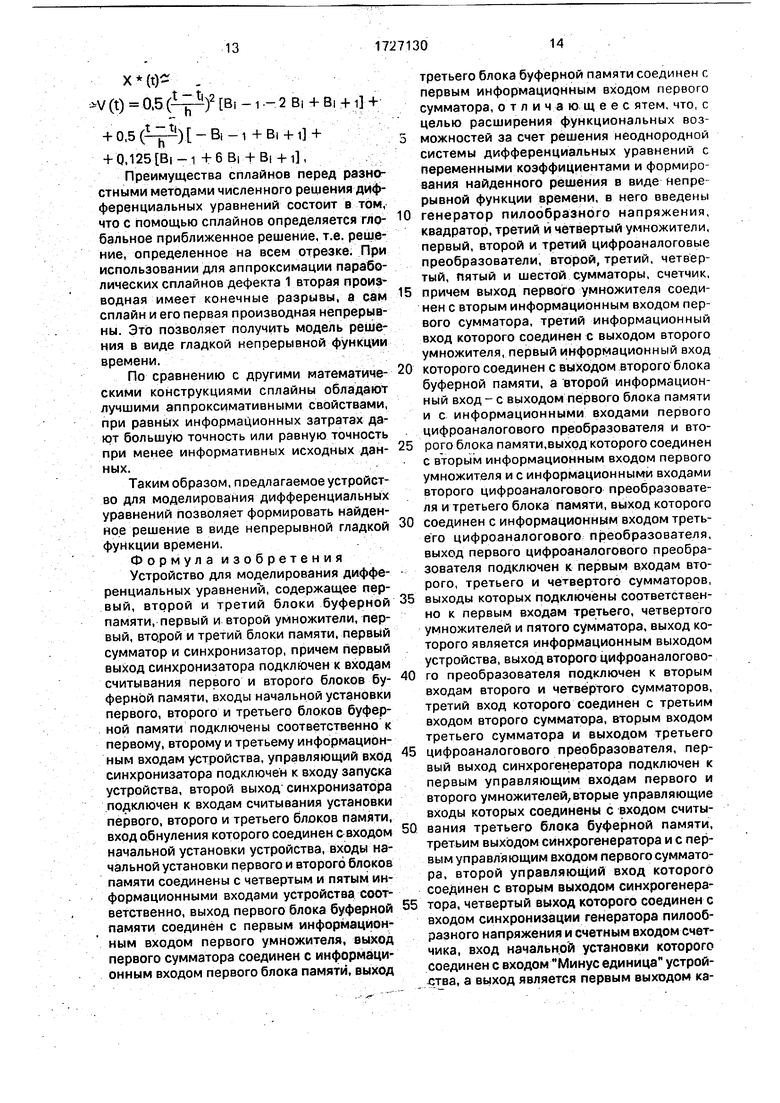

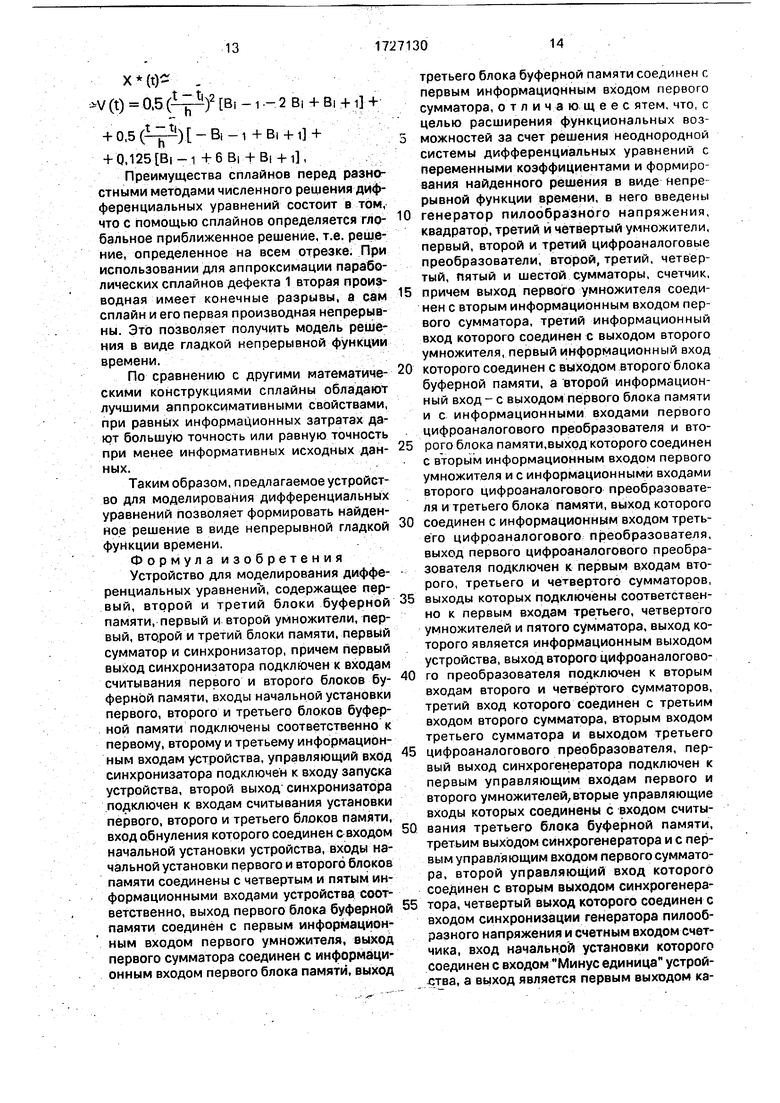

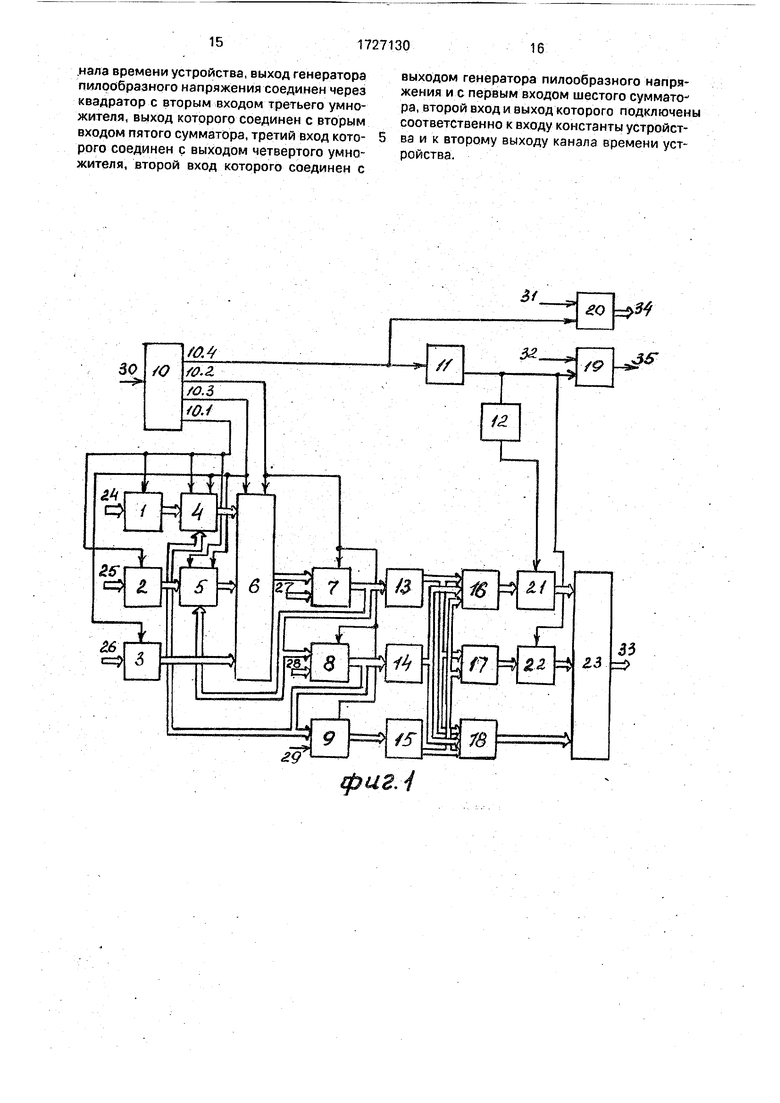

На фиг, 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит первый 1, второй 2 и третий 3 блоки буферной памяти, первый 4 и второй 5 умножители, первый 6 сумматор, первый 7, второй 8, третий 9 блоки памяти, синхрогенератор 10, генератор 11 пилообразного напряжения, квадратор 12, первый 13, второй 14 и третий 15 цифроана- логовые преобразователи, второй 16, третий 17, четвертый 18, пятый 2.3 и шестой 19 сумматоры, счетчик 20, третий 21 и четвертый 22 умножители, первый 24, второй 25, третий 26, четвертый 27 и пятый 28 информационные входы устройства, вход 29 начальной установки устройства, вход 30 запуска устройства, вход 3.1 Минус единица, вход 32 константы устройства, информационный выход 33 устройства, первый 34 и второй 35 выходы канала времени. Первый 10.1 выход синхрогенератора 10 подключен к входам считывания первого 1 и второго 2 блоков буферной памяти. Входы начальной

установки первого 1, второго 2 и третьего 3 блоков буферной памяти подключены соответственно к первому 24, второму 25 и третьему 26 информационным входам уст- 5 ройства. Управляющий вход синхрогенератора 10 подключен к входу запуска 30 устройства. Второй выход 10,2 синхрогенератора 10 подключен к входам считывания - установки первого 7, второго 8 и третьего

0 9 блоков памяти, вход обнуления которого соединен с входом 29 начальной установки устройства. Входы начальной установки первого 7 второго 8 блоков памяти соединены с четвертым 27 и пятым 28 информационными

5 входами устройства соответственно. Выход первого 1 блока буферной памяти соединен с первым информационным входом первого умножителя 4. Выход первого сумматора 6 соединен с информационным входом пер0 вого 7 блока памяти. Выход третьего блока 9 буферной памяти соединен с первым информационным входом первого сумматора 6. Выход первого умножителя 4 соединен с вторым информационным входом первого

5 сумматора 6, третий информационный вход второго соединен с выходом второго умножителя 5, первый информационный вход которого соединен с выходом второго 2 блока буферной памяти, а второй информацион0 ный вход - с выходом первого блока 7 памяти и с информационными входами первого дифроаналогового преобразователя 13 и второго блока 8 памяти, выход которого соединен с вторым информационным вхо5 дом первого 4 умножителя и с информационными входами второго цифроаналогового преобразователя 14 и третьего блока 9 памяти, выход которого соединен с информационным входом третьего цифроаналогового

0 преобразователя 15. Выход первого цифро- аналогового преобразователя 13 подключен . к первым входам второго 16, третьего 17 и четвертого 18 сумматоров, выходы которых подключены соответственно к первым вхо5 дам третьего 21, четвертого 22 умножителей и пятого 23 сумматора, выход которого является информационным выходом 33 устройства. Выход второго цифроаналогового преобразователя 14 подключен к вторым

0 входам второго 16 и четвертого сумматоров 18, третий вход которого соединен с третьим входом второго сумматора 16, вторым входом третьего сумматора 18 и выходам третьего цифроаналогового преобразовате5 ля 15, Первый выход 10.1 синхрогенератора 1.0 подключен, к первым управляющим входам первого 4 и второго 5 умножителей, вторые управляющие входы которых соединены с входом считывания третьего блока 3 буферной памяти, с третьим 10.3 выходом

синхрогенератора 10 и с первым управляющим входом первого сумматора 6, второй управляющий вход которого соединен с вторым выходом 10.2 синхрогенератора 10, четвертый выход 10.4 которого соединен с входом синхронизации генератора 11 пилообразного напряжения и счетным входом счетчика 20, вход начальной установки которого соединен с входом 31 Минус единица устройства, а выход является первым 34 выходом канала времени устройства. Выход генератора 11 пилообразного напряжения соединен через квадратор 12 с вторым вхо- . дом третьего умножителя 21, выход которого соединен с вторым входом пятого сумматора 23, третий вход которого соединен с выходом четвертого умножителя 22, второй вход которого соединен с выходом генератора 11 пилообразного напряжения и с первым входом шестого сумматора 19, второй вход и выход которого подключены соответственно к входу 32 константы устройства и к второму выходу 35 канала времени устройства.

Рассмотрим работу устройства на примере моделирования процесса системой дифференциальных уравнений

(t)X + Q(t)( X(to)Xa , (1)

где Д (t) и Q(t) - матрица и вектор переменных коэффициентов соответственно.

Используем аппроксимацию процесса параболическим нормализованным базисным вектор-сплайном размерности п

X(t)V(t),(2)

заданным на сетках узлов

A:t-j t-i ....

Aif-i t-i t0 ti ....(3)

элементы которых связаны соотношением

,-1.0, 1.2.... (4)

V(t) для интервала ti; ti+tj может быть представлен в виде

Vi(t) 0,5 fc)2 В| -1 - 2 В. + В, -и +

+ 0,5(V)-B

1+В| + 1 +

i+6Bi+Bi-H,

+ 0,125E&,-i+6Bi+Bi-H,(5)

где В|ТН;ЬЛ &2, bi3,:... вектор коэффициенте сгшбйна, h - шаг, сетки, h tn-i-ti.

Для ri разводной соответственно получим

Јv,(t) ()Bl-i-2Bi+B.+l +

,

1 + Bi+i.

Тогда для моментов времени , ,1, 2,... на основании (5) и (6) решение системы уравнений (1) может быть приведено к виду

BM Pf1LiBMH-Pf 1MiBi+ Pf1Qi.(7)

где Pi -gb E-hAft),(8)

U -НА (f.),(9)

МрО,75А(Г),№)

Е-единичная матрица.

Начальные условия для (7) формируются на основании начальных условий из (1). Уравнения для определения векторов В-ц и Во имеют вид из (1), (2), (5), (6)

В-1- Х0- 0, (to) Xo+Q (to),

Bo Xo+:0,(to)Xo+Q(t0).(11)

Моделирование процесса (1) осуществляется путем вычисления коэффициентов сплайна Bj и использования аппроксимации (2) на основе представления (5) с начальными условиями (11).

В исходном состоянии в первый 1, второй 2 и третий 3 блоки буферной памяти с первого 24, второго 25 и третьего 26 информационных входов устройства соответственно записаны значения матриц ,, в моменты времени тл, , 1,2,.... рас- считанные по формулам (8), (9), (10) и по заданным функциям времени A(t) и Q(t); в первый 7 и второй 8 блоки памяти с четвертого 27 и пятого 28 информационных входов устройства записаны соответств,енно значения коэффициентов Во и В-1, рассчитанные по формулам (11) по заданным начальным условиям Х0 и известным функциям A(t) и Q(t) при . Третий блок 9 памяти в исходном состоянии обнуляется сигналом с входа 29 начальной установки устройства, а в счетчик 20 записывается значение -1 с входа 31 Минус единица.

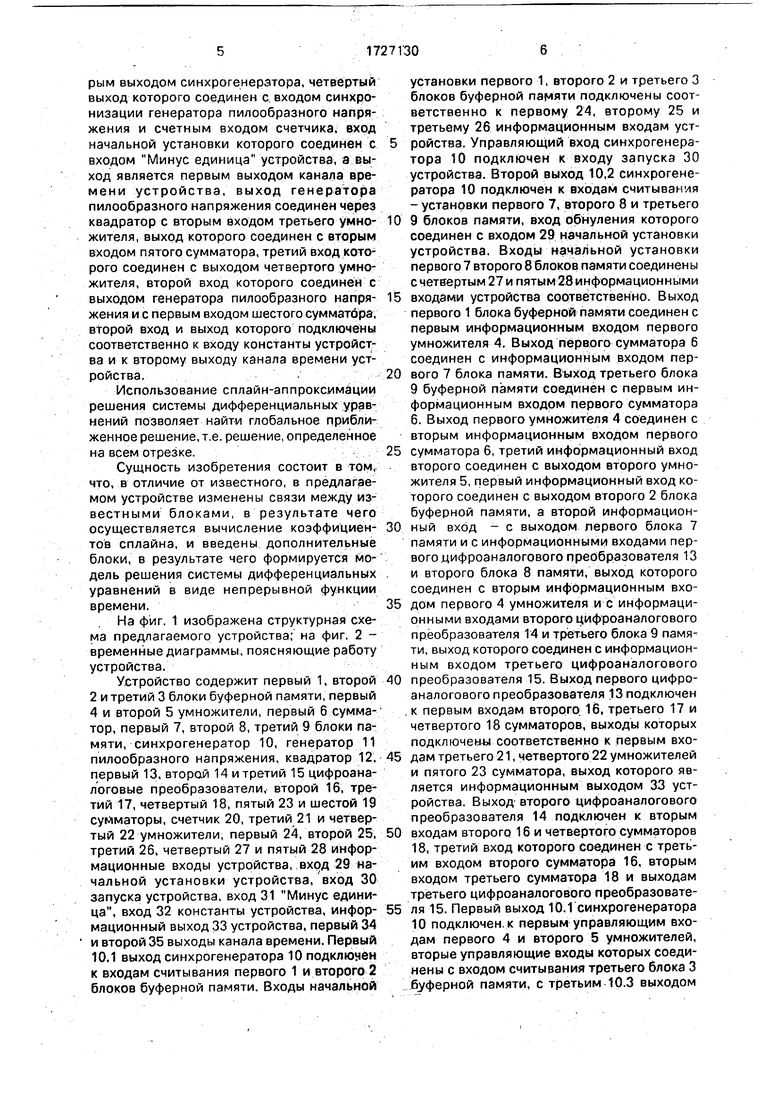

Запуск устройства осуществляется путем запуска синхрогенератора 10с входа 30 запуска. Синхрогенератор 10 на своих четырех выходах формирует четыре последовательности тактовых импульсов одинаковой частоты следования (фиг. 2 а), которые сдвинуты относительно друг друга на величины задержки, определяемые быстродействием решающих блоков. Первый тактовый импульс с выхода 10.1 синхрогенератора 10 производит считывание значений матриц и РО М0 соответственно с первого 1 50 и второго 2 блоков буферной памяти, соответствующие моменту времени to, и вычисление произведений Р0 в умножителе 4 и Ро 1М0Во в умножителе 5 (фиг. 26).

55 Тактовый импульс с выхода 10.3 синхрогенератора 10 сдвинут относительно тактового импульса с выхода 10,1 синхрогенератора 10 на время, необходимое для вычисления матричных произведений в умножителях 4 и 5(фиг.2а, в).

10

15

20

25

30

35

40

45

Первый тактовый импульс с выхода 10,3 синхрогенератора 10 производит считывание результатов операции матричного умножения в умножителях 4 и 5 и значений матрицы Ро Qo, соответствующих моменту времени to, с третьего блока 3 буферной памяти, а также управляет операцией суммирования в первом сумматоре 6 (фиг. 2в). Таким образом, первый сумматор 6 по первым тактовым импульсам с выходов 10 Л,

10.3синхрогенератора 10 формирует вектор коэффициентов сплайна (7)

.,+Po 1MoBo+Po 1Qo.

Тактовый импульс с выхода 10,2 синхрогенератора 10 сдвинут относительно тактово- го импульса с выхода 10.3 синхрогенератора 10 на время, необходимое для вычисления матричных сумм в сумматоре 6 (фиг. 2а, г).

Первый тактовый импульс с выхода 10.2 производит перезапись векторов коэффи- циентов сплайна: В1 - из сумматора 6 в блок памяти 7; В0 из блока памяти 7 в блок памяти 8; В-1 - из блока 8 памяти в блок 9 памяти (фиг. 2 д).

Тактовый импульс с выхода 10,4 синхро- генератора 10 сдвинут относительно т.актово- го импульса с выхода 10,2 синхрогенератора 10 на время, определяемое быстродействием блоков 13-18 так, чтобы сигналы, приходящие на входы умножителей 21 и 22 были синхронизированы с работой генератора пилообразного напряжения 11 (фиг. 2).

Первый тактовый импульсе выхода 10,4 синхрогенератора 10 поступает на счетный вход счетчика 20 и запускает генератор 11 пилообразного напряжения (фиг. 2е, ж). Генератор пилообразного напряжения 11 формирует на своем выходе линейно нарастающее напряжение от -U до +U (фиг. 2 е) за .период тактовых импульсов с выхода

10.4синхрогенератора 10 от ti до ti+i. По приходу очередного тактового импульса на генератор 11 пилообразного напряжения напряжение на выходе генератора 11 скачком изменяется от +U до -U и затем в течение следующего периода линейно нарастает от -U до -HJ. Момент пересечения нулевого уровня соответствует моменту ti (фиг. 2е).

Таким образом, на выходе генератора пилообразного напряжения 11 моделирует1 - ся величина т- (t - ti), где h - шаг сетки, В

данном случае шаг сетки выбран равномерными равен ТТи периоду следования тактовых

1

импульсов. Коэффициент т- характеризует

угол наклона прямой возрастания пилообразного напряжения генератора 11. Сигнал с выхода генератора 11 поступает на первый вход шестого 19 сумматора, второй вход четвертого 22 умножителя и через квадратор 12 - на второй вход третьего 21 умножителя. На выходе квадратора 12

моделируется величина -о (t - ti) (фиг. 2и),

На второй вход шестого 19 сумматора поступает постоянное напряжение +U с входа 32 константы устройства, Напряжение на выходе шестого 19 сумматора изменяется пилообразно от О до +2U (фиг. 2з). Шестой 19 сумматор на втором выходе 35 канала времени формирует аналоговую модель изменения текущего времени внутри периода следования тактовых импульсов от

О ДО Тти.

Счетчик 20 ведет подсчет числа периодов тактовой частоты и выдает дискретное значение числа периодов на первый выход 34 канала времени (фиг, 2ж). Таким образом, на выходах 34 и 35 формируется канал текущего времени, а именно, на выходе 34 - дискретное значение числа периодов тактовой частоты (фиг. 2ж), а на выходе 35 - аналоговая модель текущего времени внутри периода следования тактовых импульсов (фиг. 2з). В результате действия первого тактового импульса с выхода 10,4 синхрогенератора 10 на выходах 34 и 35 канала времени моделируется интервал времени to, ti.

Первый 13, второй 14 и третий 15 цифро- аналоговые преобразователи (ЦАП) преобразуют значения векторов коэффициентов сплайна Bi-и, BI, Вм.записанных в цифровом виде в блоках памяти 7 -.9 соответственно в аналоговую форму.

В результате операций, выполняемых под действием первого тактового импульса .с выхода 10,2 синхрогенератора 10, в первый 7 блок памяти записан вектор Вт, во второй 8 блок памяти - вектор В0, в третий 9 блок памяти В-1 в цифровом виде. ЦАП 13, 14 и 15 преобразуют эти векторы в аналоговую форму, а именно: первый 13 ЦАП - вектор BI с выходов первого 7 блока памяти, второй 14 ЦАП - вектор В0 с выходов второго 8 блока памяти, третий 15 ЦАП - вектор Вт с выходов третьего 9 блока памяти. Сигналы с выхода ЦАП 13 поступают на неинвертирующие входы второго 16, третьего 17 и четвертого 18 сумматоров. Сигналы с выхода ЦАП 14 поступают на неинвертирующие входы четвертого 18 сумматора и на инвертирующие входы второго 16 сумматора, сигналы с выхода ЦАП 15 поступают на неинвертирующие входы второго 16 и четвертого 18 сумматоров и на инвертирующие входы третьего 17 сумматора.

Второй 16 сумматор суммирует сигналы с выхода ЦАП 13 с коэффициентом К - с выхода ЦАП 14 - с коэффициентом с выхода ЦАП 15 - с коэффициентом -.

Третий 17 сумматор суммирует сигналы с

1 выхода ЦАП 13 - с коэффициентом К у: с

выхода ЦАП 15 - с коэффициентом К . Четвертый 18 сумматор суммирует сигналы

с выхода ЦАП 13 - с коэффициентом К

о

3

с выхода ЦАП 14 - с коэффициентом К --j ,

1

4

с выхода ЦАП 15 - с коэффициентом К -5-.

о

Таким образом, на первом такте работы второй 16, третий 17 и четвертый 18 сумматоры на своих выходах формируют в аналоговой форме следующие векторы: на выходе второго сумматора 16 ОДВ-1- 2B0+Bi ;,

на выходе третьего сумматора 17 0,

на выходе четвертого сумматора 18 0, +6B0+Bi.

Сигналы с выхода четвертого 18 сумматора поступают на первый вход пятого 23 сумматора. Сигналы с выхода третьего сумматора 17, умноженные в четвертом 22 ум1ножителе на величину т- (l - to) поступают

на третий вход пятого 23 сумматора.

Сигналы с выхода второго 16 сумматора, умноженные в третьем 21 умножителе на ве1

личину (t-t0) , поступают на второй вход

п

пятого 23 сумматора. В результате на пятый 23 сумматор формирует на информационном выходе 33 устройства вектор искомого процесса (1) согласно принятой аппроксимации (2), (5) для интервала времени t0; ti

X(t) V(t). 0,

В-1 - 2 Во + Bi + 0,5 ()

- В-ь + Bi + 0,125 B-v. + 6 Во + Bij.

Каждый (+1)-й тактовый импульс с выхо- да 10.1 синхрогенератора 10 считывает i-e значение матриц Pf U с первого блока памяти и со второго 2 блока буферной

. памяти, соответствующие моменту времени ti.M производит вычисление векторов РГ UBj-t

и Pi MiBi в умножителях 4 и 5 соответственно. В результате действия 0+1)-го тактового импульса с выхода 10.3 синхрогенератора 10 осуществляется считывание 1-х значений матрицы Pf1Qi в третьем 3 блоке буферной

памяти и вычисление вектора BI-H (7) в первом сумматоре 6. Под действием (i+1)-ro тактового импульса с выхода 10,2 синхрогенератора 10 осуществляется сдвиг значений векторов коэффициентов сплайна: Вм - из второго 8 блока памяти в третий 9; Bi - из первого 7 блока памяти во второй блок 8 памяти; Вн-1 - из первого 6 сумматора в первый 7 блок памяти. ЦАП 13-15 преобразуют значения векторов BI+I, Bi, Вы соответственно в аналоговую форму. Второй 16,. третий 17, четвертый 18 сумматоры после действия (i+1)-ro тактового импульса на своих выходах формируют в аналоговой форме следующие векторы: второй 16 сумматор 0,5 Ви-2В|+Ви-1 ; третий 17 сумматор 0,5 -Bi-i+Bi+i ; четвертый 18 сумматор 0,125 Вм+ 6Bj+ BI-M, которые поступают на первые входы третьего 21 и четвертого 22 умножителей и пятого 23 сумматора соответственно.

(1+1)-й тактовый импульс с выхода 10,4 синхрогенератора 10 синхронизирует работу генератора 11 пилообразного напряжения и записывает в счетчик 20 очередную единицу, с выхода которого на первый выход 34 канала времени поступает число i, соответствующее i-му интервалу времени ti: ti-и. Напряжение генератора 11 пилообразного напряжения, изменяющееся от -U до

+ U, моделирующее величину г- (t - tj), поступает на первый вход шестого 19 сумматора, второй вход четвертого 22 умножителя и через квадратор 12 на второй вход третьего умножителя. Шестой 19 сумматор, на второй вход которого поступает постоянное напряжение +U со входа 32 константы устройства,.формирует на втором выходе 35 канала времени пилообразно изменяющееся напряжение от О до.+21Г. Таким образом, на выходах 34 и 35 сформирована модель канала времени, которая под действием (i+1)-ro тактового импульса с выхода 10,4 синхрогенератора 10 моделирует интервал времени ti ; ti+t.

СигналО,5 (jp)2 Bi - 1 - 2 Bi + Bi + 1 с выхода третьего 21 умножителя и сигнал 0,5 (-г-)2 В| - 1 + Bi + ije выхода четвертого 22 умножителя поступают соответственно на второй и третий входы пятого 23 сумматора, который формирует на информационном выходе 33 устройства модель решения системы дифференциальных уравнений (1) в виде аппроксимации (2), (5), соответствующую интервалу времени ti; tn-i.

X(t) . V(t) 0,5(-)2 Bi - 1 -2 Bi -f Bi H-1 +

+ 0,5 (% - Bi - 1 + Bi+ 1 +

+ 0,125 Br-1 + 6Bi + Bi+i,,

Преимущества сплайнов перед разностными методами численного решения дифференциальных уравнений состоит в том, что с помощью сплайнов определяется глобальное приближенное решение, т.е. решение, определенное на всем отрезке. При использовании для аппроксимации параболических сплайнов дефекта 1 вторая производная имеет конечные разрывы, а сам сплайн и его первая производная непрерывны. Это позволяет получить модель решения в виде гладкой непрерывной функции времени.

По сравнению с другими математическими конструкциями сплайны обладают лучшими аппроксимативными свойствами, при равных информационных затратах дают большую точность или равную точность при менее информативных исходных данных.

Таким образом, предлагаемое устройство для моделирования дифференциальных уравнений позволяет формировать найденное решение в виде непрерывной гладкой функции времени.

Формула изобретения Устройство для моделирования дифференциальных уравнений, содержащее первый, второй и третий блоки буферной памяти, первый и второй умножители, первый, второй и третий блоки памяти, первый сумматор и синхронизатор, причем первый выход синхронизатора подключен к входам считывания первого и второго блоков буферной памяти, входы начальной установки первого, второго и третьего блоков буферной памяти подключены соответственно к первому, второму и третьему информационным входам устройства, управляющий вход синхронизатора подключен к входу запуска устройства, второй выход синхронизатора подключен к входам считывания установки первого, второго и третьего блоков памяти, вход обнуления которого соединен с входом начальной установки устройства, входы начальной установки первого и второго блоков памяти соединены с четвертым и пятым информационными входами устройства соответственно, выход первого блока буферной памяти соединён с первым информационным входом первого умножителя, выход первого сумматора соединен с информационным входом первого блока памяти, выход

третьего блока буферной памяти соединен с первым информационным входом первого сумматора, о т л и ч а ю щ е е с ятем, что, с целью расширения функциональных воз- 5 можностей за счет решения неоднородной системы дифференциальных уравнений с переменными коэффициентами и формирования найденного решения в виде непре рывной функции времени, в него введены

0 генератор пилообразного напряжения, квадратор, третий и четвертый умножители, первый, второй и третий цифроаналоговые преобразователи, второй,третий, четвертый, пятый и шестой сумматоры, счетчик,

5 причем выход первого умножителя соединен с вторым информационным входом первого сумматора, третий информационный вход которого соединен с выходом второго умножителя, первый информационный вход

0 которого соединен с выходом второго блока буферной памяти, а второй информационный вход - с выходом первого блока памяти и с информационными входами первого . цифроаналогового преобразователя и вто5 рого блока памяти,выход которого соединен с вторым информационным входом первого умножителя и с информационными входами второго цифроаналогового преобразователя и третьего блока памяти, выход которого

0 соединен с информационным входом третьего цифроаналогового преобразователя, выход первого цифроаналогового преобразователя подключен к первым входам второго, третьего и четвертого сумматоров,

5 выходы которых подключены соответственно к первым входам третьего, четвертого умножителей и пятого сумматора, выход которого является информационным выходом устройства, выход второго цифроаналогово0 го преобразователя подключен к вторым входам второго и четвёртого сумматоров, третий вход которого соединен с третьим входом второго сумматора, вторым входом третьего сумматора и выходом третьего

5 цифроаналогового преобразователя, первый выход синхрогенератора подключен к первым управляющим входам первого и второго умножителей/вторые управляющие входы которых соединены с входом считы0 вания третьего блока буферной памяти, третьим выходом синхрогенератора и с первым управляющим входом первого сумматора, второй управляющий вход которого соединен с вторым выходом синхрогенера5 тора, четвертый выход которого соединен с входом синхронизации генератора пилообразного напряжения и счетным входом счетчика, вход начальной установки которого соединен с входом Минус единица устройства, а выход является первым выходом ка.нала времени устройства, выход генератора пилообразного напряжения соединен через квадратор с вторым входом третьего умножителя, выход которого соединен с вторым входом пятого сумматора, третий вход которого соединен с выходом четвертого умножителя, второй вход которого соединен с

выходом генератора пилообразного напряжения и с первым входом шестого суммато- ра, второй вход и выход которого подключены соответственно к входу константы устройства и к второму выходу канала времени устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1991 |

|

SU1837318A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300542A1 |

| Устройство для формирования вектора на экране электронно-лучевой трубки | 1982 |

|

SU1016816A2 |

| ФУНКЦИОНАЛЬНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2408136C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ЗАЩИТЫ ИНФОРМАЦИИ В СЕТЯХ СВЯЗИ | 2005 |

|

RU2295195C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1986 |

|

SU1387038A1 |

| ОПТИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА, А ТАКЖЕ ОПТИЧЕСКИЙ ПОДБЛОК ПОЛИХРОМАТИЧЕСКИХ ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАНИЙ И ОПТИЧЕСКИЙ УПРАВЛЯЕМЫЙ ТАКТОВЫЙ ГЕНЕРАТОР ДЛЯ НЕЕ | 2005 |

|

RU2297026C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении аналого-цифровых интегрирующих машин и специализированных процессов, предназначенных для решений систем дифференциальных уравнений. Целью изобретения является расширение функциональных возможностей за счет решения неоднородной системы дифференциальных уравнений с переменными коэффициентами и формирования найденного решения в виде непрерывной функции времени. Достижение положительного эффекта основано на свойствах непрерывности параболических сплайнов и их первой производной, что позволяет получать глобальное приближенное решение, определенное на всем отрезке времени. 2 ил.

фи%.4

ь ъ ь ь ь ь Ь

S Ч. ч «о оъ Ф

Ч

| Устройство для решения дифференциальных уравнений по неявной схеме переменных направлений | 1985 |

|

SU1290347A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке № 4653473/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-15—Публикация

1989-11-15—Подача