Изобретение относится к цифровой вычислительной технике, а именно к проблемно-ориентированным параллельным процессорам.

Целью изобретения является повы- шение быстродействия.

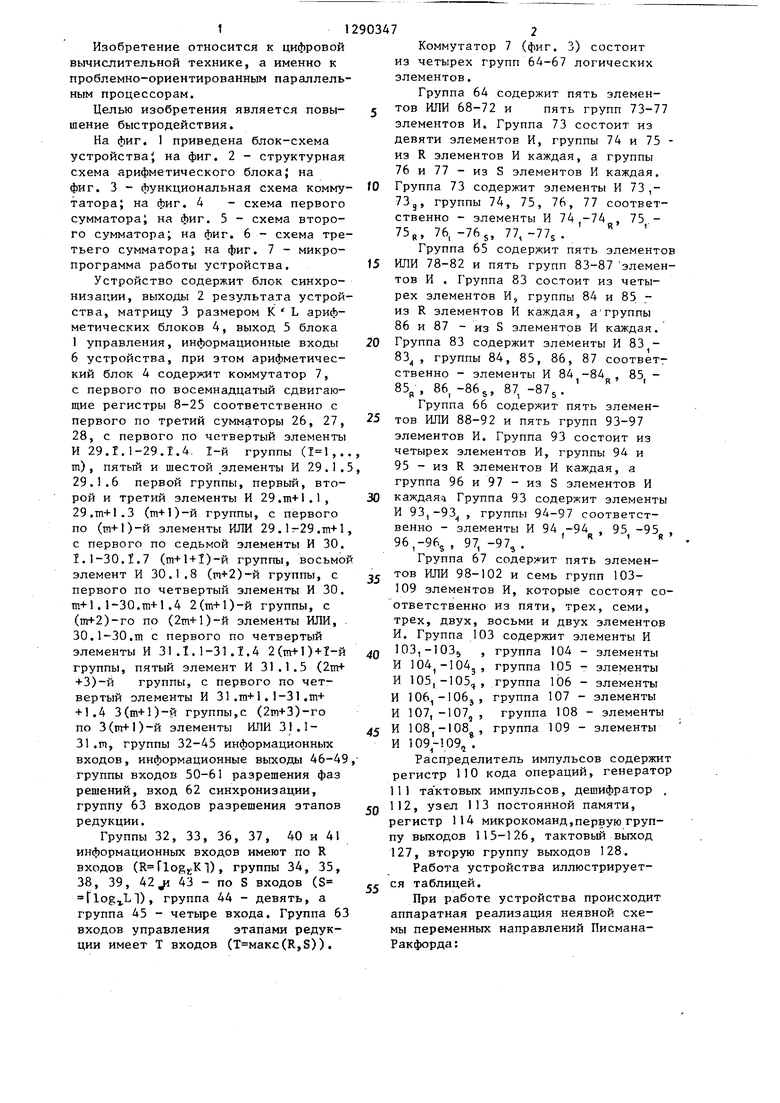

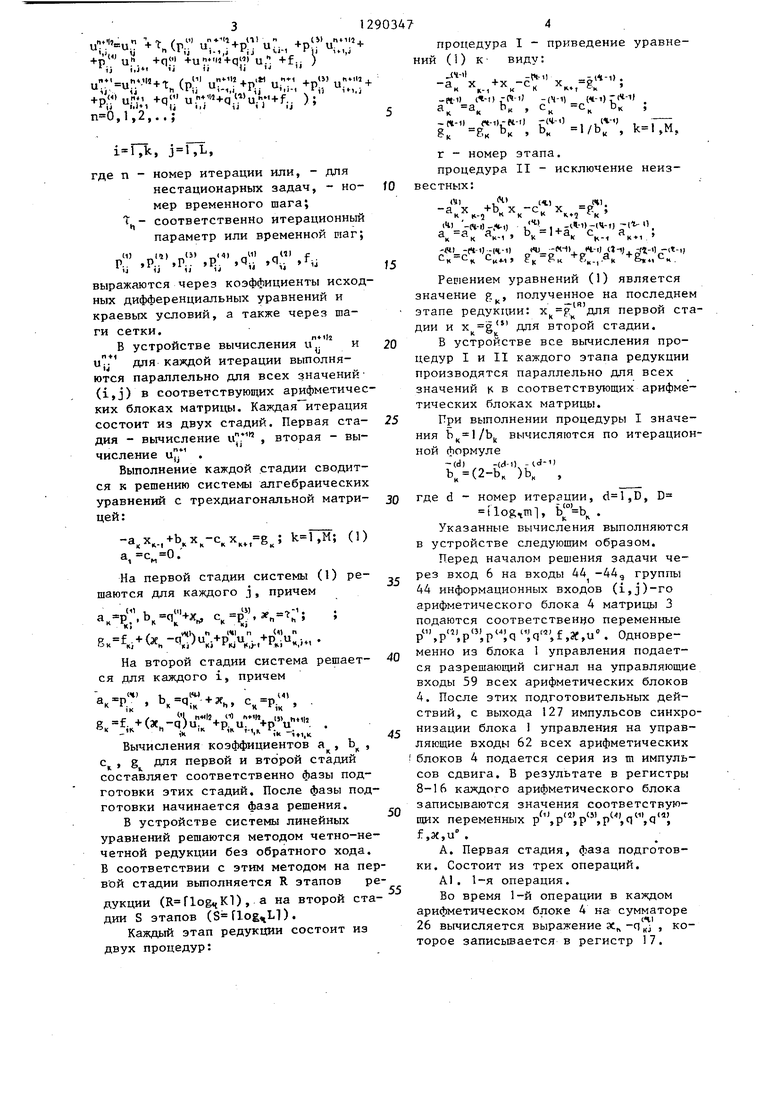

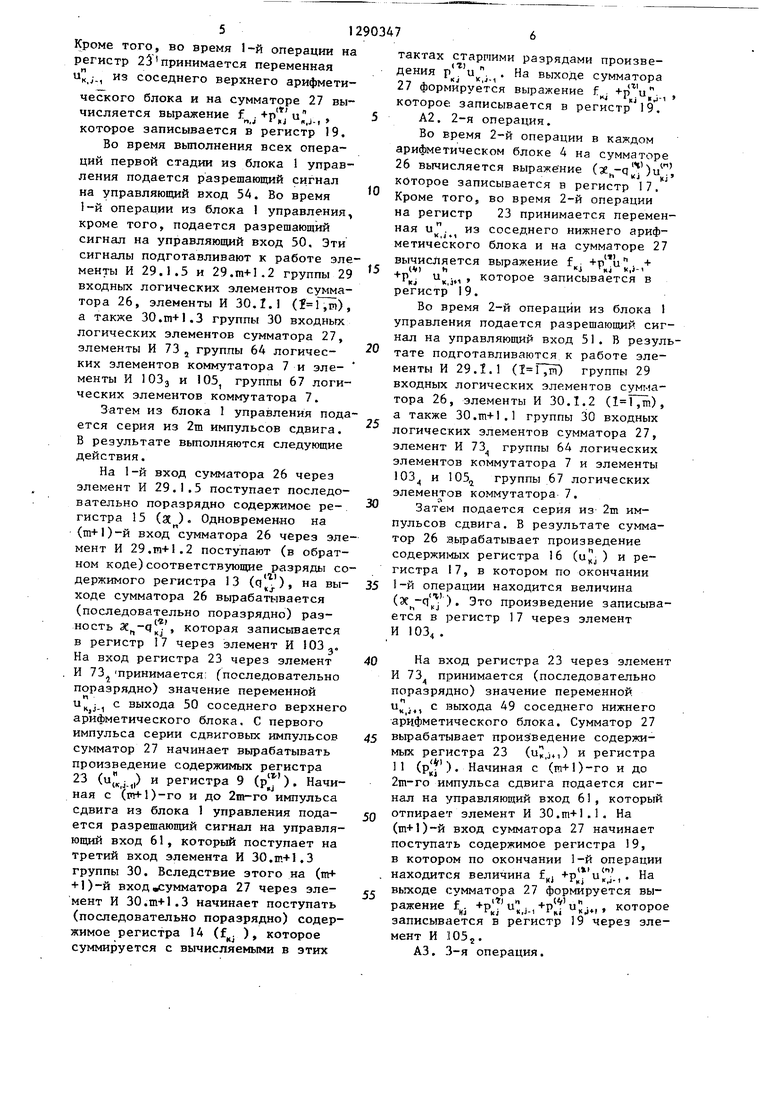

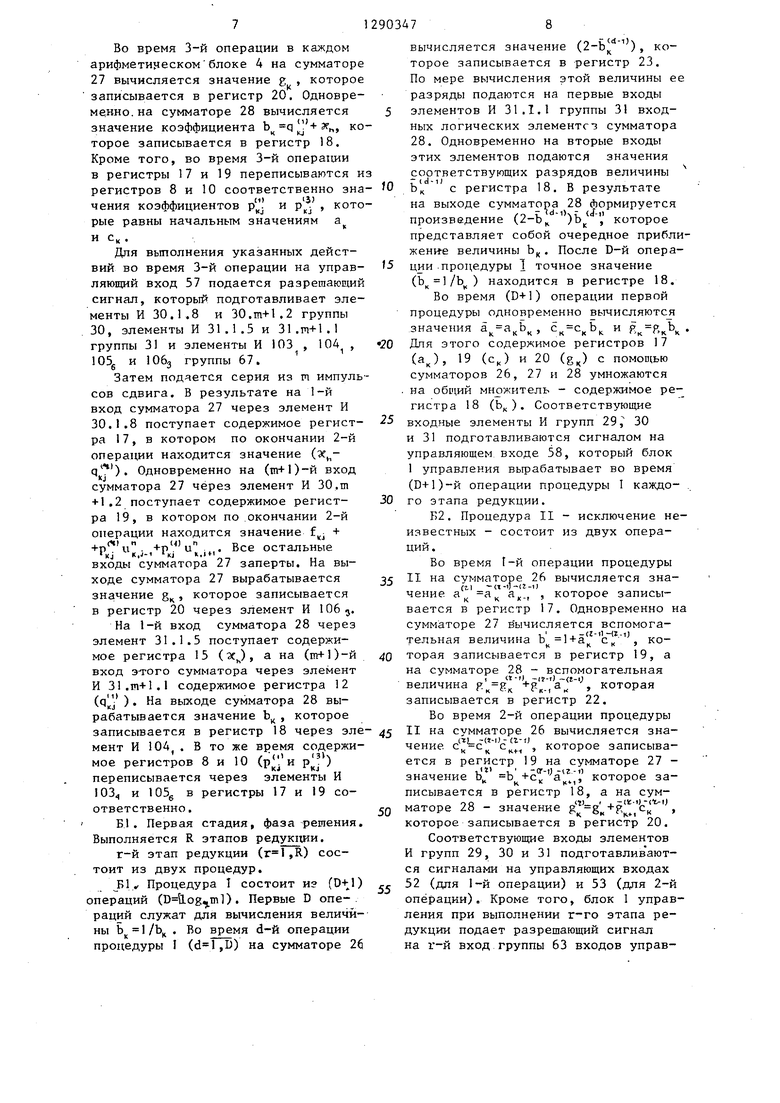

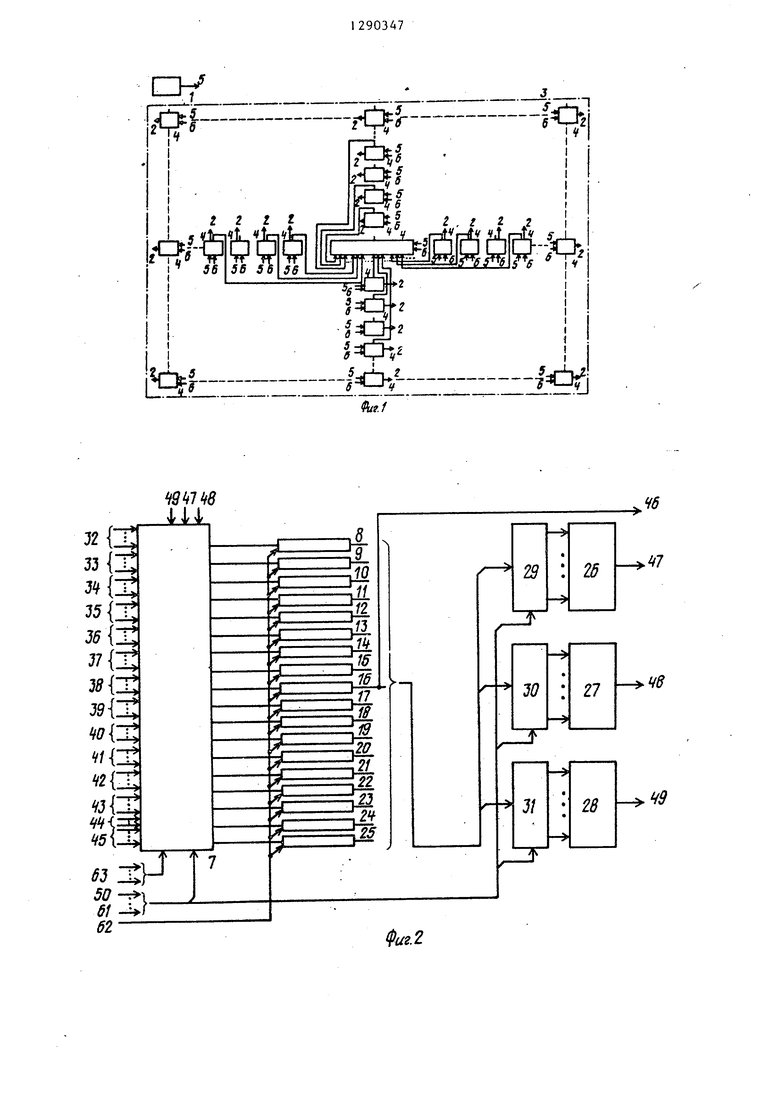

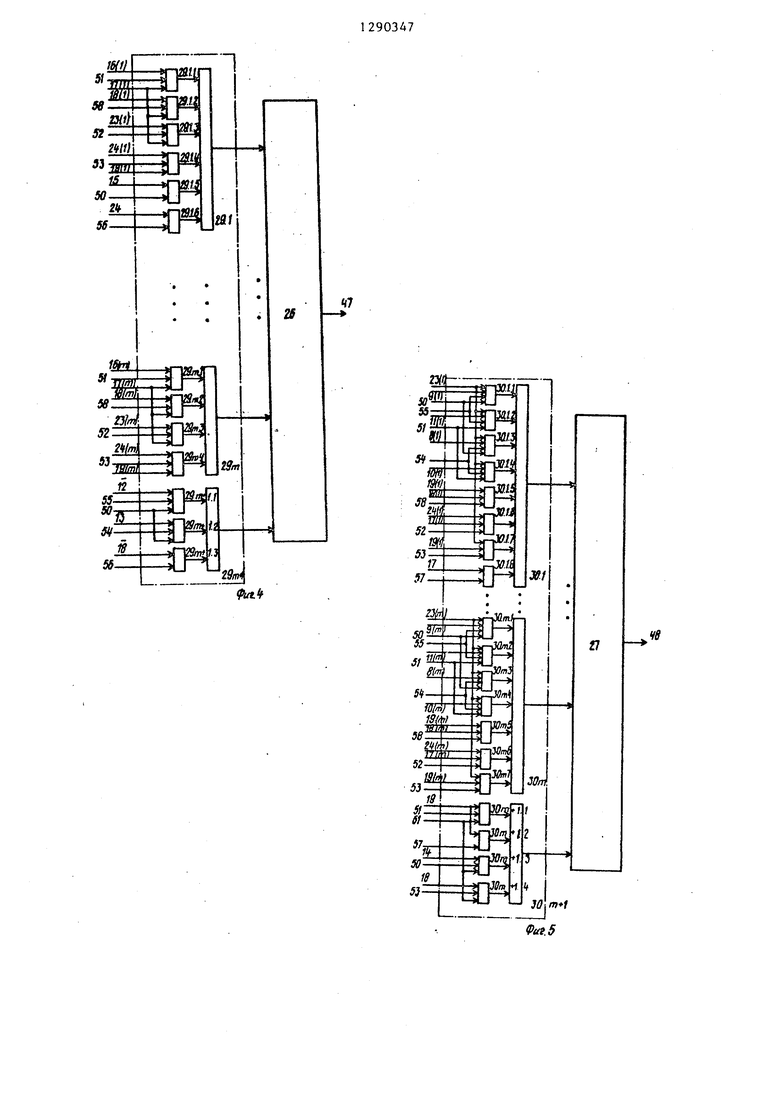

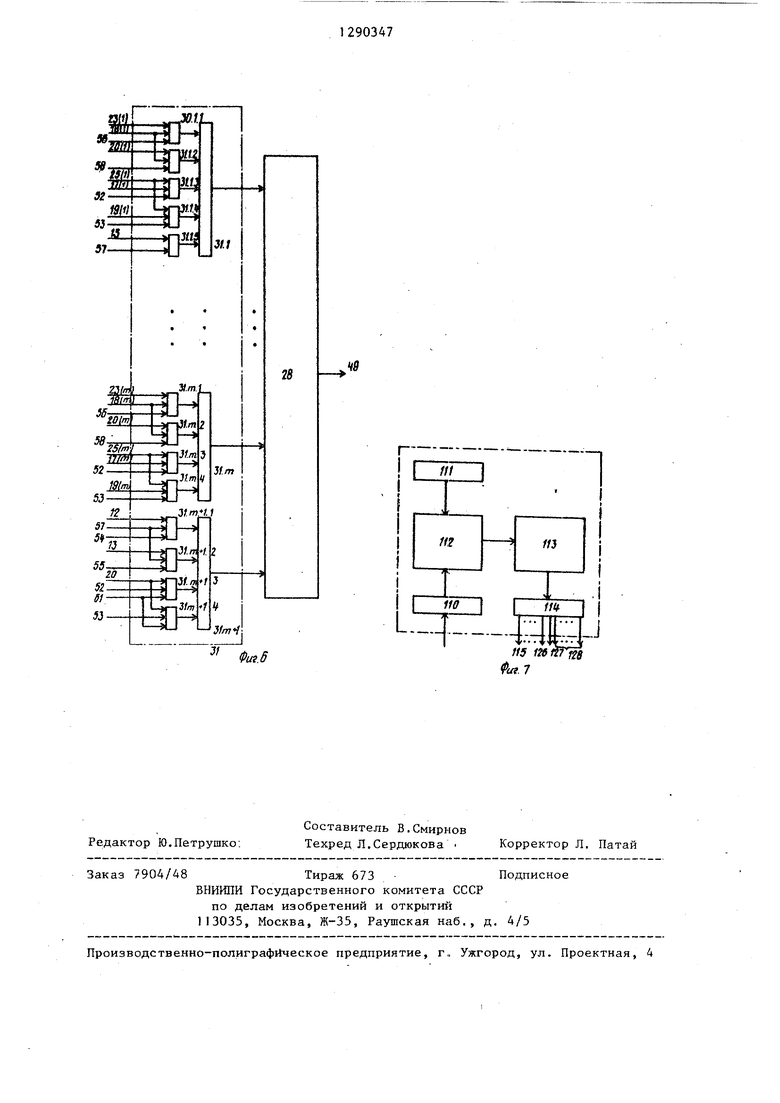

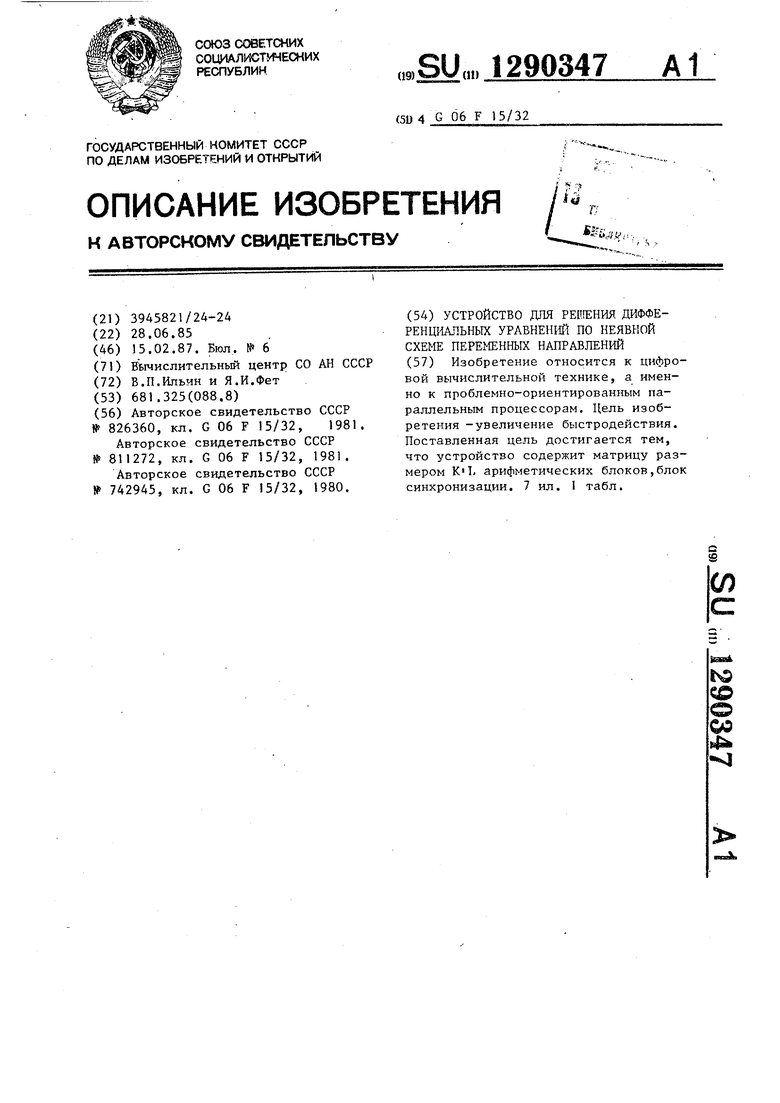

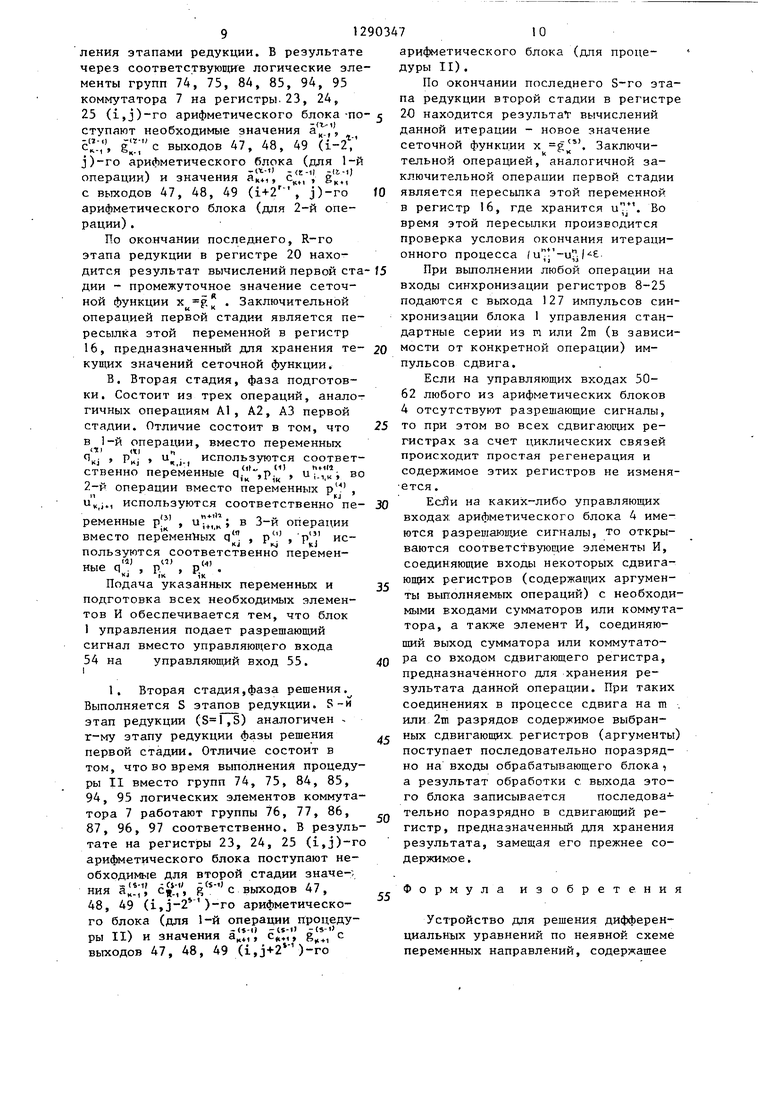

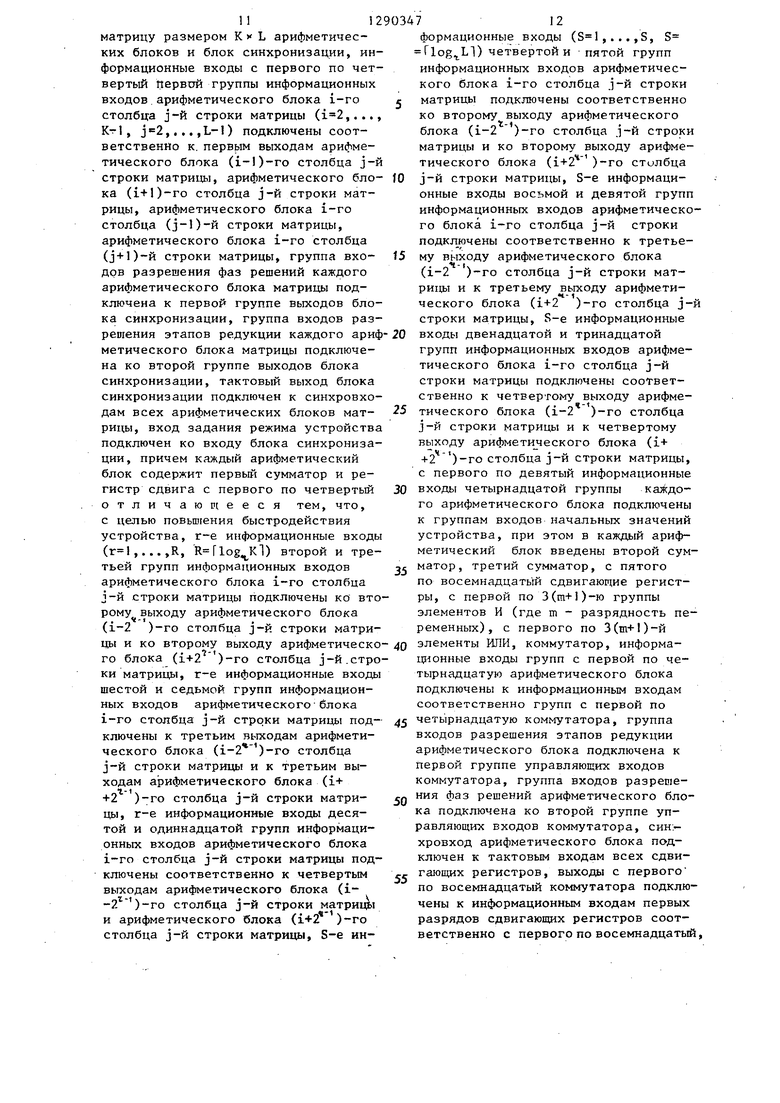

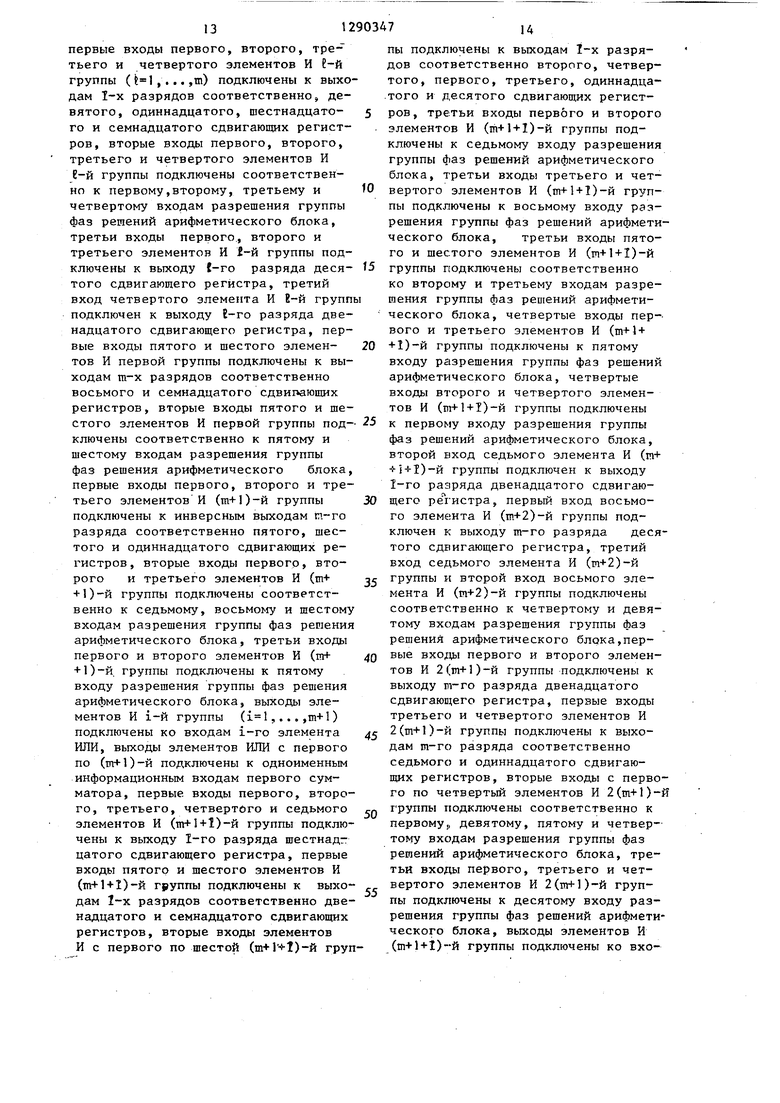

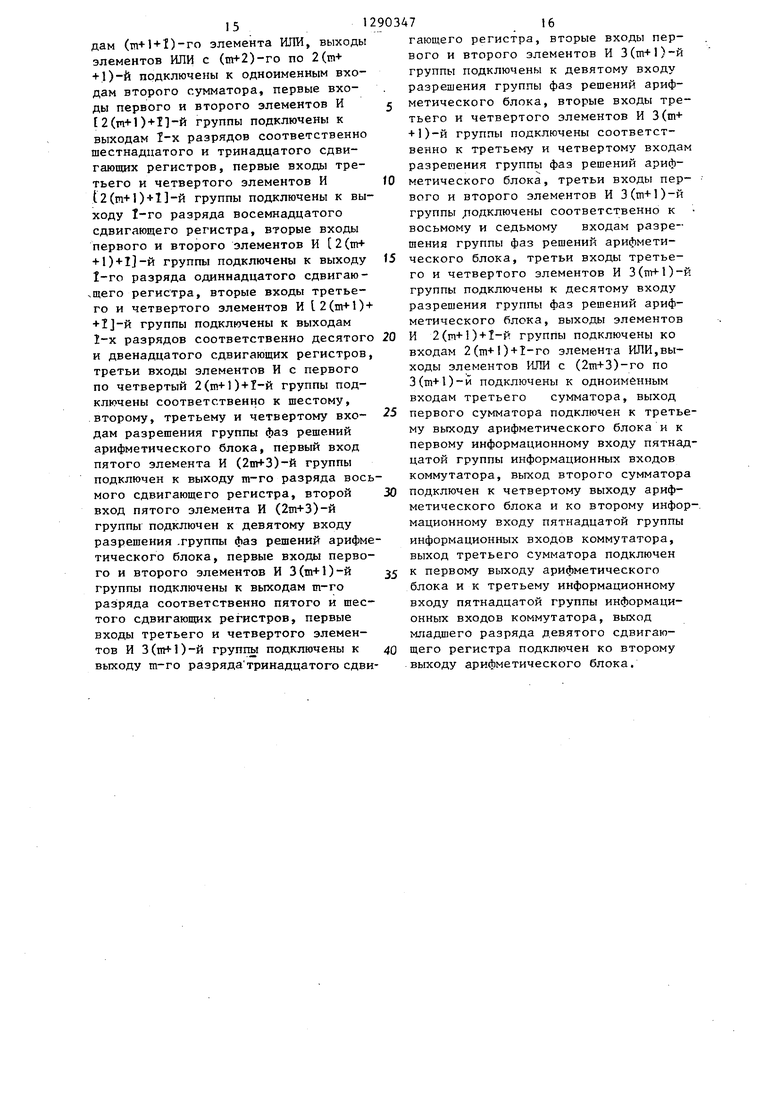

На фиг. 1 приведена блок-схема устройства , на фиг. 2 - структурная схема арифметического блока; на фиг. 3 - функциональная схема комму- татора; на фиг. 4 - схема первого сумматораi на фиг. 5 - схема второго сумматора; на фиг. 6 - схема третьего сумматора; на фиг. 7 - микропрограмма работы устройства.

Устройство содержит блок синхронизации, выходы 2 результата устройства, матрицу 3 размером К L арифметических блоков 4, выход 5 блока 1 управления, информационные входы 6 устройства, при этом арифметический блок 4 содержит коммутатор 7, с первого по восемнадцатый сдвигающие регистры 8-25 соответственно с первого по третий сумматоры 26, 27, 28, с первого по четвертый элементы И 29.1.1-29.1.4. 1-й группы (,. т) , пятьш и шестой элементы И 29 .1 . 29.1.6 первой группы, nepBbrfi, второй и третий элементы И 29.т+1.1, 29.т+1.3 (т+1)-й группы, с первого по (т+1)-й элементы ИЛИ 29. lr-29 .т+1 с первого по седьмой элементы И 30. 1.1-30.1.7 (т+1+1)-й группы, восьмо элемент И 30.1.8 (1п+2)-й группы, с первого по четвертый элементы И 30. т+1.1-30.+1.4 2(т+1)-й группы, с (т+2)-го по (2т+1)-й элементы ИЛИ, . 30.1-30.m с первого по четвертый элементы И 31.1.1-31.1.4 2(пгИ) + 1-й группы, пятый элемент И 31.1.5 (2т+ +3)-й группы, с первого по четвертый элементы И 31.m+l.1-31.т+ + 1.4 3()-й группы,с (2т+3)-го по 3(1п+1)-й элементы ИЛИ 31.1- 31.т, группы 32-45 информационных входов, информационные выходы 46-49 группы входов 50-61 разрешения фаз решений, вход 62 синхронизации, группу 63 входов разрешения этапов редукции.

Группы 32, 33, 36, 37, 40 и 41 информационных входов имеют по R входов (R riogt;Kl), группы 34, 35, 38, 39, 42 43 - по S входов (S ), группа 44 - девять, а группа 45 - четыре входа. Группа 63 входов управления этапами редукции имеет Т входов ((К,8)).

Коммутатор 7 (фиг. 3) состоит из четырех групп 64-67 логических элементов.

Группа 64 содержит пять элементов ИЛИ 68-72 и пять групп 73-77 элементов И. Группа 73 состоит иэ девяти элементов И, группы 74 и 75 из R элементов И каждая, а группы 76 и 77 - из S элементов И каждая. Группа 73 содержит элементы И 73 ,- 73д, группы 74, 75, 76, 77 соответственно - элементы И 74,-74 , 75 - 75„, 76, -76s, 77, -77s.

Группа 65 содержит пять элементо ИЛИ 78-82 и пять групп 83-87 элементов И . Группа 83 состоит из четырех элементов И, группы 84 и 85 - из R элементов И каждая, а группы 86 и 87 - из S элементов И каждая. Группа 83 содержит элементы И 83 - 83, , группы 84, 85, 86, 87 соответственно - элементы И 84 -84 , 85 - 85, 86, -86, 87 -87,.

Группа 66 содержит пять элементов ИЛИ 88-92 и пять групп 93-97 элементов И. Группа 93 состоит из четырех элементов И, группы 94 и 95 - из R элементов И каждая, а группа 96 и 97 - из S элементов И каждаял Группа 93 содержит элементы И 93,-93 , группы 94-97 соответственно - элементы И 94 -94 , 95 -95 96,-96, 97, -97,. « « Группа 67 содержит пять элементов ИЛИ 98-102 и семь групп 103- 109 элементов И, которые состоят соответственно из пяти, трех, семи, трех, двух, восьми и двух элементов И. Группа 103 содержит элементы И I03,-103g , группа 104 - элементы И 104 -104з, г РУПпа 105 - элементы И 105,-105,, группа 106 - элементы И 106,-106J, группа 107 - элементы И 107, -107,, , группа 108 - элементы И 108,-108 , группа 109 - элементы И 109-109, .

Распределитель импульсов содержи регистр 110 кода операций, генерато 111 тактовых импульсов, дешифратор 112, узел 113 постоянной памяти, регистр 114 микрокоманд,первую группу выходов 115-126, тактовый выход 127, вторую группу выходов 128.

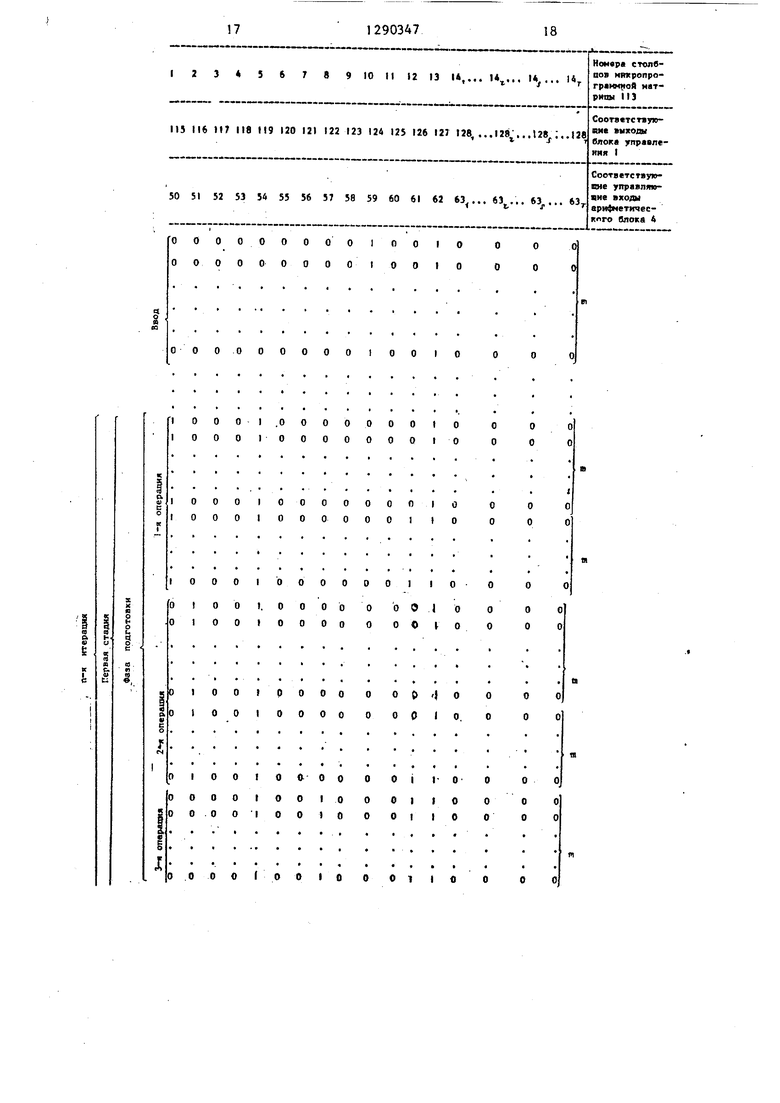

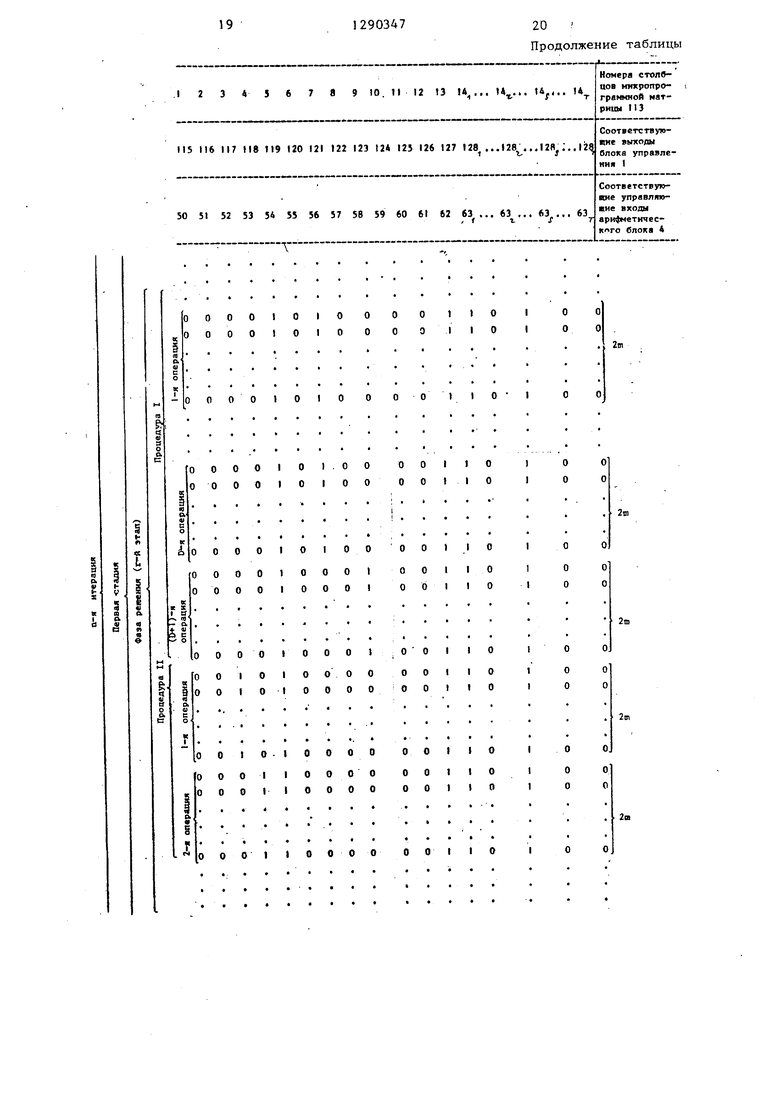

Работа устройства иллюстрируется таблицей.

При работе устройства происходит аппаратная реализация неявной схемы переменных направлений Писмана- Ракфорда:

(,,-p-u-;

+q +u 4«+q; u.. +,: )

ij i,j4 ijli1i -I

u- uir - (PU b-

);ЛЧ;: r- n - fij ;

,l,2,..;

,k, ,L,

где n - номер итерации или, - для

нестационарных задач, - но- мер временного шага; t - соответственно итерационньй параметр или временной Diar;

,p.p ,.q;:: .,fu

u и и и и

выражаются через коэффициенты исходных дифференциальных уравнений и краевых условий, а также через шаги сетки.

В устройстве вычисления и и

п+1„U

Ujj для каждой итерации выполняются параллельно для всех значений (i,j) в соответствующих арифметических блоках матрицы. Каждая итерация состоит из двух стадий. Первая ста- дня - вычисление и , вторая - вычисление .

Выполнение каждой стадии сводится к решению системы алгебраических уравнений с трехдиагональной матри- цей:

-a,x,.,+b,,x,,gj ,M; (1) а,.

На первой стадии системы (1) ре

шаются для каждого j, причем .Ь п;; +х , ;

s.f«l-oe.).-iv:,H,.

На второй стадии система решает- ся для каждого i, причем

. b,q-.e,. с,р-,. 8.f..-(.-q r-p:opV.

« iK ,к Вычисления коэффициентов а , Ь ,

С| , g для первой и второй стадий составляет соответственно фазы подготовки этих стадий. После фазы подготовки начинается фаза решения.

В устройстве системы линейных уравнений решаются методом четно-нечетной редукции без обратного хода. В соответствии с этим методом на первой стадии вьтолняется R этапов редукции (,iKl), а на второй стадии S этапов ().

Каждый этап редукции состоит из двух процедур:

процедура I - приведение уравнений (1) к- виду:

+„ -с X км к К км к

-«- I (-1) гП- ) -(Ч-1) (ч-1) . а. а.. Ь„ , с.. с„ Ьк ;

0

5

J

0

5

О

5

5

О

0

5

(VI)

-t«-i) ( , ,и -- 1 1 м

g g« b , b l/b , ,M,

r - номер этапа, процедура II - исключение неизвестных:

Л ,Л. С1) (41 . ..

.Ч, -Л-в .V,, . )-(Ч-,) -IV О . -к к-1 к к Ч-1

(Ч-.Ь-(Ч- ) )+ .) -к -и -ИМ ЕК f K « .(. Ьк, -и.

Решением уравнений (1) является значение я , полученное на последнем

-IR)

этапе редукции: для первой стадии и для второй стадии.

В устройстве все вьмисления процедур I и II каждого этапа редукции производятся параллельно для всех значений к в соответствующих арифметических блоках матрицы.

При выполнении процедуры I значения вычисляются по итерационной формуле

-(d) -(tt-tl

b (2-b, )b, ,

где d - номер итерации, ,D, D tlog.iml, .

Указанные вычисления выполняются в устройстве следующим образом.

Перед началом решения задачи через вход 6 на входы 44 -44, групгвд 44 информацнонных входов (i,j)-ro арифметического блока 4 матрицы 3 подаются соответственно переменные Р.,Г ;Ч ,3f,u°. Одновременно из блока 1 управления подается разрешающий сигнал на управляющие входы 59 всех арифметических блоков 4. После этих подготовительных действий, с выхода 127 импульсов синхронизации блока 1 управления на управляющие входы 62 всех арифметических блоков 4 подается серия из m импульсов сдвига. В результате в регистры 8-16 каждого арифметического блока записываются значения соответствующих переменных P,,,P,, f ,э(,и° .

А. Первая стадия, фаза подготовки. Состоит из трех операций.

А1 . 1-я операция.

Во время 1-й операции в каждом арифметическом блоке 4 на сумматоре 26 вычисляется выражение эс ° торое записьшается в регистр 17.

роме того, во время 1-й операции на егистр 23 принимается переменная к,;., из соседнего верхнего арифметического блока и на сумматоре 27 вычисляется выражение +p Jj и , которое записывается в регистр 19. Во время вьтолнения всех операций первой стадии из блока 1 управления подается разрешающий сигнал на управляющий вход 54. Во время 1-й операции из блока 1 управления, кроме того, подается разрешающий сигнал на управляющий вход 50, Эти сигналы подготавливают к работе элементы И 29.1.5 и 29.1П+1.2 группы 29 входных логических элементов сумматора 26, элементы И 30.1.1 (), а также 30.in+1.3 группы 30 входных логических элементов сумматора 27, элементы И 73 j группы 64 логических элементов коммутатора 7 и элементы И 103з и 105, группы 67 логических элементов коммутатора 7.

Затем из блока 1 управления подается серия из 2т импульсов сдвига. В результате вьтолняются следующие действия.

На 1-и вход сумматора 26 через элемент И 29.1.5 поступает последовательно поразрядно содержимое регистра 15 (3 )« Одновременно на (т+1)-й вход сумматора 26 через элемент И 29..2 поступают (в обратном коде)соответствующие разряды содержимого регистра 13 (), на выходе сумматора 26 вырабатывается

(последовательно поразрядно) раз{ fность . , которая записьшается

в регистр 17 через элемент И На вход регистра 23 через элемент И 72 Принимается; fпocлeдoвaтeльнo поразрядно) значение переменной с выхода 50 соседнего верхнего арифметического блока. С первого импульса серии сдвиговых импульсов сумматор 27 начинает вырабатывать произведение содержимых регистра 23 (и V,) и регистра 9 (). Начиная с (пй-1)-го и до 2in-ro импульса сдвига из блока 1 управления подается разрешающий сигнал на управляющий вход 61, который поступает на третий вход элемента И ЗО.т+1.3 группы 30. Вследствие этого на (пН- +1)-й вход«сумматора 27 через элемент И ЗО.т+1.3 начинает поступать (последовательно поразрядно) содержимое регистра 14 (f ), которое суммируется с вычисляемыми в этих

5

0

5

0

5

тактах старшими разрядами произведения . . На выходе сумматора 27 формируется выражение f .. , которое, записывается в регистр 19.

А2. 2-я операция.

Во время 2-й операции в каждом арифметическом блоке 4 на сумматоре 26 вычисляется выраже ние (), которое записывается в регистр 17. Кроме того, во время 2-й операции на регистр 23 принимается переменная и, из соседнего нижнего арифметического блока и на сумматоре 27 вычисляется выражение f +р и. +

. (V) J +р . u, , которое записывается в регистр 19.

Во время 2-й операции из блока 1 управления подается разрешающий сигнал на управляющий вход 51. В результате подготавливаются к работе элементы И 29.1.1 () группы 29 входных логических элементов сумматора 26, элементы И 30.1.2 (,т), а также ЗО.т+1.1 группы 30 входных логических элементов сумматора 27, элемент И 73 группы 64 логических элементов коммутатора 7 и элементы 103, и 105 группы 67 логических элементов коммутатора 7.

Затем подается серия из 2т импульсов сдвига. В результате сумматор 26 вырабатывает произведение содержи1 ых регистра 16 ( ) и регистра 17, в котором по окончании 1-и операции находится величина (зе-q J ). Это произведение записывается в регистр 17 через элемент И 1034 .

0 На вход регистра 23 через элемент И 73 принимается (последовательно поразрядно) значение переменной и. с вькода 49 соседнего нижнего арифметического блока. Сумматор 27

5 вырабатывает произведение содержимых регистра 23 (.j,,) и регистра 11 (). Начиная с (т+1)-го и до 2т-го импульса сдвига подается сигнал на управляющий вход 61, который

0 отпирает элемент И ЗО.т+1.1. На

(т+О-й вход сумматора 27 начинает поступать содержимое регистра 19, в котором по окончании 1-й операции . находится величина f|,j . и ,; .,. На

С выходе сумматора 27 формируется выражение f. .j.,+p|;t u:;j,,, которое записывается в регистр 19 через элемент И 105,.

A3. 3-я операция.

Во время 3-й операции в каждом арифметинеском блоке 4 на сумматоре 27 вычисляется значение g , которое записывается в регистр 20. Одновременно, на сумматоре 28

/ 1

коГ d-l)

значение коэффициента b q -t-3f

вычисляется

.

торое записывается в регистр 18. Кроме того, во время 3-й операции в регистры 17 и 19 переписываются из регистров 8 и 10 соответственно значения коэффициентов p J и , которые равны начальным значениям а и с .

Для вьтолнения указанных действий во время 3-й операции на управляющий вход 57 подается разрегааюсшй сигнал, который подготавливает элементы И 30.1.8 и ЗО.т+1.2 группы 30, элементы И 31.1.5 и 31.iii+l.l группы 31 и элементы И 103 , 104 , 105g и 106з группы 67.

Затем подается серия из m импульсов сдвига. В результате на 1-й вход сумматора 27 через элемент И 30.1.8 поступает содержимое регистра 17, в котором по окончании 2-й операции находится значение ( q ). Одновременно на (т+1)-й вход сумматора 27 через элемент И 30.m

.2 поступает содержимое регист- 30 ра 19, в котором по окончании 2-й операции находится значение f + . ,. Все остальные

«KJ KI - ч 4,

входы сумматора 27 заперты. На выходе сумматора 27 вырабатывается 35 значение g, которое записывается чение в регистр 20 через элемент И 106 .j. На 1-й вход сумматора 28 через элемент 31.1.5 поступает содержимое регистра 15 () , а на (ш+О-й 40 вход этого сумматора через элемент И 31.т+1.1 содержимое регистра 12 ( ) . На выходе сумматора 28 вырабатывается значение Ь, которое

вычисляется значение (2-6, которое записывается в регистр 23. По мере вычисления этой величины е разряды подаются на первые входы

5 элементов И 31.1.1 группы 31 входных логических элементез сумматора 28. Одновременно на вторые входы этих элементов подаются значения соответствующих разрядов величины

О Ь с регистра 18. В результате на выходе сумматора 28 Лормируется

/гл г - хГ («Г-Ч

произведение (2-Ь )Ъ , которое представляет собой очередное прибли величины Ь. После D-й опера- 5 ции процедуры 1 точное значение

() находится в регистре 18. Во время (D+1) операции первой процедуры одновременно вычисляютс значения ,Ь, и g,g 20 Для этого содержимое регистров 17 (а), 19 (с) и 20 (g) с помощью сумматоров 26, 27 и 28 умножаются . на общий множитель - содержимое регистра 18 (Ь). Соответствующие 2-5 входные элементы И групп 29 30 и 31 подготавливаются сигналом на управляющем входе 58, который блок

Iуправления вырабатывает во время (В+О-й операции процедуры I каждого этапа редукции.

Б2. Процедура II - исключение не известных - состоит из двух операций.

Во время t-й операции процедуры

IIна сумматоре 26 вычисляется зна(ti 1-1)-(г-1)

«к «.

которое записывается в регистр 17. Одновременно н сумматоре 27 в ычисляется вспомогательная величина Ь| , , которая записывается в регистр 19, а на сумматоре 28 - вспомогательная величина . a , которая записывается в регистр 22.

Во время 2-й операции процедуры

записывается в регистр 18 через эле- 45 И на сумматоре 26 вычисляется знамент И 104,. В то же время содержимое регистров 8 и 10 (р, и ) переписывается через элементы И 103ц и 105g в регистры 17 и 19 соответственно .

Б1. Первая стадия, фаза решения. Выполняется R этапов редукции.

г-й этап редукции (,R) состоит из двух процедур.

Процедура I состоит иг (D-i;) операций (). Первые D one-, раций служат для вычисления величины . Во время d-й операции процедуры I (,D) на сумматоре 26

чение с «- с-::;

которое записывается в регистр 19 на сумматоре 27 - значение Ь Ь которое за50

55

писывается в регистр 18, а на сумматоре 28 - значение , которое записывается в регистр 20. Соответствующие входы элементов И групп 29, 30 и 31 подготавливаются сигналами на управляющих входах 52 (для 1-й операции) и 53 (для 2-й операции). Кроме того, блок 1 управления при выполнении г-го этапа редукции подает разрещающий сигнал на г-й вход группы 63 входов управ

0

5 чение 0

вычисляется значение (2-6, которое записывается в регистр 23. По мере вычисления этой величины ее разряды подаются на первые входы

5 элементов И 31.1.1 группы 31 входных логических элементез сумматора 28. Одновременно на вторые входы этих элементов подаются значения соответствующих разрядов величины

О Ь с регистра 18. В результате на выходе сумматора 28 Лормируется

/гл г - хГ («Г-Ч

произведение (2-Ь )Ъ , которое представляет собой очередное прибли- величины Ь. После D-й опера- 5 ции процедуры 1 точное значение

() находится в регистре 18. Во время (D+1) операции первой процедуры одновременно вычисляютс значения ,Ь, и g,g . 0 Для этого содержимое регистров 17 (а), 19 (с) и 20 (g) с помощью сумматоров 26, 27 и 28 умножаются . на общий множитель - содержимое регистра 18 (Ь). Соответствующие -5 входные элементы И групп 29 30 и 31 подготавливаются сигналом на управляющем входе 58, который блок

Iуправления вырабатывает во время (В+О-й операции процедуры I каждо . го этапа редукции.

Б2. Процедура II - исключение неизвестных - состоит из двух операций.

Во время t-й операции процедуры

IIна сумматоре 26 вычисляется зна(ti 1-1)-(г-1)

«к «.

которое записывается в регистр 17. Одновременно на сумматоре 27 в ычисляется вспомогательная величина Ь| , , которая записывается в регистр 19, а на сумматоре 28 - вспомогательная величина . a , которая записывается в регистр 22.

Во время 2-й операции процедуры

И на сумматоре 26 вычисляется значение с «- с-::;

которое записывается в регистр 19 на сумматоре 27 - значение Ь Ь которое за

писывается в регистр 18, а на сумматоре 28 - значение , которое записывается в регистр 20. Соответствующие входы элементов И групп 29, 30 и 31 подготавливаются сигналами на управляющих входах 52 (для 1-й операции) и 53 (для 2-й операции). Кроме того, блок 1 управления при выполнении г-го этапа редукции подает разрещающий сигнал на г-й вход группы 63 входов управления этапами редукции. В результате через соответствующие логические элементы групп 74, 75, 84, 85, 94, 95 коммутатора 7 на регистры.23, 24, 25 (i,j)-ro арифметического блока-поступают необходимые значения а ,, -сз-о

.1

Ci выходов 47, 48, 49 (i-2, i)-ro арифметического блока (для 1-й

.-It-t) - /r-tl -(t-it

операции) и значения а,, с, , g,/ с выходов 47, 48, 49 (1+2 , j)-ro арифметического блока (для 2-й операции) .

По окончании последнего, R-ro этапа редукции в регистре 20 находится результат вычислений первой ста дии - промежуточное значение сеточной функции X р, . Заключительной операцией первой стадии является пересылка этой переменной в регистр 16, предназначенный для хранения текущих значений сеточной функции.

В. Вторая стадия, фаза подготовки. Состоит из трех операций, аналогичных операциям А1, А2, A3 первой стадии. Отличие состоит в том, что

., V, 9 1 t IK

2-Й операции вместо переменных р .

ц, используются соответственно пе

U

( 1tl+ lf u

ременные , u,,; в 3-й операции вместо переменных q. , , р используются соответственно перемен- ные - , 1,- , .

Подача указанных переменных и подготовка всех необходимых элементов И обеспечивается тем, что блок 1 управления подает разрешающий сигнал вместо управляющего входа

в 1-й операции, вместо переменных

л h Kj PUJ к j-i используются соответственно переменные q.,p., в

54 на

управляющий вход 55.

1. Вторая стадия,фаза решения . Выполняется S этапов редукции. S-и этап редукции (,S) аналогичен г-му этапу редукции фазы решения первой стадии. Отличие состоит в том, что во время выполнения процедуры II вместо групп 74, 75, 84, 85, 94, 95 логических элементов коммутатора 7 работают группы 76, 77, 86, 87, 96, 97 соответственно. В результате на регистры 23, 24, 25 (i,j)-ro ари4 4етического блока поступают необходимые для второй стадии значе--- ния , с выходов 47, 48, 49 (i,)-ro арифметического блока (для 1-й операции процедуры II) и значения , , выходов 47, 48, 49 (i,j-f2 )-го

10

/5 9034710

арифметического блока (для процедуры II).

По окончании последнего S-ro этапа редукции второй стадии в регистре 20 находится результат вычислений данной итерации - новое значение сеточной функции х . Заключительной операцией, аналогичной заключительной операпии первой стадии является пересылка этой переменной в регистр 16, где хранится и. Во

30

20

25

время этой пересылки производится проверка условия окончания итерационного процесса

При вьшолнении любой операции на входы синхронизации регистров 8-25 подаются с выхода 127 импульсов синхронизации блока 1 управления стандартные серии из п или 2т (в зависимости от конкретной операции) импульсов сдвига.

Если на управляющих входах 50- 62 любого из арифметических блоков 4 отсутствуют разрешающие сигналы, то при этом во всех сдвигаюищх регистрах за счет циклических связей происходит простая регенерация и содержимое этих регистров не изменяется .

ЕсЛи на каких-либо управляющих входах арифметического блока 4 имеются разрешаю1дие сигналы, то открываются соответствующие элементы И, соединяющие входы некоторых сдвигающих регистров (содержащих аргументы выполняемых операций) с необходимыми входами сумматоров или коммутатора, а также элемент И, соединяющий выход сумматора или коммутатора со входом сдвигающего регистра, предназначенного для хранения результата данной операции. При таких соединениях в процессе сдвига на m . или 2m разрядов содержимое выбран- 2 ных сдвигаюш 1х. регистров (аргументы) поступает последовательно поразрядно на входы обрабатывающего блока, а результат обработки с выхода этого блока записывается последовательно поразрядно в сдвигающий регистр , предназначенный для хранения результата, замещая его прежнее содержимое .

35

40

50

Формула изобретения

Устройство для решения дифференциальных уравнений по неявной схеме переменных направлений, содержащее

11129034712

матрицу размером Кх L арифметичес- формационные входы (,..,,5, S

fO

15

ких блоков и блок синхронизации, информационные входы с первого по четвертый Первпй группы информационных входов.арифметического блока i-ro столбца j-й строки матрицы (,..., К-:-, JC2L-1) подключены соответственно к. первым выходам арифметического блока (i-l)-ro столбца j-й строки матрицы, арифметического блока (i+l)-ro столбца j-й строки матрицы, арифметического блока i-ro столбца (л-1)-й строки матрицы, арифметического блока i-ro столбца (j+l)-A строки матрицы, группа входов разрешения фаз решений каждого арифметического блока матрицы подключена к первой группе выходов блока синхронизации, группа входов разрешения этапов редукции каждого ариф-20 метического блока матрицы подключена ко второй группе выходов блока синхронизации, тактовый выход блока синхронизации подключен к синхровхо- дам всех арифметических блоков матрицы, вход задания режима устройства подключен ко входу блока синхронизации, причем каждый арифметический блок содержит первый сумматор и регистр сдвига с первого по четвертый отличающееся тем, что, с целью повьш ения быстродействия устройства, г-е информационные входы (,...,R, ) второй и третьей групп информационных входов арифметического блока i-ro столбца i-й строки матрицы подключены ко второму выходу арифметического блока () четвертой и пятой групп информационных входов арифметического блока i-ro столбца j-й строки матрицы подключены соответственно ко второму выходу арифметического блока (i-2 )-го столбца j-й строк матрицы и ко второму выходу арифме тического блока (i+2 )-го столбца j-й строки матрицы, S-e информационные входы восьмой и девятой груп информационных входов арифметическ го блока i-ro столбца j-й строки подключены соответственно к третье му выходу арифметического блока (i-2 )-го столбца j-й строки матрицы и к третьему выходу арифметического блока (i+2 )-го столбца j строки матрицы, S-e информационные входы двенадцатой и тринадцатой групп информационных входов арифме тического блока i-ro столбца j-й строки матрицы подключены соответственно к четвертому выходу арифме тического блока (i-2 )-го столбца j-й строки матрицы и к четвертому выходу арифмети 1еского блока (i+ +2 )-го столбца j-й строки матрицы с первого по девятый информационны 30 входы четырнадцатой группы каждо го арифметического блока подключен к группам входов начальных значени устройства, при этом в каждый ариф метический блок введены второй су матор, третий сумматор, с пятого по восемнадцатый сдвигающие регист ры, с первой по 3(т+1)-ю группы элементов И (где m - разрядность п ременных) , с первого по 3(т+1)-й

25

35

)-го столбца j-й строки матрицы и ко второму выходу арифметическо- 40 элементы ИЛИ, коммутатор, информа)7

го блока (i+2 )-го столбца j-й.строки матрицы, г-е информационные входы шестой и седьмой групп информационных входов арифметического блока i-ro столбца j-й строки матрицы подключены к третьим выходам арифметического блока ()-ro столбца j-й строки матри1№1 и к третьим выходам арифметического блока (i+ +2 )-го столбца j-й строки матрицы, г-е информационные входы десятой и одиннадцатой групп информационных входов арифметического блока i-ro столбца j-й строки матрицы подключены соответственно к четвертым выходам арифметического блока (i- )-го столбца j-й строки матрищ и арифметического блока (i+2 )-го столбца j-й строки матрИ1Ц 1, S-e инционные входы групп с первой по четырнадцатую арифметического блока подключены к информационным входам соответственно групп с первой по

j четырнадцатую коммутатора, группа входов разрешения этапов редукции арифметического блока подключена к Первой группе управляющих входов коммутатора, группа входов разрешеfQ ния фаз решений арифметического бло ка подключена ко второй группе управляющих входов коммутатора, син.- хровход арифметического блока подключен к тактовым входам всех сдви гающих регистров, выходы с первого по восемнадцатый коммутатора подклю чены к информационным входам первых разрядов сдвигающих регистров соответственно с первого по восемнадцаты

55

) четвертой и пятой групп информационных входов арифметического блока i-ro столбца j-й строки матрицы подключены соответственно ко второму выходу арифметического блока (i-2 )-го столбца j-й строки матрицы и ко второму выходу арифметического блока (i+2 )-го столбца j-й строки матрицы, S-e информационные входы восьмой и девятой групп информационных входов арифметического блока i-ro столбца j-й строки подключены соответственно к третьему выходу арифметического блока (i-2 )-го столбца j-й строки матрицы и к третьему выходу арифметического блока (i+2 )-го столбца j-й строки матрицы, S-e информационные входы двенадцатой и тринадцатой групп информационных входов арифметического блока i-ro столбца j-й строки матрицы подключены соответственно к четвертому выходу арифметического блока (i-2 )-го столбца j-й строки матрицы и к четвертому выходу арифмети 1еского блока (i+ +2 )-го столбца j-й строки матрицы, с первого по девятый информационные входы четырнадцатой группы каждого арифметического блока подключены к группам входов начальных значений устройства, при этом в каждый арифметический блок введены второй сумматор, третий сумматор, с пятого по восемнадцатый сдвигающие регистры, с первой по 3(т+1)-ю группы элементов И (где m - разрядность переменных) , с первого по 3(т+1)-й

элементы ИЛИ, коммутатор, информационные входы групп с первой по четырнадцатую арифметического блока подключены к информационным входам соответственно групп с первой по

j четырнадцатую коммутатора, группа входов разрешения этапов редукции арифметического блока подключена к Первой группе управляющих входов коммутатора, группа входов разрешеQ ния фаз решений арифметического блока подключена ко второй группе управляющих входов коммутатора, син.- хровход арифметического блока подключен к тактовым входам всех сдвигающих регистров, выходы с первого по восемнадцатый коммутатора подключены к информационным входам первых разрядов сдвигающих регистров соответственно с первого по восемнадцатый.

5

первые входы первого, второго, третьего и четвертого элементов И Е-й группы (,...,т) подключены к выходам Т-х разрядов соответственно, девятого, одиннадцатого, шестнадцатого и семнадцатого сдвигающих регистров, вторые входы первого, второго, третьего и четвертого элементов И -й группы подключены соответственно к первому,второму, третьему и четвертому входам разрешения группы фаз решений арифметического блока, третьи входы первого, второго и третьего элементов И 1-й группы подключены к выходу -го разряда десятого сдвигающего регистра, третий вход четвертого элемента И Е-й групп подключен к выходу Е-го разряда двенадцатого сдвигающего регистра, первые входы пятого и шестого элементов И первой группы подключены к выходам т-х разрядов соответственно восьмого и семнадцатого сдвигающих регистров, вторые входы пятого и шестого элементов И первой группы подключены соответственно к пятому и шестому входам разрешения группы фаз решения арифметического блока первые входы первого, второго и третьего элементов И (т+1)-й группы подключены к инверсным выходам п-го разряда соответственно пятого, шестого и одиннадцатого сдвигающих регистров , вторые входы первого второго и третьего элементов И ( +1)-й группы подключены соответственно к седьмому, восьмому и шестому входам разрешения группы фаз репюния арифметического блока, третьи входы первого и второго элементов И (т+ +1)-и. группы подключены к пятому входу разрешения группы фаз решения арифметического блока, выходы элементов И i-й группы (,...,го+1) подключены ко входам i-ro элемента ИЛИ, выходы элементов ИЛИ с первого по (т+1)-й подключены к одноименным информационньм входам первого сумматора, первые входы первого, второго, третьего, четвертого и седьмого элементов И (т+1+1)-й группы подключены к выходу 1-го разряда шестнадг цатого сдвигающего регистра, первые входы пятого и шестого элементов И (т+1+1)-й группы подключены к выходам 1-х разрядов соответственно двенадцатого и семнадцатого сдвигающих регистров, вторые входы элементов И с первого по шестой ()-й гру

O

5

0

5 30

35

40

45

50

55

пы подключены к выходам 1-х разрядов соответственно второго, четвертого, первого, третьего, одиннадца- .того и десятого сдвигающих регистров, третьи входы первого и второго элементов И ( + 1)-й группы подключены к седьмому входу разрешения группы фаз решений арифметического блока, третьи входы третьего и четвертого элементов И (т+1+1)-й группы подключены к восьмому входу разрешения группы фаз решений арифметического блока, третьи входы пятого и шестого элементов И ( + 1)-й группы подключены соответственно ко второму и третьему входам разрешения группы фаз решений арифметического блока, четвертые входы пер-- вого и третьего элементов И (т+Н )-й группы подключены к пятому входу разрешения группы фаз решений арифметического блока, четвертые входы второго и четвертого элементов И (1п+1 + 1)-й группы подключены к первому входу разрешения группы фаз реше;ний арифметического блока, второй вход седьмого элемента И (in+ )-й группы подключен к выходу 1-го разряда двенадцатого сдвигающего регистра, первый вход восьмого элемешта И (т-+-2)-й группы подключен к выходу т-го разряда десятого сдвигающего регистра, третий вход седьмого элемента И ()-й группы и второй вход восьмого элемента И (1п+2)-й группы подключены соответственно к четвертому и девятому входам разрешения группы фаз решения арифметического блрка,первые входы первого и второго элементов И 2(1п+1)-й группы подключены к выходу п-го разряда двенадцатого сдвигающего регистра, первые входы третьего и четвертого элементов И 2(т+1)-й группы подключены к выходам ш-го разряда соответственно седьмого и одиннадцатого сдвигающих регистров, вторые входы с первого по четвертый элементов И 2(т+1)-й группы подключены соответственно к первомуJ, девятому, пятому и четвертому входам разрешения группы фаз решений арифметического блока, третьи входы первого, третьего и четвертого элементов И 2(т+1)-й группы подключены к десятому входу разрешения группы фаз решений арифметического блока, выходы элементов И (т+1+1)й группы подключены ко входам ()-ro элемента ИЛИ, выходы элементов ИЛИ с (т+2)-го по 2(in-i- +1)-й подключены к одноименным входам второго сумматора, первые входы первого и второго элементов И 2(тп+1) группы подключены к выходам 1-х разрядов соответственно шестнадцатого и тринадцатого сдвигающих регистров, первые входы третьего и четвертого элементов И |2(т+1) группы подключены к выходу 1-го разряда восемнадцатого сдвигающего регистра, вторые входы первого и второго элементов И 2(т+ +1) группы подключены к выходу 1-го разряда одиннадцатого сдвигаю- чщего регистра, вторые входы третьего и четвертого элементов И I2(m+l)+ группы подключены к выходам 1-х разрядов соответственно десятого и двенадцатого сдвигающих регистров, третьи входы элементов И с первого по четвертый 2(т-|-1) + Т-й группы подключены соответственно к шестому, второму, третьему и четвертому входам разрешения группы фаз решений арифметического блока, первый вход пятого элемента И (2пН-3)-й группы подключен к выходу т-го разряда восьмого сдвигающего регистра, второй вход пятого элемента И (2т+3)-й группы подключен к девятому входу разрешения .группы фаз решений арифметического блока, первые входы первого и второго элементов И 3(т+1)-и группы подключены к выходам т-го разряда соответственно пятого и шестого сдвигающих регистров, первые входы третьего и четвертого элементов И 3(1П+1)-й групгш подключены к выходу т-го разряда тринадцатого сдви

гающего регистра, вторые входы первого и второго элементов И 3(т+1)-й группы подключены к девятому входу разрешения группы фаз решений арифметического блока, вторые входы третьего и четвертого элементов И 3( +1)-й группы подключены соответственно к третьему и четвертому входам разрешения группы фаз решений арифметического блока, третьи входы первого и второго элементов И 3(т+1)-й группы /годключены соответственно к восьмому и седьмому входам разрешения группы фаз решений арифметического блока, третьи входы третьего и четвертого элементов И 3(гп+1)-й группы подключены к десятому входу разрешения группы фаз решений арифметического блока, выходы элементов И 2(1П+1) + 1-й группы подключены ко входам 2 ()- -1-го элемента ИЛИ,выходы элементов ИЛИ с (2т+3)-го по 3(1п+1)-й подключены к одноименным входам третьего сумматора, выход первого сумматора подключен к третьему выходу арифметического блока и к первому информационному входу пятнадцатой группы информационных входов коммутатора, выход второго сумматора подключен к четвертому выходу арифметического блока и ко второму инфор-. мационному входу пятнадцатой группы информационных входов коммутатора, выход третьего сумматора подключен к первому выходу арифметического блока и к третьему информационному входу пятнадцатой группы информационных входов коммутатора, выход младшего разряда девятого сдвигающего регистра подключен ко второму выходу арифметического блока.

Продолжение таблицы

21

1290347

t 2 3 4 3 в 7 в 9 0 и 12 13 14,.. 14.... I,... 14

115 116 117 118 119 120 12 122 123 124 125 126 IZ7 12«1 ...128 .,.|2Я,;..12е

50 51 52 53 54 55 56 57 58 59 60 61 62 63 ... 63 ... 63 ... 63

22 Продолжение таблицы

Конера стопв- цов микропрограммной мат- ряиы ИЗ

Соответствую- цие выхода блока управления I

Соответсгвую- цие управляю- пне входы зрифметичес- кпго блока 4

О/

iU

J2 33 {

Ч 35 {

J5{ J7{ J8{

39{

40 (:

ti{ .

5{

5 61 62

У

Л7

W

27

46

Чд

Фиг.2

5 .. felд 1„.„

Ш

3г

ь1

г г

VfJ 4Ц,

&;sVs bs

,

t

гЬ

1

сц

Joa

«

5

I . .u CZZ-IIZJ CZZZZnZD

. r.

Tff VTT Ы И T m

S- nS- r, cCS b (x P H h

S- « M «

t t tn « « d -Jfi vf «2 V «Э -.

1

т

Joa

§

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения дисперсии коэффициентов Хаара | 1982 |

|

SU1083201A2 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для ранговой фильтрации с произвольной формой окна | 1990 |

|

SU1727137A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1310839A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для определения дисперсии коэффициентов Хаара | 1980 |

|

SU942042A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1569846A1 |

Изобретение относится к цифровой вычислительной технике, а именно к проблемно-ориентированным параллельным процессорам. Цель изобретения -увеличение быстродействия. Поставленная цель достигается тем, что устройство содержит матрицу размером K L арифметических блоков,блок синхронизации. 7 ил. I табл. ю о

1

«Я1

c

ij

c

J I

i:

u§ ( « f E « ( 5Й t oT « ; x3 « SS «at; S 4

s§

«CO

D

ЙТ

«

L

fit

N1 )S

ЕЙ

sT

f.

IQQ iQa

Т I т t T I

( 5Й t oT « ; S «at; S 4

«

1 «о

jy т ч

НЧ

и Ы &

brjl Kjl ЧЭ

В

ul - iSSi Ш El.

IccH Т U J у «a tr j И

IK

brjl Kjl ЧЭ

В

j« ;

if

El.

(futif

Чв

Редактор Ю,Петрушке:

Составитель В.Смирнов Техред Л. Сердюк она

Заказ 7904/48Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытш 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г„ Ужгород, ул. Проектная, 4

(

L4-.-.HH-J

W Й/г. 7

Корректор Л. Патай

| 1979 |

|

SU826360A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения двумерныхзАдАч МАТЕМАТичЕСКОй физиКи | 1978 |

|

SU811272A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Параллельное вычислительное устройство для решения разностных уравнений задач теории поля | 1975 |

|

SU742945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-06-28—Подача